Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I²C, SPI                                                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c62b-04-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

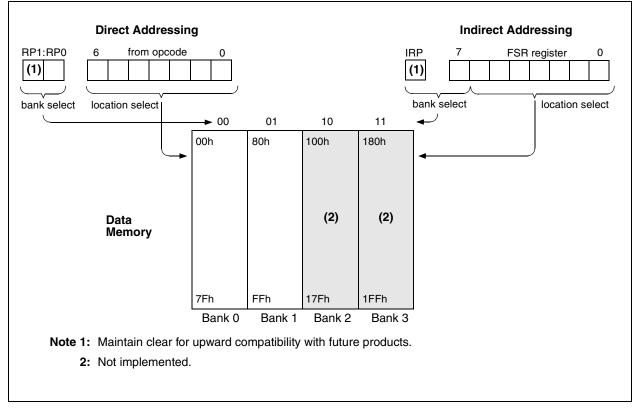

### 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*).

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-1.

### EXAMPLE 2-1: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

|          | movlw<br>movwf |       | ;initialize pointer<br>; to RAM |

|----------|----------------|-------|---------------------------------|

| NEXT     | clrf           | INDF  | ;clear INDF register            |

|          | incf           | FSR   | ;inc pointer                    |

|          | btfss          | FSR,4 | ;all done?                      |

|          | goto           | NEXT  | ;NO, clear next                 |

| CONTINUE |                |       |                                 |

|          | :              |       | ;YES, continue                  |

An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-3. However, IRP is not used in the PIC16C62B/72A.

### FIGURE 2-3: DIRECT/INDIRECT ADDRESSING

## 3.0 I/O PORTS

Some I/O port pins are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

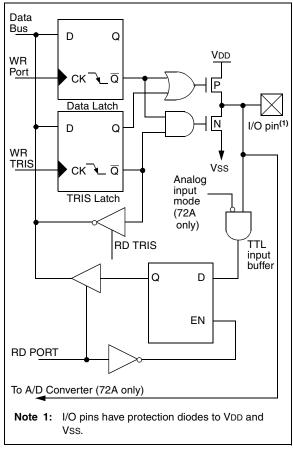

### 3.1 PORTA and the TRISA Register

PORTA is a 6-bit wide bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (=1) will make the corresponding PORTA pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISA bit (=0) will make the corresponding PORTA pin an output, (i.e., put the contents of the output latch on the selected pin).

The PORTA register reads the state of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

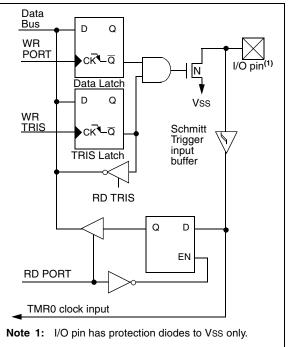

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers.

Pin RA5 is multiplexed with the SSP to become the RA5/SS pin.

On the PIC16C72A device, other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

| Note: | On a Power-on Reset, pins with analog           |  |  |  |  |

|-------|-------------------------------------------------|--|--|--|--|

|       | functions are configured as analog inputs       |  |  |  |  |

|       | with digital input buffers disabled . A digital |  |  |  |  |

|       | read of these pins will return '0'.             |  |  |  |  |

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

### FIGURE 3-1: BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

### FIGURE 3-2: BLOCK DIAGRAM OF RA4/T0CKI PIN

© 1998-2013 Microchip Technology Inc.

### TABLE 3-1 PORTA FUNCTIONS

| Name         | Bit# | Buffer | Function                                                                                      |

|--------------|------|--------|-----------------------------------------------------------------------------------------------|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input <sup>(1)</sup>                                                   |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input <sup>(1)</sup>                                                   |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input <sup>(1)</sup>                                                   |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input <sup>(1)</sup> or VREF <sup>(1)</sup>                            |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0<br>Output is open drain type                  |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input <sup>(1)</sup> |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: The PIC16C62B does not implement the A/D module.

### TABLE 3-2 SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name                          | Bit 7 | Bit 6 | Bit 5                         | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on all other resets |

|---------|-------------------------------|-------|-------|-------------------------------|-------|-------|-------|-------|-------|-------------------------|---------------------------|

| 05h     | PORTA<br>(for PIC16C72A only) | —     | —     | RA5                           | RA4   | RA3   | RA2   | RA1   | RA0   | 0x 0000                 | 0u 0000                   |

| 05h     | PORTA<br>(for PIC16C62B only) | —     | —     | RA5                           | RA4   | RA3   | RA2   | RA1   | RA0   | xx xxxx                 | uu uuuu                   |

| 85h     | TRISA                         |       |       | PORTA Data Direction Register |       |       |       |       |       | 11 1111                 | 11 1111                   |

| 9Fh     | ADCON1 <sup>(1)</sup>         |       |       |                               |       |       | PCFG2 | PCFG1 | PCFG0 | 000                     | 000                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA. Note 1: The PIC16C62B does not implement the A/D module. Maintain this register clear.

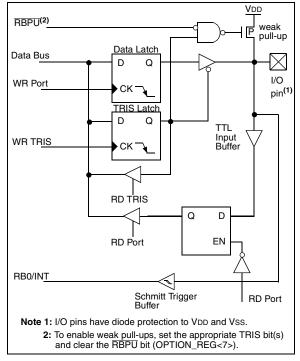

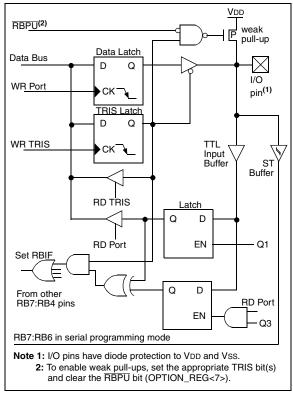

### 3.2 PORTB and the TRISB Register

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (=1) will make the corresponding PORTB pin an input, (i.e., put the corresponding output driver in a hi-impedance mode). Clearing a TRISB bit (=0) will make the corresponding PORTB pin an output, (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit  $\overline{\text{RBPU}}$  (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

### FIGURE 3-3: BLOCK DIAGRAM OF RB3:RB0 PINS

Four of PORTB's pins, RB7:RB4, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e. any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

RB0/INT is an external interupt pin and is configured using the INTEDG bit (OPTION\_REG<6>). RB0/INT is discussed in detail in Section 10.10.1.

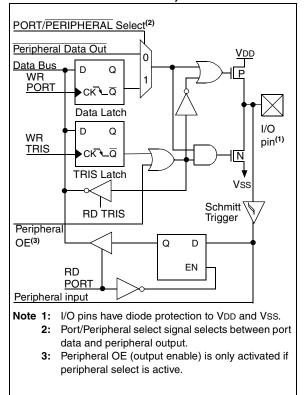

### 3.3 PORTC and the TRISC Register

PORTC is an 8-bit wide bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (=1) will make the corresponding PORTC pin an input, (i.e., put the corresponding output driver in a hi-impedance mode). Clearing a TRISC bit (=0) will make the corresponding PORTC pin an output, (i.e., put the contents of the output latch on the selected pin).

PORTC is multiplexed with several peripheral functions (Table 3-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override maybe in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

### FIGURE 3-5: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

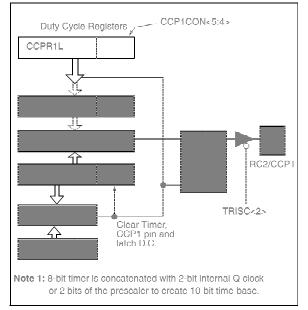

### 7.3 <u>PWM Mode</u>

In Pulse Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force  |

|-------|-------------------------------------------|

|       | the CCP1 PWM output latch to the default  |

|       | low level. This is not the PORTC I/O data |

|       | latch.                                    |

Figure 7-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step by step procedure on how to set up the CCP module for PWM operation, see Section 7.3.3.

FIGURE 7-3: SIMPLIFIED PWM BLOCK DIAGRAM

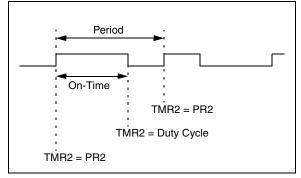

A PWM output (Figure 7-4) has a time base (period) and a time that the output stays high (on-time). The frequency of the PWM is the inverse of the period (1/period).

### FIGURE 7-4: PWM OUTPUT

### 7.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

| Note: | The Timer2 postscaler (see Section 6.0) is   |

|-------|----------------------------------------------|

|       | not used in the determination of the PWM     |

|       | frequency. The postscaler could be used to   |

|       | have a servo update rate at a different fre- |

|       | quency than the PWM output.                  |

### 7.3.2 PWM ON-TIME

The PWM on-time is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. CCPR1L contains eight MSbs and CCP1CON<5:4> contains two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

CCPR1L and CCP1CON<5:4> can be written to at any time, but the on-time value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM on-time. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2 concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

Maximum PWM resolution (bits) for a given PWM frequency:

Resolution =

$$\frac{\log(\frac{Fosc}{Fpwm})}{\log(2)}$$

bits

Note: If the PWM on-time value is larger than the PWM period, the CCP1 pin will not be cleared.

For an example PWM period and on-time calculation, see the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

### 8.3.1.2 RECEPTION

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no acknowledge ( $\overline{ACK}$ ) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set or bit SSPOV (SSPCON<6>) is set.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

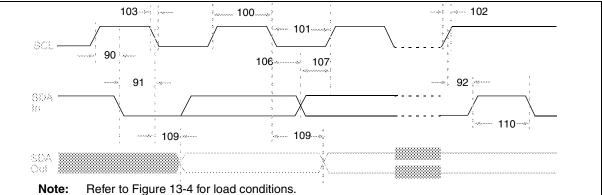

### FIGURE 8-3: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

| Receiving Address         R/W           SDA         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - </th <th>=0Receiving Data<br/>_ACK_D7XD6XD5XD4XD3XD2XD1XE<br/></th> <th></th> <th></th> | =0Receiving Data<br>_ACK_D7XD6XD5XD4XD3XD2XD1XE<br>                      |                                       |                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------|--------------------------------------|

| SSPI <u>F (PIR1&lt;3&gt;)</u><br>BF ( <u>SSPSTAT&lt;0&gt;)</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>Cleared in software</li> <li>SSPBUF register is read</li> </ul> |                                       | Bus Master<br>terminates<br>transfer |

| SSP <u>OV (SSPCON&lt;6&gt;)</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Bit SSPOV is set b                                                       | ecause the SSPBUF register is still f |                                      |

### REGISTER 8-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94h)

| R/W-0  | R/W-0                                                                                                                                                | R-0                                                                                         | R-0                      | R-0                                                        | R-0                                              | R-0           | R-0         |                                                                                      |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------|------------------------------------------------------------|--------------------------------------------------|---------------|-------------|--------------------------------------------------------------------------------------|

| SMP    | CKE                                                                                                                                                  | D/A                                                                                         | Р                        | S                                                          | R/W                                              | UA            | BF          | R = Readable bit                                                                     |

| bit7   |                                                                                                                                                      |                                                                                             |                          |                                                            |                                                  |               | bit0        | W = Writable bit<br>U = Unimplemented bit, read<br>as '0'<br>- n =Value at POR reset |

| bit 7: | $\frac{\text{SPI Ma}}{1 = \text{Inpl}}$ $0 = \text{Inpl}$ $\frac{\text{SPI Sla}}{\text{SMP m}}$ $\frac{l^2 C \text{ Mod}}{l^2 C \text{ Mod}}$        | <u>ister Oper</u><br>ut data sa<br>ut data sa<br><u>uve Mode</u><br>ust be cle<br><u>de</u> | ampled at<br>ampled at   | end of data<br>middle of d<br>n SPI is us                  | i output time<br>ata output tii<br>ed in slave n | me            |             |                                                                                      |

| bit 6: | $\frac{\text{SPI Mo}}{\text{CKP} =}$ $1 = \text{Dat}$ $0 = \text{Dat}$ $1 = \text{Dat}$ $0 = \text{Dat}$ $\frac{1^2 \text{C Mos}}{1^2 \text{C Mos}}$ | <u>de</u><br>0<br>ta transmi<br>ta transmi<br>ta transmi<br>ta transmi<br><u>de</u>         | tted on fa<br>tted on fa | sing edge o<br>Iling edge c<br>Iling edge c<br>sing edge o | of SCK<br>of SCK                                 |               |             |                                                                                      |

| bit 5: | 1 = Indi                                                                                                                                             | icates tha                                                                                  | t the last l             |                                                            | r)<br>ed or transm<br>ed or transm               |               |             |                                                                                      |

| bit 4: | detecte<br>1 = Indi                                                                                                                                  | d last, SS<br>icates tha                                                                    | SPEN is cl               | eared)<br>it has been                                      | cleared whe                                      |               |             | disabled, or when the Start bit<br>ET)                                               |

| bit 3: | detecte<br>1 = Indi                                                                                                                                  | d last, SS<br>icates tha                                                                    | SPEN is cl               | eared)<br>it has been                                      | cleared who                                      |               |             | disabled, or when the Stop bit<br>ET)                                                |

| bit 2: | This bit                                                                                                                                             | t holds th<br>s match to<br>ad                                                              | e R/W bi                 |                                                            |                                                  |               | dress match | n. This bit is only valid from th                                                    |

| bit 1: | 1 = Indi                                                                                                                                             | icates tha                                                                                  | t the user               | it I <sup>2</sup> C mode<br>needs to u<br>d to be upd      | pdate the ac                                     | ldress in the | e SSPADD i  | register                                                                             |

| bit 0: | BF: But                                                                                                                                              | ffer Full S                                                                                 | tatus bit                |                                                            |                                                  |               |             |                                                                                      |

|        | 1 = Red<br>0 = Red                                                                                                                                   | ceive com<br>ceive not                                                                      | complete,                | es)<br>PBUF is ful<br>SSPBUF is                            |                                                  |               |             |                                                                                      |

|        | 1 = Tra                                                                                                                                              |                                                                                             | rogress, S               | SPBUF is<br>PBUF is er                                     |                                                  |               |             |                                                                                      |

### TABLE 11-2 PIC16CXXX INSTRUCTION SET

| Operands         MSb         LSb         Affected           BYTE-ORIENTED FILE REGISTER OPERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Mnemonic, |       | Description                 |       | 14-Bit Opcode |      |      |      | Status   | Notes |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|-----------------------------|-------|---------------|------|------|------|----------|-------|

| ADDWF         f, d         Add W and f         1         00         0111         dfff         ffff         C,DC,Z           ANDWF         f, d         AND W with f         1         00         0101         dfff         ffff         Z           CLRF         f         Clear W         1         00         0001         lfff         ffff         Z           COMF         f, d         Complement f         1         00         0011         dfff         ffff         Z           COMF         f, d         Decrement f         1         00         1011         dfff         ffff         Z           DECFS         f, d         Decrement f, Skip if 0         1(2)         00         1010         dfff         fff           INCF5         f, d         Increment f, Skip if 0         1(2)         00         1101         dfff         fff         Z           INCFSZ         f, d         Move f         1         00         0000         diff         fff         Z           MOVF         f, d         Move f         1         00         0000         0xx0         0000         R         GR         f, d         Rotate Leift fff urough Carry         1                                                                                                                                                                                                                                                                                                                                                      | Operands  |       |                             |       | MSb           |      |      | LSb  | Affected |       |

| ANDWF         f, d         AND W with f         1         00         0101         dfff         ffff         Z           CLRF         f         Clear W         1         00         0001         1fff         ffff         Z           COMF         f, d         Complement f         1         00         0011         dfff         ffff         Z           COMF         f, d         Decrement f, Skip if 0         1(2)         00         1011         dfff         ffff         Z           DECFSZ         f, d         Increment f, Skip if 0         1(2)         00         111         dfff         ffff         Z           MOVF         f, d         Move f         1         00         000         dffff         Z           MOVF f         d         Move f         1         00         000         000         000         000         000         000           RF         f, d         Rotate Left fhrough Carry         1         00         100         dfff         ffff         Z           SUBWF         f, d         Swap nibbles in f         1         00         010         dfff         ffff         Z           SUBWF         f, b </th <th>BYTE-ORIE</th> <th>NTED</th> <th>FILE REGISTER OPERATIONS</th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th>                                                                                                                                                                                                                     | BYTE-ORIE | NTED  | FILE REGISTER OPERATIONS    |       |               |      |      |      |          |       |

| CLRF         f         Clear f         Clear f         1         00         0001         lfff         ffff         Z           COMF         f, d         Complement f         1         00         0001         dff         ffff         Z           DECF         f, d         Decrement f         1         00         1001         dff         ffff         Z           DECF         f, d         Decrement f, Skip if 0         1(2)         00         1010         dff         ffff         Z           INCFSZ         f, d         Increment f, Skip if 0         1(2)         00         1010         dfff         fff         Z           INCFSZ         f, d         Increment f, Skip if 0         1(2)         00         111         dfff         Z           INCFSZ         f, d         Increment f, Skip if C         1         00         000         dfff         Z           INCFSZ         f, d         Increment f, Skip if C         1         00         100         dfff         Z           MOVF         f, d         Move W to f         1         00         100         000         000         000         R         GR         GR         GR         GR                                                                                                                                                                                                                                                                                                                                                | ADDWF     | f, d  | Add W and f                 | 1     | 00            | 0111 | dfff | ffff | C,DC,Z   | 1,2   |

| CLRW         -         Clear W         1         00         0001         0000         0011         Z           COMF         f, d         Cormplement f         1         00         0011         dff ffff         Z           DECF         f, d         Decrement f, Skip if 0         1(2)         00         0011         dff ffff         Z           INCF f, d         Increment f, Skip if 0         1(2)         00         1010         dff ffff         Z           INCF f, d         Increment f, Skip if 0         1(2)         00         1010         dff ffff         Z           INCF f, d         Increment f, Skip if 0         1(2)         00         1011         dff ffff         Z           INCF f, d         Increment f, Skip if 0         1         00         0000         dff ffff         Z           MOVF f, d         Move f         1         00         0000         dff ffff         Z           SUBWF         f, d         Rotate Left ftmough Carry         1         00         0010         dff ffff         C,DC,Z           SUBWF         f, d         Subtract W from f         1         00         1010         dfff fffff         Z         Z           SUBWF                                                                                                                                                                                                                                                                                                                            | ANDWF     | f, d  | AND W with f                | 1     | 00            | 0101 | dfff | ffff | Z        | 1,2   |

| COMF         f, d         Complement f         1         00         1001         dfff         ffff         Z           DECFSZ         f, d         Decrement f, Skip if 0         1(2)         00         1011         dfff         ffff         Z           INCF         f, d         Increment f         1         00         1010         dfff         fffff         Z           INCFSZ         f, d         Increment f, Skip if 0         1(2)         00         1111         dfff         fffff         Z           IORWF         f, d         Increment f, Skip if 0         1(2)         00         1111         dfff         fffff         Z           MOVF         f         Move f         1         00         0000         dfff         fffff         Z           MOVF f         Move V to f         1         00         0000         dfff         fffff         Z           SUBWF f, d         Subtract W from f         1         00         100         dfff         fffff         C,DC,Z           SWAPF         f, d         Subtract W from f         1         00         0101         dfff         fffff         Z           BIT-ORIENTED FILE         Ecolusive OR W w                                                                                                                                                                                                                                                                                                                                      | CLRF      | f     | Clear f                     | 1     | 00            | 0001 | lfff | ffff | Z        | 2     |

| DECF         f, d         Decrement f         1         00         0011         dfff         fff         Z           DECFSZ         f, d         Increment f         1         00         1010         dfff         fff         Z           INCF f, d         Increment f         1         00         1010         dfff         ffff         Z           INCFSZ         f, d         Increment f, Skip if 0         1(2)         00         1111         dfff         fff         Z           INCFSZ         f, d         Inclusive OR W with f         1         00         0100         dfff         fff         Z           MOVF         f, d         Move f         1         00         1000         dfff         ffff         Z           MOVWF         f, d         Rotate Left fthrough Carry         1         00         1101         dfff         fff         C         C         Z           SUBWF         f, d         Rotate Left fthrough Carry         1         00         1100         dfff         fff         C         C         C         C         C         C         C         C         C         C         C         C         C         C                                                                                                                                                                                                                                                                                                                                                              | CLRW      | -     | Clear W                     | 1     | 00            | 0001 | 0000 | 0011 |          |       |

| DECFSZ         f, d         Decrement f, Skip if 0         1(2)         0         1011         dfff ffff           INCF f, d         Increment f         1         0         1010         dfff ffff         Z           INCFSZ f, d         Increment f, Skip if 0         1(2)         0         1111         dfff ffff         Z           INCFSZ f, d         Inclusive CR W with f         1         0         0.000         dfff ffff         Z           MOVF f, d         Move f         1         0         0.000         dfff ffff         Z           MOVWF f         Move W to f         1         0         0.0000         0.000         C.C.C.C.C.C.C.C.C.C.C.C.C.C.C.C.C.C.C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | COMF      | f, d  | Complement f                |       | 00            | 1001 | dfff | ffff | Z        | 1,2   |

| INCF         f, d         Increment f         1         00         1010         dfff         fff         Z           INCFSZ         f, d         Increment f, Skip if 0         1(2)         00         1111         dfff         fff         Z           IORWF         f, d         Move OR W with f         1         00         0100         dfff         fff         Z           MOVF         f, d         Move W to f         1         00         0000         lfff         fff         Z           MOVF         f         Move W to f         1         00         0000         lfff         Gff         Z           MOVF         f         Rotate Left fthrough Carry         1         00         1100         dfff         Gff         C         C           SUBWF         f, d         Rotate Left fthrough Carry         1         00         1100         dfff         fff         C         C,DC,Z           SUBWF         f, d         Subtract W from f         1         00         1010         dfff         ffff         C         C,DC,Z           SUBWF         f, d         Subtract W from f         1         01         010 bb         bfff         fffff                                                                                                                                                                                                                                                                                                                                                  | DECF      | f, d  | Decrement f                 | 1     | 00            | 0011 | dfff | ffff | Z        | 1,2   |

| INCFSZ         f, d         Increment f, Skip if 0         1(2)         00         1111         dff ffff         Z           MOVF         f, d         Inclusive OR W with f         1         00         0100         dfff ffff         Z           MOVF         f, d         Move f         1         00         0000         dfff ffff         Z           MOVF         f, d         Move f         1         00         0000         dfff ffff         Z           MOVF         f, d         Move f         1         00         0000         dfff         ffff           NOP         No Operation         1         00         100         dfff         ffff         C           SUBWF         f, d         Rotate Left fthrough Carry         1         00         1100         dfff         ffff         C         C,DC,Z           SWAPF         f, d         Swap nibbles in f         1         00         110         dfff         ffff         Z           BIT-ORIENTED FILE         REGISTER OPERATIONS         1         1         01         0bb bfff         fffff         Z           BTFSS         f, b         Bit Test f, Skip if Set         1         1         1                                                                                                                                                                                                                                                                                                                                             | DECFSZ    | f, d  | Decrement f, Skip if 0      | 1(2)  | 00            | 1011 | dfff | ffff |          | 1,2,3 |

| IORWF         f, d         Inclusive OR W with f         1         00         0100         dfff         ffff         Z           MOVF         f, d         Move f         1         00         0100         dfff         ffff         Z           MOVWF         f         Move W to f         1         00         0000         lfff         ffff         Z           MOVWF         f         Move W to f         1         00         0000         lfff         ffff         Z           NOP         No Operation         1         00         1000         dfff         ffff         C           RRF         f, d         Rotate Left fthrough Carry         1         00         1100         dfff         ffff         C,DC,Z           SWAPF         f, d         Subtract W from f         1         00         110         dfff         ffff         C,DC,Z           SWAPF         f, d         Exclusive OR W with f         1         01         00bb         bfff         ffff         Z           BIT-ORIENTED FILE         REGISTER OPERATIONS         1         11         01         01bb         bfff         ffff           BTFSS         f, b         Bit Test f, S                                                                                                                                                                                                                                                                                                                                               | INCF      | f, d  | Increment f                 |       | 00            | 1010 | dfff | ffff | Z        | 1,2   |

| MOVF         f, d         Move f         Move f         1         00         1000         dfff         ffff         Z           MOVWF         f         Move W to f         1         00         0000         0kx0         0000         Rff         ffff         C           NOP         -         No Operation         1         00         0000         0kx0         0000         Rk         ffff         C         C           RFF         f, d         Rotate Left fthrough Carry         1         00         1100         dfff         ffff         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C                                                                                                                                                                                                                                                                                                                                                                                         | INCFSZ    |       |                             | 1(2)  | 00            | 1111 | dfff | ffff |          | 1,2,3 |

| MOVWF         f         Move W to f         1         00         00000         lfff         ffff           NOP         -         No Operation         1         00         0000         0xx0         0000           RLF         f, d         Rotate Left fthrough Carry         1         00         1101         dfff         ffff         C           SUBWF         f, d         Subtract W from f         1         00         1100         dfff         ffff         C         D         C,DC,Z         D         C,DC,Z         D         D         D         1100         dfff         ffff         C         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D<                                                                                                                                                                                                                                                                                                                                                                                |           | ,     |                             | -     |               | 0100 |      |      | —        | 1,2   |

| NOP         -         No Operation         1         00         0000         0xxx         0000           RLF         f, d         Rotate Left f through Carry         1         00         1101         dfff ffff         C           SUBWF         f, d         Subtract W from f         1         00         0100         dfff ffff         C           SWAPF         f, d         Swap nibbles in f         1         00         0110         dfff ffff         C         C,DC,Z           SWAPF         f, d         Swap nibbles in f         1         00         0110         dfff ffff         C         C,DC,Z           XORWF         f, d         Exclusive OR W with f         1         00         0110         dfff ffff         Z           BIT-ORIENTED FILE REGISTER OPERATIONS         Bit Clear f         1         01         010bb         bfff fffff         Z           BFFSC         f, b         Bit Test f, Skip if Clear         1         1         11         11bb         bfff ffff           LITERAL AND CONTROL OPERATIONS         Interal with W         1         11         111         111k kkkk         kkkk         Z           ADDLW         k         Add literal and W         1                                                                                                                                                                                                                                                                                                          | MOVF      | f, d  | Move f                      | -     | 00            | 1000 | dfff | ffff | Z        | 1,2   |

| RLF         f, d         Rotate Leff through Carry         1         00         1101         dff ffff         C           RRF         f, d         State Right f through Carry         1         00         1101         dff ffff         C           SUBWF         f, d         Subtract W from f         1         00         1100         dff ffff         C         C,DC,Z           SWAPF         f, d         Swap nibbles in f         1         00         1101         dff ffff         C,DC,Z           SWAPF         f, d         Swap nibbles in f         1         00         1101         dff ffff         C,DC,Z           SWAPF         f, d         Swap nibbles in f         1         00         1101         dff fffff         Z           BIT-ORIENTED FILE         REGISTER OPERATIONS         1         01         00bb         bfff         ffff           BTFSC         f, b         Bit Test f, Skip if Clear         1         1         111         111b         bfff         G           ILTERAL AND CONTROL OPERATIONS         ILTERAL AND CONTROL OPERATIONS         1         1         111         111b         Kkkk kkkk         Z           CALL         k         Call subroutine         2 </td <td></td> <td>f</td> <td></td> <td>-</td> <td>00</td> <td>0000</td> <td>lfff</td> <td>ffff</td> <td></td> <td></td>                                                                                                                                                                           |           | f     |                             | -     | 00            | 0000 | lfff | ffff |          |       |

| RRFf, dRotate Right f through Carry1001100dfffffffCSUBWFf, dSubtract W from f1000010dfffffffC,DC,ZSWAPFf, dSwap nibbles in f1001110dfffffffC,DC,ZSWAPFf, dExclusive OR W with f1000110dfffffffZBIT-ORIENTED FILEREGISTER OPERATIONSBCFf, bBit Clear f10100bbbfffffffBSFf, bBit Set f10110bbbfffffffBTFSSf, bBit Test f, Skip if Clear1 (2)0111bbbfffffffBTFSSf, bBit Test f, Skip if Set1 (2)0111bbbfffffffLITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111kkkkkkkkZADDLWkAdd literal and W111111kkkk kkkkZClaulkCall subroutine2100kkk kkkkkTO,PDGOTOkGo to address2101kkk kkkkkZIORLWkInclusive OR literal with W1111000kkkk kkkkRETURReturn from interrupt20000000100IO,PDRETURNReturn from Subroutine200000000001000SLEEPGo into standby mode100 <td< td=""><td>NOP</td><td>-</td><td>No Operation</td><td>-</td><td>00</td><td>0000</td><td>0xx0</td><td>0000</td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | NOP       | -     | No Operation                | -     | 00            | 0000 | 0xx0 | 0000 |          |       |

| SUBWFf, dSubtract W from f1000010dfffffffC,DC,ZSWAPFf, dSwap nibbles in f1001110dfffffffZBIT-ORIENTED FILE REGISTER OPERATIONSBCFf, bBit Clear f10100bbbfffffffBSFf, bBit Clear f10101bbbfffffffBTFSCf, bBit Test f, Skip if Clear1 (2)0110bbbfffffffBTFSSf, bBit Test f, Skip if Set1 (2)0111bbbfffffffLITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111111xkkkkkkkkZCALLkCall subroutine2100kkkkkkkZCALLkGo to address2101kkkkkkkZGOTOkGo to address210111100xkkkkZMOVLWkInclusive OR literal with W1111100xkkkkZMOVLWkReturn from interrupt20000001001TO,PDRETFIE-Return from interrupt21101xxkkkkkkkkRETURN-Return from Subroutine21101xxkkkkkkkkRETURN-Go into standby mode10000000101TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RLF       | ,     | <b>o</b> ,                  | -     | 00            | 1101 | dfff | ffff | С        | 1,2   |

| SWAPFf, dSwap nibbles in f1001110dfffffffZBIT-ORIENTED FILE REGISTER OPERATIONSBCFf, bBit Clear f10100bbbfffffffZBSFf, bBit Clear f10101bbbfffffffZBTFSCf, bBit Test f, Skip if Clear110101bbbfffffffBTFSSf, bBit Test f, Skip if Set1120111bbbfffFfffLITERAL AND COVTROL OPERATIONSADDLWkAdd literal and W111111101kkkkkkkkZADDLWkAdd literal with W1111100kkkkkkkkZCALLkCall subroutine2101kkkkkkkZClear Watchdog Timer110000000100TO,PDGOTOkGo to address2101kkkkkkkZIORLWkInclusive OR literal with W1111000kkkkKkkMOVLWkMove literal to W1110000000001001RETFIE-Return with literal in W21101xxkkkkkkkkRETURN -Return from SubroutineSection for into standby mode100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RRF       | ,     |                             |       | 00            | 1100 | dfff | ffff | -        | 1,2   |

| XORWFf, dExclusive OR W with f1000110dfffffffZBIT-ORIENTED FILE REGISTER OPERATIONSBCFf, bBit Clear f10100bbbffffffffBSFf, bBit Set f10101bbbffffffffBTFSCf, bBit Test f, Skip if Clear1 (2)0110bbbffffffffBTFSSf, bBit Test f, Skip if Set1 (2)0111bbbfffffffLITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111111xkkkkkkkkZCALLkCall subroutine2100kkkkkkkZTO,PDGOTOkGo to address2101kkkkkkkKkkkZMOVLWkInclusive OR literal with W11100xkkkkKkkkZMOVLWkReturn from interrupt20000000001TO,PDRETFIE-Return from Subroutine21101xxkkkkKkkkFO,PDRETURN-Return from Subroutine200000000001001TO,PDRETURN-Return from Subroutine200000000001001TO,PDRETER-Go into standby mode10000001001TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SUBWF     | f, d  | Subtract W from f           | -     | 00            | 0010 | dfff | ffff | C,DC,Z   | 1,2   |

| Bit Clear fBSFf, bBit Clear f10100bbbfffffffBFFSCf, bBit Test f, Skip if Clear1 (2)0110bbbfffffffBTFSCf, bBit Test f, Skip if Clear1 (2)0110bbbfffffffBTFSSf, bBit Test f, Skip if Set1 (2)0110bbbfffffffLITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111111.kkkkkkkkZCALLkAdd literal and W1111001kkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkZCALLkGo to address210111000kkkkkkkkZGOTOkGo to address210111000kkkkZMOVLWkInclusive OR literal with W1111000kkkkZMOVLWkReturn from interrupt20000001001TO,PDGo into standby mode101000000001001TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SWAPF     | f, d  | Swap nibbles in f           |       | 00            | 1110 | dfff | ffff |          | 1,2   |

| BCFf, bBit Clear f10100bbbfffffffBSFf, bBit Set f10101bbbfffffffBTFSCf, bBit Test f, Skip if Clear110101bbbfffffffBTFSSf, bBit Test f, Skip if Set11111bbbfffffffLITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111 xkkkkkkkZADDLWkAdd literal with W1111001 kkkkkkkkC,DC,ZCALLkCall subroutine2100000001101000GOTOkGo to address2101kkkkkkkkkkkZIORLWkInclusive OR literal with W1111000 kkkkkkkkZMOVLWkReturn from interrupt200000000001001RETFIE-Return with literal in W21101xxkkkkkkkkKRETURN-Return from Subroutine200000000001000SLEEP-Go into standby mode10000000110TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -         |       |                             | 1     | 00            | 0110 | dfff | ffff | Z        | 1,2   |

| BSFf, bBit Set f10101bbbfffffffBTFSCf, bBit Test f, Skip if Clear110110bbbfffffffBTFSSf, bBit Test f, Skip if Set110110bbbfffffffLITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111kkkkkkkC,DC,ZADDLWkAdd literal with W1111001kkkkkkkkZCALLkCall subroutine210000001100100TO,PDGOTOkGo to address21011kkkkkkkkkkkkZIORLWkInclusive OR literal with W1111000kkkkKkkkZMOVLWkReturn from interrupt200000000011001TO,PDRETLWkReturn with literal in W21101xxkkkkkkkkKkkkRETURN-Return from Subroutine200000000001000TO,PDSLEEP-Go into standby mode100000001100101TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -         |       |                             |       |               |      |      |      |          |       |

| BTFSC<br>BTFSSf, b<br>bBit Test f, Skip if Clear<br>Bit Test f, Skip if Set1 (2)<br>1 (2)0110bbbfffffffLITERAL AND CONTROL OPERATIONSADDLW<br>ANDLW<br>CALLkAdd literal and W111111111xkkkkkkkkC,DC,ZADDLW<br>ANDLWkAdd literal with W1111111001kkkkkkkkZCALL<br>CALL<br>GOTO<br>GOTO<br>GOTO<br>GOTO<br>KCall subroutine<br>Go to address2100kkkkkkkkkkkZTO,PDGOTO<br>GOTO<br>GOTO<br>GOTO<br>KGo to address2101kkkkkkkZIORLW<br>KInclusive OR literal with W1111000kkkkKkkkZMOVLW<br>RETFIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE <br< td=""><td></td><td>,</td><td></td><td></td><td>01</td><td>00bb</td><td></td><td></td><td></td><td>1,2</td></br<> |           | ,     |                             |       | 01            | 00bb |      |      |          | 1,2   |

| BTFSSf, bBit Test f, Skip if Set1 (2)0111bbbfffffffLITERAL AND COVERATIONSADDLWkAdd literal and W111111 x kkkkkkkkC,DC,ZANDLWkAND literal with W111111 x kkkkkkkkC,DC,ZCALLkCall subroutine2100kkkkkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkZGOTOkGo to address2101kkkkkkkkkkkZIORLWkInclusive OR literal with W1111000kkkkKkkkZMOVLWkMove literal to W1111000kkkkkkkkZRETFIE-Return from interrupt200000000011001RETLWkReturn from Subroutine200000000001000SLEEP-Go into standby mode10000000110TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -         |       |                             | -     | 01            | 01bb | bfff | ffff |          | 1,2   |

| LITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111 111xkkkkkkkkC,DC,ZANDLWkAND literal with W1111001kkkkkkkkC,DC,ZCALLkCall subroutine2100kkkkkkkkkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkZCALLkCall subroutine21000000011001000GOTOkGo to address2101kkkkkkkkkkkZIORLWkInclusive OR literal with W1111000kkkkkkkkZMOVLWkMove literal to W1110000000001001Return from interrupt200000000010011RETLIPReturn from interrupt20000000000100010001000SLEEP-Go into standby mode100000001101001TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |       |                             |       | 01            | 10bb | bfff | ffff |          | 3     |

| ADDLWkAdd literal and W111111 x kkkkkkkkC,DC,ZANDLWkAND literal with W1111001 kkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkZCLRWDT-Clear Watchdog Timer100000001100100TO,PDGOTOkGo to address2101kkkkkkkkkkkZIORLWkInclusive OR literal with W1111000kkkkkkkkZMOVLWkMove literal to W1110000000001001RETFIE-Return from interrupt200000000001001RETURN-Return with literal in W21101xxkkkkkkkkFD,PDSLEEP-Go into standby mode100000001100101TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |       |                             | 1 (2) | 01            | 11bb | bfff | ffff |          | 3     |

| ANDLWkAND literal with W1111001kkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkKkkkZCLRWDT-Clear Watchdog Timer100000001100100TO,PDGOTOkGo to address2101kkkkkkkkkkkKkkkZIORLWkInclusive OR literal with W1111000kkkkkkkkZMOVLWkMove literal to W111000000001001RETFIE-Return from interrupt200000000001001RETLWReturn with literal in W21101xxkkkkkkkkRETURN-Return from Subroutine200000000001000TO,PDSLEEP-Go into standby mode100000001100011TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           | ND CO |                             |       |               |      |      |      |          | •     |

| CALL         k         Call subroutine         2         10         0kkk         kkkk         kkkkk         kkkk         kkkk         kkkkk         kkkk         kkkkk         kkkkkkkkkkkkkkkkkkkkkkkkkkkkkkkkkkkk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |       |                             | -     | 11            |      |      |      |          |       |

| CLRWDT         -         Clear Watchdog Timer         1         00         0000         0110         100           GOTO         k         Go to address         2         10         1kkk         kkkk         kkkk           IORLW         k         Inclusive OR literal with W         1         11         1000         kkkk         kkkk         Z           MOVLW         k         Move literal to W         1         11         1000         kkkk         kkkk         Z           RETFIE         -         Return from interrupt         2         00         0000         0000         1001           RETLW         k         Return with literal in W         2         11         01xx         kkkk         kkkk           RETURN         -         Return from Subroutine         2         00         0000         0000         1000           SLEEP         -         Go into standby mode         1         00         0000         0110         TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |       |                             |       | 11            | 1001 | kkkk | kkkk | Z        |       |

| GOTO         k         Go to address         2         10         1kkk         kkkk         kkkk           IORLW         k         Inclusive OR literal with W         1         11         1000         kkkk         kkkk         Z           MOVLW         k         Move literal to W         1         11         1000         kkkk         kkkk         Z           RETFIE         -         Return from interrupt         2         00         0000         1001           RETLW         k         Return with literal in W         2         11         01xx         kkkk         kkkk           RETURN         -         Return from Subroutine         2         00         0000         1000           SLEEP         -         Go into standby mode         1         00         0000         011         TO, PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -         |       |                             |       | 10            | 0kkk | kkkk |      |          |       |

| IORLW         k         Inclusive OR literal with W         1         11         1000         kkkk         kkkk         Z           MOVLW         k         Move literal to W         1         11         1000         kkkk         kkkk         Z           MOVLW         k         Move literal to W         1         11         1000         kkkk         kkkk         kkkk           RETFIE         -         Return from interrupt         2         00         0000         0000         1001           RETLW         k         Return with literal in W         2         11         01xx         kkkk         kkkk           RETURN         -         Return from Subroutine         2         00         0000         0000         1000           SLEEP         -         Go into standby mode         1         00         0000         011         TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |       | 5                           | -     | 00            |      |      |      | TO,PD    |       |