Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c62b-20-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table of Contents

| 1.0  | Device Overview                                       | F     |

|------|-------------------------------------------------------|-------|

|      | Memory Organization                                   |       |

|      |                                                       |       |

|      | I/O Ports                                             |       |

| 4.0  | Timer0 Module                                         |       |

|      | Timer1 Module                                         |       |

| 6.0  | Timer2 Module                                         | 31    |

| 7.0  | Capture/Compare/PWM (CCP) Module                      | 33    |

|      | Synchronous Serial Port (SSP) Module                  |       |

| 9.0  | Analog-to-Digital Converter (A/D) Module              | 49    |

| 10.0 | Special Features of the CPU                           | 55    |

| 11.0 | Instruction Set Summary                               | 67    |

| 12.0 | Development Support                                   | 75    |

| 13.0 | Electrical Characteristics                            | 81    |

| 14.0 | DC and AC Characteristics Graphs and Tables           | . 103 |

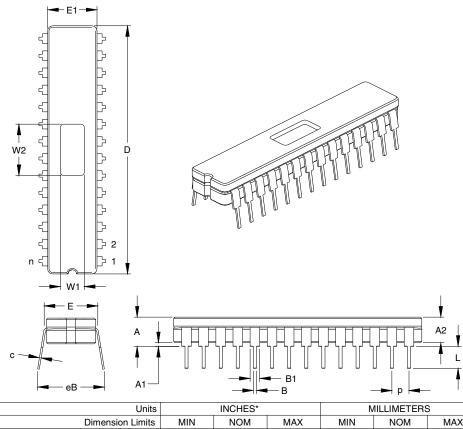

| 15.0 | Packaging Information                                 | . 105 |

| Appe | ndix A. Revision History                              | . 111 |

|      | ndix B: Conversion Considerations                     |       |

|      | ndix C: Migration from Base-line to Mid-Range Devices |       |

|      | · · · · · · · · · · · · · · · · · · ·                 |       |

| On-L | ne Support                                            | . 117 |

|      | er Response                                           |       |

|      | 6C62B/72A Product Identification System               |       |

|      |                                                       |       |

# To Our Valued Customers

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

#### **New Customer Notification System**

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

#### Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended workarounds. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Corrections to this Data Sheet**

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please:

- Fill out and mail in the reader response form in the back of this data sheet.

- E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

#### TABLE 1-1 PIC16C62B/PIC16C72A PINOUT DESCRIPTION

| Pin Name                    | DIP<br>Pin#         | SOIC<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                                  |  |  |  |  |

|-----------------------------|---------------------|--------------|---------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| OSC1/CLKIN                  | 9                   | 9            | I             | ST/CMOS <sup>(3)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                        |  |  |  |  |

| OSC2/CLKOUT                 | 10                  | 10           | 0             | _                      | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |  |  |  |  |

| MCLR/Vpp                    | 1                   | 1            | I/P           | ST                     | Master clear (reset) input or programming voltage input. This pin is an active low reset to the device.                                                                                                      |  |  |  |  |

|                             |                     |              |               |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                          |  |  |  |  |

| RA0/AN0 <sup>(4)</sup>      | 2                   | 2            | I/O           | TTL                    | RA0 can also be analog input 0                                                                                                                                                                               |  |  |  |  |

| RA1/AN1 <sup>(4)</sup>      | 3                   | 3            | I/O           | TTL                    | RA1 can also be analog input 1                                                                                                                                                                               |  |  |  |  |

| RA2/AN2 <sup>(4)</sup>      | 4                   | 4            | I/O           | TTL                    | RA2 can also be analog input 2                                                                                                                                                                               |  |  |  |  |

| RA3/AN3/VREF <sup>(4)</sup> | 5                   | 5            | I/O           | TTL                    | RA3 can also be analog input 3 or analog reference voltage                                                                                                                                                   |  |  |  |  |

| RA4/T0CKI                   | 6                   | 6            | I/O           | ST                     | RA4 can also be the clock input to the Timer0 module.<br>Output is open drain type.                                                                                                                          |  |  |  |  |

| RA5/SS/AN4 <sup>(4)</sup>   | 7                   | 7            | I/O           | TTL                    | RA5 can also be analog input 4 or the slave select for the synchronous serial port.                                                                                                                          |  |  |  |  |

|                             |                     |              |               |                        | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                                |  |  |  |  |

| RB0/INT                     | 21                  | 21           | I/O           | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                                  |  |  |  |  |

| RB1                         | 22                  | 22           | I/O           | TTL                    |                                                                                                                                                                                                              |  |  |  |  |

| RB2                         | 23                  | 23           | I/O           | TTL                    |                                                                                                                                                                                                              |  |  |  |  |

| RB3                         | 24                  | 24           | I/O           | TTL                    |                                                                                                                                                                                                              |  |  |  |  |

| RB4                         | 25                  | 25           | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                     |  |  |  |  |

| RB5                         | 26                  | 26           | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                     |  |  |  |  |

| RB6                         | 27                  | 27           | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming clock.                                                                                                                                                           |  |  |  |  |

| RB7                         | 28                  | 28           | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming data.                                                                                                                                                            |  |  |  |  |

|                             |                     |              |               |                        | PORTC is a bi-directional I/O port.                                                                                                                                                                          |  |  |  |  |

| RC0/T1OSO/T1CKI             | 11                  | 11           | I/O           | ST                     | RC0 can also be the Timer1 oscillator output or Timer1<br>clock input.                                                                                                                                       |  |  |  |  |

| RC1/T1OSI                   | 12                  | 12           | I/O           | ST                     | RC1 can also be the Timer1 oscillator input.                                                                                                                                                                 |  |  |  |  |

| RC2/CCP1                    | 13                  | 13           | I/O           | ST                     | RC2 can also be the Capture1 input/Compare1 output/<br>PWM1 output.                                                                                                                                          |  |  |  |  |

| RC3/SCK/SCL                 | 14                  | 14           | I/O           | ST                     | RC3 can also be the synchronous serial clock input/output for both SPI and I <sup>2</sup> C modes.                                                                                                           |  |  |  |  |

| RC4/SDI/SDA                 | 15                  | 15           | I/O           | ST                     | RC4 can also be the SPI Data In (SPI mode) or data I/O ( $I^2C$ mode).                                                                                                                                       |  |  |  |  |

| RC5/SDO                     | 16                  | 16           | I/O           | ST                     | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                                 |  |  |  |  |

| RC6                         | 17                  | 17           | I/O           | ST                     |                                                                                                                                                                                                              |  |  |  |  |

| RC7                         | 18                  | 18           | I/O           | ST                     |                                                                                                                                                                                                              |  |  |  |  |

| Vss                         | 8, 19               | 8, 19        | Р             | _                      | Ground reference for logic and I/O pins.                                                                                                                                                                     |  |  |  |  |

| Vdd                         | 20                  | 20           | Р             | —                      | Positive supply for logic and I/O pins.                                                                                                                                                                      |  |  |  |  |

| Legend: I = input           | O = outp<br>— = Not |              | I/O =         | input/output           | P = power or program<br>ST = Schmitt Trigger input                                                                                                                                                           |  |  |  |  |

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in serial programming mode.

This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

4: The A/D module is not available on the PIC16C62B.

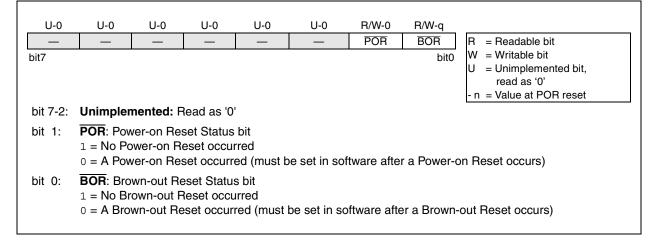

### 2.2.2.6 PCON REGISTER

The Power Control register (PCON) contains flag bits to allow differentiation between a Power-on Reset (POR), Brown-Out Reset (BOR) and resets from other sources.

Note: On Power-on Reset, the state of the BOR bit is unknown and is not predictable. If the BODEN bit in the configuration word is set, the user must first set the BOR bit on a POR, and check it on subsequent resets. If BOR is cleared while POR remains set, a Brown-out reset has occurred. If the BODEN bit is clear, the BOR bit may be ignored.

# REGISTER 2-6: PCON REGISTER (ADDRESS 8Eh)

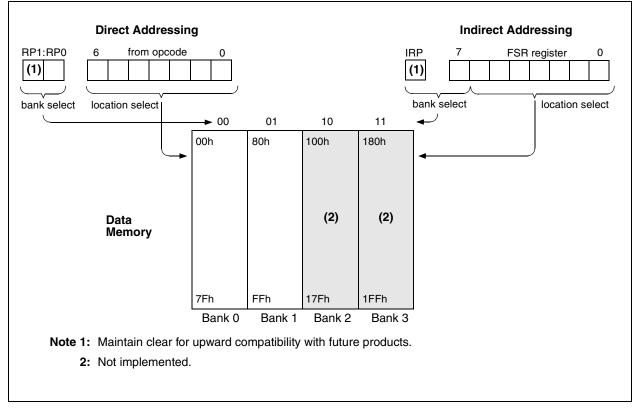

#### 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*).

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-1.

### EXAMPLE 2-1: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

|          | movlw<br>movwf |       | ;initialize pointer<br>; to RAM |

|----------|----------------|-------|---------------------------------|

| NEXT     | clrf           | INDF  | ;clear INDF register            |

|          | incf           | FSR   | ;inc pointer                    |

|          | btfss          | FSR,4 | ;all done?                      |

|          | goto           | NEXT  | ;NO, clear next                 |

| CONTINUE |                |       |                                 |

|          | :              |       | ;YES, continue                  |

An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-3. However, IRP is not used in the PIC16C62B/72A.

# FIGURE 2-3: DIRECT/INDIRECT ADDRESSING

NOTES:

#### 8.3.1.2 RECEPTION

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no acknowledge ( $\overline{ACK}$ ) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set or bit SSPOV (SSPCON<6>) is set.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

# FIGURE 8-3: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

| Receiving Address         R/W           SDA         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - </th <th>=0Receiving Data<br/>_ACK_D7XD6XD5XD4XD3XD2XD1XE<br/></th> <th></th> <th></th> | =0Receiving Data<br>_ACK_D7XD6XD5XD4XD3XD2XD1XE<br>                      |                                       |                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------|--------------------------------------|

| SSPI <u>F (PIR1&lt;3&gt;)</u><br>BF ( <u>SSPSTAT&lt;0&gt;)</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>Cleared in software</li> <li>SSPBUF register is read</li> </ul> |                                       | Bus Master<br>terminates<br>transfer |

| SSP <u>OV (SSPCON&lt;6&gt;)</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Bit SSPOV is set b                                                       | ecause the SSPBUF register is still f |                                      |

# 9.4 <u>A/D Conversions</u>

| Note: | The GO/DONE bit should NOT be set in        |

|-------|---------------------------------------------|

|       | the same instruction that turns on the A/D. |

#### 9.5 Use of the CCP Trigger

An A/D conversion can be started by the "special event trigger" of the CCP1 module. This requires that the CCP1M3:CCP1M0 bits (CCP1CON<3:0>) be programmed as 1011 and that the A/D module be enabled (ADON bit is set). When the trigger occurs, the

TABLE 9-2 SUMMARY OF A/D REGISTERS

GO/DONE bit will be set, starting the A/D conversion, and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D acquisition period with minimal software overhead. The appropriate analog input channel must be selected and the minimum acquisition time must pass before the "special event trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), then the "special event trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

| Address | Name   | Bit 7   | Bit 6      | Bit 5   | Bit 4       | Bit 3      | Bit 2   | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all other Resets |

|---------|--------|---------|------------|---------|-------------|------------|---------|--------|--------|-------------------------|---------------------------|

| 0Bh,8Bh | INTCON | GIE     | PEIE       | TOIE    | INTE        | RBIE       | T0IF    | INTF   | RBIF   | 0000 000x               | 0000 000u                 |

| 0Ch     | PIR1   | _       | ADIF       | —       | _           | SSPIF      | CCP1IF  | TMR2IF | TMR1IF | -0 0000                 | -0 0000                   |

| 8Ch     | PIE1   | _       | ADIE       | —       | _           | SSPIE      | CCP1IE  | TMR2IE | TMR1IE | -0 0000                 | -0 0000                   |

| 1Eh     | ADRES  | A/D Res | ult Regist | er      |             |            |         |        |        | xxxx xxxx               | uuuu uuuu                 |

| 1Fh     | ADCON0 | ADCS1   | ADCS0      | CHS2    | CHS1        | CHS0       | GO/DONE | —      | ADON   | 0000 00-0               | 0000 00-0                 |

| 9Fh     | ADCON1 | _       | —          | —       | —           | —          | PCFG2   | PCFG1  | PCFG0  | 000                     | 000                       |

| 05h     | PORTA  | _       | _          | RA5     | RA4         | RA3        | RA2     | RA1    | RA0    | 0x 0000                 | 0u 0000                   |

| 85h     | TRISA  |         | —          | PORTA D | Data Direct | tion Regis | ter     |        |        | 11 1111                 | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D conversion.

# 10.0 SPECIAL FEATURES OF THE CPU

The PIC16C62B/72A devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Mode Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- ID locations

- In-circuit serial programming<sup>™</sup> (ICSP)

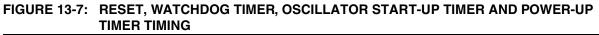

These devices have a Watchdog Timer, which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The

# FIGURE 10-1: CONFIGURATION WORD

other is the Power-up Timer (PWRT), which provides a fixed delay on power-up only and is designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

Additional information on special features is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

# 10.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

| CP1          | CP0                                                                                                                                                                                                                         | CP1                                                                                     | CP0                           | CP1                     | CP0      | _                  | BODEN      | CP1 | CP0 | PWRTE | WDTE | FOSC1 | FOSC0                      | Register:                    | CONFIG |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------|-------------------------|----------|--------------------|------------|-----|-----|-------|------|-------|----------------------------|------------------------------|--------|

| bit13        |                                                                                                                                                                                                                             |                                                                                         |                               |                         |          |                    |            |     |     |       |      |       | bit0                       | Address:                     | 2007h  |

| bit 13<br>5- | <ul> <li>3-8 CP1:CP0: Code Protection bits <sup>(2)</sup></li> <li>i1 = Code protection off</li> <li>i0 = Upper half of program memory code protected</li> <li>i1 = Upper 3/4th of program memory code protected</li> </ul> |                                                                                         |                               |                         |          |                    |            |     |     |       |      |       |                            |                              |        |

|              |                                                                                                                                                                                                                             | 00 = All memory is code protected                                                       |                               |                         |          |                    |            |     |     |       |      |       |                            |                              |        |

| bit 7:       | I                                                                                                                                                                                                                           | Unimplemented: Read as '1'                                                              |                               |                         |          |                    |            |     |     |       |      |       |                            |                              |        |

| bit 6:       |                                                                                                                                                                                                                             | BODEN: Brown-out Reset Enable bit <sup>(1)</sup><br>1 = BOR enabled<br>0 = BOR disabled |                               |                         |          |                    |            |     |     |       |      |       |                            |                              |        |

| bit 3:       |                                                                                                                                                                                                                             | PWRTE<br>1 = PW<br>0 = PW                                                               | RT dis                        | sabled                  | Timer I  | Enable             | e bit (1)  |     |     |       |      |       |                            |                              |        |

| bit 2:       | :                                                                                                                                                                                                                           | WDTE: Watchdog Timer Enable bit<br>1 = WDT enabled<br>0 = WDT disabled                  |                               |                         |          |                    |            |     |     |       |      |       |                            |                              |        |

| bit 1-       |                                                                                                                                                                                                                             | FOSC1<br>11 = RC<br>10 = HS<br>01 = X1<br>00 = LF                                       | C oscil<br>S oscil<br>T oscil | lator<br>lator<br>lator | cillator | <sup>·</sup> Selec | ction bits |     |     |       |      |       |                            |                              |        |

| Note         |                                                                                                                                                                                                                             |                                                                                         |                               |                         |          |                    |            |     |     |       |      |       | dless of the<br>tion schem | e value of bit<br>ne listed. | PWRTE. |

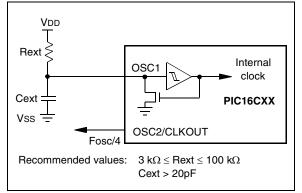

#### 10.2.3 RC OSCILLATOR

For timing insensitive applications, the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 10-4 shows how the R/C combination is connected to the PIC16CXXX.

### FIGURE 10-4: RC OSCILLATOR MODE

# 10.3 <u>Reset</u>

The PIC16CXXX differentiates between various kinds of reset:

- Power-on Reset (POR)

- MCLR reset during normal operation

- MCLR reset during SLEEP

- WDT Reset (during normal operation)

- WDT Wake-up (during SLEEP)

- Brown-out Reset (BOR)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged by any other reset. Most other registers are reset to a "reset state" on Power-on Reset (POR), on the  $\overline{\text{MCLR}}$  and WDT Reset, on  $\overline{\text{MCLR}}$  reset during SLEEP, and on Brown-out Reset (BOR). They are not affected by a WDT Wake-up from SLEEP, which is viewed as the resumption of normal operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared depending on the reset situation, as indicated in Table 10-4. These bits are used in software to determine the nature of the reset. See Table 10-6 for a full description of reset states of all registers.

A simplified block diagram of the on-chip reset circuit is shown in Figure 10-5.

The PIC devices have a  $\overline{\text{MCLR}}$  noise filter in the  $\overline{\text{MCLR}}$  reset path. The filter will ignore small pulses. However, a valid  $\overline{\text{MCLR}}$  pulse must meet the minimum pulse width (TmcL, Specification #30).

No internal reset source (WDT, BOR, POR) will drive the  $\overline{\text{MCLR}}$  pin low.

| TABLE 10-6           | INITIALI | ZATION        | CONDITIONS FOR A                   | LL REGISTERS             |                                 |

|----------------------|----------|---------------|------------------------------------|--------------------------|---------------------------------|

| Register             |          | cable<br>ices | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

| W                    | 62B      | 72A           | XXXX XXXX                          | uuuu uuuu                | սսսս սսսս                       |

| INDF                 | 62B      | 72A           | N/A                                | N/A                      | N/A                             |

| TMR0                 | 62B      | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PCL                  | 62B      | 72A           | 0000h                              | 0000h                    | PC + 1 <sup>(2)</sup>           |

| STATUS               | 62B      | 72A           | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu <b>(3)</b>            |

| FSR                  | 62B      | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| PORTA <sup>(4)</sup> | 62B      | 72A           | 0x 0000                            | 0u 0000                  | uu uuuu                         |

| PORTB <sup>(5)</sup> | 62B      | 72A           | xxxx xxxx                          | uuuu uuuu                | սսսս սսսս                       |

| PORTC <sup>(5)</sup> | 62B      | 72A           | xxxx xxxx                          | սսսս սսսս                | uuuu uuuu                       |

| PCLATH               | 62B      | 72A           | 0 0000                             | 0 0000                   | u uuuu                          |

| INTCON               | 62B      | 72A           | 0000 000x                          | 0000 000u                | uuuu uuuu <b>(1)</b>            |

|                      | 62B      | 72A           | 0000                               | 0000                     | uuuu <b>(1)</b>                 |

| PIR1                 | 62B      | 72A           | -0 0000                            | -0 0000                  | -u uuuu <b>(1)</b>              |

| TMR1L                | 62B      | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| TMR1H                | 62B      | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| T1CON                | 62B      | 72A           | 00 0000                            | uu uuuu                  | uu uuuu                         |

| TMR2                 | 62B      | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| T2CON                | 62B      | 72A           | -000 0000                          | -000 0000                | -uuu uuuu                       |

| SSPBUF               | 62B      | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| SSPCON               | 62B      | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| CCPR1L               | 62B      | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| CCPR1H               | 62B      | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| CCP1CON              | 62B      | 72A           | 00 0000                            | 00 0000                  | uu uuuu                         |

| ADRES                | 62B      | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| ADCON0               | 62B      | 72A           | 0000 00-0                          | 0000 00-0                | uuuu uu-u                       |

| OPTION_REG           | 62B      | 72A           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISA                | 62B      | 72A           | 11 1111                            | 11 1111                  | uu uuuu                         |

| TRISB                | 62B      | 72A           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISC                | 62B      | 72A           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| PIE1                 | 62B      | 72A           | 0000                               | 0000                     | uuuu                            |

|                      | 62B      | 72A           | -0 0000                            | -0 0000                  | -u uuuu                         |

| PCON                 | 62B      | 72A           | 0q                                 | uq                       | uq                              |

| PR2                  | 62B      | 72A           | 1111 1111                          | 1111 1111                | 1111 1111                       |

| SSPADD               | 62B      | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| SSPSTAT              | 62B      | 72A           | 0000 0000                          | 0000 0000                | սսսս սսսս                       |

| ADCON1               | 62B      | 72A           | 000                                | 000                      | uuu                             |

| TABLE 10-6 | INITIALIZATION CONDITIONS FOR ALL REGISTERS |

|------------|---------------------------------------------|

|            |                                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', <math>q = value depends on condition

Note 1: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

**3:** See Table 10-5 for reset value for specific condition.

4: On any device reset, these pins are configured as inputs.

5: This is the value that will be in the port output latch.

#### 10.10.1 INT INTERRUPT

The external interrupt on RB0/INT pin is edge triggered: either rising, if bit INTEDG (OPTION\_REG<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 10.13 for details on SLEEP mode.

#### 10.10.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>). (Section 4.0)

#### 10.10.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>). (Section 3.2)

## 10.11 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt, (i.e., W register and STATUS register). This will have to be implemented in software.

Example 10-1 stores and restores the W and STATUS registers. The register, W\_TEMP, must be defined in each bank and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1).

The example:

- a) Stores the W register.

- b) Stores the STATUS register in bank 0.

- c) Stores the PCLATH register.

- d) Executes the interrupt service routine code (User-generated).

- e) Restores the STATUS register (and bank select bit).

- f) Restores the W and PCLATH registers.

### EXAMPLE 10-1: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM

| MOVWF  | W_TEMP        | ;Copy W to TEMP register, could be bank one or zero     |

|--------|---------------|---------------------------------------------------------|

| SWAPF  | STATUS,W      | ;Swap status to be saved into W                         |

| CLRF   | STATUS        | ;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

| MOVWF  | STATUS_TEMP   | ;Save status to bank zero STATUS_TEMP register          |

| :      |               |                                                         |

| :(ISR) |               |                                                         |

| :      |               |                                                         |

| SWAPF  | STATUS_TEMP,W | ;Swap STATUS_TEMP register into W                       |

|        |               | ;(sets bank to original state)                          |

| MOVWF  | STATUS        | ;Move W into STATUS register                            |

| SWAPF  | W_TEMP,F      | ;Swap W_TEMP                                            |

| SWAPF  | W_TEMP,W      | ;Swap W_TEMP into W                                     |

|        |               |                                                         |

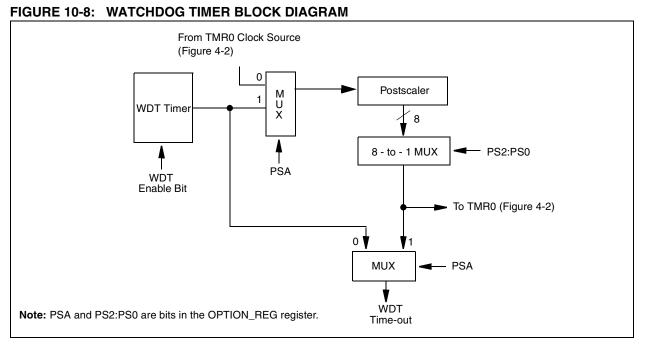

# 10.12 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. The WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit WDTE (Section 10.1).

The WDT time-out period (TWDT, parameter #31) is multiplied by the prescaler ratio, when the prescaler is assigned to the WDT. The prescaler assignment (assigned to either the WDT or Timer0) and prescaler ratio are set in the OPTION\_REG register.

Note: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

**Note:** When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

# FIGURE 10-9: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name         | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|--------------|-------|--------|-------|-------|-------|-------|-------|-------|

| 2007h   | Config. bits |       | BODEN  | CP1   | CP0   | PWRTE | WDTE  | FOSC1 | FOSC0 |

| 81h     | OPTION_REG   | RBPU  | INTEDG | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSS f,b                                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                        |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                                    |

| Description:     | If bit 'b' in register 'f' is '0', then the next instruction is executed.<br>If bit 'b' is '1', then the next instruction is discarded and a $NOP$ is executed instead, making this a 2TCY instruction. |

| CLRF             | Clear f                                                               |  |

|------------------|-----------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] CLRF f                                               |  |

| Operands:        | $0 \le f \le 127$                                                     |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |  |

| Status Affected: | Z                                                                     |  |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |  |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSC f,b                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                    |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                   |

| Description:     | If bit 'b' in register 'f' is '1', then the next instruction is executed.<br>If bit 'b' in register 'f' is '0', then the next instruction is discarded, and a NOP is executed instead, making this a 2TCY instruction. |

| CLRW             | Clear W                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                          |

| Operands:        | None                                                                  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | W register is cleared. Zero bit (Z) is set.                           |

| CALL             | Call Subroutine                                                                                                                                                                                | CLRWDT           | Clear Watchdog Timer                                                                                                             |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                        | Syntax:          | [label] CLRWDT                                                                                                                   |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                             | Operands:        | None                                                                                                                             |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                               | Operation:       | $00h \rightarrow WDT$<br>0 $\rightarrow WDT$ prescaler,<br>1 $\rightarrow \overline{TO}$                                         |

| Status Affected: | None                                                                                                                                                                                           |                  | $1 \rightarrow \overline{PD}$                                                                                                    |

| Description:     | Call Subroutine. First, return address                                                                                                                                                         | Status Affected: | TO, PD                                                                                                                           |

|                  | (PC+1) is pushed onto the stack. The<br>eleven bit immediate address is loaded<br>into PC bits <10:0>. The upper bits of<br>the PC are loaded from PCLATH.<br>CALL is a two cycle instruction. | Description:     | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT. Status bits TO and PD<br>are set. |

| SUBLW            | Subtract W from Literal                                                                                                                   |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] SUBLW k                                                                                                                           |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                         |  |  |  |  |

| Operation:       | $k - (W) \to (W)$                                                                                                                         |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                  |  |  |  |  |

| Description:     | The W register is subtracted (2's com-<br>plement method) from the eight bit lit-<br>eral 'k'. The result is placed in the W<br>register. |  |  |  |  |

| XORLW            | Exclusive OR Literal with W                                                                                                  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                                     |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                          |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                                |  |  |  |  |

| Status Affected: | Z                                                                                                                            |  |  |  |  |

| Description:     | The contents of the W register are<br>XOR'ed with the eight bit literal 'k'.<br>The result is placed in the W regis-<br>ter. |  |  |  |  |

| SUBWF        | Subtract W from f                                                                                                                                                                    | XORWF    |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Syntax:      | [label] SUBWF f,d                                                                                                                                                                    | Syntax:  |

| Operands:    | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                   | Operan   |

| Operation:   | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                | Operatio |

| Status       | C, DC, Z                                                                                                                                                                             | Status A |

| Affected:    |                                                                                                                                                                                      | Descrip  |

| Description: | Subtract (2's complement method) W<br>register from register 'f'. If 'd' is 0, the<br>result is stored in the W register. If 'd' is<br>1, the result is stored back in register 'f'. |          |

| XORWF            | Exclusive OR W with f                                                                                                                                                       |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in[0,1] \end{array}$                                                                                                                  |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                   |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |  |  |  |  |

| SWAPF            | Swap Nibbles in f                                                                                                                                                         |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                                |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                           |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>), (f<7:4>) \rightarrow (destination<3:0>)$                                                                                        |  |  |  |

| Status Affected: | None                                                                                                                                                                      |  |  |  |

| Description:     | The upper and lower nibbles of regis-<br>ter 'f' are exchanged. If 'd' is 0, the<br>result is placed in W register. If 'd' is 1,<br>the result is placed in register 'f'. |  |  |  |

| Oper Oper Oper |       |                                            | Operating<br>Operating | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extended<br>Operating voltage VDD range as described in DC spec Section 13.1<br>and Section 13.2 |     |       |                                                                         |

|----------------|-------|--------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-------------------------------------------------------------------------|

| Param<br>No.   | Sym   | Characteristic                             | Min                    | Тур†                                                                                                                                                                                                                                                                                                                                          | Max | Units | Conditions                                                              |

|                |       |                                            | -                      | -                                                                                                                                                                                                                                                                                                                                             | 0.6 | V     | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C                            |

| D083           |       | OSC2/CLKOUT<br>(RC osc mode)               | -                      | -                                                                                                                                                                                                                                                                                                                                             | 0.6 | V     | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                             |

|                |       |                                            | -                      | -                                                                                                                                                                                                                                                                                                                                             | 0.6 | V     | IOL = 1.2 mA, VDD = 4.5V,<br>-40°C to +125°C                            |

|                |       | Output High Voltage                        |                        |                                                                                                                                                                                                                                                                                                                                               |     |       |                                                                         |

| D090           | Vон   | I/O ports (Note 3)                         | VDD-0.7                | -                                                                                                                                                                                                                                                                                                                                             | -   | V     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +85°C                            |

|                |       |                                            | VDD-0.7                | -                                                                                                                                                                                                                                                                                                                                             | -   | V     | IOH = -2.5 mA, VDD = 4.5V,<br>-40°С to +125°С                           |

| D092           |       | OSC2/CLKOUT (RC osc<br>mode)               | Vdd-0.7                | -                                                                                                                                                                                                                                                                                                                                             | -   | V     | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                            |

|                |       |                                            | Vdd-0.7                | -                                                                                                                                                                                                                                                                                                                                             | -   | V     | IOH = -1.0 mA, VDD = 4.5V,<br>-40°C to +125°C                           |

| D150*          | Vod   | Open-Drain High Voltage                    | -                      | -                                                                                                                                                                                                                                                                                                                                             | 8.5 | V     | RA4 pin                                                                 |

|                |       | Capacitive Loading Specs<br>on Output Pins |                        |                                                                                                                                                                                                                                                                                                                                               |     |       |                                                                         |

| D100           | Cosc2 | OSC2 pin                                   | -                      | -                                                                                                                                                                                                                                                                                                                                             | 15  | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1. |

| D101           | Cio   | All I/O pins and OSC2 (in RC mode)         | -                      | -                                                                                                                                                                                                                                                                                                                                             | 50  | pF    |                                                                         |

| D102           | Cb    | SCL, SDA in I <sup>2</sup> C mode          | -                      | -                                                                                                                                                                                                                                                                                                                                             | 400 | pF    |                                                                         |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the device be driven with external clock in RC mode.

2: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

# 13.4 AC (Timing) Characteristics

# 13.4.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2              | ppS                                 | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|-----------------------|-------------------------------------|-----------|----------------------------------------|

| 2. TppS               |                                     | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                     |                                     |           |                                        |

| F                     | Frequency                           | Т         | Time                                   |

| Lowercas              | se letters (pp) and their meanings: |           |                                        |

| рр                    |                                     |           |                                        |

| сс                    | CCP1                                | OSC       | OSC1                                   |

| ck                    | CLKOUT                              | rd        | RD                                     |

| CS                    | CS                                  | rw        | RD or WR                               |

| di                    | SDI                                 | SC        | SCK                                    |

| do                    | SDO                                 | SS        | SS                                     |

| dt                    | Data in                             | t0        | TOCKI                                  |

| io                    | I/O port                            | t1        | T1CKI                                  |

| mc                    | MCLR                                | wr        | WR                                     |

| Uppercas              | se letters and their meanings:      |           |                                        |

| S                     |                                     |           |                                        |

| F                     | Fall                                | Р         | Period                                 |

| Н                     | High                                | R         | Rise                                   |

| I                     | Invalid (Hi-impedance)              | V         | Valid                                  |

| L                     | Low                                 | Z         | Hi-impedance                           |

| I <sup>2</sup> C only |                                     |           |                                        |

| AA                    | output access                       | High      | High                                   |

| BUF                   | Bus free                            | Low       | Low                                    |

| Tcc:st (I             | <sup>2</sup> C specifications only) |           |                                        |

| CC                    |                                     |           |                                        |

| HD                    | Hold                                | SU        | Setup                                  |

| ST                    |                                     |           |                                        |

| DAT                   | DATA input hold                     | STO       | STOP condition                         |

| STA                   | START condition                     |           |                                        |

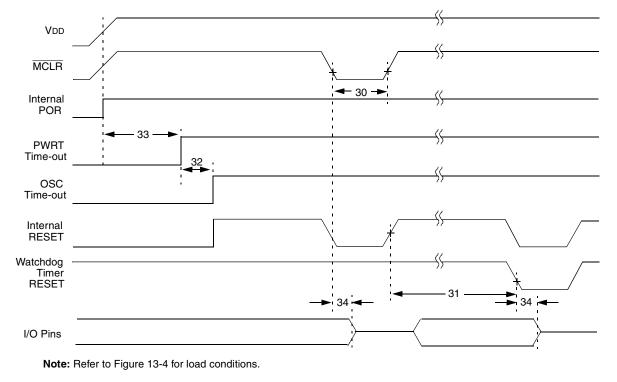

### FIGURE 13-8: BROWN-OUT RESET TIMING