Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

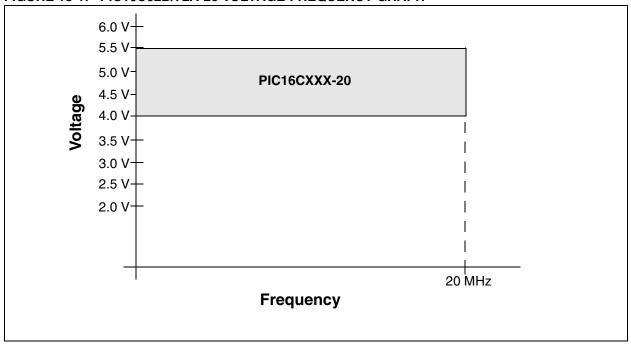

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c62b-20i-ss |

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets; core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral feature section.

TABLE 2-1 SPECIAL FUNCTION REGISTER SUMMARY

| Addr    | Name                    | Bit 7                                     | Bit 6               | Bit 5         | Bit 4         | Bit 3          | Bit 2           | Bit 1        | Bit 0         | Value on:<br>POR,<br>BOR | Value on all other resets (4) |  |

|---------|-------------------------|-------------------------------------------|---------------------|---------------|---------------|----------------|-----------------|--------------|---------------|--------------------------|-------------------------------|--|

| Bank 0  | 3ank 0                  |                                           |                     |               |               |                |                 |              |               |                          |                               |  |

| 00h     | INDF <sup>(1)</sup>     | Addressing                                | this locatio        | n uses conte  | ents of FSR   | to address d   | ata memory      | (not a physi | cal register) | 0000 0000                | 0000 0000                     |  |

| 01h     | TMR0                    | Timer0 mo                                 | dule's regist       | er            |               |                |                 |              |               | xxxx xxxx                | uuuu uuuu                     |  |

| 02h     | PCL <sup>(1)</sup>      | Program C                                 | ounter's (PC        | C) Least Sign | nificant Byte |                |                 |              |               | 0000 0000                | 0000 0000                     |  |

| 03h     | STATUS <sup>(1)</sup>   | IRP <sup>(5)</sup>                        | RP1 <sup>(5)</sup>  | RP0           | TO            | PD             | Z               | DC           | С             | 0001 1xxx                | 000q quuu                     |  |

| 04h     | FSR <sup>(1)</sup>      | Indirect dat                              | a memory a          | ddress poin   | ter           |                |                 |              |               | xxxx xxxx                | uuuu uuuu                     |  |

| 05h     | PORTA <sup>(6,7)</sup>  | _                                         | _                   | PORTA Da      | ta Latch whe  | en written: Po | ORTA pins w     | hen read     |               | 0x 0000                  | 0u 0000                       |  |

| 06h     | PORTB <sup>(6,7)</sup>  | PORTB Da                                  | ta Latch wh         | en written: F | PORTB pins    | when read      |                 |              |               | xxxx xxxx                | uuuu uuuu                     |  |

| 07h     | PORTC <sup>(6,7)</sup>  | PORTC Da                                  | ıta Latch wh        | en written: F | PORTC pins    | when read      |                 |              |               | xxxx xxxx                | uuuu uuuu                     |  |

| 08h-09h | ı                       | Unimpleme                                 | ented               |               |               |                |                 |              |               | _                        | _                             |  |

| 0Ah     | PCLATH <sup>(1,2)</sup> | _                                         | 1                   | 1             | Write Buffe   | r for the upp  | er 5 bits of th | e Program (  | Counter       | 0 0000                   | 0 0000                        |  |

| 0Bh     | INTCON <sup>(1)</sup>   | GIE                                       | PEIE                | TOIE          | INTE          | RBIE           | TOIF            | INTF         | RBIF          | 0000 000x                | 0000 000u                     |  |

| 0Ch     | PIR1                    | _                                         | ADIF <sup>(3)</sup> | 1             | ı             | SSPIF          | CCP1IF          | TMR2IF       | TMR1IF        | -0 0000                  | -0 0000                       |  |

| 0Dh     | I                       | Unimpleme                                 | ented               |               |               |                |                 |              |               | _                        | _                             |  |

| 0Eh     | TMR1L                   | Holding reg                               | jister for the      | Least Signi   | ficant Byte o | of the 16-bit  | TMR1 registe    | r            |               | xxxx xxxx                | uuuu uuuu                     |  |

| 0Fh     | TMR1H                   | Holding reg                               | ister for the       | Most Signif   | icant Byte o  | f the 16-bit T | MR1 register    |              |               | xxxx xxxx                | uuuu uuuu                     |  |

| 10h     | T1CON                   | _                                         | 1                   | T1CKPS1       | T1CKPS0       | T10SCEN        | T1SYNC          | TMR1CS       | TMR10N        | 00 0000                  | uu uuuu                       |  |

| 11h     | TMR2                    | Timer2 mo                                 | dule's regist       | er            |               |                |                 |              |               | 0000 0000                | 0000 0000                     |  |

| 12h     | T2CON                   | _                                         | TOUTPS3             | TOUTPS2       | TOUTPS1       | TOUTPS0        | TMR2ON          | T2CKPS1      | T2CKPS0       | -000 0000                | -000 0000                     |  |

| 13h     | SSPBUF                  | Synchrono                                 | us Serial Po        | rt Receive E  | Buffer/Transr | nit Register   |                 |              |               | xxxx xxxx                | uuuu uuuu                     |  |

| 14h     | SSPCON                  | WCOL                                      | SSPOV               | SSPEN         | CKP           | SSPM3          | SSPM2           | SSPM1        | SSPM0         | 0000 0000                | 0000 0000                     |  |

| 15h     | CCPR1L                  | Capture/Compare/PWM Register1 (LSB)       |                     |               |               |                |                 |              | xxxx xxxx     | uuuu uuuu                |                               |  |

| 16h     | CCPR1H                  | Capture/Compare/PWM Register1 (MSB)       |                     |               |               |                |                 |              | xxxx xxxx     | uuuu uuuu                |                               |  |

| 17h     | CCP1CON                 | - CCP1X CCP1Y CCP1M3 CCP1M2 CCP1M1 CCP1M0 |                     |               |               |                |                 | 00 0000      | 00 0000       |                          |                               |  |

| 18h-1Dh |                         | Unimplemented                             |                     |               |               |                |                 |              | _             | _                        |                               |  |

| 1Eh     | ADRES <sup>(3)</sup>    | A/D Result Register                       |                     |               |               |                |                 |              | xxxx xxxx     | uuuu uuuu                |                               |  |

| 1Fh     | ADCON0 <sup>(3)</sup>   | ADCS1                                     | ADCS0               | CHS2          | CHS1          | CHS0           | GO/DONE         | _            | ADON          | 0000 00-0                | 0000 00-0                     |  |

Legend:  $x = \text{unknown}, u = \text{unchanged}, q = \text{value depends on condition}, -= \text{unimplemented}, \text{read as '0'}, Shaded locations are unimplemented, read as '0'}.$

- Note 1: These registers can be addressed from either bank.

- 2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8> whose contents are transferred to the upper byte of the program counter.

- 3: A/D not implemented on the PIC16C62B, maintain as '0'.

- 4: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

- 5: The IRP and RP1 bits are reserved. Always maintain these bits clear.

- **6:** On any device reset, these pins are configured as inputs.

- **7:** This is the value that will be in the port output latch.

TABLE 2-1 SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

| Addr    | Name                    | Bit 7                                                            | Bit 6               | Bit 5         | Bit 4         | Bit 3          | Bit 2           | Bit 1        | Bit 0         | Value on:<br>POR,<br>BOR | Value on all other resets (4) |

|---------|-------------------------|------------------------------------------------------------------|---------------------|---------------|---------------|----------------|-----------------|--------------|---------------|--------------------------|-------------------------------|

| Bank 1  |                         |                                                                  |                     |               |               |                |                 |              |               |                          |                               |

| 80h     | INDF <sup>(1)</sup>     | Addressing                                                       | this locatio        | n uses conte  | ents of FSR   | to address d   | ata memory      | (not a physi | cal register) | 0000 0000                | 0000 0000                     |

| 81h     | OPTION_REG              | RBPU                                                             | INTEDG              | T0CS          | T0SE          | PSA            | PS2             | PS1          | PS0           | 1111 1111                | 1111 1111                     |

| 82h     | PCL <sup>(1)</sup>      | Program Co                                                       | ounter's (PC        | C) Least Sign | nificant Byte | ı              |                 |              |               | 0000 0000                | 0000 0000                     |

| 83h     | STATUS <sup>(1)</sup>   | IRP <sup>(5)</sup>                                               | RP1 <sup>(5)</sup>  | RP0           | TO            | PD             | Z               | DC           | С             | 0001 1xxx                | 000q quuu                     |

| 84h     | FSR <sup>(1)</sup>      | Indirect dat                                                     | a memory a          | ddress poin   | iter          |                |                 |              |               | xxxx xxxx                | uuuu uuuu                     |

| 85h     | TRISA                   | _                                                                | _                   | PORTA Da      | ta Direction  | Register       |                 |              |               | 11 1111                  | 11 1111                       |

| 86h     | TRISB                   | PORTB Da                                                         | ta Direction        | Register      |               |                |                 |              |               | 1111 1111                | 1111 1111                     |

| 87h     | TRISC                   | PORTC Da                                                         | ta Direction        | Register      |               |                |                 |              |               | 1111 1111                | 1111 1111                     |

| 88h-89h | _                       | Unimpleme                                                        | Unimplemented       |               |               |                |                 |              |               |                          | _                             |

| 8Ah     | PCLATH <sup>(1,2)</sup> | _                                                                | _                   | _             | Write Buffe   | r for the uppe | er 5 bits of th | e Program (  | Counter       | 0 0000                   | 0 0000                        |

| 8Bh     | INTCON <sup>(1)</sup>   | GIE                                                              | PEIE                | TOIE          | INTE          | RBIE           | TOIF            | INTF         | RBIF          | 0000 000x                | 0000 000u                     |

| 8Ch     | PIE1                    | _                                                                | ADIE <sup>(3)</sup> | _             | _             | SSPIE          | CCP1IE          | TMR2IE       | TMR1IE        | -0 0000                  | -0 0000                       |

| 8Dh     | ı                       | Unimpleme                                                        | ented               |               |               |                |                 |              |               | _                        | _                             |

| 8Eh     | PCON                    | -                                                                | -                   | _             | _             | _              | _               | POR          | BOR           | qq                       | uu                            |

| 8Fh-91h | _                       | Unimpleme                                                        | ented               |               |               |                |                 |              |               | _                        | _                             |

| 92h     | PR2                     | Timer2 Period Register                                           |                     |               |               |                |                 |              | 1111 1111     | 1111 1111                |                               |

| 93h     | SSPADD                  | Synchronous Serial Port (I <sup>2</sup> C mode) Address Register |                     |               |               |                |                 |              | 0000 0000     | 0000 0000                |                               |

| 94h     | SSPSTAT                 | SMP                                                              | CKE                 | D/A           | Р             | S              | R/W             | UA           | BF            | 0000 0000                | 0000 0000                     |

| 95h-9Eh | _                       | Unimplemented                                                    |                     |               |               |                |                 |              |               | _                        | _                             |

| 9Fh     | ADCON1 <sup>(3)</sup>   | _                                                                | _                   | _             | _             | _              | PCFG2           | PCFG1        | PCFG0         | 000                      | 000                           |

Legend: x = unknown, u = unchanged, q = value depends on condition, -= unimplemented, read as '0', Shaded locations are unimplemented, read as '0'.

- Note 1: These registers can be addressed from either bank.

- 2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8> whose contents are transferred to the upper byte of the program counter.

- 3: A/D not implemented on the PIC16C62B, maintain as '0'.

- 4: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

- 5: The IRP and RP1 bits are reserved. Always maintain these bits clear.

- **6:** On any device reset, these pins are configured as inputs.

- 7: This is the value that will be in the port output latch.

### 2.2.2.2 OPTION\_REG REGISTER

The OPTION\_REG register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known as the prescaler), the External INT Interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

# REGISTER 2-2: OPTION\_REG REGISTER (ADDRESS 81h)

| R/W-1    | R/W-1                                                                                                                                                 | R/W-1            | R/W-1      | R/W-1       | R/W-1    | R/W-1 | R/W-1 |                                           |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------|-------------|----------|-------|-------|-------------------------------------------|--|--|--|

| RBPU     | INTEDG                                                                                                                                                | T0CS             | T0SE       | PSA         | PS2      | PS1   | PS0   | R = Readable bit                          |  |  |  |

| bit7     |                                                                                                                                                       |                  |            |             |          |       | bit0  | W = Writable bit - n = Value at POR reset |  |  |  |

| bit 7:   | RBPU: PORTB Pull-up Enable bit  1 = PORTB pull-ups are disabled  0 = PORTB pull-ups are enabled for all PORTB inputs                                  |                  |            |             |          |       |       |                                           |  |  |  |

| bit 6:   | INTEDG: Interrupt Edge Select bit  1 = Interrupt on rising edge of RB0/INT pin  0 = Interrupt on falling edge of RB0/INT pin                          |                  |            |             |          |       |       |                                           |  |  |  |

| bit 5:   | TOCS: TMI  1 = Transit  0 = Interna                                                                                                                   | ion on R         | A4/T0CKI   | pin         | (OUT)    |       |       |                                           |  |  |  |

| bit 4:   | T0SE: TMR0 Source Edge Select bit  1 = Increment on high-to-low transition on RA4/T0CKI pin  0 = Increment on low-to-high transition on RA4/T0CKI pin |                  |            |             |          |       |       |                                           |  |  |  |

| bit 3:   | PSA: Pres<br>1 = Presca<br>0 = Presca                                                                                                                 | ıler is ass      | igned to t | he WDT      | ) module |       |       |                                           |  |  |  |

| bit 2-0: | PS2:PS0:                                                                                                                                              | Prescale         | r Rate Sel | lect bits   |          |       |       |                                           |  |  |  |

|          | Bit Value                                                                                                                                             | TMR0 R           | ate WD     | ΓRate       |          |       |       |                                           |  |  |  |

|          | 000                                                                                                                                                   | 1:2<br>1:4       | 1:         |             |          |       |       |                                           |  |  |  |

|          | 010                                                                                                                                                   | 1:8              |            | : 4         |          |       |       |                                           |  |  |  |

|          | 011<br>100                                                                                                                                            | 1:16             |            | : 8<br>: 16 |          |       |       |                                           |  |  |  |

|          | 100                                                                                                                                                   | 1 : 32<br>1 : 64 | -          | : 32        |          |       |       |                                           |  |  |  |

|          | 110                                                                                                                                                   | 1:12             |            | : 64        |          |       |       |                                           |  |  |  |

|          | 111                                                                                                                                                   | 1:25             | 6 1        | : 128       |          |       |       |                                           |  |  |  |

|          |                                                                                                                                                       |                  |            |             |          |       |       |                                           |  |  |  |

#### 4.0 TIMERO MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Read and write

- INT on overflow

- · 8-bit software programmable prescaler

- · INT or EXT clock select

- EXT clock edge select

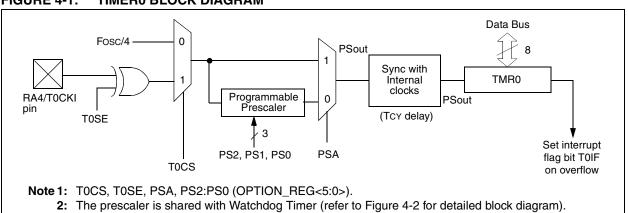

Figure 4-1 is a simplified block diagram of the Timer0 module.

Additional information on timer modules is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

### 4.1 <u>Timer0 Operation</u>

Timer0 can operate as a timer or as a counter.

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed below.

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization. Additional information on external clock requirements is available in the Electrical Specifications section of this manual, and in the PIC® MCU Mid-Range Reference Manual, (DS33023).

#### 4.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 4-2). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. There is only one prescaler available which is shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The prescaler is not readable or writable.

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

Clearing bit PSA will assign the prescaler to the Timer0 module. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable.

Setting bit PSA will assign the prescaler to the Watchdog Timer (WDT). When the prescaler is assigned to the WDT, prescale values of 1:1, 1:2, ..., 1:128 are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

**Note:** Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment or ratio.

FIGURE 4-1: TIMERO BLOCK DIAGRAM

### 6.1 <u>Timer2 Operation</u>

The Timer2 output is also used by the CCP module to generate the PWM "On-Time", and the PWM period with a match with PR2.

The TMR2 register is readable and writable, and is cleared on any device reset.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The match output of TMR2 goes through a 4-bit post-scaler (which gives a 1:1 to 1:16 scaling) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

The prescaler and postscaler counters are cleared when any of the following occurs:

- · a write to the TMR2 register

- · a write to the T2CON register

- any device reset (Power-on Reset, MCLR reset, Watchdog Timer reset or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

# 6.2 <u>Timer2 Interrupt</u>

The Timer2 module has an 8-bit period register PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon reset.

#### 6.3 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module, which optionally uses it to generate shift clock.

TABLE 6-1 REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Address | Name   | Bit 7       | Bit 6          | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|--------|-------------|----------------|---------|---------|---------|--------|---------|---------|-------------------------|---------------------------------|

| 0Bh,8Bh | INTCON | GIE         | PEIE           | TOIE    | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x               | 0000 000u                       |

| 0Ch     | PIR1   | _           | ADIF           | -       | -       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | -00- 0000               | 0000 0000                       |

| 8Ch     | PIE1   | _           | ADIE           | _       | _       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | -0 0000                 | 0000 0000                       |

| 11h     | TMR2   | Timer2 mod  | dule's registe | r       |         |         |        |         |         | 0000 0000               | 0000 0000                       |

| 12h     | T2CON  | _           | TOUTPS3        | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000               | -000 0000                       |

| 92h     | PR2    | Timer2 Peri | od Register    |         |         |         |        |         |         | 1111 1111               | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

# 7.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The CCP (Capture/Compare/PWM) module contains a 16-bit register, which can operate as a 16-bit capture register, as a 16-bit compare register or as a PWM master/slave duty cycle register. Table 7-1 shows the timer resources of the CCP module modes.

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

Additional information on the CCP module is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

TABLE 7-1 CCP MODE - TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

#### TABLE 7-2 INTERACTION OF TWO CCP MODULES

| CCPx Mode | <b>CCPy Mode</b> | Interaction                                                                           |

|-----------|------------------|---------------------------------------------------------------------------------------|

| Capture   | Capture          | Same TMR1 time-base.                                                                  |

| Capture   | Compare          | The compare should be configured for the special event trigger, which clears TMR1.    |

| Compare   | Compare          | The compare(s) should be configured for the special event trigger, which clears TMR1. |

| PWM       | PWM              | The PWMs will have the same frequency and update rate (TMR2 interrupt).               |

| PWM       | Capture          | None.                                                                                 |

| PWM       | Compare          | None.                                                                                 |

# **REGISTER 7-1:CCP1CON REGISTER (ADDRESS 17h)**

| U-0  | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |                                                                              |

|------|-----|-------|-------|--------|--------|--------|--------|------------------------------------------------------------------------------|

| _    | _   | CCP1X | CCP1Y | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 | R = Readable bit                                                             |

| bit7 |     |       |       |        |        |        | bit0   | W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset |

bit 7-6: Unimplemented: Read as '0'

bit 5-4: CCP1X:CCP1Y: PWM Least Significant bits

Capture Mode: Unused Compare Mode: Unused

PWM Mode: These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPR1L.

bit 3-0: CCP1M3:CCP1M0: CCP1 Mode Select bits

0000 = Capture/Compare/PWM off (resets CCP1 module)

0100 = Capture mode, every falling edge

0101 = Capture mode, every rising edge

0110 = Capture mode, every 4th rising edge

0111 = Capture mode, every 16th rising edge

1000 = Compare mode, set output on match (CCP1IF bit is set)

1001 = Compare mode, clear output on match (CCP1IF bit is set)

1010 = Compare mode, generate software interrupt on match (CCP1IF bit is set, CCP1 pin is unaffected)

1011 = Compare mode, trigger special event (CCP1IF bit is set; CCP1 resets TMR1 and starts an A/D conversion (if A/D module is enabled))

11xx = PWM mode

TABLE 8-1 REGISTERS ASSOCIATED WITH SPI OPERATION

| Address | Name    | Bit 7      | Bit 6                   | Bit 5      | Bit 4     | Bit 3      | Bit 2    | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all other resets |

|---------|---------|------------|-------------------------|------------|-----------|------------|----------|--------|--------|-------------------------|---------------------------|

| 0Bh,8Bh | INTCON  | GIE        | PEIE                    | TOIE       | INTE      | RBIE       | TOIF     | INTF   | RBIF   | 0000 000x               | 0000 000u                 |

| 0Ch     | PIR1    | _          | ADIF                    |            | _         | SSPIF      | CCP1IF   | TMR2IF | TMR1IF | -0 0000                 | -0 0000                   |

| 8Ch     | PIE1    | _          | ADIE                    |            | _         | SSPIE      | CCP1IE   | TMR2IE | TMR1IE | -0 0000                 | -0 0000                   |

| 13h     | SSPBUF  | Synchronou | s Serial Po             | ort Receiv | e Buffer/ | Transmit F | Register |        |        | xxxx xxxx               | uuuu uuuu                 |

| 14h     | SSPCON  | WCOL       | SSPOV                   | SSPEN      | CKP       | SSPM3      | SSPM2    | SSPM1  | SSPM0  | 0000 0000               | 0000 0000                 |

| 94h     | SSPSTAT | SMP        | CKE                     | D/A        | Р         | S          | R/W      | UA     | BF     | 0000 0000               | 0000 0000                 |

| 85h     | TRISA   | _          | _                       | PORTA D    | Data Dire | ction Regi | ster     |        |        | 11 1111                 | 11 1111                   |

| 87h     | TRISC   | PORTC Data | Data Direction Register |            |           |            |          |        |        | 1111 1111               | 1111 1111                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the SSP in SPI mode.

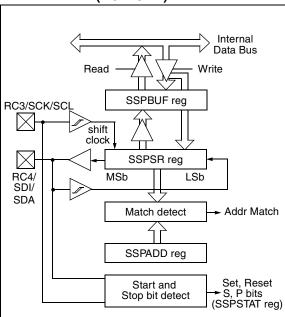

# 8.3 SSP I<sup>2</sup>C Operation

The SSP module in I<sup>2</sup>C mode fully implements all slave functions, except general call support, and provides interrupts on start and stop bits in hardware to support firmware implementations of the master functions. The SSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RC3/SCK/SCL pin, which is the clock (SCL), and the RC4/SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

The SSP module functions are enabled by setting SSP Enable bit SSPEN (SSPCON<5>).

FIGURE 8-2: SSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

The SSP module has five registers for  $I^2C$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the I<sup>2</sup>C operation. Four mode selection bits (SSPCON<3:0>) allow one of the following I<sup>2</sup>C modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with start and stop bit interrupts enabled for firmware master mode support

- I<sup>2</sup>C Slave mode (10-bit address), with start and stop bit interrupts enabled for firmware master mode support

- I<sup>2</sup>C start and stop bit interrupts enabled for firmware master mode support, slave mode idle

Selection of any  $I^2C$  mode, with the SSPEN bit set, forces the SCL and SDA pins to be operated as open drain outputs, provided these pins are programmed to inputs by setting the appropriate TRISC bits.

Additional information on SSP  $I^2C$  operation may be found in the  $PIC^{\textcircled{\tiny{B}}}$  MCU Mid-Range Reference Manual, (DS33023).

#### 8.3.1 SLAVE MODE

In slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched or the data transfer after an address match is received, the hardware automatically will generate the acknowledge ( $\overline{ACK}$ ) pulse, and load the SSPBUF register with the received value in the SSPSR register.

There are certain conditions that will cause the SSP module not to give this  $\overline{ACK}$  pulse. This happens if either of the following conditions occur:

- a) The buffer full bit BF (SSPSTAT<0>) was set before the transfer was completed.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was completed.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. Table 8-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the I<sup>2</sup>C specification, as well as the requirement of the SSP module, is shown in timing parameter #100, THIGH, and parameter #101, TLOW.

# 9.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

**Note:** This section applies to the PIC16C72A only.

The analog-to-digital (A/D) converter module has five input channels.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number (refer to Application Note AN546 for use of A/D Converter). The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD) or the voltage level on the RA3/AN3/VREF pin.

The A/D converter has the feature of being able to operate while the device is in SLEEP mode. To operate in sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

Additional information on the A/D module is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

The A/D module has three registers. These registers are:

- A/D Result Register (ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

A device reset forces all registers to their reset state. This forces the A/D module to be turned off, and any conversion is aborted.

The ADCON0 register, shown in Figure 9-1, controls the operation of the A/D module. The ADCON1 register, shown in Figure 9-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference) or as digital I/O.

### **REGISTER 9-1:ADCONO REGISTER (ADDRESS 1Fh)**

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | U-0 | R/W-0 |

|-------|-------|-------|-------|-------|---------|-----|-------|

| ADCS1 | ADCS0 | CHS2  | CHS1  | CHS0  | GO/DONE | _   | ADON  |

| bit7  |       | •     |       |       |         |     | bit0  |

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as '0'

- n = Value at POR reset

bit 7-6: ADCS1:ADCS0: A/D Conversion Clock Select bits

00 = Fosc/2

01 = Fosc/8

10 = Fosc/32

11 = FRC (clock derived from an internal RC oscillator)

bit 5-3: CHS2:CHS0: Analog Channel Select bits

000 = channel 0, (RA0/AN0)

001 = channel 1, (RA1/AN1)

010 = channel 2, (RA2/AN2)

011 = channel 3, (RA3/AN3)

100 = channel 4, (RA5/AN4)

bit 2: GO/DONE: A/D Conversion Status bit

#### If ADON = 1

- 1 = A/D conversion in progress (setting this bit starts the A/D conversion)

- 0 = A/D conversion not in progress (This bit is automatically cleared by hardware when the A/D conversion is complete)

bit 1: Unimplemented: Read as '0'

bit 0: ADON: A/D On bit

- 1 = A/D converter module is operating

- 0 = A/D converter module is shutoff and consumes no operating current

# 10.0 SPECIAL FEATURES OF THE CPU

The PIC16C62B/72A devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Mode Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- · Watchdog Timer (WDT)

- SLEEP

- Code protection

- · ID locations

- In-circuit serial programming™ (ICSP)

These devices have a Watchdog Timer, which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The

other is the Power-up Timer (PWRT), which provides a fixed delay on power-up only and is designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

Additional information on special features is available in the  $PIC^{\textcircled{\tiny{0}}}$  MCU Mid-Range Reference Manual, (DS33023).

### 10.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

#### FIGURE 10-1: CONFIGURATION WORD

CP1 CP0 CP1 CP0 CP1 CP0 BODEN CP1 CP0 **PWRTE** WDTE FOSC1 FOSC0 Register: CONFIG Address: 2007h bit13 bit0 bit 13-8 CP1:CP0: Code Protection bits (2) 5-4: 11 = Code protection off 10 = Upper half of program memory code protected 01 = Upper 3/4th of program memory code protected 00 = All memory is code protected bit 7: Unimplemented: Read as '1' **BODEN**: Brown-out Reset Enable bit (1) bit 6: 1 = BOR enabled 0 = BOR disabled **PWRTE**: Power-up Timer Enable bit (1) bit 3: 1 = PWRT disabled 0 = PWRT enabled bit 2: WDTE: Watchdog Timer Enable bit 1 = WDT enabled 0 = WDT disabled bit 1-0: FOSC1:FOSC0: Oscillator Selection bits 11 = RC oscillator 10 = HS oscillator 01 = XT oscillator 00 = LP oscillator Note 1: Enabling Brown-out Reset automatically enables Power-up Timer (PWRT), regardless of the value of bit PWRTE. All of the CP1:CP0 pairs must be given the same value to enable the code protection scheme listed.

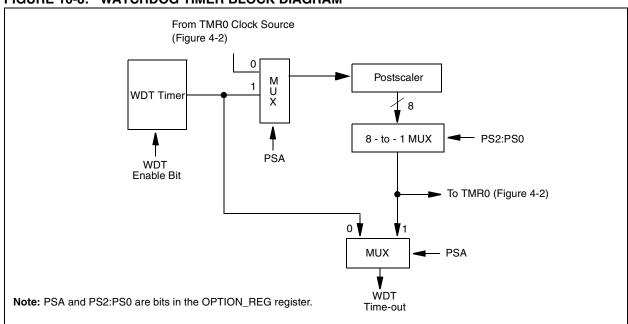

### 10.12 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. The WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit WDTE (Section 10.1).

The WDT time-out period (TWDT, parameter #31) is multiplied by the prescaler ratio, when the prescaler is assigned to the WDT. The prescaler assignment (assigned to either the WDT or Timer0) and prescaler ratio are set in the OPTION\_REG register.

Note: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

Note: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

#### FIGURE 10-8: WATCHDOG TIMER BLOCK DIAGRAM

# FIGURE 10-9: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name         | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|--------------|-------|--------|-------|-------|-------|-------|-------|-------|

| 2007h   | Config. bits |       | BODEN  | CP1   | CP0   | PWRTE | WDTE  | FOSC1 | FOSC0 |

| 81h     | OPTION_REG   | RBPU  | INTEDG | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

| SUBLW            | Subtract W from Literal                                                                                                      | XORLW            | Exclusive OR Literal with W                                                                                       |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] SUBLW k                                                                                                              | Syntax:          | [label] XORLW k                                                                                                   |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                          | Operands:        | $0 \le k \le 255$                                                                                                 |  |  |  |

| Operation:       | $k - (W) \rightarrow (W)$                                                                                                    | Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                     |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                     | Status Affected: | Z                                                                                                                 |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the eight bit literal 'k'. The result is placed in the W register. | Description:     | The contents of the W register are XOR'ed with the eight bit literal 'k'. The result is placed in the W register. |  |  |  |

| SUBWF               | Subtract W from f                                                                                                                                                           |  |  |  |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:             | [ label ] SUBWF f,d                                                                                                                                                         |  |  |  |  |  |  |

| Operands:           | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                          |  |  |  |  |  |  |

| Operation:          | (f) - (W) $\rightarrow$ (destination)                                                                                                                                       |  |  |  |  |  |  |

| Status<br>Affected: | C, DC, Z                                                                                                                                                                    |  |  |  |  |  |  |

| Description:        | Subtract (2's complement method) W register from register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |  |  |  |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                       |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                          |  |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                   |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |  |  |  |  |  |

| Swap Nibbles in f                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [label] SWAPF f,d                                                                                                                                              |

| $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                             |

| $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                        |

| None                                                                                                                                                           |

| The upper and lower nibbles of register 'f' are exchanged. If 'd' is 0, the result is placed in W register. If 'd' is 1, the result is placed in register 'f'. |

|                                                                                                                                                                |

### 12.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- · Integrated Development Environment

- MPLAB™ IDE Software

- Assemblers/Compilers/Linkers

- MPASM Assembler

- MPLAB-C17 and MPLAB-C18 C Compilers

- MPLINK/MPLIB Linker/Librarian

- Simulators

- MPLAB-SIM Software Simulator

- Emulators

- MPLAB-ICE Real-Time In-Circuit Emulator

- PICMASTER®/PICMASTER-CE In-Circuit Emulator

- ICEPIC™

- · In-Circuit Debugger

- MPLAB-ICD for PIC16F877

- · Device Programmers

- PRO MATE® II Universal Programmer

- PICSTART® Plus Entry-Level Prototype Programmer

- · Low-Cost Demonstration Boards

- SIMICE

- PICDEM-1

- PICDEM-2

- PICDEM-3

- PICDEM-17

- SEEVAL®

- KEELOQ®

## 12.1 <u>MPLAB Integrated Development</u> Environment Software

- The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a Windows®-based application which contains:

- Multiple functionality

- editor

- simulator

- programmer (sold separately)

- emulator (sold separately)

- A full featured editor

- A project manager

- · Customizable tool bar and key mapping

- · A status bar

- On-line help

MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU tools (automatically updates all project information)

- · Debug using:

- source files

- absolute listing file

- object code

The ability to use MPLAB with Microchip's simulator, MPLAB-SIM, allows a consistent platform and the ability to easily switch from the cost-effective simulator to the full featured emulator with minimal retraining.

### 12.2 MPASM Assembler

MPASM is a full featured universal macro assembler for all PIC MCUs. It can produce absolute code directly in the form of HEX files for device programmers, or it can generate relocatable objects for MPLINK.

MPASM has a command line interface and a Windows shell and can be used as a standalone application on a Windows 3.x or greater system. MPASM generates relocatable object files, Intel standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file which contains source lines and generated machine code, and a COD file for MPLAB debugging.

MPASM features include:

- MPASM and MPLINK are integrated into MPLAB projects.

- MPASM allows user defined macros to be created for streamlined assembly.

- MPASM allows conditional assembly for multi purpose source files.

- MPASM directives allow complete control over the assembly process.

# 12.3 MPLAB-C17 and MPLAB-C18 C Compilers

The MPLAB-C17 and MPLAB-C18 Code Development Systems are complete ANSI 'C' compilers and integrated development environments for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

#### 12.4 MPLINK/MPLIB Linker/Librarian

MPLINK is a relocatable linker for MPASM and MPLAB-C17 and MPLAB-C18. It can link relocatable objects from assembly or C source files along with precompiled libraries using directives from a linker script.

## 13.0 ELECTRICAL CHARACTERISTICS

## Absolute Maximum Ratings (†)

| Ambient temperature under bias                                     | 55°C to +125°C       |

|--------------------------------------------------------------------|----------------------|

| Storage temperature                                                | 65°C to +150°C       |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4) | 0.3V to (VDD + 0.3V) |

| Voltage on VDD with respect to Vss                                 | 0.3V to +7.5V        |

| Voltage on MCLR with respect to Vss (Note 2)                       | 0V to +13.25V        |

| Voltage on RA4 with respect to Vss                                 | 0V to +8.5V          |

| Total power dissipation (Note 1)                                   | 1.0W                 |

| Maximum current out of Vss pin                                     | 300 mA               |

| Maximum current into VDD pin                                       |                      |

| Input clamp current, IIK (VI < 0 or VI > VDD)                      | ±20 mA               |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                     | ±20 mA               |

| Maximum output current sunk by any I/O pin                         | 25 mA                |

| Maximum output current sourced by any I/O pin                      | 25 mA                |

| Maximum current sunk by PORTA and PORTB (combined)                 | 200 mA               |

| Maximum current sourced by PORTA and PORTB (combined)              | 200 mA               |

| Maximum current sunk by PORTC                                      | 200 mA               |

| Maximum current sourced by PORTC                                   | 200 mA               |

**Note 1:** Power dissipation is calculated as follows: Pdis = VDD x {IDD -  $\sum$  IOH} +  $\sum$  {(VDD-VOH) x IOH} +  $\sum$ (VOI x IOL)

2: Voltage spikes below Vss at the  $\overline{\text{MCLR}/\text{VPP}}$  pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100 $\Omega$  should be used when applying a "low" level to the  $\overline{\text{MCLR}/\text{VPP}}$  pin, rather than pulling this pin directly to Vss.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

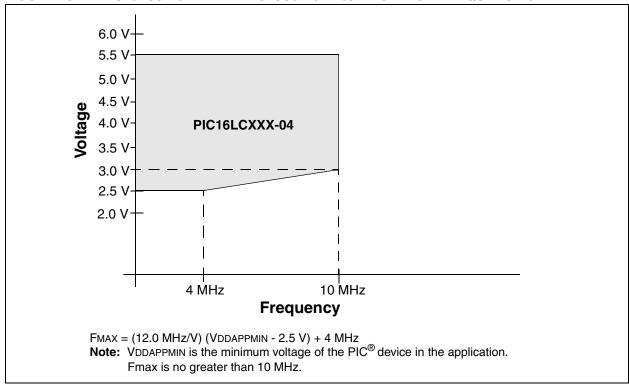

FIGURE 13-1: PIC16C62B/72A-20 VOLTAGE-FREQUENCY GRAPH

FIGURE 13-2: PIC16LC62B/72A AND PIC16C62B/72A/JW VOLTAGE-FREQUENCY GRAPH

DC CHARACTERISTICS

13.3 DC Characteristics: PIC16C62B/72A-04 (Commercial, Industrial, Extended)

PIC16C62B/72A-20 (Commercial, Industrial, Extended)

PIC16LC62B/72A-04 (Commercial, Industrial)

Standard Operating Conditions (unless otherwise stated)

Operating temperature  $0^{\circ}C \le TA \le +70^{\circ}C$  for commercial

-40°C  $\leq$  TA  $\leq$  +85°C for industrial -40°C  $\leq$  TA  $\leq$ +125°C for extended

Operating voltage VDD range as described in DC spec Section 13.1

and Section 13.2

| Param<br>No. | Sym   | Characteristic                        | Min                | Typ† | Max     | Units | Conditions                                   |

|--------------|-------|---------------------------------------|--------------------|------|---------|-------|----------------------------------------------|

| 110.         |       | Input Low Voltage                     |                    |      |         |       |                                              |

|              | VIL   | I/O ports                             |                    |      |         |       |                                              |

| D030         | •     | with TTL buffer                       | Vss                | _    | 0.15Vpp | V     | For entire VDD range                         |

| D030A        |       | Will 112 Ballot                       | Vss                | -    | 0.8V    | V     | 4.5V ≤ VDD ≤ 5.5V                            |

| D031         |       | with Schmitt Trigger buffer           | Vss                | -    | 0.2VDD  | V     |                                              |

| D032         |       | MCLR, OSC1 (in RC mode)               | Vss                | -    | 0.2VDD  | V     |                                              |

| D033         |       | OSC1 (in XT, HS and LP modes)         | Vss                | -    | 0.3VDD  | V     | Note1                                        |

|              |       | Input High Voltage                    |                    |      |         |       |                                              |

|              | VIH   | I/O ports                             |                    | -    |         |       |                                              |

| D040         |       | with TTL buffer                       | 2.0                | -    | VDD     | V     | $4.5V \leq V_{DD} \leq 5.5V$                 |

| D040A        |       |                                       | 0.25VD<br>D + 0.8V | -    | Vdd     | V     | For entire VDD range                         |

| D041         |       | with Schmitt Trigger buffer           | 0.8VDD             | -    | VDD     | V     | For entire VDD range                         |

| D042         |       | MCLR                                  | 0.8VDD             | -    | VDD     | V     |                                              |

| D042A        |       | OSC1 (XT, HS and LP modes)            | 0.7VDD             | -    | VDD     | V     | Note1                                        |

| D043         |       | OSC1 (in RC mode)                     | 0.9VDD             | -    | Vdd     | V     |                                              |

|              |       | Input Leakage Current<br>(Notes 2, 3) |                    |      |         |       |                                              |

| D060         | lıL   | I/O ports                             | -                  | -    | ±1      | μА    | Vss ≤ VPIN ≤ VDD,<br>Pin at hi-impedance     |

| D061         |       | MCLR, RA4/T0CKI                       | -                  | -    | ±5      | μΑ    | Vss ≤ VPIN ≤ VDD                             |

| D063         |       | OSC1                                  | -                  | -    | ±5      | μА    | Vss ≤ VPIN ≤ VDD,<br>XT, HS and LP osc modes |

| D070         | IPURB | PORTB weak pull-up current            | 50                 | 250  | 400     | μΑ    | VDD = 5V, VPIN = VSS                         |

|              |       | Output Low Voltage                    |                    |      |         |       |                                              |

| D080         | Vol   | I/O ports                             | -                  | -    | 0.6     | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C  |

<sup>\*</sup> These parameters are characterized but not tested.

- 2: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the device be driven with external clock in RC mode.

Standard Operating Conditions (unless otherwise stated)

Operating temperature  $0^{\circ}C \leq TA \leq +70^{\circ}C$  for commercial

$-40^{\circ}\text{C}$   $\leq \text{TA} \leq +85^{\circ}\text{C}$  for industrial

-40°C ≤ TA ≤+125°C for extended

Operating voltage VDD range as described in DC spec Section 13.1

and Section 13.2

| Param | Sym   | ym Characteristic Min Typ† Max Unit     |         |      |       |       | Conditions                                                        |

|-------|-------|-----------------------------------------|---------|------|-------|-------|-------------------------------------------------------------------|

| No.   | Jyiii | Characteristic                          | IVIIII  | וקעי | IVIAA | Units | Conditions                                                        |

|       |       |                                         | -       | -    | 0.6   | V     | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C                      |

| D083  |       | OSC2/CLKOUT<br>(RC osc mode)            | -       | -    | 0.6   | V     | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                       |

|       |       |                                         | -       | -    | 0.6   | V     | IOL = 1.2 mA, VDD = 4.5V,<br>-40°C to +125°C                      |

|       |       | Output High Voltage                     |         |      |       |       |                                                                   |

| D090  | Vон   | I/O ports (Note 3)                      | VDD-0.7 | -    | -     | V     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +85°C                      |

|       |       |                                         | VDD-0.7 | -    | -     | V     | IOH = -2.5 mA, VDD = 4.5V,<br>-40°C to +125°C                     |

| D092  |       | OSC2/CLKOUT (RC osc mode)               | VDD-0.7 | -    | -     | V     | IOH = -1.3 mA, VDD = $4.5V$ , $-40^{\circ}$ C to $+85^{\circ}$ C  |

|       |       |                                         | VDD-0.7 | -    | -     | V     | IOH = -1.0 mA, VDD = 4.5V,<br>-40°C to +125°C                     |

| D150* | Vod   | Open-Drain High Voltage                 | -       |      | 8.5   | V     | RA4 pin                                                           |

|       |       | Capacitive Loading Specs on Output Pins |         |      |       |       |                                                                   |

| D100  | Cosc2 | OSC2 pin                                | -       | -    | 15    | pF    | In XT, HS and LP modes when external clock is used to drive OSC1. |

| D101  | Сю    | All I/O pins and OSC2 (in RC mode)      | -       | -    | 50    | pF    |                                                                   |

| D102  | Cb    | SCL, SDA in I <sup>2</sup> C mode       | -       | -    | 400   | pF    |                                                                   |

<sup>\*</sup> These parameters are characterized but not tested.

- **Note 1:** In RC oscillator mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the device be driven with external clock in RC mode.

- 2: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

**DC CHARACTERISTICS**

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

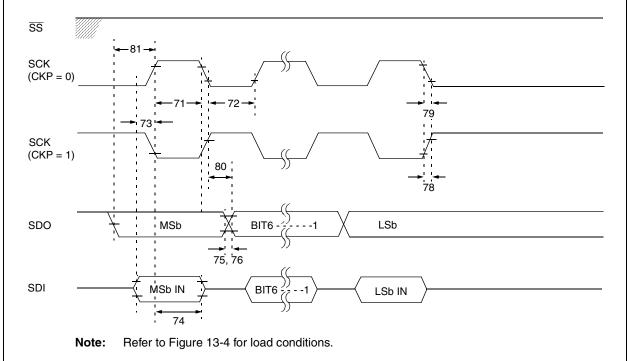

FIGURE 13-12: EXAMPLE SPI MASTER MODE TIMING (CKE = 1)

TABLE 13-8: EXAMPLE SPI MODE REQUIREMENTS (MASTER MODE, CKE = 1)

| Param.<br>No. | Symbol                     | Characteristic                                          |             | Min          | Typ† | Max | Units | Conditions |

|---------------|----------------------------|---------------------------------------------------------|-------------|--------------|------|-----|-------|------------|

| 71            | TscH                       | SCK input high time                                     | Continuous  | 1.25Tcy + 30 | _    | _   | ns    |            |

| 71A           |                            | (slave mode)                                            | Single Byte | 40           | _    | _   | ns    | Note 1     |

| 72            | TscL                       | SCK input low time                                      | Continuous  | 1.25Tcy + 30 | _    | _   | ns    |            |

| 72A           |                            | (slave mode)                                            | Single Byte | 40           | _    | _   | ns    | Note 1     |

| 73            | TdiV2scH,<br>TdiV2scL      | Setup time of SDI data input to SCK edge                |             | 100          | _    | _   | ns    |            |

| 73A           | Тв2в                       | Last clock edge of Byte1 to the 1st clock edge of Byte2 |             | 1.5Tcy + 40  | _    | _   | ns    | Note 1     |

| 74            | TscH2diL,<br>TscL2diL      | Hold time of SDI data input to SCK edge                 |             | 100          | _    | _   | ns    |            |

| 75            | TdoR SDO data output rise  |                                                         | PIC16CXX    | _            | 10   | 25  | ns    |            |

| t             | time                       | PIC16LCXX                                               |             | 20           | 45   | ns  |       |            |

| 76            | TdoF                       | SDO data output fall time                               |             | _            | 10   | 25  | ns    |            |

|               | SCK output rise time       | PIC16CXX                                                | _           | 10           | 25   | ns  |       |            |

|               | (master mode)              | PIC16LCXX                                               |             | 20           | 45   | ns  |       |            |

| 79            | TscF                       | SCK output fall time (master mode)                      |             | _            | 10   | 25  | ns    |            |

| 80            | 100.12001, 020 00.00 00.00 |                                                         | PIC16CXX    |              |      | 50  | ns    |            |

|               | TscL2doV                   | after SCK edge                                          | PIC16LCXX   |              | _    | 100 | ns    |            |

| 81            | TdoV2scH,<br>TdoV2scL      | SDO data output setup to                                | SCK edge    | Tcy          | _    |     | ns    |            |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Specification 73A is only required if specifications 71A and 72A are used.

#### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

# Worldwide Sales and Service

#### **AMERICAS**

**Corporate Office**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/

support Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN

Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara

Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto

Mississauga, Ontario,

Canada

Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong

Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733

Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu

Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing

Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Hangzhou

Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

China - Hong Kong SAR

Tel: 852-2943-5100 Fax: 852-2401-3431

China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai

Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Osaka

Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

Japan - Tokyo

Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu

Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

M-1-----

**Malaysia - Kuala Lumpur** Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung

Tel: 886-7-213-7828 Fax: 886-7-330-9305

Taiwan - Taipei

Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok

Tel: 66-2-694-1351 Fax: 66-2-694-1350

### EUROPE

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich**