#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | ОТР                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c62bt-04i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

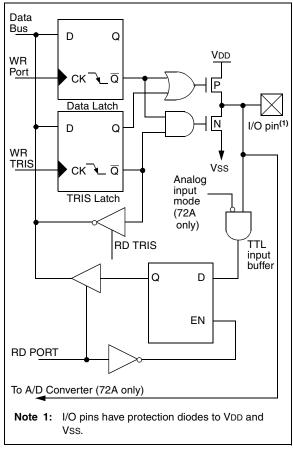

# 3.0 I/O PORTS

Some I/O port pins are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

# 3.1 PORTA and the TRISA Register

PORTA is a 6-bit wide bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (=1) will make the corresponding PORTA pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISA bit (=0) will make the corresponding PORTA pin an output, (i.e., put the contents of the output latch on the selected pin).

The PORTA register reads the state of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

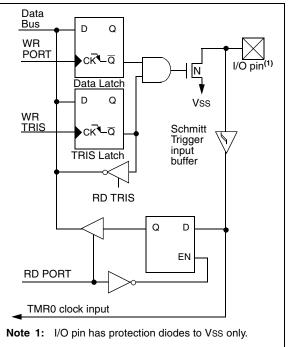

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers.

Pin RA5 is multiplexed with the SSP to become the RA5/SS pin.

On the PIC16C72A device, other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

| Note: | On a Power-on Reset, pins with analog           |

|-------|-------------------------------------------------|

|       | functions are configured as analog inputs       |

|       | with digital input buffers disabled . A digital |

|       | read of these pins will return '0'.             |

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

# FIGURE 3-1: BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

# FIGURE 3-2: BLOCK DIAGRAM OF RA4/T0CKI PIN

© 1998-2013 Microchip Technology Inc.

# TABLE 3-1 PORTA FUNCTIONS

| Name         | Bit# | Buffer | Function                                                                                      |

|--------------|------|--------|-----------------------------------------------------------------------------------------------|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input <sup>(1)</sup>                                                   |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input <sup>(1)</sup>                                                   |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input <sup>(1)</sup>                                                   |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input <sup>(1)</sup> or VREF <sup>(1)</sup>                            |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0<br>Output is open drain type                  |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input <sup>(1)</sup> |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: The PIC16C62B does not implement the A/D module.

# TABLE 3-2 SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name                          | Bit 7 | Bit 6 | Bit 5 | Bit 4                                | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on all other resets |

|---------|-------------------------------|-------|-------|-------|--------------------------------------|-------|-------|-------|-------|-------------------------|---------------------------|

| 05h     | PORTA<br>(for PIC16C72A only) | —     | —     | RA5   | RA4                                  | RA3   | RA2   | RA1   | RA0   | 0x 0000                 | 0u 0000                   |

| 05h     | PORTA<br>(for PIC16C62B only) | —     | —     | RA5   | RA4                                  | RA3   | RA2   | RA1   | RA0   | xx xxxx                 | uu uuuu                   |

| 85h     | TRISA                         |       |       | PORTA | PORTA Data Direction Register11 1111 |       |       |       |       |                         |                           |

| 9Fh     | ADCON1 <sup>(1)</sup>         |       |       |       |                                      |       | PCFG2 | PCFG1 | PCFG0 | 000                     | 000                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA. Note 1: The PIC16C62B does not implement the A/D module. Maintain this register clear.

# TABLE 3-5 PORTC FUNCTIONS

| Name            | Bit# | Buffer<br>Type | Function                                                                    | TRISC<br>Override |

|-----------------|------|----------------|-----------------------------------------------------------------------------|-------------------|

| RC0/T1OSO/T1CKI | bit0 | ST             | Input/output port pin or Timer1 oscillator output/Timer1 clock input        | Yes               |

| RC1/T1OSI       | bit1 | ST             | Input/output port pin or Timer1 oscillator input                            | Yes               |

| RC2/CCP1        | bit2 | ST             | Input/output port pin or Capture1 input/Compare1 output/PWM1 output         | No                |

| RC3/SCK/SCL     | bit3 | ST             | RC3 can also be the synchronous serial clock for both SPI and $I^2C$ modes. | No                |

| RC4/SDI/SDA     | bit4 | ST             | RC4 can also be the SPI Data In (SPI mode) or data $I/O$ ( $I^2C$ mode).    | No                |

| RC5/SDO         | bit5 | ST             | Input/output port pin or Synchronous Serial Port data output                | No                |

| RC6             | bit6 | ST             | Input/output port pin                                                       | No                |

| RC7             | bit7 | ST             | Input/output port pin                                                       | No                |

Legend: ST = Schmitt Trigger input

# TABLE 3-6SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7   | Bit 6                                             | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|---------|---------------------------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 07h     | PORTC | RC7     | RC6                                               | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   | xxxx xxxx                | uuuu uuuu                 |

| 87h     | TRISC | PORTC I | PORTC Data Direction Register 1111 1111 1111 1111 |       |       |       |       |       |       | 1111 1111                |                           |

Legend: x = unknown, u = unchanged.

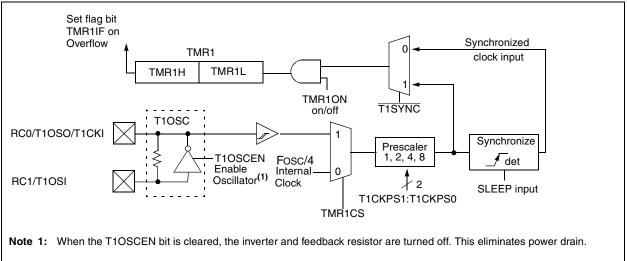

# FIGURE 5-1: TIMER1 BLOCK DIAGRAM

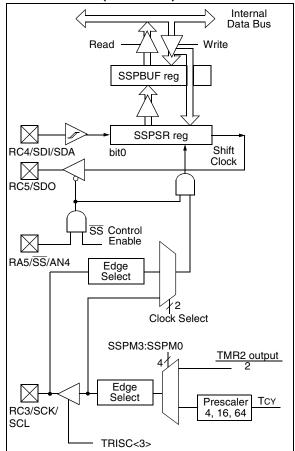

# 8.0 SYNCHRONOUS SERIAL PORT (SSP) MODULE

# 8.1 SSP Module Overview

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

For more information on SSP operation (including an I<sup>2</sup>C Overview), refer to the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023). Also, refer to Application Note AN578, *"Use of the SSP Module in the I<sup>2</sup>C Multi-Master Environment."*

# 8.2 SPI Mode

This section contains register definitions and operational characteristics of the SPI module.

Additional information on SPI operation may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

8.2.1 OPERATION OF SSP MODULE IN SPI MODE

A block diagram of the SSP Module in SPI Mode is shown in Figure 8-1.

The SPI mode allows 8-bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, three pins are used:

- Serial Data Out (SDO)RC5/SDO

- Serial Data In (SDI)RC4/SDI/SDA

- Serial Clock (SCK)RC3/SCK/SCL

Additionally, a fourth pin may be used when in a slave mode of operation:

Slave Select (SS)RA5/SS/AN4

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- Master Operation (SCK is the clock output)

- Slave Mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Clock Edge (Output data on rising/falling edge of SCK)

- Clock Rate (master operation only)

- Slave Select Mode (Slave mode only)

To enable the serial port, SSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON reg-

ister, and then set bit SSPEN. This configures the SDI, SDO, SCK and  $\overline{SS}$  pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISC register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (master operation) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set (if used)

Note: When the SPI is in Slave Mode with  $\overline{SS}$  pin control enabled, (SSPCON<3:0> = 0100) the SPI module will reset if the  $\overline{SS}$  pin is set to VDD.

**Note:** If the SPI is used in Slave Mode with CKE = '1', then the  $\overline{SS}$  pin control must be enabled.

## FIGURE 8-1: SSP BLOCK DIAGRAM (SPI MODE)

# 9.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 9.5TAD per 8-bit conversion. The source of the A/D conversion clock is software selectable. The four possible options for TAD are:

- 2Tosc

- 8Tosc

- 32Tosc

- Internal RC oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu s.$

The A/D module can operate during sleep mode, but the RC oscillator must be selected as the A/D clock source prior to the SLEEP instruction.

Table 9-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

# 9.3 Configuring Analog Port Pins

The ADCON1 and TRISA registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS2:CHS0 bits and the TRIS bits.

- Note 1: When reading the port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs, will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- **Note 2:** Analog levels on any pin that is defined as a digital input (including the AN4:AN0 pins) may cause the input buffer to consume current that is out of the devices specification.

# TABLE 9-1TAD vs. DEVICE OPERATING FREQUENCIES

| AD Cloc           | k Source (TAD) | Device Frequency          |                           |                           |                         |  |  |  |  |  |

|-------------------|----------------|---------------------------|---------------------------|---------------------------|-------------------------|--|--|--|--|--|

| Operation         | ADCS1:ADCS0    | 20 MHz                    | 5 MHz                     | 1.25 MHz                  | 333.33 kHz              |  |  |  |  |  |

| 2Tosc             | 00             | 100 ns <sup>(2)</sup>     | 400 ns <sup>(2)</sup>     | 1.6 μs                    | 6 μs                    |  |  |  |  |  |

| 8Tosc             | 01             | 400 ns <sup>(2)</sup>     | 1.6 μs                    | 6.4 μs                    | 24 μs <sup>(3)</sup>    |  |  |  |  |  |

| 32Tosc            | 10             | 1.6 μs                    | 6.4 μs                    | 25.6 μs <sup>(3)</sup>    | 96 μs <sup>(3)</sup>    |  |  |  |  |  |

| RC <sup>(5)</sup> | 11             | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1)</sup> |  |  |  |  |  |

Legend: Shaded cells are outside of recommended range.

Note 1: The RC source has a typical TAD time of 4  $\mu$ s.

- 2: These values violate the minimum required TAD time.

- **3:** For faster conversion times, the selection of another clock source is recommended.

- 4: When device frequency is greater than 1 MHz, the RC A/D conversion clock source is recommended for sleep operation only.

- 5: For extended voltage devices (LC), please refer to Electrical Specifications section.

# 10.0 SPECIAL FEATURES OF THE CPU

The PIC16C62B/72A devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Mode Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- ID locations

- In-circuit serial programming<sup>™</sup> (ICSP)

These devices have a Watchdog Timer, which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The

# FIGURE 10-1: CONFIGURATION WORD

other is the Power-up Timer (PWRT), which provides a fixed delay on power-up only and is designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

Additional information on special features is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

# 10.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

| CP1    | CP0                                                                                                                                                                                              | CP1                                                                                                                            | CP0   | CP1    | CP0    | _     | BODEN | CP1 | CP0 | PWRTE | WDTE | FOSC1 | FOSC0                      | Register:                    | CONFIG |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------|--------|--------|-------|-------|-----|-----|-------|------|-------|----------------------------|------------------------------|--------|

| bit13  |                                                                                                                                                                                                  | bito Address: 2007h                                                                                                            |       |        |        |       |       |     |     |       |      |       |                            |                              |        |

|        | <pre>it 13-8 CP1:CP0: Code Protection bits <sup>(2)</sup> 5-4: 11 = Code protection off 10 = Upper half of program memory code protected 01 = Upper 3/4th of program memory code protected</pre> |                                                                                                                                |       |        |        |       |       |     |     |       |      |       |                            |                              |        |

|        |                                                                                                                                                                                                  | 00 = AII                                                                                                                       |       |        |        |       |       |     |     |       |      |       |                            |                              |        |

| bit 7: | I                                                                                                                                                                                                | Jnimpl                                                                                                                         | emen  | ted: R | ead as | s '1' |       |     |     |       |      |       |                            |                              |        |

| bit 6: |                                                                                                                                                                                                  | BODEN: Brown-out Reset Enable bit <sup>(1)</sup><br>1 = BOR enabled<br>0 = BOR disabled                                        |       |        |        |       |       |     |     |       |      |       |                            |                              |        |

| bit 3: |                                                                                                                                                                                                  | <b>PWRTE</b> : Power-up Timer Enable bit <sup>(1)</sup><br>1 = PWRT disabled<br>0 = PWRT enabled                               |       |        |        |       |       |     |     |       |      |       |                            |                              |        |

| bit 2: | :                                                                                                                                                                                                | <b>WDTE</b> :<br>1 = WD<br>0 = WD                                                                                              | T ena | bled   | imer E | nable | bit   |     |     |       |      |       |                            |                              |        |

| bit 1- |                                                                                                                                                                                                  | FOSC1:FOSC0: Oscillator Selection bits<br>11 = RC oscillator<br>10 = HS oscillator<br>01 = XT oscillator<br>00 = LP oscillator |       |        |        |       |       |     |     |       |      |       |                            |                              |        |

| Note   |                                                                                                                                                                                                  |                                                                                                                                |       |        |        |       |       |     |     |       |      |       | dless of the<br>tion schem | e value of bit<br>ne listed. | PWRTE. |

# 10.4 Power-On Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.5V - 2.1V). To take advantage of the POR, just tie the  $\overline{\text{MCLR}}$  pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified (SVDD, parameter D004). For a slow rise time, see Figure 10-6.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met. Brown-out Reset may be used to meet the start-up conditions.

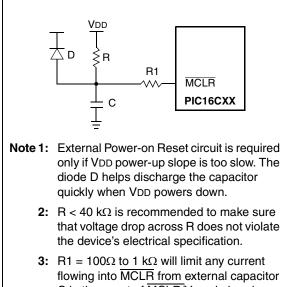

### FIGURE 10-6: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

#### R1 = 100Ω to 1 kΩ will limit any current flowing into $\overline{MCLR}$ from external capacitor C in the event of $\overline{MCLR}/VPP$ pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

# 10.5 Power-up Timer (PWRT)

The Power-up Timer provides a fixed nominal time-out (TPWRT, parameter #33) from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip-to-chip due to VDD, temperature and process variation. See DC parameters for details.

# 10.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a delay of 1024 oscillator cycles (from OSC1 input) after the PWRT delay is over (TOST, parameter #32). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

Note: The OST delay may not occur when the device wakes from SLEEP.

# 10.7 Brown-Out Reset (BOR)

The configuration bit, BODEN, can enable or disable the Brown-Out Reset circuit. If VPP falls below Vbor (parameter #35, about  $100\mu$ S), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a reset may not occur.

Once the brown-out occurs, the device will remain in brown-out reset until VDD rises above VBOR. The power-up timer then keeps the device in reset for TPWRT (parameter #33, about 72mS). If VDD should fall below VBOR during TPWRT, the brown-out reset process will restart when VDD rises above VBOR with the power-up timer reset. The power-up timer is always enabled when the brown-out reset circuit is enabled, regardless of the state of the PWRT configuration bit.

| TABLE 10-6 INITIALIZATION CONDITIONS FOR ALL REGISTERS |     |               |                                    |                          |                                 |  |  |  |  |

|--------------------------------------------------------|-----|---------------|------------------------------------|--------------------------|---------------------------------|--|--|--|--|

| Register                                               |     | cable<br>ices | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT or<br>Interrupt |  |  |  |  |

| W                                                      | 62B | 72A           | XXXX XXXX                          | uuuu uuuu                | սսսս սսսս                       |  |  |  |  |

| INDF                                                   | 62B | 72A           | N/A                                | N/A                      | N/A                             |  |  |  |  |

| TMR0                                                   | 62B | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |

| PCL                                                    | 62B | 72A           | 0000h                              | 0000h                    | PC + 1 <sup>(2)</sup>           |  |  |  |  |

| STATUS                                                 | 62B | 72A           | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu <b>(3)</b>            |  |  |  |  |

| FSR                                                    | 62B | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |

| PORTA <sup>(4)</sup>                                   | 62B | 72A           | 0x 0000                            | 0u 0000                  | uu uuuu                         |  |  |  |  |

| PORTB <sup>(5)</sup>                                   | 62B | 72A           | xxxx xxxx                          | սսսս սսսս                | սսսս սսսս                       |  |  |  |  |

| PORTC <sup>(5)</sup>                                   | 62B | 72A           | xxxx xxxx                          | սսսս սսսս                | uuuu uuuu                       |  |  |  |  |

| PCLATH                                                 | 62B | 72A           | 0 0000                             | 0 0000                   | u uuuu                          |  |  |  |  |

| INTCON                                                 | 62B | 72A           | 0000 000x                          | 0000 000u                | uuuu uuuu <b>(1)</b>            |  |  |  |  |

|                                                        | 62B | 72A           | 0000                               | 0000                     | uuuu <b>(1)</b>                 |  |  |  |  |

| PIR1                                                   | 62B | 72A           | -0 0000                            | -0 0000                  | -u uuuu <b>(1)</b>              |  |  |  |  |

| TMR1L                                                  | 62B | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |

| TMR1H                                                  | 62B | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |

| T1CON                                                  | 62B | 72A           | 00 0000                            | uu uuuu                  | uu uuuu                         |  |  |  |  |

| TMR2                                                   | 62B | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |  |  |

| T2CON                                                  | 62B | 72A           | -000 0000                          | -000 0000                | -uuu uuuu                       |  |  |  |  |

| SSPBUF                                                 | 62B | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |

| SSPCON                                                 | 62B | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |  |  |

| CCPR1L                                                 | 62B | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |

| CCPR1H                                                 | 62B | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |

| CCP1CON                                                | 62B | 72A           | 00 0000                            | 00 0000                  | uu uuuu                         |  |  |  |  |

| ADRES                                                  | 62B | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |

| ADCON0                                                 | 62B | 72A           | 0000 00-0                          | 0000 00-0                | uuuu uu-u                       |  |  |  |  |

| OPTION_REG                                             | 62B | 72A           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |  |  |  |  |

| TRISA                                                  | 62B | 72A           | 11 1111                            | 11 1111                  | uu uuuu                         |  |  |  |  |

| TRISB                                                  | 62B | 72A           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |  |  |  |  |

| TRISC                                                  | 62B | 72A           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |  |  |  |  |

| PIE1                                                   | 62B | 72A           | 0000                               | 0000                     | uuuu                            |  |  |  |  |

|                                                        | 62B | 72A           | -0 0000                            | -0 0000                  | -u uuuu                         |  |  |  |  |

| PCON                                                   | 62B | 72A           | 0q                                 | uq                       | uq                              |  |  |  |  |

| PR2                                                    | 62B | 72A           | 1111 1111                          | 1111 1111                | 1111 1111                       |  |  |  |  |

| SSPADD                                                 | 62B | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |  |  |

| SSPSTAT                                                | 62B | 72A           | 0000 0000                          | 0000 0000                | սսսս սսսս                       |  |  |  |  |

| ADCON1                                                 | 62B | 72A           | 000                                | 000                      | uuu                             |  |  |  |  |

| TABLE 10-6 | INITIALIZATION CONDITIONS FOR ALL REGISTERS |

|------------|---------------------------------------------|

|            |                                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', <math>q = value depends on condition

Note 1: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

**3:** See Table 10-5 for reset value for specific condition.

4: On any device reset, these pins are configured as inputs.

5: This is the value that will be in the port output latch.

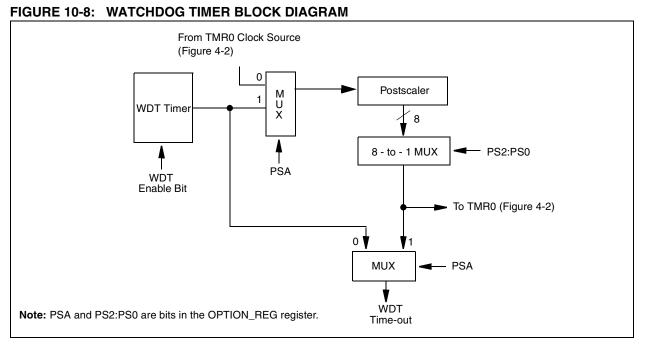

# 10.12 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. The WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit WDTE (Section 10.1).

The WDT time-out period (TWDT, parameter #31) is multiplied by the prescaler ratio, when the prescaler is assigned to the WDT. The prescaler assignment (assigned to either the WDT or Timer0) and prescaler ratio are set in the OPTION\_REG register.

Note: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

**Note:** When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

# FIGURE 10-9: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name         | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|--------------|-------|--------|-------|-------|-------|-------|-------|-------|

| 2007h   | Config. bits |       | BODEN  | CP1   | CP0   | PWRTE | WDTE  | FOSC1 | FOSC0 |

| 81h     | OPTION_REG   | RBPU  | INTEDG | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

# 11.1 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                       |

|------------------|-------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                |

| Operands:        | $0 \leq k \leq 255$                                                                                                     |

| Operation:       | $(W) + k \to (W)$                                                                                                       |

| Status Affected: | C, DC, Z                                                                                                                |

| Description:     | The contents of the W register are<br>added to the eight bit literal 'k' and the<br>result is placed in the W register. |

| ANDWF            | AND W with f                                                                                                                                                |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                             |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                   |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |

| Description:     | AND the W register with register 'f'. If<br>'d' is 0, the result is stored in the W<br>register. If 'd' is 1, the result is stored<br>back in register 'f'. |  |  |

| ADDWF            | Add W and f                                                                                                                                                                 |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                             |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                    |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result is<br>stored in the W register. If 'd' is 1, the<br>result is stored back in register 'f'. |  |  |

| BCF              | Bit Clear f                                                         |  |

|------------------|---------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] BCF f,b                                            |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |  |

| Operation:       | $0 \rightarrow (f < b >)$                                           |  |

| Status Affected: | None                                                                |  |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |  |

| ANDLW            | AND Literal with W                                                                                                  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                            |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                   |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                     |  |  |

| Status Affected: | Z                                                                                                                   |  |  |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal 'k'.<br>The result is placed in the W register. |  |  |

| BSF              | Bit Set f                                                           |  |

|------------------|---------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |  |

| Operation:       | $1 \rightarrow (f < b >)$                                           |  |

| Status Affected: | None                                                                |  |

| Description:     | Bit 'b' in register 'f' is set.                                     |  |

| IORLW            | Inclusive OR Literal with W                                                                                           |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ label ] IORLW k                                                                                                     |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                   |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                          |  |  |

| Status Affected: | Z                                                                                                                     |  |  |

| Description:     | The contents of the W register is<br>OR'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |  |  |

| MOVLW            | Move Literal to W                                                                          |  |  |

|------------------|--------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                   |  |  |

| Operands:        | $0 \le k \le 255$                                                                          |  |  |

| Operation:       | $k \rightarrow (W)$                                                                        |  |  |

| Status Affected: | None                                                                                       |  |  |

| Description:     | The eight bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                                  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] IORWF f,d                                                                                                                                                      |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                            |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                               |  |  |

| Status Affected: | Z                                                                                                                                                                      |  |  |

| Description:     | Inclusive OR the W register with regis-<br>ter 'f'. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>placed back in register 'f'. |  |  |

| MOVWF            | Move W to f                           |  |  |

|------------------|---------------------------------------|--|--|

| Syntax:          | [label] MOVWF f                       |  |  |

| Operands:        | $0 \le f \le 127$                     |  |  |

| Operation:       | $(W) \rightarrow (f)$                 |  |  |

| Status Affected: | None                                  |  |  |

| Description:     | Move data from W register to register |  |  |

| MOVF             | Move f                                                                                                                                                                                                                                                                                |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                             |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                           |  |  |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                                       |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                                     |  |  |

| Description:     | The contents of register f is moved to<br>a destination dependant upon the sta-<br>tus of d. If $d = 0$ , destination is W reg-<br>ister. If $d = 1$ , the destination is file<br>register f itself. $d = 1$ is useful to test a<br>file register since status flag Z is<br>affected. |  |  |

| No Operation  |

|---------------|

| [label] NOP   |

| None          |

| No operation  |

| None          |

| No operation. |

|               |

| RETFIE                  | Return from Interrupt       | RLF              | Rotate Left f through Carry                                                                                                                                                                                   |

|-------------------------|-----------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                 | [ label ] RETFIE            | Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                      |

| Operands:<br>Operation: | None $TOS \rightarrow PC$ , | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                             |

| -                       | $1 \rightarrow \text{GIE}$  | Operation:       | See description below                                                                                                                                                                                         |

| Status Affected:        | None                        | Status Affected: | С                                                                                                                                                                                                             |

|                         |                             | Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>stored back in register 'f'. |

| - | C 🚽 | Register f | ] |  |

|---|-----|------------|---|--|

|   |     |            |   |  |

| RETLW            | Return with Literal in W                                                                                                                                                            | RRF              | Rotate Right f through Carry                                                                                                                                                                                   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            | Syntax:          | [label] RRF f,d                                                                                                                                                                                                |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                   | Operands:        | $0 \leq f \leq 127$                                                                                                                                                                                            |

| Operation:       | $k \rightarrow (W);$                                                                                                                                                                |                  | d ∈ [0,1]                                                                                                                                                                                                      |

|                  | $TOS \rightarrow PC$                                                                                                                                                                | Operation:       | See description below                                                                                                                                                                                          |

| Status Affected: | None                                                                                                                                                                                | Status Affected: | С                                                                                                                                                                                                              |

| Description:     | The W register is loaded with the eight<br>bit literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a two cycle<br>instruction. | Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>placed back in register 'f'. |

|                  |                                                                                                                                                                                     |                  | C Register f                                                                                                                                                                                                   |

| RETURN           | Return from Subroutine                                                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETURN                                                                                                                                          |

| Operands:        | None                                                                                                                                                    |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                    |

| Status Affected: | None                                                                                                                                                    |

| Description:     | Return from subroutine. The stack is<br>POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a two cycle instruction. |

| SLEEP            |                                                                                                                                                                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                                                                             |

| Operands:        | None                                                                                                                                                                                                                                                                                      |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \ \text{prescaler}, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                                                                               |

| Status Affected: | TO, PD                                                                                                                                                                                                                                                                                    |

| Description:     | The power-down status bit, $\overline{\text{PD}}$ is<br>cleared. Time-out status bit, $\overline{\text{TO}}$ is<br>set. Watchdog Timer and its pres-<br>caler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped.<br>See Section 10.13 for more details. |

© 1998-2013 Microchip Technology Inc.

NOTES:

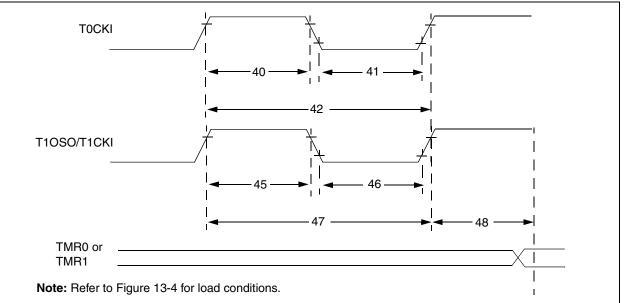

# FIGURE 13-9: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| TABLE 13-5: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|-------------|-----------------------------------------------|

| IADEE IV V. |                                               |

| Param<br>No. | Sym       |                                                 | Characteristic             |                | Min                                       | Тур† | Max   | Units | Conditions                         |

|--------------|-----------|-------------------------------------------------|----------------------------|----------------|-------------------------------------------|------|-------|-------|------------------------------------|

| 40*          | Tt0H      | T0CKI High Pulse W                              | ′idth                      | No Prescaler   | 0.5Tcy + 20                               | -    | -     | ns    | Must also meet                     |

|              |           |                                                 |                            | With Prescaler | 10                                        | -    |       | ns    | parameter 42                       |

| 41*          | Tt0L      | T0CKI Low Pulse W                               | idth                       | No Prescaler   | 0.5Tcy + 20                               | -    |       | ns    | Must also meet                     |

|              |           |                                                 |                            | With Prescaler | 10                                        | -    |       | ns    | parameter 42                       |

| 42*          | Tt0P      | T0CKI Period                                    |                            | No Prescaler   | Tcy + 40                                  | —    | -     | ns    |                                    |

|              |           | -                                               |                            | With Prescaler | Greater of:<br>20 or <u>Tcy + 40</u><br>N | -    | -     | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | Tt1H      | T1CKI High Time                                 | Synchronous, P             | rescaler = 1   | 0.5Tcy + 20                               | —    | -     | ns    | Must also meet                     |

|              |           |                                                 | Synchronous,               | PIC16CXX       | 15                                        | -    |       | ns    | parameter 47                       |

|              |           |                                                 | Prescaler = 2,4,8          | PIC16LCXX      | 25                                        | —    | _     | ns    | ]                                  |

|              |           |                                                 | Asynchronous               | PIC16CXX       | 30                                        |      | _     | ns    |                                    |

|              |           |                                                 |                            | PIC16LCXX      | 50                                        |      | _     | ns    |                                    |

| 46* Tt11     | Tt1L      | T1CKI Low Time                                  | Synchronous, Prescaler = 1 |                | 0.5TCY + 20                               | -    |       | ns    | Must also meet                     |

|              |           |                                                 | Synchronous,               | PIC16CXX       | 15                                        | —    | -     | ns    | parameter 47                       |

|              |           |                                                 | Prescaler = 2,4,8          | PIC16LCXX      | 25                                        | —    |       | ns    |                                    |

|              |           |                                                 | Asynchronous               | PIC16CXX       | 30                                        | -    |       | ns    |                                    |

|              |           |                                                 |                            | PIC16LCXX      | 50                                        | -    |       | ns    |                                    |

| 47* T        | Tt1P      | T1CKI input period                              | Synchronous                | PIC16CXX       | GREATER OF:<br>30 OR <u>TCY + 40</u><br>N | _    | _     | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                                                 |                            | PIC16LCXX      | GREATER OF:<br>50 OR <u>TCY + 40</u><br>N |      |       |       | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                                                 | Asynchronous               | PIC16CXX       | 60                                        | -    |       | ns    |                                    |

|              |           |                                                 |                            | PIC16LCXX      | 100                                       | —    | —     | ns    |                                    |

|              | Ft1       | Timer1 oscillator inp<br>(oscillator enabled by |                            |                | DC                                        | -    | 200   | kHz   |                                    |

| 48           | TCKEZtmr1 | Delay from external                             | clock edge to time         | er increment   | 2Tosc                                     |      | 7Tosc | -     |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

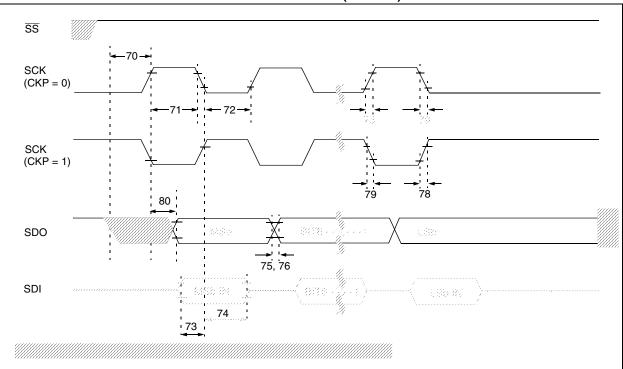

## FIGURE 13-11: EXAMPLE SPI MASTER MODE TIMING (CKE = 0)

| Param.<br>No. | Symbol                | Characteristic                            |             | Min          | Тур† | Max | Units  | Conditions |

|---------------|-----------------------|-------------------------------------------|-------------|--------------|------|-----|--------|------------|

| 70            | TssL2scH,<br>TssL2scL | SS↓ to SCK↓ or SCK↑ input                 | ut          | Тсү          | —    | —   | ns     |            |

| 71            | TscH                  | SCK input high time                       | Continuous  | 1.25Tcy + 30 | —    | _   | ns     |            |

| 71A           |                       | (slave mode)                              | Single Byte | 40           |      | _   | ns     | Note 1     |

| 72            | TscL                  | SCK input low time                        | Continuous  | 1.25Tcy + 30 | _    |     | ns     |            |

| 72A           |                       | (slave mode)                              | Single Byte | 40           | _    | _   | ns     | Note 1     |

| 73            | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge  |             | 100          | —    | —   | ns     |            |

| 73A           | Тв2в                  | Last clock edge of Byte1 to edge of Byte2 | 1.5Tcy + 40 | —            | —    | ns  | Note 1 |            |

| 74            | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge   |             | 100          | —    | —   | ns     |            |

| 75            | TdoR                  | SDO data output rise time                 | PIC16CXX    | _            | 10   | 25  | ns     |            |

|               |                       |                                           | PIC16LCXX   | _            | 20   | 45  | ns     |            |

| 76            | TdoF                  | SDO data output fall time                 |             | _            | 10   | 25  | ns     |            |

| 78            | TscR                  | SCK output rise time                      | PIC16CXX    | _            | 10   | 25  | ns     |            |

|               | (mas                  | (master mode)                             | PIC16LCXX   | _            | 20   | 45  | ns     |            |

| 79            | TscF                  | SCK output fall time (maste               | er mode)    | _            | 10   | 25  | ns     |            |

| 80            | TscH2doV,             | SDO data output valid                     | PIC16CXX    | _            | _    | 50  | ns     |            |

|               | TscL2doV              | after SCK edge                            | PIC16LCXX   | _            | —    | 100 | ns     | ]          |

### TABLE 13-7: EXAMPLE SPI MODE REQUIREMENTS (MASTER MODE, CKE = 0)

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Specification 73A is only required if specifications 71A and 72A are used.

© 1998-2013 Microchip Technology Inc.

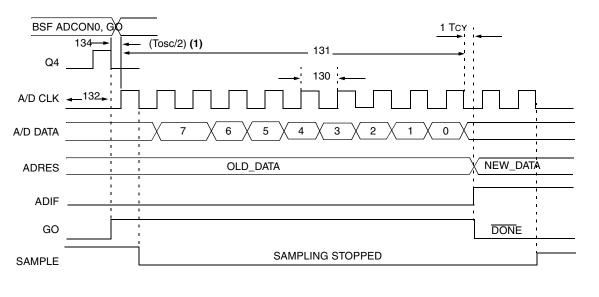

# FIGURE 13-17: A/D CONVERSION TIMING

**Note 1:** If the A/D clock source is selected as RC, a time of TCY is added before the A/D clock starts. This allows the SLEEP instruction to be executed.

| Param | Sym  | Characteristic                                    |                         | Min    | Typ†   | Max | Unit | Conditions                                                                                                                                                                                                                         |

|-------|------|---------------------------------------------------|-------------------------|--------|--------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.   |      |                                                   |                         |        |        |     | S    |                                                                                                                                                                                                                                    |

| 130   | TAD  | A/D clock period                                  | PIC16CXX                | 1.6    |        |     | μs   | Tosc based, VREF $\geq 3.0V$                                                                                                                                                                                                       |

|       |      |                                                   | PIC16LCXX               | 2.0    |        | -   | μs   | Tosc based, VREF full range                                                                                                                                                                                                        |

|       |      |                                                   | PIC16CXX                | 2.0    | 4.0    | 6.0 | μS   | A/D RC Mode                                                                                                                                                                                                                        |

|       |      |                                                   | PIC16LCXX               | 3.0    | 6.0    | 9.0 | μS   | A/D RC Mode                                                                                                                                                                                                                        |

| 131   | TCNV | Conversion time (not including S/H time) (Note 1) |                         | 11     |        | 11  | Tad  |                                                                                                                                                                                                                                    |

| 132   | TACQ | Acquisition time                                  |                         | Note 2 | 20     |     | μS   |                                                                                                                                                                                                                                    |

|       |      |                                                   |                         | 5*     | _      | _   | μs   | The minimum time is the<br>amplifier settling time. This<br>may be used if the "new" input<br>voltage has not changed by<br>more than 1 LSb (i.e., 20.0 mV<br>@ 5.12V) from the last sam-<br>pled voltage (as stated on<br>CHOLD). |

| 134   | TGO  | Q4 to A/D clock start                             |                         |        | Tosc/2 |     |      | If the A/D clock source is<br>selected as RC, a time of TCY<br>is added before the A/D clock<br>starts. This allows the SLEEP<br>instruction to be executed.                                                                       |

| 135   | Tswc | Switching from conve<br>time                      | $rt \rightarrow sample$ | 1.5    |        |     | Tad  |                                                                                                                                                                                                                                    |

# TABLE 13-14: A/D CONVERSION REQUIREMENTS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** ADRES register may be read on the following TCY cycle.

2: See Section 9.1 for min conditions.

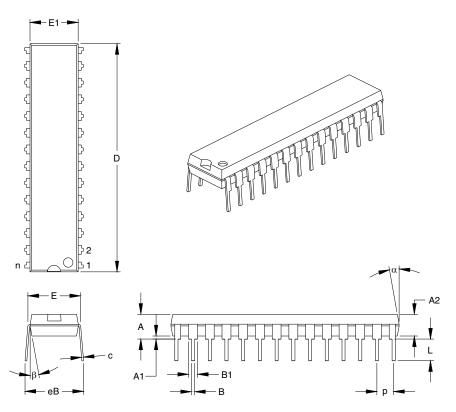

#### 28-Lead Skinny Plastic Dual In-line (SP) – 300 mil (PDIP) 15.2

|                            | INCHES* |       |       | MILLIMETERS |       |       |       |

|----------------------------|---------|-------|-------|-------------|-------|-------|-------|

| Dimension                  | Limits  | MIN   | NOM   | MAX         | MIN   | NOM   | MAX   |

| Number of Pins             | n       |       | 28    |             |       | 28    |       |

| Pitch                      | р       |       | .100  |             |       | 2.54  |       |

| Top to Seating Plane       | Α       | .140  | .150  | .160        | 3.56  | 3.81  | 4.06  |

| Molded Package Thickness   | A2      | .125  | .130  | .135        | 3.18  | 3.30  | 3.43  |

| Base to Seating Plane      | A1      | .015  |       |             | 0.38  |       |       |

| Shoulder to Shoulder Width | E       | .300  | .313  | .325        | 7.62  | 7.94  | 8.26  |

| Molded Package Width       | E1      | .279  | .307  | .335        | 7.09  | 7.80  | 8.51  |

| Overall Length             | D       | 1.345 | 1.365 | 1.385       | 34.16 | 34.67 | 35.18 |

| Tip to Seating Plane       | L       | .125  | .130  | .135        | 3.18  | 3.30  | 3.43  |

| Lead Thickness             | С       | .008  | .012  | .015        | 0.20  | 0.29  | 0.38  |

| Upper Lead Width           | B1      | .040  | .053  | .065        | 1.02  | 1.33  | 1.65  |

| Lower Lead Width           | В       | .016  | .019  | .022        | 0.41  | 0.48  | 0.56  |

| Overall Row Spacing        | eB      | .320  | .350  | .430        | 8.13  | 8.89  | 10.92 |

| Mold Draft Angle Top       | α       | 5     | 10    | 15          | 5     | 10    | 15    |

| Mold Draft Angle Bottom    | β       | 5     | 10    | 15          | 5     | 10    | 15    |

\*Controlling Parameter

Notes: Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-095 Drawing No. C04-070

# INDEX

# Α

| A/D  |                                             |    |       | 49 |

|------|---------------------------------------------|----|-------|----|

|      | A/D Converter Enable (ADIE Bit)             |    |       | 14 |

|      | A/D Converter Flag (ADIF Bit)               |    |       |    |

|      | A/D Converter Interrupt, Configuring        |    |       |    |

|      | ADCON0 Register                             |    |       |    |

|      | ADCON1 Register10                           |    |       |    |

|      | ADRES Register                              |    |       |    |

|      | Analog Port Pins                            |    | ····. | 6  |

|      | Analog Port Pins, Configuring               |    |       |    |

|      | Block Diagram                               |    |       |    |

|      | Block Diagram, Analog Input Model           |    |       |    |

|      | Channel Select (CHS2:CHS0 Bits)             |    |       |    |

|      | Clock Select (ADCS1:ADCS0 Bits)             |    |       |    |

|      | Configuring the Module                      |    |       |    |

|      | Conversion Clock (TAD)                      |    |       |    |

|      | Conversion Status (GO/DONE Bit)             |    |       |    |

|      | Conversions                                 |    |       |    |

|      | Converter Characteristics                   |    | 1     | 01 |

|      | Module On/Off (ADON Bit)                    |    |       |    |

|      | Port Configuration Control (PCFG2:PCFG0 Bit | s) |       | 50 |

|      | Sampling Requirements                       |    |       |    |

|      | Special Event Trigger (CCP)                 |    | 35,   | 54 |

|      | Timing Diagram                              |    | Í     | 02 |

| Abso | blute Maximum Ratings                       |    |       |    |

| ADC  | ON0 Register                                |    | . 9,  | 49 |

|      | ADCS1:ADCS0 Bits                            |    |       |    |

|      | ADON Bit                                    |    |       | 49 |

|      | CHS2:CHS0 Bits                              |    |       | 49 |

|      | GO/DONE Bit                                 |    | 49,   | 51 |

| ADC  | ON1 Register10                              | 0, | 49,   | 50 |

|      | PCFG2:PCFG0 Bits                            |    |       | 50 |

| ADR  | ES Register                                 |    |       |    |

|      | itecture                                    |    |       |    |

|      | PIC16C62B/PIC16C72A Block Diagram           |    |       | 5  |

| Asse | embler                                      |    |       |    |

|      | MPASM Assembler                             |    |       | 75 |

| в    |                                             |    |       |    |

| D    |                                             |    |       |    |

|  |   | ١. |

|--|---|----|

|  | 1 |    |

|  |   |    |

|  |   |    |

| Banking, Data Memory   |  |

|------------------------|--|

| Brown-out Reset (BOR)  |  |

| BOR Enable (BODEN Bit) |  |

| BOR Status (BOR Bit)   |  |

|                        |  |

# С

| Capture (CCP Module)                |    |

|-------------------------------------|----|