Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I²C, SPI                                                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c62bt-20-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

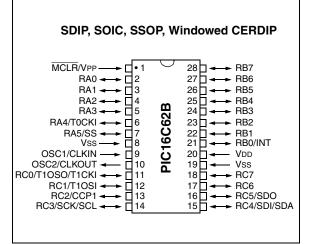

## **Pin Diagrams**

| Key Features<br>PIC <sup>®</sup> Mid-Range Reference Manual (DS33023) | PIC16C62B            | PIC16C72A            |

|-----------------------------------------------------------------------|----------------------|----------------------|

| Operating Frequency                                                   | DC - 20 MHz          | DC - 20 MHz          |

| Resets (and Delays)                                                   | POR, BOR (PWRT, OST) | POR, BOR (PWRT, OST) |

| Program Memory (14-bit words)                                         | 2K                   | 2K                   |

| Data Memory (bytes)                                                   | 128                  | 128                  |

| Interrupts                                                            | 7                    | 8                    |

| I/O Ports                                                             | Ports A,B,C          | Ports A,B,C          |

| Timers                                                                | 3                    | 3                    |

| Capture/Compare/PWM modules                                           | 1                    | 1                    |

| Serial Communications                                                 | SSP                  | SSP                  |

| 8-bit Analog-to-Digital Module                                        | —                    | 5 input channels     |

# PIC16C62B/72A

#### 2.2.2.4 PIE1 REGISTER

This register contains the individual enable bits for the peripheral interrupts.

## REGISTER 2-4: PIE1 REGISTER (ADDRESS 8Ch)

#### R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 U-0 U-0 U-0 ADIE<sup>(1)</sup> SSPIE CCP1IE TMR2IE TMR1IE R = Readable bit W = Writable bit bit7 bit0 U = Unimplemented bit, read as '0' n = Value at POR reset Unimplemented: Read as '0' bit 7: ADIE<sup>(1)</sup>: A/D Converter Interrupt Enable bit bit 6: 1 = Enables the A/D interrupt 0 = Disables the A/D interrupt bit 5-4: Unimplemented: Read as '0' bit 3: SSPIE: Synchronous Serial Port Interrupt Enable bit 1 = Enables the SSP interrupt 0 = Disables the SSP interrupt CCP1IE: CCP1 Interrupt Enable bit bit 2: 1 = Enables the CCP1 interrupt 0 = Disables the CCP1 interrupt TMR2IE: TMR2 to PR2 Match Interrupt Enable bit bit 1: 1 = Enables the TMR2 to PR2 match interrupt 0 = Disables the TMR2 to PR2 match interrupt TMR1IE: TMR1 Overflow Interrupt Enable bit bit 0: 1 = Enables the TMR1 overflow interrupt 0 = Disables the TMR1 overflow interrupt Note 1: The PIC16C62B does not have an A/D module. This bit location is reserved on these devices. Always maintain this bit clear.

#### Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

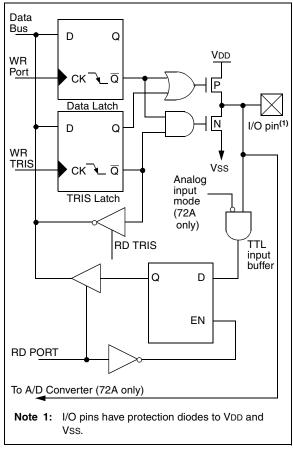

## 3.0 I/O PORTS

Some I/O port pins are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

## 3.1 PORTA and the TRISA Register

PORTA is a 6-bit wide bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (=1) will make the corresponding PORTA pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISA bit (=0) will make the corresponding PORTA pin an output, (i.e., put the contents of the output latch on the selected pin).

The PORTA register reads the state of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

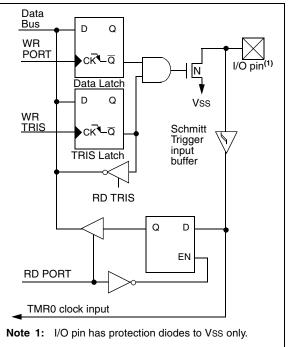

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers.

Pin RA5 is multiplexed with the SSP to become the RA5/SS pin.

On the PIC16C72A device, other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

| Note: | On a Power-on Reset, pins with analog           |  |  |  |  |  |

|-------|-------------------------------------------------|--|--|--|--|--|

|       | functions are configured as analog inputs       |  |  |  |  |  |

|       | with digital input buffers disabled . A digital |  |  |  |  |  |

|       | read of these pins will return '0'.             |  |  |  |  |  |

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

### FIGURE 3-1: BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

### FIGURE 3-2: BLOCK DIAGRAM OF RA4/T0CKI PIN

© 1998-2013 Microchip Technology Inc.

## TABLE 3-1 PORTA FUNCTIONS

| Name         | Bit# | Buffer | Function                                                                                      |

|--------------|------|--------|-----------------------------------------------------------------------------------------------|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input <sup>(1)</sup>                                                   |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input <sup>(1)</sup>                                                   |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input <sup>(1)</sup>                                                   |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input <sup>(1)</sup> or VREF <sup>(1)</sup>                            |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0<br>Output is open drain type                  |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input <sup>(1)</sup> |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: The PIC16C62B does not implement the A/D module.

## TABLE 3-2 SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name                          | Bit 7 | Bit 6 | Bit 5 | Bit 4                         | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on all other resets |

|---------|-------------------------------|-------|-------|-------|-------------------------------|-------|-------|-------|-------|-------------------------|---------------------------|

| 05h     | PORTA<br>(for PIC16C72A only) | —     | —     | RA5   | RA4                           | RA3   | RA2   | RA1   | RA0   | 0x 0000                 | 0u 0000                   |

| 05h     | PORTA<br>(for PIC16C62B only) | —     | —     | RA5   | RA4                           | RA3   | RA2   | RA1   | RA0   | xx xxxx                 | uu uuuu                   |

| 85h     | TRISA                         |       |       | PORTA | PORTA Data Direction Register |       |       |       |       | 11 1111                 | 11 1111                   |

| 9Fh     | ADCON1 <sup>(1)</sup>         |       |       |       |                               |       | PCFG2 | PCFG1 | PCFG0 | 000                     | 000                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA. Note 1: The PIC16C62B does not implement the A/D module. Maintain this register clear.

| TABLE 3-3 | PORTB FUNCTIONS |

|-----------|-----------------|

| IADLE 3-3 | PURID FUNCTIONS |

| Name    | Bit# | Buffer                | Function                                                                                                               |

|---------|------|-----------------------|------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input.<br>Internal software programmable weak pull-up.                          |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB3     | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt on change).<br>Internal software programmable weak pull-up.                           |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt on change).<br>Internal software programmable weak pull-up.                           |

| RB6     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change).<br>Internal software programmable weak pull-up. Serial programming clock. |

| RB7     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change).<br>Internal software programmable weak pull-up. Serial programming data.  |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

#### TABLE 3-4 SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address | Name       | Bit 7                                                                                         | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|------------|-----------------------------------------------------------------------------------------------|-------------------------------|-------|-------|-------|-------|-------|-----------|--------------------------|---------------------------|

| 06h     | PORTB      | RB7                                                                                           | RB6                           | RB5   | RB4   | RB3   | RB2   | RB1   | RB0       | xxxx xxxx                | uuuu uuuu                 |

| 86h     | TRISB      | PORTB I                                                                                       | PORTB Data Direction Register |       |       |       |       |       |           |                          | 1111 1111                 |

| 81h     | OPTION_REG | RBPU         INTEDG         TOCS         TOSE         PSA         PS2         PS1         PS0 |                               |       |       |       |       |       | 1111 1111 | 1111 1111                |                           |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

NOTES:

## 6.1 <u>Timer2 Operation</u>

The Timer2 output is also used by the CCP module to generate the PWM "On-Time", and the PWM period with a match with PR2.

The TMR2 register is readable and writable, and is cleared on any device reset.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device reset (Power-on Reset, MCLR reset, Watchdog Timer reset or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

## 6.2 <u>Timer2 Interrupt</u>

The Timer2 module has an 8-bit period register PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon reset.

## 6.3 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module, which optionally uses it to generate shift clock.

## TABLE 6-1 REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Address | Name                       | Bit 7      | Bit 6          | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|----------------------------|------------|----------------|---------|---------|---------|--------|---------|---------|-------------------------|---------------------------------|

| 0Bh,8Bh | INTCON                     | GIE        | PEIE           | TOIE    | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x               | 0000 000u                       |

| 0Ch     | PIR1                       | _          | ADIF           | _       | _       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | -00- 0000               | 0000 0000                       |

| 8Ch     | PIE1                       | _          | ADIE           | _       | _       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | -0 0000                 | 0000 0000                       |

| 11h     | TMR2                       | Timer2 mod | dule's registe | r       |         |         |        |         |         | 0000 0000               | 0000 0000                       |

| 12h     | T2CON                      | _          | TOUTPS3        | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000               | -000 0000                       |

| 92h     | PR2 Timer2 Period Register |            |                |         |         |         |        |         |         | 1111 1111               | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

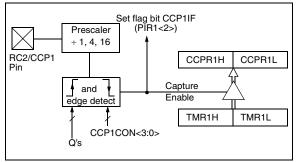

## 7.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register, when an event occurs on pin RC2/CCP1. An event is defined as:

- every falling edge

- · every rising edge

- every 4th rising edge

- every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit ,CCP1IF (PIR1<2>), is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### FIGURE 7-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 7.1.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

**Note:** If the RC2/CCP1 is configured as an output, a write to the port can cause a capture condition.

#### 7.1.2 TIMER1 MODE SELECTION

Timer1 must be running in timer mode or synchronized counter mode for the CCP module to use the capture feature. In asynchronous counter mode, the capture operation may not work consistently.

#### 7.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should clear CCP1IE (PIE1<2>) before changing the capture mode to avoid false interrupts. Clear the interrupt flag bit, CCP1IE before setting CCP1IE.

## 7.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in capture mode, the prescaler counter is cleared. This means that any reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 7-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

## EXAMPLE 7-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;Turn CCP module off    |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | ;Load the W reg with    |

|       |             | ; the new prescaler     |

|       |             | ; mode value and CCP ON |

| MOVWF | CCP1CON     | ;Load CCP1CON with this |

|       |             | ; value                 |

## REGISTER 8-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94h)

| R/W-0  | R/W-0                                                                                                                                                | R-0                                                                                         | R-0                      | R-0                                                        | R-0                                              | R-0           | R-0         |                                                                                      |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------|------------------------------------------------------------|--------------------------------------------------|---------------|-------------|--------------------------------------------------------------------------------------|

| SMP    | CKE                                                                                                                                                  | D/A                                                                                         | Р                        | S                                                          | R/W                                              | UA            | BF          | R = Readable bit                                                                     |

| bit7   |                                                                                                                                                      |                                                                                             |                          |                                                            |                                                  |               | bit0        | W = Writable bit<br>U = Unimplemented bit, read<br>as '0'<br>- n =Value at POR reset |

| bit 7: | $\frac{\text{SPI Ma}}{1 = \text{Inpl}}$ $0 = \text{Inpl}$ $\frac{\text{SPI Sla}}{\text{SMP m}}$ $\frac{l^2 C \text{ Mod}}{l^2 C \text{ Mod}}$        | <u>ister Oper</u><br>ut data sa<br>ut data sa<br><u>uve Mode</u><br>ust be cle<br><u>de</u> | ampled at<br>ampled at   | end of data<br>middle of d<br>n SPI is us                  | i output time<br>ata output tii<br>ed in slave n | me            |             |                                                                                      |

| bit 6: | $\frac{\text{SPI Mo}}{\text{CKP} =}$ $1 = \text{Dat}$ $0 = \text{Dat}$ $1 = \text{Dat}$ $0 = \text{Dat}$ $\frac{1^2 \text{C Mos}}{1^2 \text{C Mos}}$ | <u>de</u><br>0<br>ta transmi<br>ta transmi<br>ta transmi<br>ta transmi<br><u>de</u>         | tted on fa<br>tted on fa | sing edge o<br>Iling edge c<br>Iling edge c<br>sing edge o | of SCK<br>of SCK                                 |               |             |                                                                                      |

| bit 5: | 1 = Indi                                                                                                                                             | icates tha                                                                                  | t the last l             |                                                            | r)<br>ed or transm<br>ed or transm               |               |             |                                                                                      |

| bit 4: | detecte<br>1 = Indi                                                                                                                                  | d last, SS<br>icates tha                                                                    | SPEN is cl               | eared)<br>it has been                                      | cleared whe                                      |               |             | disabled, or when the Start bit<br>ET)                                               |

| bit 3: | detecte<br>1 = Indi                                                                                                                                  | d last, SS<br>icates tha                                                                    | SPEN is cl               | eared)<br>it has been                                      | cleared who                                      |               |             | disabled, or when the Stop bit<br>ET)                                                |

| bit 2: | This bit                                                                                                                                             | t holds th<br>s match to<br>ad                                                              | e R/W bi                 |                                                            |                                                  |               | dress match | n. This bit is only valid from th                                                    |

| bit 1: | 1 = Indi                                                                                                                                             | icates tha                                                                                  | t the user               | it I <sup>2</sup> C mode<br>needs to u<br>d to be upd      | pdate the ac                                     | ldress in the | e SSPADD i  | register                                                                             |

| bit 0: | BF: But                                                                                                                                              | ffer Full S                                                                                 | tatus bit                |                                                            |                                                  |               |             |                                                                                      |

|        | 1 = Red<br>0 = Red                                                                                                                                   | ceive com<br>ceive not                                                                      | complete,                | es)<br>PBUF is ful<br>SSPBUF is                            |                                                  |               |             |                                                                                      |

|        | 1 = Tra                                                                                                                                              |                                                                                             | rogress, S               | SPBUF is<br>PBUF is er                                     |                                                  |               |             |                                                                                      |

NOTES:

## 10.2 Oscillator Configurations

#### 10.2.1 OSCILLATOR TYPES

The PIC16CXXX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

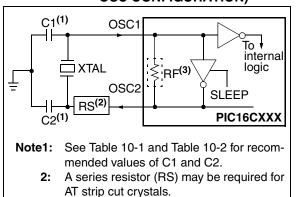

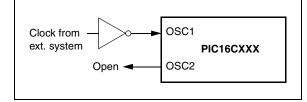

## 10.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 10-2). The PIC16CXXX oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can use an external clock source to drive the OSC1/CLKIN pin (Figure 10-3).

#### FIGURE 10-2: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

3: RF varies with the crystal chosen.

#### FIGURE 10-3: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

## TABLE 10-1 CERAMIC RESONATORS

## Ranges Tested:

| Ranges Tested: |                                                                         |                              |              |  |  |  |  |  |

|----------------|-------------------------------------------------------------------------|------------------------------|--------------|--|--|--|--|--|

| Mode           | Freq OSC1 OSC2                                                          |                              |              |  |  |  |  |  |

| XT             | 455 kHz                                                                 | 68 - 100 pF                  | 68 - 100 pF  |  |  |  |  |  |

|                | 2.0 MHz                                                                 | 15 - 68 pF 🛛 <               | 15 - 68 pF   |  |  |  |  |  |

|                | 4.0 MHz                                                                 | 15 - 68 pF                   | ∖15, - 68 pF |  |  |  |  |  |

| HS             | 8.0 MHz                                                                 | 10 - 68(pF                   | े10 - 68 pF  |  |  |  |  |  |

|                | 16.0 MHz                                                                | 10,-22,0F                    | 10 - 22 pF   |  |  |  |  |  |

|                | These values are for design guidance only. See notes at bottom of gage. |                              |              |  |  |  |  |  |

| Resonator      | rs Used: 🔨                                                              | Par -                        |              |  |  |  |  |  |

| 455 kHz        | Panasonie E                                                             | FO-A455K04B                  | ± 0.3%       |  |  |  |  |  |

| 2.0 MHz        | Murata Érie (                                                           | CSA2.00MG                    | $\pm 0.5\%$  |  |  |  |  |  |

| 4.0 MHz        | Murata Erie (                                                           | Murata Erie CSA4.00MG ± 0.5% |              |  |  |  |  |  |

| 8.0 MAHZ       | Murata Erie CSA8.00MT ± 0.5%                                            |                              |              |  |  |  |  |  |

| 16.0 MHz       | Murata Erie CSA16.00MX ± 0.5%                                           |                              |              |  |  |  |  |  |

| Resona         | ators did not hav                                                       | ve built-in capacito         | ors.         |  |  |  |  |  |

## TABLE 10-2CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq                                                         | Cap. Range<br>C1 | Cap. Range<br>C2 |  |  |  |  |

|----------|-------------------------------------------------------------------------|------------------|------------------|--|--|--|--|

| LP       | 32 kHz                                                                  | 33 pF            | 33 pF            |  |  |  |  |

|          | 200 kHz                                                                 | 15 pF            | 15 pF            |  |  |  |  |

| XT       | 200 kHz                                                                 | 47-68 pF         | 47-68 pF         |  |  |  |  |

|          | 1 MHz                                                                   | 15 pF 🔍          | ↓15.pF<br>15.pF  |  |  |  |  |

|          | 4 MHz                                                                   | 15 pF 🕟          | ∕∕15 pF          |  |  |  |  |

| HS       | 4 MHz                                                                   | 15 pt            | ✓ 15 pF          |  |  |  |  |

|          | 8 MHz                                                                   | 15-33 pE>        | 15-33 pF         |  |  |  |  |

|          | 20 MHz                                                                  | (15-33 pF        | 15-33 pF         |  |  |  |  |

|          | These values are for design guidance only. See notes at bottom of page. |                  |                  |  |  |  |  |

|          | Crystals Used                                                           |                  |                  |  |  |  |  |

| 32 kHz   | Epson C-001R32.768K-A ± 20 PPM                                          |                  |                  |  |  |  |  |

| 200 kt/2 | 970 XTL 200.000KHz ± 20 PPM                                             |                  |                  |  |  |  |  |

| 1 MHz    | ECS ECS-10-13-1 ± 50 PPM                                                |                  |                  |  |  |  |  |

| 4 MHz    | ECS ECS-40-20-1 ± 50 PPM                                                |                  |                  |  |  |  |  |

| 8 MHz    | EPSON CA-301 8.000M-C ± 30 PPM                                          |                  |                  |  |  |  |  |

**Note 1:** Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

EPSON CA-301 20.000M-C

20 MHz

2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

± 30 PPM

- **3:** Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- 4: Oscillator performance should be verified when migrating between devices (including PIC16C62A to PIC16C62B and PIC16C72 to PIC16C72A)

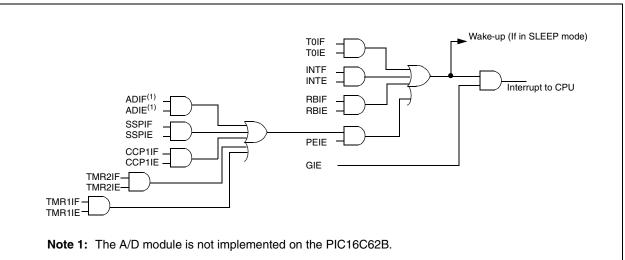

### 10.10 Interrupts

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set regard- |

|-------|------------------------------------------------|

|       | less of the status of their corresponding      |

|       | mask bit or the GIE bit.                       |

A global interrupt enable bit, GIE (INTCON<7>) enables or disables all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt flag bits are set regardless of the status of the GIE bit. The GIE bit is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit, which reenables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register. The peripheral interrupt flags are contained in the special function registers PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupts, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine, the source of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles, depending on when the interrupt event occurs. The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit

#### FIGURE 10-7: INTERRUPT LOGIC

### 10.13 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D and disable external clocks. Pull all I/O pins that are hi-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC, parameter D042).

#### 10.13.1 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- 1. External reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change, or some Peripheral Interrupts.

External  $\overline{\text{MCLR}}$  Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from SLEEP:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. CCP capture mode interrupt.

- 3. Special event trigger (Timer1 in asynchronous mode using an external clock. CCP1 is in compare mode).

- 4. SSP (Start/Stop) bit detect interrupt.

- 5. SSP transmit or receive in slave mode (SPI/I<sup>2</sup>C).

- 6. USART RX or TX (synchronous slave mode).

Other peripherals cannot generate interrupts since during SLEEP, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is

regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device resumes execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, a NOP should follow the SLEEP instruction.

#### 10.13.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

<sup>© 1998-2013</sup> Microchip Technology Inc.

# PIC16C62B/72A

NOTES:

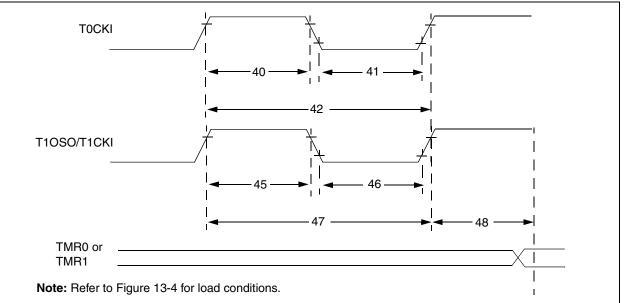

## FIGURE 13-9: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| TABLE 13-5: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|-------------|-----------------------------------------------|

| IADEE IV V. |                                               |

| Param<br>No. | Sym       |                                                   | Characteristic                               |                | Min                                       | Тур† | Max   | Units | Conditions                         |

|--------------|-----------|---------------------------------------------------|----------------------------------------------|----------------|-------------------------------------------|------|-------|-------|------------------------------------|

| 40* Tt0H     |           | T0CKI High Pulse W                                | ′idth                                        | No Prescaler   | 0.5Tcy + 20                               | -    | -     | ns    | Must also meet                     |

|              |           |                                                   |                                              | With Prescaler | 10                                        | -    |       | ns    | parameter 42                       |

| 41*          | Tt0L      | T0CKI Low Pulse W                                 | idth                                         | No Prescaler   | 0.5TCY + 20                               | -    |       | ns    | Must also meet                     |

|              |           |                                                   |                                              |                | 10                                        | -    |       | ns    | parameter 42                       |

| 42*          | Tt0P      | T0CKI Period                                      |                                              | No Prescaler   | Tcy + 40                                  | —    | -     | ns    |                                    |

|              |           | -                                                 |                                              | With Prescaler | Greater of:<br>20 or <u>Tcy + 40</u><br>N | -    | -     | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | Tt1H      | T1CKI High Time                                   | Synchronous, P                               | rescaler = 1   | 0.5Tcy + 20                               | —    | -     | ns    | Must also meet                     |

|              |           |                                                   | Synchronous,<br>Prescaler =<br>2,4,8         | PIC16CXX       | 15                                        | -    |       | ns    | parameter 47                       |

|              |           |                                                   |                                              | PIC16LCXX      | 25                                        | —    | _     | ns    |                                    |

|              |           |                                                   | Asynchronous                                 | PIC16CXX       | 30                                        |      | _     | ns    |                                    |

|              |           |                                                   |                                              | PIC16LCXX      | 50                                        |      | _     | ns    |                                    |

| 46*          | Tt1L      | t1L T1CKI Low Time                                | Synchronous, Prescaler = 1                   |                | 0.5Tcy + 20                               | -    |       | ns    | Must also meet                     |

|              |           |                                                   | Synchronous,<br>Prescaler =<br>2,4,8         | PIC16CXX       | 15                                        | —    | -     | ns    | parameter 47                       |

|              |           |                                                   |                                              | PIC16LCXX      | 25                                        | —    |       | ns    |                                    |

|              |           |                                                   | Asynchronous                                 | PIC16CXX       | 30                                        | -    |       | ns    |                                    |

|              |           |                                                   |                                              | PIC16LCXX      | 50                                        | -    |       | ns    |                                    |

| 47*          | Tt1P      | Tt1P T1CKI input period                           | Synchronous                                  | PIC16CXX       | GREATER OF:<br>30 OR <u>TCY + 40</u><br>N | -    | -     | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                                                   |                                              | PIC16LCXX      | GREATER OF:<br>50 OR <u>TCY + 40</u><br>N |      |       |       | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                                                   | Asynchronous                                 | PIC16CXX       | 60                                        | _    | —     | ns    |                                    |

|              |           |                                                   |                                              | PIC16LCXX      | 100                                       | —    | —     | ns    |                                    |

|              | Ft1       | Timer1 oscillator inp<br>(oscillator enabled by   | ut frequency range<br>y setting bit T1OSCEN) |                | DC                                        | -    | 200   | kHz   |                                    |

| 48           | TCKEZtmr1 | Delay from external clock edge to timer increment |                                              |                | 2Tosc                                     |      | 7Tosc | _     |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

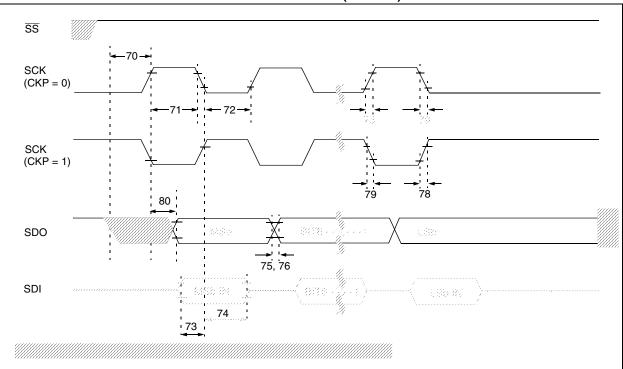

#### FIGURE 13-11: EXAMPLE SPI MASTER MODE TIMING (CKE = 0)

| Param.<br>No. | Symbol                | Characterist                              | Min         | Тур†         | Max | Units | Conditions |        |

|---------------|-----------------------|-------------------------------------------|-------------|--------------|-----|-------|------------|--------|

| 70            | TssL2scH,<br>TssL2scL | SS↓ to SCK↓ or SCK↑ input                 |             | Тсү          | —   | —     | ns         |        |

| 71            | TscH                  | SCK input high time                       | Continuous  | 1.25Tcy + 30 | —   | _     | ns         |        |

| 71A           |                       | (slave mode)                              | Single Byte | 40           |     | _     | ns         | Note 1 |

| 72            | TscL                  | SCK input low time                        | Continuous  | 1.25Tcy + 30 | —   |       | ns         |        |

| 72A           |                       | (slave mode)                              | Single Byte | 40           | _   | _     | ns         | Note 1 |

| 73            | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge  |             | 100          | —   | —     | ns         |        |

| 73A           | Тв2в                  | Last clock edge of Byte1 to edge of Byte2 | 1.5Tcy + 40 | —            | —   | ns    | Note 1     |        |

| 74            | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge   |             | 100          | —   | —     | ns         |        |

| 75            | TdoR                  | SDO data output rise time                 | PIC16CXX    | _            | 10  | 25    | ns         |        |

|               |                       |                                           | PIC16LCXX   | _            | 20  | 45    | ns         |        |

| 76            | TdoF                  | SDO data output fall time                 |             | _            | 10  | 25    | ns         |        |

| 78 T          | TscR                  | SCK output rise time                      | PIC16CXX    | _            | 10  | 25    | ns         |        |

|               |                       | (master mode)                             | PIC16LCXX   | _            | 20  | 45    | ns         |        |

| 79            | TscF                  | SCK output fall time (master mode)        |             | _            | 10  | 25    | ns         |        |

| 80            | TscH2doV,             | SDO data output valid                     | PIC16CXX    | _            | _   | 50    | ns         |        |

|               | TscL2doV              | after SCK edge                            | PIC16LCXX   | _            | —   | 100   | ns         | ]      |

#### TABLE 13-7: EXAMPLE SPI MODE REQUIREMENTS (MASTER MODE, CKE = 0)

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Specification 73A is only required if specifications 71A and 72A are used.

© 1998-2013 Microchip Technology Inc.

NOTES:

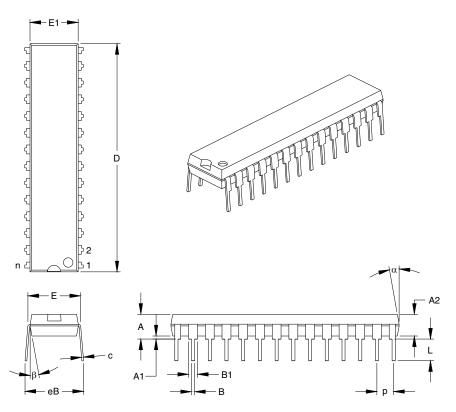

#### 28-Lead Skinny Plastic Dual In-line (SP) – 300 mil (PDIP) 15.2

|                            | INCHES* |       |       | MILLIMETERS |       |       |       |

|----------------------------|---------|-------|-------|-------------|-------|-------|-------|

| Dimension                  | Limits  | MIN   | NOM   | MAX         | MIN   | NOM   | MAX   |

| Number of Pins             | n       |       | 28    |             |       | 28    |       |

| Pitch                      | р       |       | .100  |             |       | 2.54  |       |

| Top to Seating Plane       | Α       | .140  | .150  | .160        | 3.56  | 3.81  | 4.06  |

| Molded Package Thickness   | A2      | .125  | .130  | .135        | 3.18  | 3.30  | 3.43  |

| Base to Seating Plane      | A1      | .015  |       |             | 0.38  |       |       |

| Shoulder to Shoulder Width | E       | .300  | .313  | .325        | 7.62  | 7.94  | 8.26  |

| Molded Package Width       | E1      | .279  | .307  | .335        | 7.09  | 7.80  | 8.51  |

| Overall Length             | D       | 1.345 | 1.365 | 1.385       | 34.16 | 34.67 | 35.18 |

| Tip to Seating Plane       | L       | .125  | .130  | .135        | 3.18  | 3.30  | 3.43  |

| Lead Thickness             | С       | .008  | .012  | .015        | 0.20  | 0.29  | 0.38  |

| Upper Lead Width           | B1      | .040  | .053  | .065        | 1.02  | 1.33  | 1.65  |

| Lower Lead Width           | В       | .016  | .019  | .022        | 0.41  | 0.48  | 0.56  |

| Overall Row Spacing        | eB      | .320  | .350  | .430        | 8.13  | 8.89  | 10.92 |

| Mold Draft Angle Top       | α       | 5     | 10    | 15          | 5     | 10    | 15    |

| Mold Draft Angle Bottom    | β       | 5     | 10    | 15          | 5     | 10    | 15    |

\*Controlling Parameter

Notes: Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-095 Drawing No. C04-070

## APPENDIX C: MIGRATION FROM BASE-LINE TO MID-RANGE DEVICES

This section discusses how to migrate from a baseline device (i.e., PIC16C5X) to a mid-range device (i.e., PIC16CXXX).

The following are the list of modifications over the PIC16C5X microcontroller family:

- 1. Instruction word length is increased to 14-bits. This allows larger page sizes both in program memory (2K now as opposed to 512 before) and register file (128 bytes now versus 32 bytes before).

- A PC high latch register (PCLATH) is added to handle program memory paging. Bits PA2, PA1, PA0 are removed from STATUS register.

- 3. Data memory paging is redefined slightly. STATUS register is modified.

- Four new instructions have been added: RETURN, RETFIE, ADDLW, and SUBLW. Two instructions TRIS and OPTION are being phased out although they are kept for compati-bility with PIC16C5X.

- 5. OPTION\_REG and TRIS registers are made addressable.

- 6. Interrupt capability is added. Interrupt vector is at 0004h.

- 7. Stack size is increased to 8 deep.

- 8. Reset vector is changed to 0000h.

- 9. Reset of all registers is revisited. Five different reset (and wake-up) types are recognized. Registers are reset differently.

- 10. Wake up from SLEEP through interrupt is added.

- 11. Two separate timers, Oscillator Start-up Timer (OST) and Power-up Timer (PWRT) are included for more reliable power-up. These timers are invoked selectively to avoid unnecessary delays on power-up and wake-up.

- 12. PORTB has weak pull-ups and interrupt on change feature.

- 13. T0CKI pin is also a port pin (RA4) now.

- 14. FSR is made a full eight bit register.

- 15. "In-circuit serial programming" is made possible. The user can program PIC16CXX devices using only five pins: VDD, Vss, MCLR/VPP, RB6 (clock) and RB7 (data in/out).

- 16. PCON status register is added with a Power-on Reset status bit (POR).

- 17. Code protection scheme is enhanced such that portions of the program memory can be protected, while the remainder is unprotected.

- Brown-out protection circuitry has been added. Controlled by configuration word bit BODEN. Brown-out reset ensures the device is placed in a reset condition if VDD dips below a fixed setpoint.

To convert code written for PIC16C5X to PIC16CXXX, the user should take the following steps:

- 1. Remove any program memory page select operations (PA2, PA1, PA0 bits) for CALL, GOTO.

- 2. Revisit any computed jump operations (write to PC or add to PC, etc.) to make sure page bits are set properly under the new scheme.

- 3. Eliminate any data memory page switching. Redefine data variables to reallocate them.

- 4. Verify all writes to STATUS, OPTION, and FSR registers since these have changed.

- 5. Change reset vector to 0000h.

## READER RESPONSE

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE: | Technical Publications Manager<br>Reader Response         | Total Pages Sent                     |

|------------|-----------------------------------------------------------|--------------------------------------|

| Fror       | n: Name                                                   |                                      |

|            | Company                                                   |                                      |

|            | Address                                                   |                                      |

|            | City / State / ZIP / Country                              |                                      |

|            | Telephone: ()                                             | FAX: ()                              |

| Арр        | lication (optional):                                      |                                      |

| Wou        | Ild you like a reply?YN                                   |                                      |

| Dev        | ice: 24xx010                                              | Literature Number: DS35008C          |

| Que        | stions:                                                   |                                      |

| 1.         | What are the best features of this document?              |                                      |

|            |                                                           |                                      |

| 2.         | How does this document meet your hardware and softw       | are development needs?               |

|            |                                                           |                                      |

| 3.         | Do you find the organization of this document easy to fo  | llow? If not, why?                   |

|            |                                                           |                                      |

|            |                                                           |                                      |

| 4.         | What additions to the document do you think would enh     | ance the structure and subject?      |

|            |                                                           |                                      |

| 5.         | What deletions from the document could be made witho      | ut affecting the overall usefulness? |

|            |                                                           |                                      |

|            |                                                           |                                      |

| 6.         | Is there any incorrect or misleading information (what ar | nd where)?                           |

|            |                                                           |                                      |

| 7.         | How would you improve this document?                      |                                      |

|            |                                                           |                                      |

|            |                                                           |                                      |