Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betans                     |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

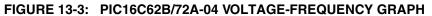

| Speed                      | 4MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c72a-04-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.2 OPTION\_REG REGISTER

Г

The OPTION\_REG register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known as the prescaler), the External INT Interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

#### REGISTER 2-2: OPTION\_REG REGISTER (ADDRESS 81h)

| R/W-1    | R/W-1       | R/W-1                          | R/W-1    | R/W-1        | R/W-1     | R/W-1   | R/W-1 |                          |

|----------|-------------|--------------------------------|----------|--------------|-----------|---------|-------|--------------------------|

| RBPU     | INTEDG      | TOCS                           | T0SE     | PSA          | PS2       | PS1     | PS0   | R = Readable bit         |

| bit7     |             |                                |          |              |           |         | bit0  | W = Writable bit         |

|          |             |                                |          |              |           |         |       | - n = Value at POR reset |

| bit 7:   | RBPU: PC    |                                |          |              |           |         |       |                          |

|          |             | B pull-ups a                   |          |              |           | _       |       |                          |

|          | 0 = PORTI   | B pull-ups a                   | are enat | oled for all | PORTB inp | outs    |       |                          |

| bit 6:   | INTEDG: I   | nterrupt Ed                    | lge Sele | ct bit       |           |         |       |                          |

|          | 1 = Interru | pt on rising                   | edge o   | f RB0/INT    | pin       |         |       |                          |

|          | 0 = Interru | pt on falling                  | g edge o | f RB0/INT    | - pin     |         |       |                          |

| bit 5:   | TOCS: TM    | R0 Clock S                     | ource S  | elect bit    |           |         |       |                          |

|          | 1 = Transit | ion on RA4                     | /T0CKI   | pin          |           |         |       |                          |

|          |             | al instruction                 |          | •            | (OUT)     |         |       |                          |

| bit 4:   | TOSE: TMI   |                                | -        | •            | ,         |         |       |                          |

| Dit 4.   |             |                                |          |              | on RA4/T0 | CKI nin |       |                          |

|          |             | •                              |          |              | on RA4/T0 | •       |       |                          |

| hit 0.   |             |                                | •        |              |           | o p     |       |                          |

| bit 3:   | PSA: Pres   | •                              |          |              |           |         |       |                          |

|          |             | tler is assig<br>tler is assig |          |              | modulo    |         |       |                          |

|          |             | 0                              |          |              | module    |         |       |                          |

| bit 2-0: | PS2:PS0:    | Prescaler F                    | Rate Sel | ect bits     |           |         |       |                          |

|          | Bit Value   | TMR0 Rat                       | e WD     | Γ Rate       |           |         |       |                          |

|          | 000         | 1:2                            | 1:       | 1            |           |         |       |                          |

|          | 001         | 1:4                            | 1 :      |              |           |         |       |                          |

|          | 010         | 1:8                            | 1:       |              |           |         |       |                          |

|          | 011         | 1:16                           | 1:       | -            |           |         |       |                          |

|          | 100         | 1:32                           |          | 16           |           |         |       |                          |

|          | 101         | 1:64                           |          | 32<br>64     |           |         |       |                          |

|          | 110         | 1:128                          |          | 64<br>128    |           |         |       |                          |

|          | 111         | 1:256                          |          | 120          |           |         |       |                          |

#### 2.2.2.3 INTCON REGISTER

The INTCON Register is a readable and writable register, which contains various interrupt enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts. Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| R/W-0<br>GIE | R/W-0<br>PEIE                                                                                                                                                          | R/W-0<br>T0IE | R/W-0<br>INTE | R/W-0<br>RBIE | R/W-0<br>T0IF | R/W-0 | R/W-x<br>RBIF | R = Readable bit                                                 |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|---------------|---------------|-------|---------------|------------------------------------------------------------------|--|

| bit7         | PEIE                                                                                                                                                                   | TUIE          | INTE          | RBIE          | TUIF          | INTE  | BIF<br>bit0   | R = Readable bit<br>W = Writable bit<br>- n = Value at POR reset |  |

| bit 7:       | GIE: Global Interrupt Enable bit<br>1 = Enables all un-masked interrupts<br>0 = Disables all interrupts                                                                |               |               |               |               |       |               |                                                                  |  |

| bit 6:       | <ul> <li>PEIE: Peripheral Interrupt Enable bit</li> <li>1 = Enables all un-masked peripheral interrupts</li> <li>0 = Disables all peripheral interrupts</li> </ul>     |               |               |               |               |       |               |                                                                  |  |

| bit 5:       | <b>TolE</b> : TMR0 Overflow Interrupt Enable bit<br>1 = Enables the TMR0 interrupt<br>0 = Disables the TMR0 interrupt                                                  |               |               |               |               |       |               |                                                                  |  |

| bit 4:       | IINTE: RB0/INT External Interrupt Enable bit<br>1 = Enables the RB0/INT external interrupt<br>0 = Disables the RB0/INT external interrupt                              |               |               |               |               |       |               |                                                                  |  |

| bit 3:       | <b>RBIE</b> : RB Port Change Interrupt Enable bit<br>1 = Enables the RB port change interrupt<br>0 = Disables the RB port change interrupt                             |               |               |               |               |       |               |                                                                  |  |

| bit 2:       | <b>T0IF</b> : TMR0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed (software must clear bit)<br>0 = TMR0 register did not overflow                     |               |               |               |               |       |               |                                                                  |  |

| bit 1:       | INTF: RB0/INT External Interrupt Flag bit<br>1 = The RB0/INT external interrupt occurred (software must clear bit)<br>0 = The RB0/INT external interrupt did not occur |               |               |               |               |       |               |                                                                  |  |

| bit 0:       | 1 = At lea                                                                                                                                                             |               | the RB7:F     | B4 input p    |               |       | ite (clear by | v reading PORTB)                                                 |  |

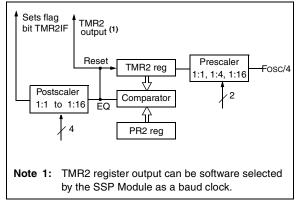

#### 6.0 TIMER2 MODULE

The Timer2 module timer has the following features:

- 8-bit timer (TMR2 register)

- Readable and writable

- 8-bit period register (PR2)

- Readable and writable

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on match (TMR2 = PR2)

- Timer2 can be used by SSP and CCP

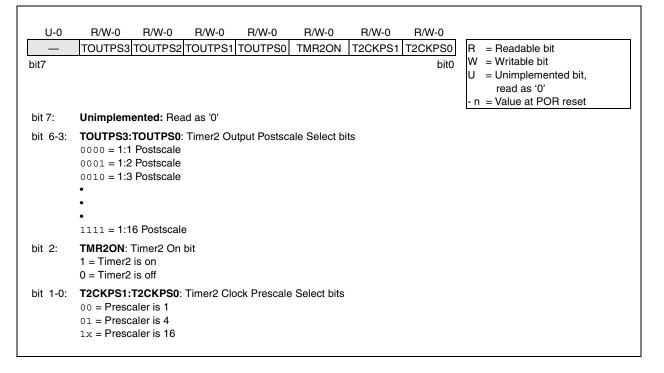

Timer2 has a control register, shown in Register 6-1. Timer2 can be shut off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Figure 6-1 is a simplified block diagram of the Timer2 module.

Additional information on timer modules is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

FIGURE 6-1: TIMER2 BLOCK DIAGRAM

#### REGISTER 6-1:T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

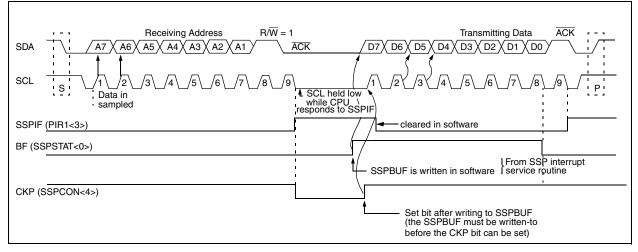

#### 8.3.1.3 TRANSMISSION

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and the CKP will be cleared by hardware, holding SCL low. Slave devices cause the master to wait by holding the SCL line low. The transmit data is loaded into the SSPBUF register, which in turn loads the SSPSR register. When bit CKP (SSP-CON<4>) is set, pin RC3/SCK/SCL releases SCL. When the SCL line goes high, the master may resume operating the SCL line and receiving data. The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 8-4).

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software, and the SSPSTAT register used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the masterreceiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not  $\overline{ACK}$ ), then the data transfer is complete. When the  $\overline{ACK}$  is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave then monitors for another occurrence of the START bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP.

FIGURE 8-4: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

#### 9.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

Note: This section applies to the PIC16C72A only.

The analog-to-digital (A/D) converter module has five input channels.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number (refer to Application Note AN546 for use of A/D Converter). The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD) or the voltage level on the RA3/AN3/VREF pin.

The A/D converter has the feature of being able to operate while the device is in SLEEP mode. To operate in sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

Additional information on the A/D module is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

The A/D module has three registers. These registers are:

- A/D Result Register (ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

A device reset forces all registers to their reset state. This forces the A/D module to be turned off, and any conversion is aborted.

The ADCON0 register, shown in Figure 9-1, controls the operation of the A/D module. The ADCON1 register, shown in Figure 9-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference) or as digital I/O.

| R/W-0         | R/W-0                                                                                                                                                                                                                                     | R/W-0      | R/W-0      | R/W-0      | R/W-0         | U-0 | R/W-0        |                                                                               |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|------------|---------------|-----|--------------|-------------------------------------------------------------------------------|--|

| ADCS1<br>bit7 | ADCS0                                                                                                                                                                                                                                     | CHS2       | CHS1       | CHS0       | GO/DONE       | _   | ADON<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0' |  |

| bit 7-6:      | ADCS1:ADCS0: A/D Conversion Clock Select bits<br>00 = Fosc/2<br>01 = Fosc/8<br>10 = Fosc/32<br>11 = FRC (clock derived from an internal RC oscillator)                                                                                    |            |            |            |               |     |              |                                                                               |  |

| bit 5-3:      | CHS2:CHS0: Analog Channel Select bits<br>000 = channel 0, (RA0/AN0)<br>001 = channel 1, (RA1/AN1)<br>010 = channel 2, (RA2/AN2)<br>011 = channel 3, (RA3/AN3)<br>100 = channel 4, (RA5/AN4)                                               |            |            |            |               |     |              |                                                                               |  |

| bit 2:        | GO/DON                                                                                                                                                                                                                                    | E: A/D Co  | nversion   | Status bit |               |     |              |                                                                               |  |

|               | $\frac{\text{If ADON} = 1}{1 = A/D \text{ conversion in progress (setting this bit starts the A/D conversion)}$<br>0 = A/D conversion not in progress (This bit is automatically cleared by hardware when the A/D conversion is complete) |            |            |            |               |     |              |                                                                               |  |

| bit 1:        | Unimpler                                                                                                                                                                                                                                  | nented: F  | Read as '0 | ı          |               |     |              |                                                                               |  |

| bit 0:        | <b>ADON</b> : $A_{1} = A/D c$                                                                                                                                                                                                             | onverter r |            |            | l consumes no |     | n ourront    |                                                                               |  |

#### **REGISTER 9-1: ADCON0 REGISTER (ADDRESS 1Fh)**

#### 10.0 SPECIAL FEATURES OF THE CPU

The PIC16C62B/72A devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Mode Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- ID locations

- In-circuit serial programming<sup>™</sup> (ICSP)

These devices have a Watchdog Timer, which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The

#### FIGURE 10-1: CONFIGURATION WORD

other is the Power-up Timer (PWRT), which provides a fixed delay on power-up only and is designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

Additional information on special features is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

#### 10.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

| CP1          | CP0 | CP1                                                                                                                            | CP0  | CP1    | CP0    | _     | BODEN | CP1 | CP0 | PWRTE | WDTE | FOSC1 | FOSC0                      | Register:                    | CONFIG |

|--------------|-----|--------------------------------------------------------------------------------------------------------------------------------|------|--------|--------|-------|-------|-----|-----|-------|------|-------|----------------------------|------------------------------|--------|

| bit13        |     |                                                                                                                                |      |        |        |       |       |     |     |       |      |       | bit0                       | Address:                     | 2007h  |

| bit 13<br>5- | 4:  |                                                                                                                                |      |        |        |       |       |     |     |       |      |       |                            |                              |        |

|              |     | 00 = AII                                                                                                                       |      |        |        |       |       |     |     |       |      |       |                            |                              |        |

| bit 7:       | I   | Jnimpl                                                                                                                         | emen | ted: R | ead as | s '1' |       |     |     |       |      |       |                            |                              |        |

| bit 6:       |     | BODEN: Brown-out Reset Enable bit <sup>(1)</sup><br>1 = BOR enabled<br>0 = BOR disabled                                        |      |        |        |       |       |     |     |       |      |       |                            |                              |        |

| bit 3:       |     | <b>PWRTE</b> : Power-up Timer Enable bit <sup>(1)</sup><br>1 = PWRT disabled<br>0 = PWRT enabled                               |      |        |        |       |       |     |     |       |      |       |                            |                              |        |

| bit 2:       | :   | WDTE: Watchdog Timer Enable bit<br>1 = WDT enabled<br>0 = WDT disabled                                                         |      |        |        |       |       |     |     |       |      |       |                            |                              |        |

| bit 1-       |     | FOSC1:FOSC0: Oscillator Selection bits<br>11 = RC oscillator<br>10 = HS oscillator<br>01 = XT oscillator<br>00 = LP oscillator |      |        |        |       |       |     |     |       |      |       |                            |                              |        |

| Note         |     |                                                                                                                                |      |        |        |       |       |     |     |       |      |       | dless of the<br>tion schem | e value of bit<br>ne listed. | PWRTE. |

#### 10.8 <u>Time-out Sequence</u>

When a POR reset occurs, the PWRT delay starts (if enabled). When PWRT ends, the OST counts 1024 oscillator cycles (LP, XT, HS modes only). When OST completes, the device comes out of reset. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all.

If MCLR is kept low long enough, the time-outs will expire. Bringing MCLR high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16CXXX device operating in parallel.

#### **Status Register**

Table 10-5 shows the reset conditions for the STATUS, PCON and PC registers, while Table 10-6 shows the reset conditions for all the registers.

#### 10.9 <u>Power Control/Status Register</u> (PCON)

The  $\overline{\text{BOR}}$  bit is unknown on Power-on Reset. If the Brown-out Reset circuit is used, the  $\overline{\text{BOR}}$  bit must be set by the user and checked on subsequent resets to see if it was cleared, indicating a Brown-out has occurred.

POR (Power-on Reset Status bit) is cleared on a Power-on Reset and unaffected otherwise. The user

| IRP | RP1 | RP0 | TO | PD | Z | DC | С |

|-----|-----|-----|----|----|---|----|---|

|     |     |     |    |    |   |    |   |

| POR BOF |

|---------|

|---------|

TABLE 10-3 TIME-OUT IN VARIOUS SITUATIONS

| Oppillator Configuration | Power              | -up      | Brown out        | Wake-up from |  |

|--------------------------|--------------------|----------|------------------|--------------|--|

| Oscillator Configuration | PWRTE = 0PWRTE = 1 |          | Brown-out        | SLEEP        |  |

| XT, HS, LP               | 72 ms + 1024Tosc   | 1024Tosc | 72 ms + 1024Tosc | 1024Tosc     |  |

| RC                       | 72 ms              |          | 72 ms            | —            |  |

#### TABLE 10-4 STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | TO | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset                                          |

| 0   | x   | 0  | x  | Illegal, TO is set on POR                               |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

#### TABLE 10-5 RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

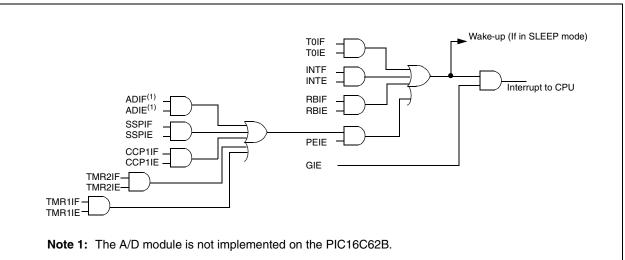

#### 10.10 Interrupts

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set regard- |

|-------|------------------------------------------------|

|       | less of the status of their corresponding      |

|       | mask bit or the GIE bit.                       |

A global interrupt enable bit, GIE (INTCON<7>) enables or disables all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt flag bits are set regardless of the status of the GIE bit. The GIE bit is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit, which reenables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register. The peripheral interrupt flags are contained in the special function registers PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupts, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine, the source of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles, depending on when the interrupt event occurs. The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit

#### FIGURE 10-7: INTERRUPT LOGIC

| COMF             | Complement f                                                                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] COMF f,d                                                                                                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                           |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                |

| Status Affected: | Z                                                                                                                                                         |

| Description:     | The contents of register 'f' are comple-<br>mented. If 'd' is 0, the result is stored<br>in W. If 'd' is 1, the result is stored<br>back in register 'f'. |

| GOTO             | Unconditional Branch                                                                                                                                                                          |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                       |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                            |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                               |

| Status Affected: | None                                                                                                                                                                                          |

| Description:     | GOTO is an unconditional branch. The<br>eleven bit immediate value is loaded<br>into PC bits <10:0>. The upper bits of<br>PC are loaded from PCLATH<4:3>.<br>GOTO is a two cycle instruction. |

| DECF             | Decrement f                                                                                                                          |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECF f,d                                                                                                            |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                          |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                  |

| Status Affected: | Z                                                                                                                                    |

| Description:     | Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| INCF             | Increment f                                                                                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                       |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                     |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is 0, the result is placed<br>in the W register. If 'd' is 1, the result is<br>placed back in register 'f'. |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                      | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                          | Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                             | Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in[0,1] \end{array}$                                                                                                                                                                                                                                                            |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                  | Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                        | Status Affected: | None                                                                                                                                                                                                                                                                                                                  |

| Description:     | The contents of register 'f' are decre-<br>mented. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>placed back in register 'f'.<br>If the result is 1, the next instruction, is<br>executed. If the result is 0, then a NOP is<br>executed instead making it a $2Tcy$<br>instruction. | Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is 0, the result is placed<br>in the W register. If 'd' is 1, the result is<br>placed back in register 'f'.<br>If the result is 1, the next instruction is<br>executed. If the result is 0, a NOP is<br>executed instead making it a $2TCY$<br>instruction. |

# PIC16C62B/72A

MPLIB is a librarian for pre-compiled code to be used with MPLINK. When a routine from a library is called from another source file, only the modules that contains that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications. MPLIB manages the creation and modification of library files.

MPLINK features include:

- MPLINK works with MPASM and MPLAB-C17 and MPLAB-C18.

- MPLINK allows all memory areas to be defined as sections to provide link-time flexibility.

MPLIB features include:

- MPLIB makes linking easier because single libraries can be included instead of many smaller files.

- MPLIB helps keep code maintainable by grouping related modules together.

- MPLIB commands allow libraries to be created and modules to be added, listed, replaced, deleted, or extracted.

#### 12.5 MPLAB-SIM Software Simulator

The MPLAB-SIM Software Simulator allows code development in a PC host environment by simulating the PIC series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file or user-defined key press to any of the pins. The execution can be performed in single step, execute until break, or trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C17 and MPLAB-C18 and MPASM. The Software Simulator offers the flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

#### 12.6 <u>MPLAB-ICE High Performance</u> <u>Universal In-Circuit Emulator with</u> <u>MPLAB IDE</u>

The MPLAB-ICE Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers (MCUs). Software control of MPLAB-ICE is provided by the MPLAB Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB-ICE allows expansion to support new PIC microcontrollers.

The MPLAB-ICE Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows 3.x/95/98 environment were chosen to best make these features available to you, the end user.

MPLAB-ICE 2000 is a full-featured emulator system with enhanced trace, trigger, and data monitoring features. Both systems use the same processor modules and will operate across the full operating speed range of the PIC MCU.

#### 12.7 PICMASTER/PICMASTER CE

The PICMASTER system from Microchip Technology is a full-featured, professional quality emulator system. This flexible in-circuit emulator provides a high-quality, universal platform for emulating Microchip 8-bit PIC microcontrollers (MCUs). PICMASTER systems are sold worldwide, with a CE compliant model available for European Union (EU) countries.

#### 12.8 <u>ICEPIC</u>

ICEPIC is a low-cost in-circuit emulation solution for the Microchip Technology PIC16C5X, PIC16C6X, PIC16C7X, and PIC16CXXX families of 8-bit one-timeprogrammable (OTP) microcontrollers. The modular system can support different subsets of PIC16C5X or PIC16CXXX products through the use of interchangeable personality modules or daughter boards. The emulator is capable of emulating without target application circuitry being present.

#### 12.9 MPLAB-ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB-ICD, is a powerful, low-cost run-time development tool. This tool is based on the flash PIC16F877 and can be used to develop for this and other PIC microcontrollers from the PIC16CXXX family. MPLAB-ICD utilizes the In-Circuit Debugging capability built into the PIC16F87X. This feature, along with Microchip's In-Circuit Serial Programming protocol, offers cost-effective in-circuit flash programming and debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time. The MPLAB-ICD is also a programmer for the flash PIC16F87X family.

#### 12.10 PRO MATE II Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode. PRO MATE II is CE compliant.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In

<sup>© 1998-2013</sup> Microchip Technology Inc.

|                 |               |                                                                         | Standar     | d Opera | ating Co | ondition | s (unless otherwise stated)                                                                                  |

|-----------------|---------------|-------------------------------------------------------------------------|-------------|---------|----------|----------|--------------------------------------------------------------------------------------------------------------|

| DC CHA          | RACTE         | RISTICS                                                                 | Operatir    | ng temp | erature  |          | $\leq$ TA $\leq$ +70°C for commercial                                                                        |

|                 | 1             | 1                                                                       | 1           | 1       | 1        | -40°C    |                                                                                                              |

| Param<br>No.    | Sym           | Characteristic                                                          | Min         | Тур†    | Мах      | Units    | Conditions                                                                                                   |

| D001            | Vdd           | Supply Voltage                                                          | 2.5         | -       | 5.5      | V        | LP, XT, RC osc modes (DC - 4 MHz)                                                                            |

|                 |               |                                                                         | VBOR*       | -       | 5.5      | V        | BOR enabled (Note 7)                                                                                         |

| D002*           | Vdr           | RAM Data Retention<br>Voltage (Note 1)                                  | -           | 1.5     | -        | V        |                                                                                                              |

| D003            | VPOR          | <b>VDD Start Voltage</b> to<br>ensure internal<br>Power-on Reset signal | -           | Vss     | -        | V        | See section on Power-on Reset for details                                                                    |

| D004*<br>D004A* | SVDD          | <b>VDD Rise Rate</b> to<br>ensure internal<br>Power-on Reset signal     | 0.05<br>TBD | -<br>-  | -        | V/ms     | PWRT enabled (PWRTE bit clear)<br>PWRT disabled (PWRTE bit set)<br>See section on Power-on Reset for details |

| D005            | VBOR          | Brown-out Reset<br>voltage trip point                                   | 3.65        | -       | 4.35     | V        | BODEN bit set                                                                                                |

| D010            | IDD           | Supply Current<br>(Note 2, 5)                                           | -           | 2.0     | 3.8      | mA       | XT, RC osc modes<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                        |

| D010A           |               |                                                                         | -           | 22.5    | 48       | μA       | LP OSC MODE<br>FOSC = 32 kHz, VDD = 3.0V, WDT disabled                                                       |

| D020            | IPD           | Power-down Current                                                      | -           | 7.5     | 30       | μA       | VDD = 3.0V, WDT enabled, -40°C to +85°C                                                                      |

| D021            |               | (Note 3, 5)                                                             | -           | 0.9     | 5        | μA       | VDD = $3.0V$ , WDT disabled, $0^{\circ}C$ to $+70^{\circ}C$                                                  |

| D021A           |               |                                                                         | -           | 0.9     | 5        | μA       | VDD = 3.0V, WDT disabled, -40°C to +85°C                                                                     |

|                 |               | Module Differential<br>Current (Note 6)                                 |             |         |          |          |                                                                                                              |

| D022*           | $\Delta$ IWDT | Watchdog Timer                                                          | -           | 6.0     | 20       | μA       | WDTE BIT SET, VDD = 4.0V                                                                                     |

| D022A*          | $\Delta$ IBOR | Brown-out Reset                                                         | -           | TBD     | 200      | μA       | BODEN bit set, VDD = 5.0V                                                                                    |

#### 13.2 DC Characteristics: PIC16LC62B/72A-04 (Commercial, Industrial)

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD,

$\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- 4: For RC osc mode, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: This is the voltage where the device enters the Brown-out Reset. When BOR is enabled, the device will perform a brown-out reset when VDD falls below VBOR.

#### 13.4 AC (Timing) Characteristics

#### 13.4.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2              | ppS                                 | 3. TCC:ST | (I <sup>2</sup> C specifications only) |

|-----------------------|-------------------------------------|-----------|----------------------------------------|

| 2. TppS               |                                     | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                     |                                     |           |                                        |

| F                     | Frequency                           | Т         | Time                                   |

| Lowercas              | e letters (pp) and their meanings:  |           |                                        |

| рр                    |                                     |           |                                        |

| сс                    | CCP1                                | OSC       | OSC1                                   |

| ck                    | CLKOUT                              | rd        | RD                                     |

| cs                    | CS                                  | rw        | RD or WR                               |

| di                    | SDI                                 | SC        | SCK                                    |

| do                    | SDO                                 | SS        | SS                                     |

| dt                    | Data in                             | t0        | TOCKI                                  |

| io                    | I/O port                            | t1        | T1CKI                                  |

| mc                    | MCLR                                | wr        | WR                                     |

| Uppercas              | se letters and their meanings:      |           |                                        |

| S                     |                                     |           |                                        |

| F                     | Fall                                | Р         | Period                                 |

| Н                     | High                                | R         | Rise                                   |

| I                     | Invalid (Hi-impedance)              | V         | Valid                                  |

| L                     | Low                                 | Z         | Hi-impedance                           |

| I <sup>2</sup> C only |                                     |           |                                        |

| AA                    | output access                       | High      | High                                   |

| BUF                   | Bus free                            | Low       | Low                                    |

| TCC:ST (I             | <sup>2</sup> C specifications only) |           |                                        |

| CC                    |                                     |           |                                        |

| HD                    | Hold                                | SU        | Setup                                  |

| ST                    |                                     |           |                                        |

| DAT                   | DATA input hold                     | STO       | STOP condition                         |

| STA                   | START condition                     |           |                                        |

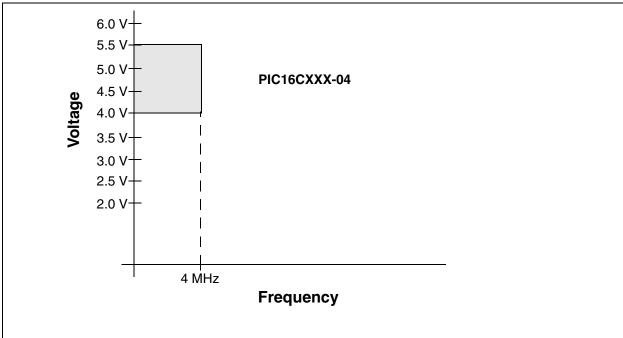

| Param<br>No. | Sym      | Characteristic                          |                    | Min        | Тур† | Мах         | Units | Conditions |

|--------------|----------|-----------------------------------------|--------------------|------------|------|-------------|-------|------------|

| 10*          | TosH2ckL | OSC1↑ to CLKOUT↓                        | OSC1↑ to CLKOUT↓   |            |      | 200         | ns    | Note 1     |

| 11*          | TosH2ckH | OSC1↑ to CLKOUT↑                        |                    | —          | 75   | 200         | ns    | Note 1     |

| 12*          | TckR     | CLKOUT rise time                        |                    | _          | 35   | 100         | ns    | Note 1     |

| 13*          | TckF     | CLKOUT fall time                        |                    | _          | 35   | 100         | ns    | Note 1     |

| 14*          | TckL2ioV | CLKOUT ↓ to Port out valid              |                    | —          |      | 0.5TCY + 20 | ns    | Note 1     |

| 15*          | TioV2ckH | Port in valid before CLKOUT ↑           |                    | Tosc + 200 |      | _           | ns    | Note 1     |

| 16*          | TckH2iol | Port in hold after CLKOUT ↑             |                    | 0          |      | _           | ns    | Note 1     |

| 17*          | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to Port of | —                  | 50         | 150  | ns          |       |            |

| 18*          | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to Port    | PIC16CXX           | 100        |      | _           | ns    |            |

| 18A*         |          | input invalid (I/O in hold<br>time)     | PIC16LCXX          | 200        |      | _           | ns    |            |

| 19*          | TioV2osH | Port input valid to OSC11 (             | I/O in setup time) | 0          | _    | —           | ns    |            |

| 20*          | TioR     | Port output rise time                   | PIC16CXX           | —          | 10   | 40          | ns    |            |

| 20A*         |          |                                         | PIC16LCXX          | _          |      | 80          | ns    |            |

| 21*          | TioF     | Port output fall time                   | PIC16CXX           | —          | 10   | 40          | ns    |            |

| 21A*         |          |                                         | PIC16LCXX          | _          | _    | 80          | ns    |            |

| 22††*        | Tinp     | INT pin high or low time                | ·                  | Тсү        | _    | —           | ns    |            |

| 23††*        | Trbp     | RB7:RB4 change INT high                 | or low time        | Тсү        | _    |             | ns    |            |

| TABLE 13-3: | CLKOUT AND I/O TIMING REQUIREMENTS |

|-------------|------------------------------------|

|             |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

tt These parameters are asynchronous events not related to any internal clock edge.

**Note 1:** Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

# TABLE 13-13:A/D CONVERTER CHARACTERISTICS:<br/>PIC16C72A-04 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC16C72A-20 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC16LC72A-04 (COMMERCIAL, INDUSTRIAL)

| Param<br>No. | Sym                              | Characte                                   | ristic    | Min                    | Тур†  | Мах        | Units                                                                                                                                      | Conditions                                                           |

|--------------|----------------------------------|--------------------------------------------|-----------|------------------------|-------|------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| A01          | NR                               | Resolution                                 |           | —                      | —     | 8-bits     | bit                                                                                                                                        | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$ |

| A02          | Eabs                             | Total Absolute error                       | —         | _                      | < ± 1 | LSB        | $\begin{array}{l} \text{VREF} = \text{VDD} = 5.12\text{V},\\ \text{VSS} \leq \text{VAIN} \leq \text{VREF} \end{array}$                     |                                                                      |

| A03          | EIL                              | Integral linearity error                   | _         | —                      | < ± 1 | LSB        | $\begin{array}{l} \text{VREF} = \text{VDD} = 5.12\text{V},\\ \text{VSS} \leq \text{VAIN} \leq \text{VREF} \end{array}$                     |                                                                      |

| A04          | Edl                              | Differential linearity er                  |           | _                      | < ± 1 | LSB        | $\begin{array}{l} \text{VREF} = \text{VDD} = 5.12\text{V},\\ \text{VSS} \leq \text{VAIN} \leq \text{VREF} \end{array}$                     |                                                                      |

| A05          | Efs                              | Full scale error                           |           | _                      | < ± 1 | LSB        | $\begin{array}{l} \text{VREF} = \text{VDD} = 5.12\text{V},\\ \text{VSS} \leq \text{VAIN} \leq \text{VREF} \end{array}$                     |                                                                      |

| A06          | EOFF                             | Offset error                               | _         | —                      | < ± 1 | LSB        | $\begin{array}{l} \text{VREF} = \text{VDD} = 5.12\text{V},\\ \text{VSS} \leq \text{VAIN} \leq \text{VREF} \end{array}$                     |                                                                      |

| A10          | —                                | Monotonicity                               | _         | guaranteed<br>(Note 3) | —     |            | $VSS \leq VAIN \leq VREF$                                                                                                                  |                                                                      |

| A20          | VREF                             | Reference voltage                          |           | 2.5V                   | —     | VDD + 0.3  | V                                                                                                                                          |                                                                      |

| A25          | VAIN                             | Analog input voltage                       |           | Vss - 0.3              | _     | VREF + 0.3 | V                                                                                                                                          |                                                                      |

| A30          | ZAIN                             | Recommended imped<br>analog voltage source |           | _                      | —     | 10.0       | kΩ                                                                                                                                         |                                                                      |

| A40          | IAD                              | A/D conversion                             | PIC16CXX  | —                      | 180   | —          | μA                                                                                                                                         | Average current con-                                                 |

|              |                                  | current (VDD)                              | PIC16LCXX | —                      | 90    | —          | μA                                                                                                                                         | sumption when A/D is on. (Note 1)                                    |

| A50          | IREF VREF input current (Note 2) |                                            | 10        |                        | 1000  | μΑ<br>μΑ   | During VAIN acquisi-<br>tion. Based on differ-<br>ential of VHOLD to<br>VAIN to charge<br>CHOLD, see<br>Section 9.1.<br>During A/D conver- |                                                                      |

|              |                                  |                                            |           |                        |       |            |                                                                                                                                            | sion cycle                                                           |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: When A/D is off, it will not consume any current other than minor leakage current.

The power-down current spec includes any such leakage from the A/D module.

**2:** VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

**3:** The A/D conversion result never decreases with an increase in the Input Voltage and has no missing codes.

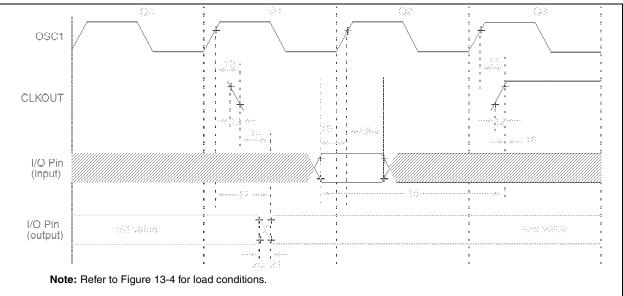

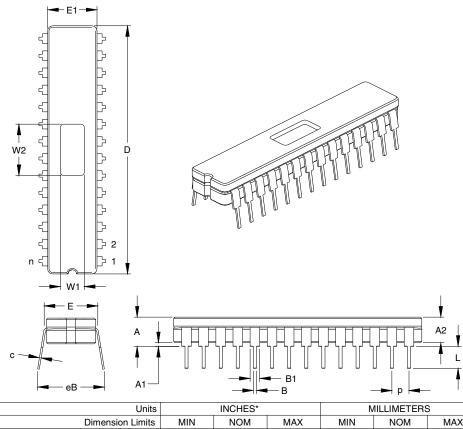

#### 28-Lead Skinny Plastic Dual In-line (SP) – 300 mil (PDIP) 15.2

|                            | Units  |       |       |       | MILLIMETERS |       |       |  |

|----------------------------|--------|-------|-------|-------|-------------|-------|-------|--|

| Dimension                  | Limits | MIN   | NOM   | MAX   | MIN         | NOM   | MAX   |  |

| Number of Pins             | n      |       | 28    |       |             | 28    |       |  |

| Pitch                      | р      |       | .100  |       |             | 2.54  |       |  |

| Top to Seating Plane       | Α      | .140  | .150  | .160  | 3.56        | 3.81  | 4.06  |  |

| Molded Package Thickness   | A2     | .125  | .130  | .135  | 3.18        | 3.30  | 3.43  |  |

| Base to Seating Plane      | A1     | .015  |       |       | 0.38        |       |       |  |

| Shoulder to Shoulder Width | E      | .300  | .313  | .325  | 7.62        | 7.94  | 8.26  |  |

| Molded Package Width       | E1     | .279  | .307  | .335  | 7.09        | 7.80  | 8.51  |  |

| Overall Length             | D      | 1.345 | 1.365 | 1.385 | 34.16       | 34.67 | 35.18 |  |

| Tip to Seating Plane       | L      | .125  | .130  | .135  | 3.18        | 3.30  | 3.43  |  |

| Lead Thickness             | С      | .008  | .012  | .015  | 0.20        | 0.29  | 0.38  |  |

| Upper Lead Width           | B1     | .040  | .053  | .065  | 1.02        | 1.33  | 1.65  |  |

| Lower Lead Width           | В      | .016  | .019  | .022  | 0.41        | 0.48  | 0.56  |  |

| Overall Row Spacing        | eB     | .320  | .350  | .430  | 8.13        | 8.89  | 10.92 |  |

| Mold Draft Angle Top       | α      | 5     | 10    | 15    | 5           | 10    | 15    |  |

| Mold Draft Angle Bottom    | β      | 5     | 10    | 15    | 5           | 10    | 15    |  |

\*Controlling Parameter

Notes: Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-095 Drawing No. C04-070

#### 15.3 <u>28-Lead Ceramic Dual In-line with Window (JW) – 300 mil (CERDIP)</u>

|                            | Units     |       |       |       |       | )     |       |

|----------------------------|-----------|-------|-------|-------|-------|-------|-------|

| Dimensio                   | on Limits | MIN   | NOM   | MAX   | MIN   | NOM   | MAX   |

| Number of Pins             | n         |       | 28    |       |       | 28    |       |

| Pitch                      | р         |       | .100  |       |       | 2.54  |       |

| Top to Seating Plane       | Α         | .170  | .183  | .195  | 4.32  | 4.64  | 4.95  |

| Ceramic Package Height     | A2        | .155  | .160  | .165  | 3.94  | 4.06  | 4.19  |

| Standoff                   | A1        | .015  | .023  | .030  | 0.38  | 0.57  | 0.76  |

| Shoulder to Shoulder Width | E         | .300  | .313  | .325  | 7.62  | 7.94  | 8.26  |

| Ceramic Pkg. Width         | E1        | .285  | .290  | .295  | 7.24  | 7.37  | 7.49  |

| Overall Length             | D         | 1.430 | 1.458 | 1.485 | 36.32 | 37.02 | 37.72 |

| Tip to Seating Plane       | L         | .135  | .140  | .145  | 3.43  | 3.56  | 3.68  |

| Lead Thickness             | С         | .008  | .010  | .012  | 0.20  | 0.25  | 0.30  |

| Upper Lead Width           | B1        | .050  | .058  | .065  | 1.27  | 1.46  | 1.65  |

| Lower Lead Width           | В         | .016  | .019  | .021  | 0.41  | 0.47  | 0.53  |

| Overall Row Spacing        | eB        | .345  | .385  | .425  | 8.76  | 9.78  | 10.80 |

| Window Width               | W1        | .130  | .140  | .150  | 3.30  | 3.56  | 3.81  |

| Window Length              | W2        | .290  | .300  | .310  | 7.37  | 7.62  | 7.87  |

| *0 · // D ·                |           |       |       |       |       |       |       |

\*Controlling Parameter JEDEC Equivalent: MO-058 Drawing No. C04-080

© 1998-2013 Microchip Technology Inc.

### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

#### CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

## Worldwide Sales and Service

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney Tel: 61-2-9868-6733

Fax: 61-2-9868-6755 China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Fax: 45-4485-2829

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

11/29/12