Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

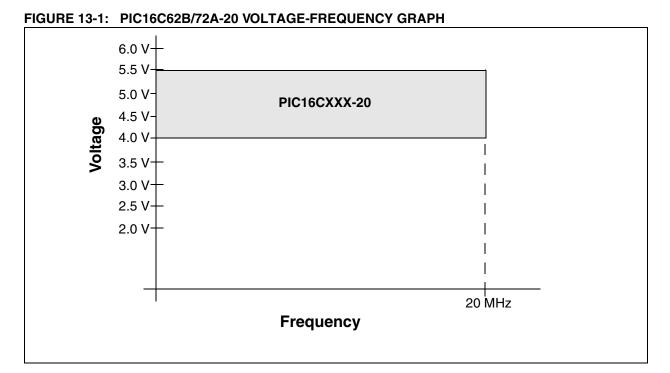

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

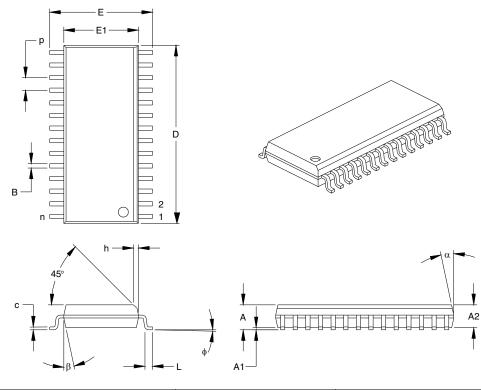

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c72a-04e-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Addr    | Name                    | Bit 7              | Bit 6               | Bit 5                     | Bit 4         | Bit 3         | Bit 2           | Bit 1        | Bit 0         | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(4) |

|---------|-------------------------|--------------------|---------------------|---------------------------|---------------|---------------|-----------------|--------------|---------------|--------------------------|-------------------------------------|

| Bank 1  |                         |                    |                     |                           |               |               |                 |              |               |                          |                                     |

| 80h     | INDF <sup>(1)</sup>     | Addressing         | this locatio        | n uses conte              | ents of FSR   | to address d  | ata memory      | (not a physi | cal register) | 0000 0000                | 0000 0000                           |

| 81h     | OPTION_REG              | RBPU               | INTEDG              | T0CS                      | TOSE          | PSA           | PS2             | PS1          | PS0           | 1111 1111                | 1111 1111                           |

| 82h     | PCL <sup>(1)</sup>      | Program C          | ounter's (PC        | C) Least Sig              | nificant Byte | 1             |                 |              |               | 0000 0000                | 0000 0000                           |

| 83h     | STATUS <sup>(1)</sup>   | IRP <sup>(5)</sup> | RP1 <sup>(5)</sup>  | RP0                       | TO            | PD            | Z               | DC           | С             | 0001 1xxx                | 000q quuu                           |

| 84h     | FSR <sup>(1)</sup>      | Indirect dat       | a memory a          | ddress poir               | nter          |               |                 |              |               | xxxx xxxx                | uuuu uuuu                           |

| 85h     | TRISA                   | —                  | —                   | PORTA Da                  | ta Direction  | Register      |                 |              |               | 11 1111                  | 11 1111                             |

| 86h     | TRISB                   | PORTB Da           | ta Direction        | Register                  |               |               |                 |              |               | 1111 1111                | 1111 1111                           |

| 87h     | TRISC                   | PORTC Da           | ta Direction        | Register                  |               |               |                 |              |               | 1111 1111                | 1111 1111                           |

| 88h-89h | _                       | Unimpleme          | ented               |                           |               |               |                 |              |               | _                        | _                                   |

| 8Ah     | PCLATH <sup>(1,2)</sup> | —                  | _                   | —                         | Write Buffe   | r for the upp | er 5 bits of th | e Program (  | Counter       | 0 0000                   | 0 0000                              |

| 8Bh     | INTCON <sup>(1)</sup>   | GIE                | PEIE                | TOIE                      | INTE          | RBIE          | TOIF            | INTF         | RBIF          | 0000 000x                | 0000 000u                           |

| 8Ch     | PIE1                    | —                  | ADIE <sup>(3)</sup> | _                         | —             | SSPIE         | CCP1IE          | TMR2IE       | TMR1IE        | -0 0000                  | -0 0000                             |

| 8Dh     | _                       | Unimpleme          | ented               |                           |               |               |                 |              |               | _                        | _                                   |

| 8Eh     | PCON                    | —                  | _                   | —                         | —             | _             | —               | POR          | BOR           | dd                       | uu                                  |

| 8Fh-91h | _                       | Unimpleme          | ented               |                           |               |               |                 | •            |               | _                        | _                                   |

| 92h     | PR2                     | Timer2 Per         | iod Registe         | r                         |               |               |                 |              |               | 1111 1111                | 1111 1111                           |

| 93h     | SSPADD                  | Synchrono          | us Serial Po        | rt (I <sup>2</sup> C mode | e) Address F  | Register      |                 |              |               | 0000 0000                | 0000 0000                           |

| 94h     | SSPSTAT                 | SMP                | CKE                 | D/A                       | Р             | S             | R/W             | UA           | BF            | 0000 0000                | 0000 0000                           |

| 95h-9Eh | —                       | Unimpleme          | ented               |                           |               |               |                 |              |               | —                        | —                                   |

| 9Fh     | ADCON1 <sup>(3)</sup>   | _                  | _                   | _                         | _             | _             | PCFG2           | PCFG1        | PCFG0         | 000                      | 000                                 |

## TABLE 2-1 SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0',

Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: A/D not implemented on the PIC16C62B, maintain as '0'.

4: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

5: The IRP and RP1 bits are reserved. Always maintain these bits clear.

**6:** On any device reset, these pins are configured as inputs.

7: This is the value that will be in the port output latch.

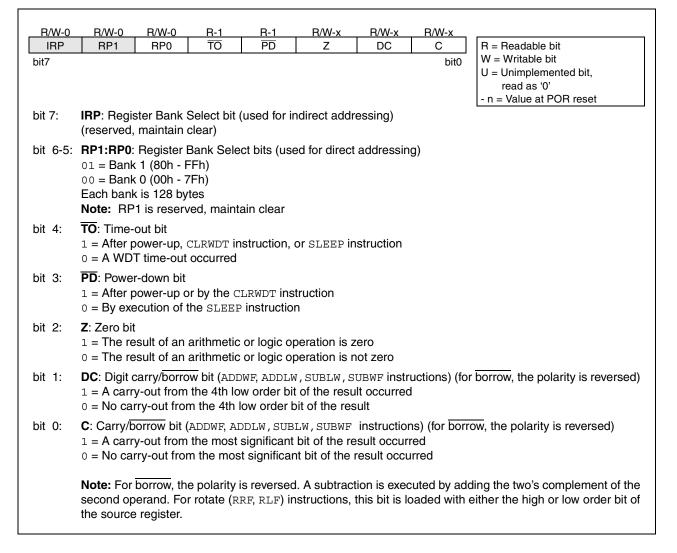

### 2.2.2.1 STATUS REGISTER

The STATUS register, shown in Register 2-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, the write to these three bits is disabled. These bits are set or cleared according to the device logic. The TO and PD bits are not writable. The result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

- **Note 1:** The IRP and RP1 bits are reserved. Maintain these bits clear to ensure upward compatibility with future products.

- Note 2: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions.

## REGISTER 2-1: STATUS REGISTER (ADDRESS 03h, 83h)

# PIC16C62B/72A

### 2.2.2.4 PIE1 REGISTER

This register contains the individual enable bits for the peripheral interrupts.

## REGISTER 2-4: PIE1 REGISTER (ADDRESS 8Ch)

#### R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 U-0 U-0 U-0 ADIE<sup>(1)</sup> SSPIE CCP1IE TMR2IE TMR1IE R = Readable bit W = Writable bit bit7 bit0 U = Unimplemented bit, read as '0' n = Value at POR reset Unimplemented: Read as '0' bit 7: ADIE<sup>(1)</sup>: A/D Converter Interrupt Enable bit bit 6: 1 = Enables the A/D interrupt 0 = Disables the A/D interrupt bit 5-4: Unimplemented: Read as '0' bit 3: SSPIE: Synchronous Serial Port Interrupt Enable bit 1 = Enables the SSP interrupt 0 = Disables the SSP interrupt CCP1IE: CCP1 Interrupt Enable bit bit 2: 1 = Enables the CCP1 interrupt 0 = Disables the CCP1 interrupt TMR2IE: TMR2 to PR2 Match Interrupt Enable bit bit 1: 1 = Enables the TMR2 to PR2 match interrupt 0 = Disables the TMR2 to PR2 match interrupt TMR1IE: TMR1 Overflow Interrupt Enable bit bit 0: 1 = Enables the TMR1 overflow interrupt 0 = Disables the TMR1 overflow interrupt Note 1: The PIC16C62B does not have an A/D module. This bit location is reserved on these devices. Always maintain this bit clear.

#### Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

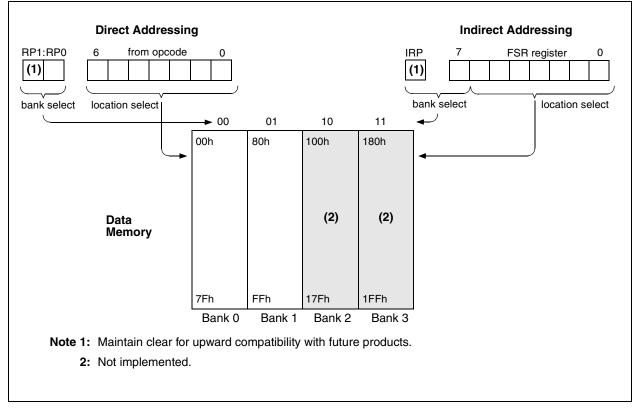

### 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*).

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-1.

## EXAMPLE 2-1: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

|          | movlw<br>movwf |       | ;initialize pointer<br>; to RAM |

|----------|----------------|-------|---------------------------------|

| NEXT     | clrf           | INDF  | ;clear INDF register            |

|          | incf           | FSR   | ;inc pointer                    |

|          | btfss          | FSR,4 | ;all done?                      |

|          | goto           | NEXT  | ;NO, clear next                 |

| CONTINUE |                |       |                                 |

|          | :              |       | ;YES, continue                  |

An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-3. However, IRP is not used in the PIC16C62B/72A.

## FIGURE 2-3: DIRECT/INDIRECT ADDRESSING

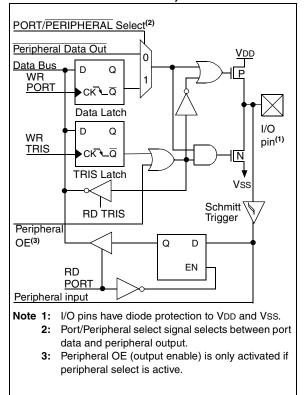

## 3.3 PORTC and the TRISC Register

PORTC is an 8-bit wide bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (=1) will make the corresponding PORTC pin an input, (i.e., put the corresponding output driver in a hi-impedance mode). Clearing a TRISC bit (=0) will make the corresponding PORTC pin an output, (i.e., put the contents of the output latch on the selected pin).

PORTC is multiplexed with several peripheral functions (Table 3-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override maybe in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

## FIGURE 3-5: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

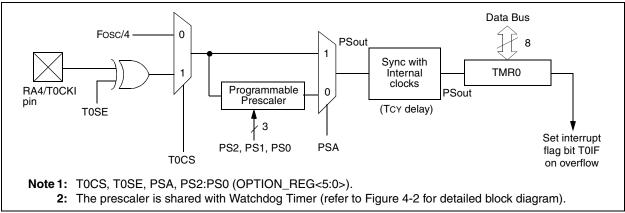

## 4.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Read and write

- INT on overflow

- 8-bit software programmable prescaler

- INT or EXT clock select

- EXT clock edge select

Figure 4-1 is a simplified block diagram of the Timer0 module.

Additional information on timer modules is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

## 4.1 <u>Timer0 Operation</u>

Timer0 can operate as a timer or as a counter.

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed below.

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization. Additional information on external clock requirements is available in the Electrical Specifications section of this manual, and in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

## 4.2 <u>Prescaler</u>

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 4-2). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. There is only one prescaler available which is shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The prescaler is not readable or writable.

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

Clearing bit PSA will assign the prescaler to the Timer0 module. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable.

Setting bit PSA will assign the prescaler to the Watchdog Timer (WDT). When the prescaler is assigned to the WDT, prescale values of 1:1, 1:2, ..., 1:128 are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment or ratio.

## FIGURE 4-1: TIMER0 BLOCK DIAGRAM

NOTES:

## 8.0 SYNCHRONOUS SERIAL PORT (SSP) MODULE

## 8.1 SSP Module Overview

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

For more information on SSP operation (including an I<sup>2</sup>C Overview), refer to the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023). Also, refer to Application Note AN578, *"Use of the SSP Module in the I<sup>2</sup>C Multi-Master Environment."*

## 8.2 SPI Mode

This section contains register definitions and operational characteristics of the SPI module.

Additional information on SPI operation may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

8.2.1 OPERATION OF SSP MODULE IN SPI MODE

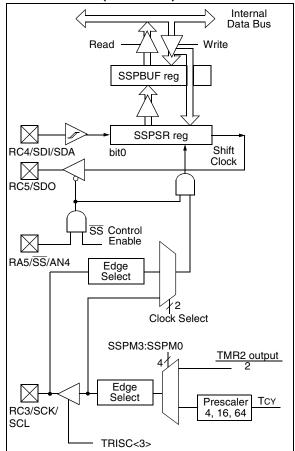

A block diagram of the SSP Module in SPI Mode is shown in Figure 8-1.

The SPI mode allows 8-bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, three pins are used:

- Serial Data Out (SDO)RC5/SDO

- Serial Data In (SDI)RC4/SDI/SDA

- Serial Clock (SCK)RC3/SCK/SCL

Additionally, a fourth pin may be used when in a slave mode of operation:

Slave Select (SS)RA5/SS/AN4

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- Master Operation (SCK is the clock output)

- Slave Mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Clock Edge (Output data on rising/falling edge of SCK)

- Clock Rate (master operation only)

- Slave Select Mode (Slave mode only)

To enable the serial port, SSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON reg-

ister, and then set bit SSPEN. This configures the SDI, SDO, SCK and  $\overline{SS}$  pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISC register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (master operation) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set (if used)

Note: When the SPI is in Slave Mode with  $\overline{SS}$  pin control enabled, (SSPCON<3:0> = 0100) the SPI module will reset if the  $\overline{SS}$  pin is set to VDD.

**Note:** If the SPI is used in Slave Mode with CKE = '1', then the  $\overline{SS}$  pin control must be enabled.

## FIGURE 8-1: SSP BLOCK DIAGRAM (SPI MODE)

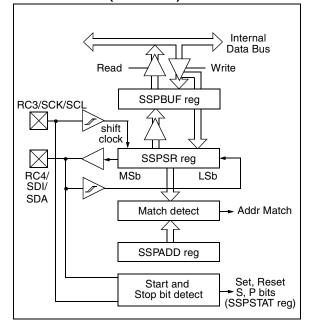

## 8.3 <u>SSP I<sup>2</sup>C Operation</u>

The SSP module in I<sup>2</sup>C mode fully implements all slave functions, except general call support, and provides interrupts on start and stop bits in hardware to support firmware implementations of the master functions. The SSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RC3/SCK/SCL pin, which is the clock (SCL), and the RC4/SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

The SSP module functions are enabled by setting SSP Enable bit SSPEN (SSPCON<5>).

FIGURE 8-2: SSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

The SSP module has five registers for  $I^2C$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with start and stop bit interrupts enabled for firmware master mode support

- I<sup>2</sup>C Slave mode (10-bit address), with start and stop bit interrupts enabled for firmware master mode support

- I<sup>2</sup>C start and stop bit interrupts enabled for firmware master mode support, slave mode idle

Selection of any  $I^2C$  mode, with the SSPEN bit set, forces the SCL and SDA pins to be operated as open drain outputs, provided these pins are programmed to inputs by setting the appropriate TRISC bits.

Additional information on SSP I<sup>2</sup>C operation may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

## 8.3.1 SLAVE MODE

In slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched or the data transfer after an address match is received, the hardware automatically will generate the acknowledge ( $\overline{ACK}$ ) pulse, and load the SSPBUF register with the received value in the SSPSR register.

There are certain conditions that will cause the SSP module not to give this  $\overline{ACK}$  pulse. This happens if either of the following conditions occur:

- a) The buffer full bit BF (SSPSTAT<0>) was set before the transfer was completed.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was completed.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. Table 8-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the SSP module, is shown in timing parameter #100, THIGH, and parameter #101, TLOW.

## 9.4 <u>A/D Conversions</u>

| Note: | The GO/DONE bit should NOT be set in        |

|-------|---------------------------------------------|

|       | the same instruction that turns on the A/D. |

## 9.5 Use of the CCP Trigger

An A/D conversion can be started by the "special event trigger" of the CCP1 module. This requires that the CCP1M3:CCP1M0 bits (CCP1CON<3:0>) be programmed as 1011 and that the A/D module be enabled (ADON bit is set). When the trigger occurs, the

TABLE 9-2 SUMMARY OF A/D REGISTERS

GO/DONE bit will be set, starting the A/D conversion, and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D acquisition period with minimal software overhead. The appropriate analog input channel must be selected and the minimum acquisition time must pass before the "special event trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), then the "special event trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

| Address | Name   | Bit 7   | Bit 6      | Bit 5   | Bit 4       | Bit 3      | Bit 2   | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all other Resets |

|---------|--------|---------|------------|---------|-------------|------------|---------|--------|--------|-------------------------|---------------------------|

| 0Bh,8Bh | INTCON | GIE     | PEIE       | TOIE    | INTE        | RBIE       | T0IF    | INTF   | RBIF   | 0000 000x               | 0000 000u                 |

| 0Ch     | PIR1   | _       | ADIF       | —       | _           | SSPIF      | CCP1IF  | TMR2IF | TMR1IF | -0 0000                 | -0 0000                   |

| 8Ch     | PIE1   | _       | ADIE       | —       | _           | SSPIE      | CCP1IE  | TMR2IE | TMR1IE | -0 0000                 | -0 0000                   |

| 1Eh     | ADRES  | A/D Res | ult Regist | er      |             |            |         |        |        | xxxx xxxx               | uuuu uuuu                 |

| 1Fh     | ADCON0 | ADCS1   | ADCS0      | CHS2    | CHS1        | CHS0       | GO/DONE | —      | ADON   | 0000 00-0               | 0000 00-0                 |

| 9Fh     | ADCON1 | _       | —          | —       | —           | —          | PCFG2   | PCFG1  | PCFG0  | 000                     | 000                       |

| 05h     | PORTA  | _       | _          | RA5     | RA4         | RA3        | RA2     | RA1    | RA0    | 0x 0000                 | 0u 0000                   |

| 85h     | TRISA  |         | —          | PORTA D | Data Direct | tion Regis | ter     |        |        | 11 1111                 | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D conversion.

## 10.2 Oscillator Configurations

### 10.2.1 OSCILLATOR TYPES

The PIC16CXXX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

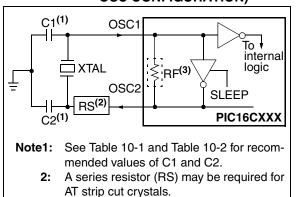

## 10.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

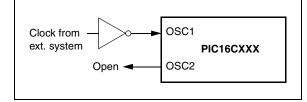

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 10-2). The PIC16CXXX oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can use an external clock source to drive the OSC1/CLKIN pin (Figure 10-3).

## FIGURE 10-2: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

3: RF varies with the crystal chosen.

## FIGURE 10-3: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

## TABLE 10-1 CERAMIC RESONATORS

## Ranges Tested:

| Ranges I                                                                | estea:                            |                      |              |  |  |  |  |

|-------------------------------------------------------------------------|-----------------------------------|----------------------|--------------|--|--|--|--|

| Mode                                                                    | Freq                              | OSC1 OSC2            |              |  |  |  |  |

| XT                                                                      | 455 kHz                           | 68 - 100 pF          | 68 - 100 pF  |  |  |  |  |

|                                                                         | 2.0 MHz                           | 15 - 68 pF 🛛 🤇       | 15 - 68 pF   |  |  |  |  |

|                                                                         | 4.0 MHz                           | 15 - 68 pF           | ∖15, - 68 pF |  |  |  |  |

| HS                                                                      | 8.0 MHz                           | 10 - 68(pF           | े10 - 68 pF  |  |  |  |  |

|                                                                         | 16.0 MHz                          | 10,-22,0F            | 10 - 22 pF   |  |  |  |  |

| These values are for design guidance only. See notes at bottom of page. |                                   |                      |              |  |  |  |  |

| Resonators Used:                                                        |                                   |                      |              |  |  |  |  |

| 455 kHz                                                                 | Panasonie E                       | FO-A455K04B          | ± 0.3%       |  |  |  |  |

| 2.0 MHz                                                                 | Murata Érie CSA2.00MG ± 0.5%      |                      |              |  |  |  |  |

| 4.0 MHz                                                                 | Murata Erie CSA4.00MG ± 0.5%      |                      |              |  |  |  |  |

| 8.0 MAHZ                                                                | Murata Erie CSA8.00MT ± 0.5%      |                      |              |  |  |  |  |

| 16.0 MHz                                                                | MHz Murata Erie CSA16.00MX ± 0.5% |                      |              |  |  |  |  |

| Resona                                                                  | ators did not hav                 | ve built-in capacito | ors.         |  |  |  |  |

## TABLE 10-2CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq                                                         | Cap. Range<br>C1 | Cap. Range<br>C2 |  |  |  |  |  |

|----------|-------------------------------------------------------------------------|------------------|------------------|--|--|--|--|--|

| LP       | 32 kHz                                                                  | 33 pF            | 33 pF            |  |  |  |  |  |

|          | 200 kHz                                                                 | 15 pF            | 15 pF            |  |  |  |  |  |

| XT       | 200 kHz                                                                 | 47-68 pF         |                  |  |  |  |  |  |

|          | 1 MHz                                                                   | 15 pF 🔍          | ↓15.pF<br>15.pF  |  |  |  |  |  |

|          | 4 MHz                                                                   | 15 pF 🕟          | 15 pF            |  |  |  |  |  |

| HS       | 4 MHz                                                                   | 15 pt            | ✓ 15 pF          |  |  |  |  |  |

|          | 8 MHz                                                                   | 15-33 pF         |                  |  |  |  |  |  |

|          | 20 MHz                                                                  |                  |                  |  |  |  |  |  |

|          | These values are for design guidance only. See notes at bottom of page. |                  |                  |  |  |  |  |  |

|          | Crystals Used                                                           |                  |                  |  |  |  |  |  |

| 32 kHz   | Epson C-00                                                              | 01R32.768K-A     | ± 20 PPM         |  |  |  |  |  |

| 200 kt/2 | STO XTL 2                                                               | ± 20 PPM         |                  |  |  |  |  |  |

| 1 MHz    | ECS ECS-                                                                | 10-13-1          | ± 50 PPM         |  |  |  |  |  |

| 4 MHz    | ECS ECS-4                                                               | 40-20-1          | ± 50 PPM         |  |  |  |  |  |

| 8 MHz    | EPSON CA                                                                | -301 8.000M-C    | ± 30 PPM         |  |  |  |  |  |

**Note 1:** Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

EPSON CA-301 20.000M-C

20 MHz

2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

± 30 PPM

- **3:** Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- 4: Oscillator performance should be verified when migrating between devices (including PIC16C62A to PIC16C62B and PIC16C72 to PIC16C72A)

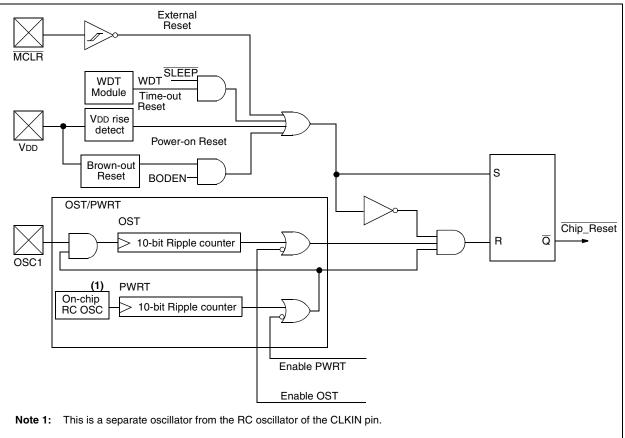

## FIGURE 10-5: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

## TABLE 11-2 PIC16CXXX INSTRUCTION SET

| Operands  MSb  LSb  Affected    BYTE-ORIENTED FILE REGISTER OPERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Mnemonic, |       | Description                 | Cycles |    | 14-Bit | Opcode | •    | Status   | Notes |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|-----------------------------|--------|----|--------|--------|------|----------|-------|

| ADDWF  f, d  Add W and f  1  00  0111  dfff  ffff  C,DC,Z    ANDWF  f, d  AND W with f  1  00  0101  dfff  ffff  Z    CLRF  f  Clear W  1  00  0001  lfff  ffff  Z    COMF  f, d  Complement f  1  00  0011  dfff  ffff  Z    COMF  f, d  Decrement f  1  00  1011  dfff  ffff  Z    DECFS  f, d  Increment f  1  00  1010  dfff  fff  Z    INCF5  f, d  Increment f skip if 0  1(2)  00  1101  dfff  fff  Z    INCF52  f, d  Move f  1  00  0000  diff  fff  Z    MOVF  f, d  Move f  1  00  0100  dfff  fff  Z    MOVF  f, d  Rotate Leift through Carry <th>Operands</th> <th></th> <th colspan="5">MSb</th> <th>LSb</th> <th>Affected</th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Operands  |       | MSb                         |        |    |        |        | LSb  | Affected |       |

| ANDWF  f, d  AND W with f  1  00  0101  dfff  ffff  Z    CLRF  f  Clear W  1  00  0001  1fff  ffff  Z    COMF  f, d  Complement f  1  00  0011  dfff  ffff  Z    COMF  f, d  Decrement f, Skip if 0  1(2)  00  1011  dfff  ffff  Z    DECFSZ  f, d  Increment f, Skip if 0  1(2)  00  111  dfff  ffff  Z    MOVF  f, d  Move f  1  00  000  dffff  Z    MOVF f  d  Move f  1  00  000  000  000  000  000  000    RF  f, d  Rotate Left fhrough Carry  1  00  100  dfff  ffff  Z    SUBWF  f, d  Swap nibbles in f  1  00  010  dfff  ffff  Z    SUBWF  f, b </th <th>BYTE-ORIE</th> <th>NTED</th> <th>FILE REGISTER OPERATIONS</th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | BYTE-ORIE | NTED  | FILE REGISTER OPERATIONS    |        |    |        |        |      |          |       |

| CLRF  f  Clear f  Clear f  1  00  0001  lfff  ffff  Z    COMF  f, d  Complement f  1  00  0001  dff  ffff  Z    DECF  f, d  Decrement f  1  00  1001  dff  ffff  Z    DECF  f, d  Decrement f, Skip if 0  1(2)  00  1010  dff  ffff  Z    INCFSZ  f, d  Increment f, Skip if 0  1(2)  00  1010  dfff  fff  Z    INCFSZ  f, d  Increment f, Skip if 0  1(2)  00  111  dfff  Z    INCFSZ  f, d  Increment f, Skip if C  1  00  000  dfff  Z    INCFSZ  f, d  Increment f, Skip if C  1  00  100  dfff  Z    MOVF  f, d  Move W to f  1  00  100  000  000  000  R  GR  GR  GR  GR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ADDWF     | f, d  | Add W and f                 | 1      | 00 | 0111   | dfff   | ffff | C,DC,Z   | 1,2   |

| CLRW  -  Clear W  1  00  0001  0000  0011  Z    COMF  f, d  Cormplement f  1  00  0011  dff ffff  Z    DECF  f, d  Decrement f, Skip if 0  1(2)  00  0011  dff ffff  Z    INCF f, d  Increment f, Skip if 0  1(2)  00  1010  dff ffff  Z    INCF f, d  Increment f, Skip if 0  1(2)  00  1010  dff ffff  Z    INCF f, d  Increment f, Skip if 0  1(2)  00  1011  dff ffff  Z    INCF f, d  Increment f, Skip if 0  1  00  0000  dff ffff  Z    MOVF f, d  Move f  1  00  0000  dff ffff  Z    SUBWF  f, d  Rotate Left ftmough Carry  1  00  0010  dff ffff  C,DC,Z    SUBWF  f, d  Subtract W from f  1  00  1010  dfff fffff  Z  Z    SUBWF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ANDWF     | f, d  | AND W with f                | 1      | 00 | 0101   | dfff   | ffff | Z        | 1,2   |

| COMF  f, d  Complement f  1  00  1001  dfff  ffff  Z    DECFSZ  f, d  Decrement f, Skip if 0  1(2)  00  1011  dfff  ffff  Z    INCF  f, d  Increment f  1  00  1010  dfff  fffff  Z    INCFSZ  f, d  Increment f, Skip if 0  1(2)  00  1111  dfff  fffff  Z    IORWF  f, d  Increment f, Skip if 0  1(2)  00  1111  dfff  fffff  Z    MOVF  f  Move f  1  00  0000  dfff  fffff  Z    MOVF f  Move V to f  1  00  0000  dfff  fffff  Z    SUBWF f, d  Subtract W from f  1  00  100  dfff  fffff  C,DC,Z    SWAPF  f, d  Subtract W from f  1  00  0101  dfff  fffff  Z    BIT-ORIENTED FILE  Ecolusive OR W w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CLRF      | f     | Clear f                     | 1      | 00 | 0001   | lfff   | ffff | Z        | 2     |

| DECF  f, d  Decrement f  1  00  0011  dfff  fff  Z    DECFSZ  f, d  Increment f  1  00  1010  dfff  fff  Z    INCF f, d  Increment f  1  00  1010  dfff  ffff  Z    INCFSZ  f, d  Increment f, Skip if 0  1(2)  00  1111  dfff  fff  Z    INCFSZ  f, d  Inclusive OR W with f  1  00  0100  dfff  fff  Z    MOVF  f, d  Move f  1  00  1000  dfff  ffff  Z    MOVWF  f, d  Rotate Left fthrough Carry  1  00  1101  dfff  fff  C  C  Z    SUBWF  f, d  Rotate Left fthrough Carry  1  00  1100  dfff  fff  C  C  C  C  C  C  C  C  C  C  C  C  C  C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CLRW      | -     | Clear W                     | 1      | 00 | 0001   | 0000   | 0011 |          |       |

| DECFSZ  f, d  Decrement f, Skip if 0  1(2)  0  1011  dfff ffff    INCF f, d  Increment f  1  0  1010  dfff ffff  Z    INCFSZ f, d  Increment f, Skip if 0  1(2)  0  1111  dfff ffff  Z    INCFSZ f, d  Inclusive CR W with f  1  0  0.000  dfff ffff  Z    MOVF f, d  Move f  1  0  0.000  dfff ffff  Z    MOVWF f  Move W to f  1  0  0.0000  0.000  C.C.C.C.C.C.C.C.C.C.C.C.C.C.C.C.C.C.C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | COMF      | f, d  | Complement f                |        | 00 | 1001   | dfff   | ffff | Z        | 1,2   |

| INCF  f, d  Increment f  1  00  1010  dfff  fff  Z    INCFSZ  f, d  Increment f, Skip if 0  1(2)  00  1111  dfff  fff  Z    IORWF  f, d  Move OR W with f  1  00  0100  dfff  fff  Z    MOVF  f, d  Move W to f  1  00  0000  lfff  fff  Z    MOVF  f  Move W to f  1  00  0000  lfff  Gff  Z    MOVF  f  Rotate Left fthrough Carry  1  00  1100  dfff  Gff  C  C    SUBWF  f, d  Rotate Left fthrough Carry  1  00  1100  dfff  fff  C  C,DC,Z    SUBWF  f, d  Subtract W from f  1  00  1010  dfff  ffff  C  C,DC,Z    SUBWF  f, d  Exclusive OR W with f  1  01  010 bb  bfff  fffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DECF      | f, d  | Decrement f                 | 1      | 00 | 0011   | dfff   | ffff | Z        | 1,2   |

| INCFSZ  f, d  Increment f, Skip if 0  1(2)  00  1111  dff ffff  Z    MOVF  f, d  Inclusive OR W with f  1  00  0100  dfff ffff  Z    MOVF  f, d  Move f  1  00  0000  dfff ffff  Z    MOVF  f, d  Move f  1  00  0000  dfff ffff  Z    MOVF  f, d  Move f  1  00  0000  dfff  ffff    NOP  No Operation  1  00  100  dfff  ffff  C    SUBWF  f, d  Rotate Left fthrough Carry  1  00  1100  dfff  ffff  C  C,DC,Z    SWAPF  f, d  Swap nibbles in f  1  00  110  dfff  ffff  Z    BIT-ORIENTED FILE  REGISTER OPERATIONS  1  1  01  0bb bfff  fffff  Z    BTFSS  f, b  Bit Test f, Skip if Set  1  1  1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DECFSZ    | f, d  | Decrement f, Skip if 0      | 1(2)   | 00 | 1011   | dfff   | ffff |          | 1,2,3 |

| IORWF  f, d  Inclusive OR W with f  1  00  0100  dfff  ffff  Z    MOVF  f, d  Move f  1  00  0100  dfff  ffff  Z    MOVWF  f  Move W to f  1  00  0000  lfff  ffff  Z    MOVWF  f  Move W to f  1  00  0000  lfff  ffff  Z    NOP  No Operation  1  00  1000  dfff  ffff  C    RRF  f, d  Rotate Left fthrough Carry  1  00  1100  dfff  ffff  C,DC,Z    SWAPF  f, d  Subtract W from f  1  00  110  dfff  ffff  C,DC,Z    SWAPF  f, d  Exclusive OR W with f  1  01  00bb  bfff  ffff  Z    BIT-ORIENTED FILE  REGISTER OPERATIONS  1  11  01  01bb  bfff  ffff    BTFSS  f, b  Bit Test f, S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | INCF      | f, d  | Increment f                 |        | 00 | 1010   | dfff   | ffff | Z        | 1,2   |

| MOVF  f, d  Move f  Move f  1  00  1000  dfff  ffff  Z    MOVWF  f  Move W to f  1  00  0000  0kx0  0000  Rff  ffff  C    NOP  -  No Operation  1  00  0000  0kx0  0000  Rk  ffff  C  C    RFF  f, d  Rotate Left fthrough Carry  1  00  1100  dfff  ffff  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C  C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | INCFSZ    |       |                             | 1(2)   | 00 | 1111   | dfff   | ffff |          | 1,2,3 |

| MOVWF  f  Move W to f  1  00  00000  lfff  ffff    NOP  -  No Operation  1  00  0000  0xx0  0000    RLF  f, d  Rotate Left fthrough Carry  1  00  1101  dfff  ffff  C    SUBWF  f, d  Subtract W from f  1  00  1100  dfff  ffff  C  D  C,DC,Z  D  C,DC,Z  D  D  D  1100  dfff  ffff  C  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D  D<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           | ,     |                             | -      |    | 0100   |        |      | —        | 1,2   |

| NOP  -  No Operation  1  00  0000  0xxx  0000    RLF  f, d  Rotate Left f through Carry  1  00  1101  dfff ffff  C    SUBWF  f, d  Subtract W from f  1  00  0100  dfff ffff  C    SWAPF  f, d  Swap nibbles in f  1  00  0110  dfff ffff  C  C,DC,Z    SWAPF  f, d  Swap nibbles in f  1  00  0110  dfff ffff  C  C,DC,Z    XORWF  f, d  Exclusive OR W with f  1  00  0110  dfff ffff  Z    BIT-ORIENTED FILE REGISTER OPERATIONS  Bit Clear f  1  01  010bb  bfff fffff  Z    BFFSC  f, b  Bit Test f, Skip if Clear  1  1  11  11bb  bfff ffff    LITERAL AND CONTROL OPERATIONS  Interal with W  1  11  111  111k kkkk  kkkk  Z    ADDLW  k  Add literal and W  1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MOVF      | f, d  | Move f                      | -      | 00 | 1000   | dfff   | ffff | Z        | 1,2   |

| RLF  f, d  Rotate Leff through Carry  1  00  1101  dff ffff  C    RRF  f, d  State Right f through Carry  1  00  1101  dff ffff  C    SUBWF  f, d  Subtract W from f  1  00  1100  dff ffff  C  C,DC,Z    SWAPF  f, d  Swap nibbles in f  1  00  1101  dff ffff  C,DC,Z    SWAPF  f, d  Swap nibbles in f  1  00  1101  dff ffff  C,DC,Z    SWAPF  f, d  Swap nibbles in f  1  00  1101  dff ffff  Z    BIT-ORIENTED FILE  REGISTER OPERATIONS  I  1  01  00bb  bfff  ffff    BTFSS  f, b  Bit Test f, Skip if Clear  1  1  11  111b  bfff  ffff    LITERAL AND CONTROL OPERATIONS  I  11  111  1111  111k  kkkk kkkk  Z    CALL k  Calls subroutine  2  10 <td></td> <td>f</td> <td></td> <td>-</td> <td>00</td> <td>0000</td> <td>lfff</td> <td>ffff</td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           | f     |                             | -      | 00 | 0000   | lfff   | ffff |          |       |

| RRFf, dRotate Right f through Carry1001100dfffffffCSUBWFf, dSubtract W from f1000010dfffffffC,DC,ZSWAPFf, dSwap nibbles in f1001110dfffffffC,DC,ZSWAPFf, dExclusive OR W with f1000110dfffffffZBIT-ORIENTED FILEREGISTER OPERATIONSBCFf, bBit Clear f10100bbbfffffffBSFf, bBit Set f10110bbbfffffffBTFSSf, bBit Test f, Skip if Clear1 (2)0111bbbfffffffBTFSSf, bBit Test f, Skip if Set1 (2)0111bbbfffffffLITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111kkkkkkkkZADDLWkAdd literal and W111111kkkk kkkkZClaulkCall subroutine2100kkk kkkkkTO,PDGOTOkGo to address2101kkk kkkkkZIORLWkInclusive OR literal with W1111000kkkk kkkkRETURReturn from interrupt20000000100IO,PDRETURNReturn from Subroutine200000000001000SLEEPGo into standby mode100 <td< td=""><td>NOP</td><td>-</td><td>No Operation</td><td>-</td><td>00</td><td>0000</td><td>0xx0</td><td>0000</td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | NOP       | -     | No Operation                | -      | 00 | 0000   | 0xx0   | 0000 |          |       |

| SUBWFf, dSubtract W from f1000010dfffffffC,DC,ZSWAPFf, dSwap nibbles in f1001110dfffffffZBIT-ORIENTED FILE REGISTER OPERATIONSBCFf, bBit Clear f10100bbbfffffffBSFf, bBit Clear f10101bbbfffffffBTFSCf, bBit Test f, Skip if Clear1 (2)0110bbbfffffffBTFSSf, bBit Test f, Skip if Set1 (2)0111bbbfffffffLITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111111xkkkkkkkkZCALLkCall subroutine2100kkkkkkkZCALLkGo to address2101kkkkkkkZGOTOkGo to address210111100xkkkkZMOVLWkInclusive OR literal with W1111100xkkkkZMOVLWkReturn from interrupt20000001001TO,PDRETFIE-Return from interrupt21101xxkkkkkkkkRETURN-Return from Subroutine21101xxkkkkkkkkRETURN-Go into standby mode10000000101TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RLF       | ,     | <b>o</b> ,                  | -      | 00 | 1101   | dfff   | ffff | С        | 1,2   |

| SWAPFf, dSwap nibbles in f1001110dfffffffZBIT-ORIENTED FILE REGISTER OPERATIONSBCFf, bBit Clear f10100bbbfffffffZBSFf, bBit Clear f10101bbbfffffffZBTFSCf, bBit Test f, Skip if Clear110101bbbfffffffBTFSSf, bBit Test f, Skip if Set1120111bbbfffFfffLITERAL AND COVTROL OPERATIONSADDLWkAdd literal and W111111101kkkkkkkkZCALLkCall subroutine2100kkkkkkkKkkZCALLkCall subroutine2101kkkkkkkZGo to address2101kkkkkkkZOVUW1111000kkkkKkkZMOVLW1110000000001001Return from interrupt200000000001001Return from subroutine21101xxkkkkkkkRETURN -Return from Subroutine20000001001Go into standby mode10000000101 <td>RRF</td> <td>,</td> <td></td> <td></td> <td>00</td> <td>1100</td> <td>dfff</td> <td>ffff</td> <td>-</td> <td>1,2</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RRF       | ,     |                             |        | 00 | 1100   | dfff   | ffff | -        | 1,2   |

| XORWFf, dExclusive OR W with f1000110dfffffffZBIT-ORIENTED FILE REGISTER OPERATIONSBCFf, bBit Clear f10100bbbffffffffBSFf, bBit Set f10101bbbffffffffBTFSCf, bBit Test f, Skip if Clear1 (2)0110bbbffffffffBTFSSf, bBit Test f, Skip if Set1 (2)0111bbbfffffffLITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111111xkkkkkkkkZCALLkCall subroutine2100kkkkkkkZTO,PDGOTOkGo to address2101kkkkkkkKkkkZMOVLWkInclusive OR literal with W11100xkkkkKkkkZMOVLWkReturn from interrupt20000000001TO,PDRETFIE-Return from Subroutine21101xxkkkkKkkkFO,PDRETURN-Return from Subroutine200000000001001TO,PDRETURN-Return from Subroutine200000000001001TO,PDRETER-Go into standby mode10000001001TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SUBWF     | f, d  | Subtract W from f           | -      | 00 | 0010   | dfff   | ffff | C,DC,Z   | 1,2   |

| Bit Clear fBSFf, bBit Clear f10100bbbfffffffBFFSCf, bBit Test f, Skip if Clear1 (2)0110bbbfffffffBTFSCf, bBit Test f, Skip if Clear1 (2)0110bbbfffffffBTFSSf, bBit Test f, Skip if Set1 (2)0110bbbfffffffLITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111111.kkkkkkkkZCALLkAdd literal and W1111001kkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkZCALLkGo to address210111000kkkkkkkkZGOTOkGo to address210111000kkkkZMOVLWkInclusive OR literal with W1111000kkkkZMOVLWkReturn from interrupt20000001001TO,PDGo into standby mode101000000001001TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SWAPF     | f, d  | Swap nibbles in f           |        | 00 | 1110   | dfff   | ffff |          | 1,2   |

| BCFf, bBit Clear f10100bbbfffffffBSFf, bBit Set f10101bbbfffffffBTFSCf, bBit Test f, Skip if Clear110101bbbfffffffBTFSSf, bBit Test f, Skip if Set11111bbbfffffffLITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111 xkkkkkkkZADDLWkAdd literal with W1111001 kkkkkkkkC,DC,ZCALLkCall subroutine2100000001101000GOTOkGo to address2101kkkkkkkkkkkZIORLWkInclusive OR literal with W1111000 kkkkkkkkZMOVLWkReturn from interrupt200000000001001RETFIE-Return with literal in W21101xxkkkkkkkkKRETURN-Return from Subroutine200000000001000SLEEP-Go into standby mode10000000110TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -         |       |                             | 1      | 00 | 0110   | dfff   | ffff | Z        | 1,2   |

| BSFf, bBit Set f10101bbbfffffffBTFSCf, bBit Test f, Skip if Clear110110bbbfffffffBTFSSf, bBit Test f, Skip if Set110110bbbfffffffLITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111kkkkkkkC,DC,ZADDLWkAdd literal with W1111001kkkkkkkkZCALLkCall subroutine210000001100100TO,PDGOTOkGo to address21011kkkkkkkkkkkkZIORLWkInclusive OR literal with W1111000kkkkKkkkZMOVLWkReturn from interrupt200000000011001TO,PDRETLWkReturn with literal in W21101xxkkkkkkkkKkkkRETURN-Return from Subroutine200000000001001TO,PDSLEEP-Go into standby mode100000001100101TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -         |       |                             |        |    |        |        |      |          |       |

| BTFSC<br>BTFSSf, b<br>bBit Test f, Skip if Clear<br>Bit Test f, Skip if Set1 (2)<br>1 (2)0110bbbfffffffLITERAL AND CONTROL OPERATIONSADDLW<br>ANDLW<br>CALLkAdd literal and W111111111xkkkkkkkkC,DC,ZADDLW<br>ANDLWkAdd literal with W1111111001kkkkkkkkZCALL<br>CALL<br>GOTO<br>GOTO<br>GOTO<br>GOTO<br>KCall subroutine<br>Go to address2100kkkkkkkkkkkZTO,PDGOTO<br>GOTO<br>GOTO<br>GOTO<br>KGo to address2101kkkkkkkZIORLW<br>KInclusive OR literal with W1111000kkkkKkkkZMOVLW<br>RETFIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE<br>FTIE <br< td=""><td></td><td>,</td><td></td><td></td><td>01</td><td>00bb</td><td></td><td></td><td></td><td>1,2</td></br<> |           | ,     |                             |        | 01 | 00bb   |        |      |          | 1,2   |

| BTFSSf, bBit Test f, Skip if Set1 (2)0111bbbfffffffLITERAL AND COVERATIONSADDLWkAdd literal and W111111 x kkkkkkkkC,DC,ZANDLWkAND literal with W111111 x kkkkkkkkC,DC,ZCALLkCall subroutine2100kkkkkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkZGOTOkGo to address2101kkkkkkkkkkkZIORLWkInclusive OR literal with W1111000kkkkKkkkZMOVLWkMove literal to W1111000kkkkkkkkZRETFIE-Return from interrupt200000000011001RETLWkReturn from Subroutine200000000001000SLEEP-Go into standby mode10000000110TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -         |       |                             | -      | 01 | 01bb   | bfff   | ffff |          | 1,2   |

| LITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111 111xkkkkkkkkC,DC,ZANDLWkAND literal with W1111001kkkkkkkkC,DC,ZCALLkCall subroutine2100kkkkkkkkkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkZCALLkCall subroutine21000000011001000GOTOkGo to address2101kkkkkkkkkkkZIORLWkInclusive OR literal with W1111000kkkkkkkkZMOVLWkMove literal to W1110000000001001Return from interrupt200000000010011RETLIPReturn from interrupt20000000000100010001000SLEEP-Go into standby mode100000001101001TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |       |                             |        | 01 | 10bb   | bfff   | ffff |          | 3     |

| ADDLWkAdd literal and W111111 x kkkkkkkkC,DC,ZANDLWkAND literal with W1111001 kkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkZCLRWDT-Clear Watchdog Timer100000001100100TO,PDGOTOkGo to address2101kkkkkkkkkkkZIORLWkInclusive OR literal with W1111000kkkkkkkkZMOVLWkMove literal to W1110000000001001RETFIE-Return from interrupt200000000001001RETURN-Return with literal in W21101xxkkkkkkkkRETURN-Return from Subroutine200000000001000TO,PDSLEEP-Go into standby mode10000000110011TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |       |                             | 1 (2)  | 01 | 11bb   | bfff   | ffff |          | 3     |

| ANDLWkAND literal with W1111001kkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkKkkkZCLRWDT-Clear Watchdog Timer100000001100100TO,PDGOTOkGo to address2101kkkkkkkkkkkKkkkZIORLWkInclusive OR literal with W1111000kkkkkkkkZMOVLWkMove literal to W111000000001001RETFIE-Return from interrupt200000000001001RETLWReturn with literal in W21101xxkkkkkkkkRETURN-Return from Subroutine200000000001000TO,PDSLEEP-Go into standby mode100000001100011TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           | ND CO |                             |        |    |        |        |      |          | •     |