Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | · .                                                                        |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

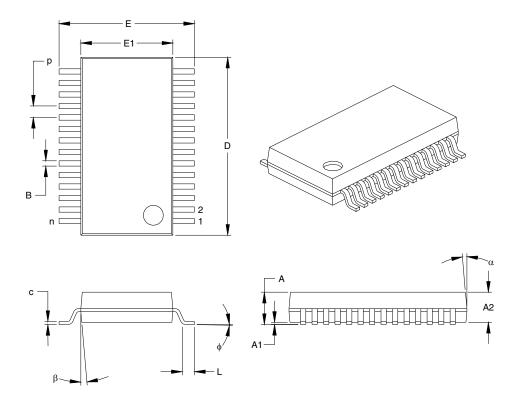

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c72a-04e-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

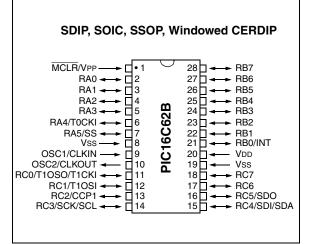

### **Pin Diagrams**

| Key Features<br>PIC <sup>®</sup> Mid-Range Reference Manual (DS33023) | PIC16C62B            | PIC16C72A            |

|-----------------------------------------------------------------------|----------------------|----------------------|

| Operating Frequency                                                   | DC - 20 MHz          | DC - 20 MHz          |

| Resets (and Delays)                                                   | POR, BOR (PWRT, OST) | POR, BOR (PWRT, OST) |

| Program Memory (14-bit words)                                         | 2K                   | 2K                   |

| Data Memory (bytes)                                                   | 128                  | 128                  |

| Interrupts                                                            | 7                    | 8                    |

| I/O Ports                                                             | Ports A,B,C          | Ports A,B,C          |

| Timers                                                                | 3                    | 3                    |

| Capture/Compare/PWM modules                                           | 1                    | 1                    |

| Serial Communications                                                 | SSP                  | SSP                  |

| 8-bit Analog-to-Digital Module                                        | —                    | 5 input channels     |

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets; core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral feature section.

| Addr    | Name                    | Bit 7              | Bit 6                               | Bit 5         | Bit 4          | Bit 3           | Bit 2           | Bit 1        | Bit 0         | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(4) |

|---------|-------------------------|--------------------|-------------------------------------|---------------|----------------|-----------------|-----------------|--------------|---------------|--------------------------|-------------------------------------|

| Bank 0  |                         |                    |                                     |               | •              |                 |                 |              |               |                          |                                     |

| 00h     | INDF <sup>(1)</sup>     | Addressing         | this locatio                        | n uses conte  | ents of FSR    | to address d    | ata memory      | (not a physi | cal register) | 0000 0000                | 0000 0000                           |

| 01h     | TMR0                    | Timer0 mo          | dule's regist                       | er            |                |                 |                 |              |               | xxxx xxxx                | uuuu uuuu                           |

| 02h     | PCL <sup>(1)</sup>      | Program C          | ounter's (PC                        | C) Least Sig  | nificant Byte  | !               |                 |              |               | 0000 0000                | 0000 0000                           |

| 03h     | STATUS <sup>(1)</sup>   | IRP <sup>(5)</sup> | RP1 <sup>(5)</sup>                  | RP0           | TO             | PD              | Z               | DC           | С             | 0001 1xxx                | 000q quuu                           |

| 04h     | FSR <sup>(1)</sup>      | Indirect dat       | a memory a                          | ddress poir   | nter           |                 |                 |              |               | xxxx xxxx                | uuuu uuuu                           |

| 05h     | PORTA <sup>(6,7)</sup>  | —                  | _                                   | PORTA Da      | ta Latch whe   | en written: P   | ORTA pins w     | hen read     |               | 0x 0000                  | 0u 0000                             |

| 06h     | PORTB <sup>(6,7)</sup>  | PORTB Da           | ta Latch wh                         | en written: F | PORTB pins     | when read       |                 |              |               | xxxx xxxx                | uuuu uuuu                           |

| 07h     | PORTC <sup>(6,7)</sup>  | PORTC Da           | ita Latch wh                        | en written: I | PORTC pins     | when read       |                 |              |               | xxxx xxxx                | uuuu uuuu                           |

| 08h-09h | _                       | Unimpleme          | ented                               |               |                |                 |                 |              |               | —                        | —                                   |

| 0Ah     | PCLATH <sup>(1,2)</sup> | _                  | _                                   | _             | Write Buffe    | r for the uppe  | er 5 bits of th | e Program (  | Counter       | 0 0000                   | 0 0000                              |

| 0Bh     | INTCON <sup>(1)</sup>   | GIE                | PEIE                                | TOIE          | INTE           | RBIE            | TOIF            | INTF         | RBIF          | 0000 000x                | 0000 000u                           |

| 0Ch     | PIR1                    | —                  | ADIF <sup>(3)</sup>                 | _             | _              | SSPIF           | CCP1IF          | TMR2IF       | TMR1IF        | -0 0000                  | -0 0000                             |

| 0Dh     | _                       | Unimpleme          | ented                               |               |                |                 |                 |              |               | —                        | —                                   |

| 0Eh     | TMR1L                   | Holding reg        | jister for the                      | Least Signi   | ificant Byte o | of the 16-bit 1 | MR1 registe     | r            |               | xxxx xxxx                | uuuu uuuu                           |

| 0Fh     | TMR1H                   | Holding reg        | jister for the                      | Most Signif   | icant Byte o   | f the 16-bit T  | MR1 register    | r            |               | xxxx xxxx                | uuuu uuuu                           |

| 10h     | T1CON                   | _                  | —                                   | T1CKPS1       | T1CKPS0        | T1OSCEN         | T1SYNC          | TMR1CS       | TMR1ON        | 00 0000                  | uu uuuu                             |

| 11h     | TMR2                    | Timer2 mo          | dule's regist                       | er            |                |                 |                 |              |               | 0000 0000                | 0000 0000                           |

| 12h     | T2CON                   | _                  | TOUTPS3                             | TOUTPS2       | TOUTPS1        | TOUTPS0         | TMR2ON          | T2CKPS1      | T2CKPS0       | -000 0000                | -000 0000                           |

| 13h     | SSPBUF                  | Synchrono          | us Serial Po                        | rt Receive E  | Buffer/Transr  | nit Register    |                 |              |               | xxxx xxxx                | uuuu uuuu                           |

| 14h     | SSPCON                  | WCOL               | SSPOV                               | SSPEN         | СКР            | SSPM3           | SSPM2           | SSPM1        | SSPM0         | 0000 0000                | 0000 0000                           |

| 15h     | CCPR1L                  | Capture/Co         | Capture/Compare/PWM Register1 (LSB) |               |                |                 |                 |              | xxxx xxxx     | uuuu uuuu                |                                     |

| 16h     | CCPR1H                  | Capture/Co         | Capture/Compare/PWM Register1 (MSB) |               |                |                 |                 | xxxx xxxx    | uuuu uuuu     |                          |                                     |

| 17h     | CCP1CON                 | —                  | _                                   | CCP1X         | CCP1Y          | CCP1M3          | CCP1M2          | CCP1M1       | CCP1M0        | 00 0000                  | 00 0000                             |

| 18h-1Dh | _                       | Unimplemented —    |                                     |               |                |                 |                 | —            | —             |                          |                                     |

| 1Eh     | ADRES <sup>(3)</sup>    | A/D Result         | A/D Result Register xxxx            |               |                |                 |                 | xxxx xxxx    | uuuu uuuu     |                          |                                     |

| 1Fh     | ADCON0 <sup>(3)</sup>   | ADCS1              | ADCS0                               | CHS2          | CHS1           | CHS0            | GO/DONE         | —            | ADON          | 0000 00-0                | 0000 00-0                           |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0',

Shaded locations are unimplemented, read as '0'. **Note 1:** These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: A/D not implemented on the PIC16C62B, maintain as '0'.

4: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

5: The IRP and RP1 bits are reserved. Always maintain these bits clear.

6: On any device reset, these pins are configured as inputs.

7: This is the value that will be in the port output latch.

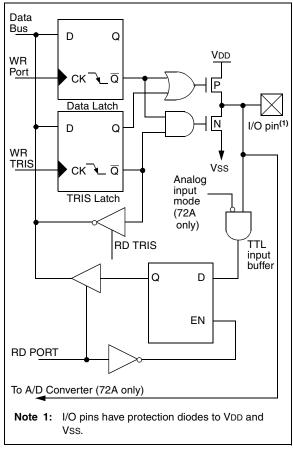

## 3.0 I/O PORTS

Some I/O port pins are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

### 3.1 PORTA and the TRISA Register

PORTA is a 6-bit wide bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (=1) will make the corresponding PORTA pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISA bit (=0) will make the corresponding PORTA pin an output, (i.e., put the contents of the output latch on the selected pin).

The PORTA register reads the state of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

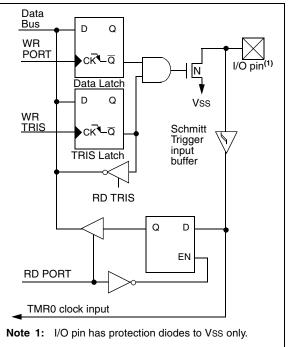

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers.

Pin RA5 is multiplexed with the SSP to become the RA5/SS pin.

On the PIC16C72A device, other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

| Note: | On a Power-on Reset, pins with analog           |

|-------|-------------------------------------------------|

|       | functions are configured as analog inputs       |

|       | with digital input buffers disabled . A digital |

|       | read of these pins will return '0'.             |

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

### FIGURE 3-1: BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

### FIGURE 3-2: BLOCK DIAGRAM OF RA4/T0CKI PIN

© 1998-2013 Microchip Technology Inc.

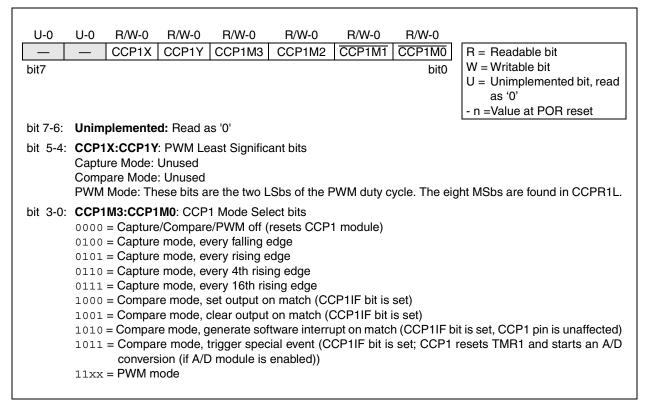

### 7.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The CCP (Capture/Compare/PWM) module contains a 16-bit register, which can operate as a 16-bit capture register, as a 16-bit compare register or as a PWM master/slave duty cycle register. Table 7-1 shows the timer resources of the CCP module modes.

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable. Additional information on the CCP module is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

# TABLE 7-1CCP MODE - TIMER<br/>RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

### TABLE 7-2INTERACTION OF TWO CCP MODULES

| CCPx Mode | CCPy Mode | Interaction                                                                           |

|-----------|-----------|---------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time-base.                                                                  |

| Capture   | Compare   | The compare should be configured for the special event trigger, which clears TMR1.    |

| Compare   | Compare   | The compare(s) should be configured for the special event trigger, which clears TMR1. |

| PWM       | PWM       | The PWMs will have the same frequency and update rate (TMR2 interrupt).               |

| PWM       | Capture   | None.                                                                                 |

| PWM       | Compare   | None.                                                                                 |

### **REGISTER 7-1:CCP1CON REGISTER (ADDRESS 17h)**

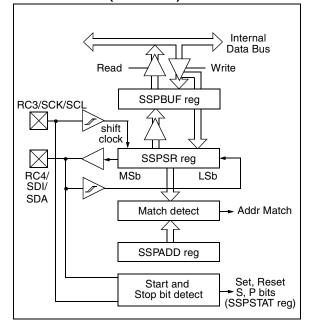

## 8.3 <u>SSP I<sup>2</sup>C Operation</u>

The SSP module in I<sup>2</sup>C mode fully implements all slave functions, except general call support, and provides interrupts on start and stop bits in hardware to support firmware implementations of the master functions. The SSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RC3/SCK/SCL pin, which is the clock (SCL), and the RC4/SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

The SSP module functions are enabled by setting SSP Enable bit SSPEN (SSPCON<5>).

FIGURE 8-2: SSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

The SSP module has five registers for  $I^2C$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with start and stop bit interrupts enabled for firmware master mode support

- I<sup>2</sup>C Slave mode (10-bit address), with start and stop bit interrupts enabled for firmware master mode support

- I<sup>2</sup>C start and stop bit interrupts enabled for firmware master mode support, slave mode idle

Selection of any  $I^2C$  mode, with the SSPEN bit set, forces the SCL and SDA pins to be operated as open drain outputs, provided these pins are programmed to inputs by setting the appropriate TRISC bits.

Additional information on SSP I<sup>2</sup>C operation may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

### 8.3.1 SLAVE MODE

In slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched or the data transfer after an address match is received, the hardware automatically will generate the acknowledge ( $\overline{ACK}$ ) pulse, and load the SSPBUF register with the received value in the SSPSR register.

There are certain conditions that will cause the SSP module not to give this  $\overline{ACK}$  pulse. This happens if either of the following conditions occur:

- a) The buffer full bit BF (SSPSTAT<0>) was set before the transfer was completed.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was completed.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. Table 8-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the SSP module, is shown in timing parameter #100, THIGH, and parameter #101, TLOW.

NOTES:

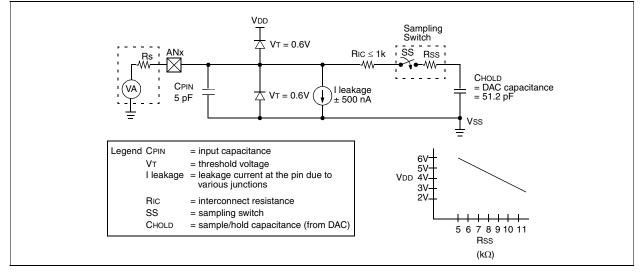

### 9.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 9-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 10 k $\Omega$ . After the analog input channel is selected (changed), this acquisition must pass before the conversion can be started.

To calculate the minimum acquisition time, TACQ, see Equation 9-1. This equation calculates the acquisition time to within 1/2 LSb error (512 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified accuracy.

| Note: | When the conversion is started, the hold-         |  |  |  |  |  |

|-------|---------------------------------------------------|--|--|--|--|--|

|       | ing capacitor is disconnected from the input pin. |  |  |  |  |  |

|       | input pin.                                        |  |  |  |  |  |

In general;

Assuming Rs =  $10k\Omega$

Vdd =

$$3.0V$$

(Rss =  $10k\Omega$ )

TACQ  $\approx~13.0~\mu Sec$

By increasing VDD and reducing Rs and Temp., TACQ can be substantially reduced.

### FIGURE 9-2: ANALOG INPUT MODEL

### EQUATION 9-1: ACQUISITION TIME

- TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient

- = TAMP + TC + TCOFF TAMP =  $5\mu S$ TC = -  $(51.2pF)(1k\Omega + Rss + Rs) In(1/511)$ TCOFF =  $(Temp - 25^{\circ}C)(0.05\mu S/^{\circ}C)$

| TABLE 10-6 INITIALIZATION CONDITIONS FOR ALL REGISTERS |     |               |                                    |                          |                                 |  |

|--------------------------------------------------------|-----|---------------|------------------------------------|--------------------------|---------------------------------|--|

| Register                                               |     | cable<br>ices | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT or<br>Interrupt |  |

| W                                                      | 62B | 72A           | XXXX XXXX                          | uuuu uuuu                | սսսս սսսս                       |  |

| INDF                                                   | 62B | 72A           | N/A                                | N/A                      | N/A                             |  |

| TMR0                                                   | 62B | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| PCL                                                    | 62B | 72A           | 0000h                              | 0000h                    | PC + 1 <sup>(2)</sup>           |  |

| STATUS                                                 | 62B | 72A           | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu <b>(3)</b>            |  |

| FSR                                                    | 62B | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |

| PORTA <sup>(4)</sup>                                   | 62B | 72A           | 0x 0000                            | 0u 0000                  | uu uuuu                         |  |

| PORTB <sup>(5)</sup>                                   | 62B | 72A           | xxxx xxxx                          | uuuu uuuu                | սսսս սսսս                       |  |

| PORTC <sup>(5)</sup>                                   | 62B | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| PCLATH                                                 | 62B | 72A           | 0 0000                             | 0 0000                   | u uuuu                          |  |

| INTCON                                                 | 62B | 72A           | 0000 000x                          | 0000 000u                | uuuu uuuu <b>(1)</b>            |  |

|                                                        | 62B | 72A           | 0000                               | 0000                     | uuuu <b>(1)</b>                 |  |

| PIR1                                                   | 62B | 72A           | -0 0000                            | -0 0000                  | -u uuuu <b>(1)</b>              |  |

| TMR1L                                                  | 62B | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| TMR1H                                                  | 62B | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| T1CON                                                  | 62B | 72A           | 00 0000                            | uu uuuu                  | uu uuuu                         |  |

| TMR2                                                   | 62B | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |

| T2CON                                                  | 62B | 72A           | -000 0000                          | -000 0000                | -uuu uuuu                       |  |

| SSPBUF                                                 | 62B | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |

| SSPCON                                                 | 62B | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |

| CCPR1L                                                 | 62B | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |

| CCPR1H                                                 | 62B | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| CCP1CON                                                | 62B | 72A           | 00 0000                            | 00 0000                  | uu uuuu                         |  |

| ADRES                                                  | 62B | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |

| ADCON0                                                 | 62B | 72A           | 0000 00-0                          | 0000 00-0                | uuuu uu-u                       |  |

| OPTION_REG                                             | 62B | 72A           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |  |

| TRISA                                                  | 62B | 72A           | 11 1111                            | 11 1111                  | uu uuuu                         |  |

| TRISB                                                  | 62B | 72A           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |  |

| TRISC                                                  | 62B | 72A           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |  |

|                                                        | 62B | 72A           | 0000                               | 0000                     | uuuu                            |  |

| PIE1                                                   | 62B | 72A           | -0 0000                            | -0 0000                  | -u uuuu                         |  |

| PCON                                                   | 62B | 72A           | 0q                                 | uq                       | uq                              |  |

| PR2                                                    | 62B | 72A           | 1111 1111                          | 1111 1111                | 1111 1111                       |  |

| SSPADD                                                 | 62B | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |

| SSPSTAT                                                | 62B | 72A           | 0000 0000                          | 0000 0000                | սսսս սսսս                       |  |

| ADCON1                                                 | 62B | 72A           | 000                                | 000                      | uuu                             |  |

| TABLE 10-6 | INITIALIZATION CONDITIONS FOR ALL REGISTERS |

|------------|---------------------------------------------|

|            |                                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', <math>q = value depends on condition

Note 1: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

**3:** See Table 10-5 for reset value for specific condition.

4: On any device reset, these pins are configured as inputs.

5: This is the value that will be in the port output latch.

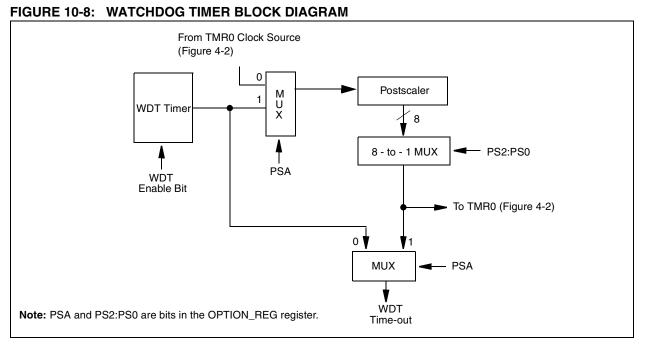

### 10.12 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. The WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit WDTE (Section 10.1).

The WDT time-out period (TWDT, parameter #31) is multiplied by the prescaler ratio, when the prescaler is assigned to the WDT. The prescaler assignment (assigned to either the WDT or Timer0) and prescaler ratio are set in the OPTION\_REG register.

Note: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

**Note:** When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

### FIGURE 10-9: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name         | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|--------------|-------|--------|-------|-------|-------|-------|-------|-------|

| 2007h   | Config. bits |       | BODEN  | CP1   | CP0   | PWRTE | WDTE  | FOSC1 | FOSC0 |

| 81h     | OPTION_REG   | RBPU  | INTEDG | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

# 11.1 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                       |

|------------------|-------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                |

| Operands:        | $0 \leq k \leq 255$                                                                                                     |

| Operation:       | $(W) + k \to (W)$                                                                                                       |

| Status Affected: | C, DC, Z                                                                                                                |

| Description:     | The contents of the W register are<br>added to the eight bit literal 'k' and the<br>result is placed in the W register. |

| ANDWF            | AND W with f                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                             |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                   |

| Status Affected: | Z                                                                                                                                                           |

| Description:     | AND the W register with register 'f'. If<br>'d' is 0, the result is stored in the W<br>register. If 'd' is 1, the result is stored<br>back in register 'f'. |

| ADDWF            | Add W and f                                                                                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                             |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                       |

| Status Affected: | C, DC, Z                                                                                                                                                                    |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result is<br>stored in the W register. If 'd' is 1, the<br>result is stored back in register 'f'. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BCF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ANDLW            | AND Literal with W                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                            |

| Operands:        | $0 \le k \le 255$                                                                                                   |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                     |

| Status Affected: | Z                                                                                                                   |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal 'k'.<br>The result is placed in the W register. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

# PIC16C62B/72A

| IORLW            | Inclusive OR Literal with W                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] IORLW k                                                                                                     |

| Operands:        | $0 \le k \le 255$                                                                                                     |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                          |

| Status Affected: | Z                                                                                                                     |

| Description:     | The contents of the W register is<br>OR'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |

| MOVLW            | Move Literal to W                                                                          |

|------------------|--------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                        |

| Operation:       | $k \rightarrow (W)$                                                                        |

| Status Affected: | None                                                                                       |

| Description:     | The eight bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |

| IORWF            | Inclusive OR W with f                                                                                                                                                  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] IORWF f,d                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                            |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                               |

| Status Affected: | Z                                                                                                                                                                      |

| Description:     | Inclusive OR the W register with regis-<br>ter 'f'. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>placed back in register 'f'. |

| MOVWF            | Move W to f                           |

|------------------|---------------------------------------|

| Syntax:          | [label] MOVWF f                       |

| Operands:        | $0 \leq f \leq 127$                   |

| Operation:       | $(W) \rightarrow (f)$                 |

| Status Affected: | None                                  |

| Description:     | Move data from W register to register |

| MOVF             | Move f                                                                                                                                                                                                                                                                                |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                           |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                                       |

| Status Affected: | Z                                                                                                                                                                                                                                                                                     |

| Description:     | The contents of register f is moved to<br>a destination dependant upon the sta-<br>tus of d. If $d = 0$ , destination is W reg-<br>ister. If $d = 1$ , the destination is file<br>register f itself. $d = 1$ is useful to test a<br>file register since status flag Z is<br>affected. |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

|                                                           | PIC12CXX | PIC14000 | PIC16C5X | PIC16C6X | PIC16CXX | PIC16F62 | X7381319 | X7Oðfolg | PIC16C8X | PIC16F8X | X6D91DI9 | (\$3712)q | (X73713I9 | PIC18CXX | 63CXX<br>52CXX/<br>54CXX/ | хххсэн | мсяғххя | MCP2510 |

|-----------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|-----------|-----------|----------|---------------------------|--------|---------|---------|

| MPLAB™ Integrated<br>Development Environment              | >        | >        | >        | >        | >        | >        | `        | >        | `        | >        | >        | >         | >         | >        |                           |        |         |         |

| MPLAB™ C17 Compiler                                       |          |          |          |          |          |          |          |          |          |          |          | >         | >         |          |                           |        |         |         |

| MPLAB™ C18 Compiler                                       |          |          |          |          |          |          |          |          |          |          |          |           |           | >        |                           |        |         |         |

| MPASM/MPLINK                                              | >        | >        | >        | >        | >        | >        | >        | >        | >        | >        | >        | >         | >         | >        | >                         | >      |         |         |

| MPLAB <sup>TM-</sup> ICE                                  | >        | >        | >        | >        | >        | **^      | >        | >        | >        | >        | >        | >         | >         | >        |                           |        |         |         |

| PICMASTER/PICMASTER-CE                                    | ~        | >        | >        | >        | >        |          | >        | >        | >        |          | >        | >         | >         |          |                           |        |         |         |

| In-Circuit Emulator                                       | >        |          | >        | >        | >        |          | >        | >        | >        |          | >        |           |           |          |                           |        |         |         |

| et<br>MPLAB-ICD In-Circuit Debugger<br>De                 |          |          |          | *        |          |          | *>       |          |          | >        |          |           |           |          |                           |        |         |         |

| PICSTART <sup>®</sup> Plus<br>Low-Cost Universal Dev. Kit | ^        | `        | >        | ~        | ~        | **^      | >        | >        | `        | `        | `        | ~         | ~         | >        |                           |        |         |         |

| ଖେମ୍ମ PRO MATE® I<br>Universal Programmer<br>ଦି           | >        | >        | >        | >        | >        | **>      | >        | >        | >        | >        | >        | >         | >         | >        | >                         | >      |         |         |

| SIMICE                                                    | ^        |          | ~        |          |          |          |          |          |          |          |          |           |           |          |                           |        |         |         |

| PICDEM-1                                                  |          |          | >        |          | >        |          | ⁺,       |          | >        |          |          | >         |           |          |                           |        |         |         |

| PICDEM-2                                                  |          |          |          | <⁺       |          |          | ✓†       |          |          |          |          |           |           | ^        |                           |        |         |         |

| PICDEM-3                                                  |          |          |          |          |          |          |          |          |          |          | ~        |           |           |          |                           |        |         |         |

| PICDEM-14A                                                |          | >        |          |          |          |          |          |          |          |          |          |           |           |          |                           |        |         |         |

| PICDEM-17                                                 |          |          |          |          |          |          |          |          |          |          |          |           | >         |          |                           |        |         |         |

| KEELoo <sup>®</sup> Evaluation Kit                        |          |          |          |          |          |          |          |          |          |          |          |           |           |          |                           | >      |         |         |

| KEELoo Transponder Kit                                    |          |          |          |          |          |          |          |          |          |          |          |           |           |          |                           | >      |         |         |

| microID <sup>TM</sup> Programmer's Kit                    |          |          |          |          |          |          |          |          |          |          |          |           |           |          |                           |        | `       |         |

| 125 kHz microlD Developer's Kit                           |          |          |          |          |          |          |          |          |          |          |          |           |           |          |                           |        | >       |         |

| 125 kHz Anticollision microlD<br>Developer's Kit          |          |          |          |          |          |          |          |          |          |          |          |           |           |          |                           |        | >       |         |

| 13.56 MHz Anticollision microID<br>Developer's Kit        |          |          |          |          |          |          |          |          |          |          |          |           |           |          |                           |        | >       |         |

| MCP2510 CAN Developer's Kit                               |          |          |          |          |          |          |          |          |          |          |          |           |           |          |                           |        |         | >       |

TABLE 12-1: DEVELOPMENT TOOLS FROM MICROCHIP

$\ensuremath{\textcircled{}^{\circ}}$  1998-2013 Microchip Technology Inc.

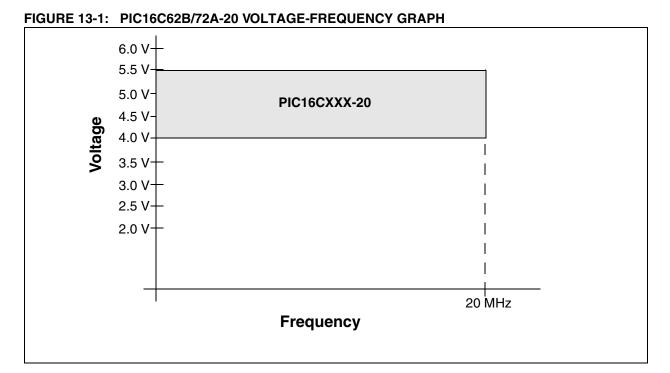

# **13.0 ELECTRICAL CHARACTERISTICS**

### Absolute Maximum Ratings (†)

| Ambient temperature under bias                                                                                   | 55°C to +125°C               |

|------------------------------------------------------------------------------------------------------------------|------------------------------|

| Storage temperature                                                                                              |                              |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)                                               |                              |

| Voltage on VDD with respect to VSS                                                                               |                              |

| Voltage on MCLR with respect to Vss (Note 2)                                                                     |                              |

| Voltage on RA4 with respect to Vss                                                                               |                              |

| Total power dissipation (Note 1)                                                                                 |                              |

| Maximum current out of Vss pin                                                                                   |                              |

| Maximum current into VDD pin                                                                                     |                              |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                                     |                              |

| Output clamp current, Ioк (Vo < 0 or Vo > VDD)                                                                   |                              |

| Maximum output current sunk by any I/O pin                                                                       | 25 mA                        |

| Maximum output current sourced by any I/O pin                                                                    | 25 mA                        |

| Maximum current sunk by PORTA and PORTB (combined)                                                               |                              |

| Maximum current sourced by PORTA and PORTB (combined)                                                            | 200 mA                       |

| Maximum current sunk by PORTC                                                                                    | 200 mA                       |

| Maximum current sourced by PORTC                                                                                 | 200 mA                       |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-Value) | OH) x IOH} + $∑$ (VOI x IOL) |

**2:** Voltage spikes below Vss at the MCLR/VPP pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR/VPP pin, rather than pulling this pin directly to Vss.

**†** NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# 13.3 DC Characteristics:

### cs: PIC16C62B/72A-04 (Commercial, Industrial, Extended) PIC16C62B/72A-20 (Commercial, Industrial, Extended) PIC16LC62B/72A-04 (Commercial, Industrial)

| DC CHA        | RISTICS | $\begin{array}{rl} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C & \leq TA \leq +70^{\circ}C & \mbox{for commercial} \\ & -40^{\circ}C & \leq TA \leq +85^{\circ}C & \mbox{for industrial} \\ & -40^{\circ}C & \leq TA \leq +125^{\circ}C & \mbox{for extended} \\ \\ \mbox{Operating voltage VDD range as described in DC spec Section 13.7} \\ \mbox{and Section 13.2} \end{array}$ |                    |      |                 |        |                                                                                                    |  |

|---------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|-----------------|--------|----------------------------------------------------------------------------------------------------|--|

| Param<br>No.  | Sym     | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                      | Min                | Тур† | Max             | Units  | Conditions                                                                                         |  |

|               |         | Input Low Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |      |                 |        |                                                                                                    |  |

|               | VIL     | I/O ports                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    |      |                 |        |                                                                                                    |  |

| D030<br>D030A |         | with TTL buffer                                                                                                                                                                                                                                                                                                                                                                                                                                     | Vss<br>Vss         | -    | 0.15Vdd<br>0.8V | V<br>V | For entire VDD range $4.5V \le VDD \le 5.5V$                                                       |  |

| D031          |         | with Schmitt Trigger buffer                                                                                                                                                                                                                                                                                                                                                                                                                         | Vss                | -    | 0.2Vdd          | V      |                                                                                                    |  |

| D032          |         | MCLR, OSC1 (in RC mode)                                                                                                                                                                                                                                                                                                                                                                                                                             | Vss                | -    | 0.2Vdd          | V      |                                                                                                    |  |

| D033          |         | OSC1 (in XT, HS and LP modes)                                                                                                                                                                                                                                                                                                                                                                                                                       | Vss                | -    | 0.3Vdd          | V      | Note1                                                                                              |  |

|               |         | Input High Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |      |                 |        |                                                                                                    |  |

|               | Vін     | I/O ports                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    | -    |                 |        |                                                                                                    |  |

| D040          |         | with TTL buffer                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2.0                | -    | Vdd             | V      | $4.5V \leq V\text{DD} \leq 5.5V$                                                                   |  |

| D040A         |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.25Vd<br>D + 0.8V | -    | Vdd             | V      | For entire VDD range                                                                               |  |

| D041          |         | with Schmitt Trigger buffer                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.8Vdd             | -    | Vdd             | v      | For entire VDD range                                                                               |  |

| D042          |         | MCLR                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.8Vdd             | -    | Vdd             | V      |                                                                                                    |  |

| D042A         |         | OSC1 (XT, HS and LP modes)                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.7Vdd             | -    | Vdd             | V      | Note1                                                                                              |  |

| D043          |         | OSC1 (in RC mode)                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.9Vdd             | -    | Vdd             | V      |                                                                                                    |  |

|               |         | Input Leakage Current<br>(Notes 2, 3)                                                                                                                                                                                                                                                                                                                                                                                                               |                    |      |                 |        |                                                                                                    |  |

| D060          | lı∟     | I/O ports                                                                                                                                                                                                                                                                                                                                                                                                                                           | -                  | -    | ±1              | μA     | $\label{eq:Vss} \begin{split} &Vss \leq V PIN \leq V DD, \\ &Pin \ at \ hi\ impedance \end{split}$ |  |

| D061          |         | MCLR, RA4/T0CKI                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                  | -    | ±5              | μA     | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                           |  |

| D063          |         | OSC1                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                  | -    | ±5              | μA     | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc modes                                                |  |

| D070          | IPURB   | PORTB weak pull-up current                                                                                                                                                                                                                                                                                                                                                                                                                          | 50                 | 250  | 400             | μA     | VDD = 5V, VPIN = VSS                                                                               |  |

| D080          | Vol     | Output Low Voltage<br>I/O ports                                                                                                                                                                                                                                                                                                                                                                                                                     | -                  | -    | 0.6             | v      | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                                                        |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the device be driven with external clock in RC mode.

3: Negative current is defined as current sourced by the pin.

<sup>2:</sup> The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

### 13.4.3 TIMING DIAGRAMS AND SPECIFICATIONS

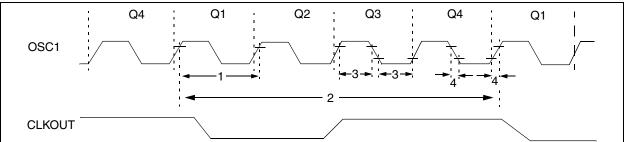

### FIGURE 13-5: EXTERNAL CLOCK TIMING

| Param<br>No. | Sym   | Characteristic                  | Min | Тур† | Мах    | Units | Conditions          |

|--------------|-------|---------------------------------|-----|------|--------|-------|---------------------|

| 1A           | Fosc  | External CLKIN Frequency        |     |      | 4      | MHz   | RC and XT osc modes |

|              |       | (Note 1)                        | DC  | —    | 4      | MHz   | HS osc mode (-04)   |

|              |       |                                 |     | —    | 20     | MHz   | HS osc mode (-20)   |

|              |       |                                 | DC  | _    | 200    | kHz   | LP osc mode         |

|              |       | Oscillator Frequency            | DC  |      | 4      | MHz   | RC osc mode         |

|              |       | (Note 1)                        | 0.1 | —    | 4      | MHz   | XT osc mode         |

|              |       |                                 | 4   | —    | 20     | MHz   | HS osc mode         |

|              |       |                                 | 5   | _    | 200    | kHz   | LP osc mode         |

| 1            | Tosc  | External CLKIN Period           |     | —    | —      | ns    | RC and XT osc modes |

|              |       | (Note 1)                        | 250 | —    | —      | ns    | HS osc mode (-04)   |

|              |       |                                 | 50  | —    | —      | ns    | HS osc mode (-20)   |

|              |       |                                 | 5   | _    | —      | μS    | LP osc mode         |

|              |       | Oscillator Period<br>(Note 1)   | 250 | —    | —      | ns    | RC osc mode         |

|              |       |                                 | 250 | —    | 10,000 | ns    | XT osc mode         |

|              |       |                                 | 250 | —    | 250    | ns    | HS osc mode (-04)   |

|              |       |                                 |     | —    | 250    | ns    | HS osc mode (-20)   |

|              |       |                                 | 5   | _    | —      | μS    | LP osc mode         |

| 2            | Тсү   | Instruction Cycle Time (Note 1) | 200 | _    | DC     | ns    | Tcy = 4/Fosc        |

| 3*           | TosL, | External Clock in (OSC1) High   | 100 | —    | —      | ns    | XT oscillator       |

|              | TosH  | or Low Time                     | 2.5 | —    | —      | μS    | LP oscillator       |

|              |       |                                 | 15  | _    | —      | ns    | HS oscillator       |

| 4*           | TosR, | External Clock in (OSC1) Rise   | —   | —    | 25     | ns    | XT oscillator       |

|              | TosF  | or Fall Time                    | —   | —    | 50     | ns    | LP oscillator       |

|              |       |                                 | _   | _    | 15     | ns    | HS oscillator       |

### TABLE 13-2: EXTERNAL CLOCK TIMING REQUIREMENTS

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin.

When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

| Param<br>No. | Sym      | Characteristic                        | Min                | Тур†       | Мах | Units       | Conditions |        |

|--------------|----------|---------------------------------------|--------------------|------------|-----|-------------|------------|--------|

| 10*          | TosH2ckL | OSC1↑ to CLKOUT↓                      | —                  | 75         | 200 | ns          | Note 1     |        |

| 11*          | TosH2ckH | OSC1↑ to CLKOUT↑                      |                    | —          | 75  | 200         | ns         | Note 1 |

| 12*          | TckR     | CLKOUT rise time                      |                    | _          | 35  | 100         | ns         | Note 1 |

| 13*          | TckF     | CLKOUT fall time                      |                    | _          | 35  | 100         | ns         | Note 1 |

| 14*          | TckL2ioV | CLKOUT ↓ to Port out valid            |                    | —          |     | 0.5TCY + 20 | ns         | Note 1 |

| 15*          | TioV2ckH | Port in valid before CLKOUT ↑         |                    | Tosc + 200 |     | _           | ns         | Note 1 |

| 16*          | TckH2iol | Port in hold after CLKOUT ↑           |                    | 0          |     | _           | ns         | Note 1 |

| 17*          | TosH2ioV | OSC1↑ (Q1 cycle) to Port out valid    |                    | —          | 50  | 150         | ns         |        |

| 18*          | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to Port  | PIC16CXX           | 100        |     | _           | ns         |        |

| 18A*         |          | input invalid (I/O in hold<br>time)   | PIC16LCXX          | 200        |     | —           | ns         |        |

| 19*          | TioV2osH | Port input valid to OSC11 (           | I/O in setup time) | 0          | _   | _           | ns         |        |

| 20*          | TioR     | Port output rise time                 | PIC16CXX           | —          | 10  | 40          | ns         |        |

| 20A*         |          | PIC16LCXX                             |                    | _          |     | 80          | ns         |        |

| 21*          | TioF     | Port output fall time <b>PIC16CXX</b> |                    | —          | 10  | 40          | ns         |        |

| 21A*         |          |                                       | PIC16LCXX          | _          | _   | 80          | ns         |        |

| 22††*        | Tinp     | INT pin high or low time              |                    | Тсү        | _   | —           | ns         |        |

| 23††*        | Trbp     | RB7:RB4 change INT high               | or low time        | Тсү        | —   | —           | ns         |        |

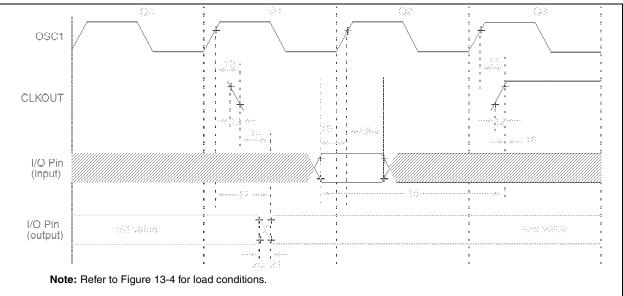

| TABLE 13-3: | CLKOUT AND I/O TIMING REQUIREMENTS |

|-------------|------------------------------------|

|             |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

tt These parameters are asynchronous events not related to any internal clock edge.

**Note 1:** Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

# PIC16C62B/72A

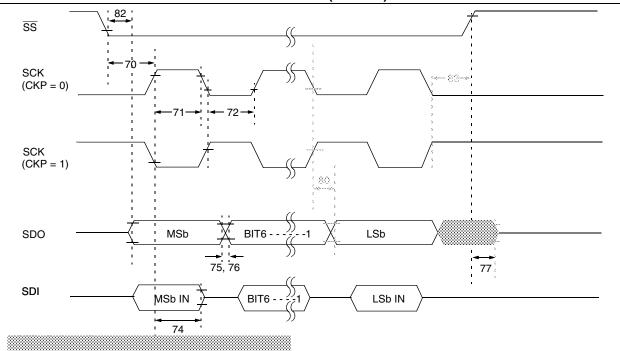

### FIGURE 13-14: EXAMPLE SPI SLAVE MODE TIMING (CKE = 1)

### TABLE 13-10: EXAMPLE SPI SLAVE MODE REQUIREMENTS (CKE = 1)

| Param.<br>No. | Symbol                            | Characteris                                                           | Min         | Тур†         | Мах | Units | Conditions |        |

|---------------|-----------------------------------|-----------------------------------------------------------------------|-------------|--------------|-----|-------|------------|--------|