Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

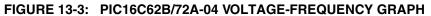

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

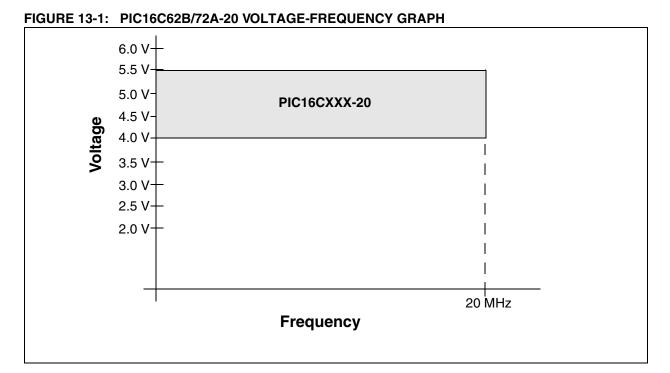

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c72a-04i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Addr    | Name                    | Bit 7              | Bit 6                                  | Bit 5                     | Bit 4         | Bit 3         | Bit 2           | Bit 1        | Bit 0         | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(4) |

|---------|-------------------------|--------------------|----------------------------------------|---------------------------|---------------|---------------|-----------------|--------------|---------------|--------------------------|-------------------------------------|

| Bank 1  |                         |                    |                                        |                           |               |               |                 |              |               |                          |                                     |

| 80h     | INDF <sup>(1)</sup>     | Addressing         | this locatio                           | n uses conte              | ents of FSR   | to address d  | ata memory      | (not a physi | cal register) | 0000 0000                | 0000 0000                           |

| 81h     | OPTION_REG              | RBPU               | INTEDG                                 | T0CS                      | TOSE          | PSA           | PS2             | PS1          | PS0           | 1111 1111                | 1111 1111                           |

| 82h     | PCL <sup>(1)</sup>      | Program C          | ounter's (PC                           | C) Least Sig              | nificant Byte | 1             |                 |              |               | 0000 0000                | 0000 0000                           |

| 83h     | STATUS <sup>(1)</sup>   | IRP <sup>(5)</sup> | RP1 <sup>(5)</sup>                     | RP0                       | TO            | PD            | Z               | DC           | С             | 0001 1xxx                | 000q quuu                           |

| 84h     | FSR <sup>(1)</sup>      | Indirect dat       | a memory a                             | ddress poir               | nter          |               |                 |              |               | xxxx xxxx                | uuuu uuuu                           |

| 85h     | TRISA                   | —                  | —                                      | PORTA Da                  | ta Direction  | Register      |                 |              |               | 11 1111                  | 11 1111                             |

| 86h     | TRISB                   | PORTB Da           | PORTB Data Direction Register 1        |                           |               |               |                 |              |               |                          | 1111 1111                           |

| 87h     | TRISC                   | PORTC Da           | PORTC Data Direction Register 1111 111 |                           |               |               |                 |              |               |                          | 1111 1111                           |

| 88h-89h | _                       | Unimplemented      |                                        |                           |               |               |                 |              | _             | _                        |                                     |

| 8Ah     | PCLATH <sup>(1,2)</sup> | —                  | _                                      | —                         | Write Buffe   | r for the upp | er 5 bits of th | e Program (  | Counter       | 0 0000                   | 0 0000                              |

| 8Bh     | INTCON <sup>(1)</sup>   | GIE                | PEIE                                   | TOIE                      | INTE          | RBIE          | TOIF            | INTF         | RBIF          | 0000 000x                | 0000 000u                           |

| 8Ch     | PIE1                    | —                  | ADIE <sup>(3)</sup>                    | _                         | —             | SSPIE         | CCP1IE          | TMR2IE       | TMR1IE        | -0 0000                  | -0 0000                             |

| 8Dh     | _                       | Unimpleme          | ented                                  |                           |               |               |                 |              |               | _                        | _                                   |

| 8Eh     | PCON                    | —                  | _                                      | —                         | —             | _             | —               | POR          | BOR           | dd                       | uu                                  |

| 8Fh-91h | _                       | Unimpleme          | ented                                  |                           |               |               |                 | •            |               | _                        | _                                   |

| 92h     | PR2                     | Timer2 Per         | iod Registe                            | r                         |               |               |                 |              |               | 1111 1111                | 1111 1111                           |

| 93h     | SSPADD                  | Synchrono          | us Serial Po                           | rt (I <sup>2</sup> C mode | e) Address F  | Register      |                 |              |               | 0000 0000                | 0000 0000                           |

| 94h     | SSPSTAT                 | SMP                | CKE                                    | D/A                       | Р             | S             | R/W             | UA           | BF            | 0000 0000                | 0000 0000                           |

| 95h-9Eh | —                       | Unimpleme          | ented                                  |                           |               |               |                 |              |               | —                        | —                                   |

| 9Fh     | ADCON1 <sup>(3)</sup>   | _                  | _                                      | _                         | _             | _             | PCFG2           | PCFG1        | PCFG0         | 000                      | 000                                 |

#### TABLE 2-1 SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0',

Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: A/D not implemented on the PIC16C62B, maintain as '0'.

4: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

5: The IRP and RP1 bits are reserved. Always maintain these bits clear.

**6:** On any device reset, these pins are configured as inputs.

7: This is the value that will be in the port output latch.

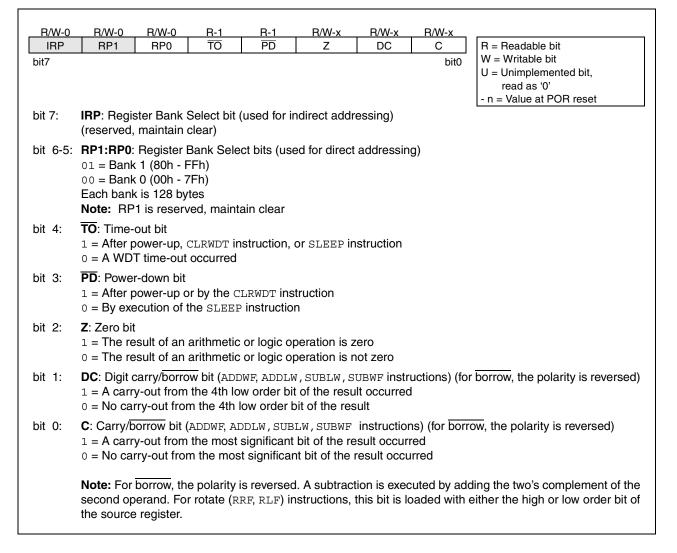

#### 2.2.2.1 STATUS REGISTER

The STATUS register, shown in Register 2-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, the write to these three bits is disabled. These bits are set or cleared according to the device logic. The TO and PD bits are not writable. The result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

- **Note 1:** The IRP and RP1 bits are reserved. Maintain these bits clear to ensure upward compatibility with future products.

- Note 2: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions.

## REGISTER 2-1: STATUS REGISTER (ADDRESS 03h, 83h)

#### 2.2.2.5 PIR1 REGISTER

This register contains the individual flag bits for the Peripheral interrupts.

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## REGISTER 2-5: PIR1 REGISTER (ADDRESS 0Ch)

| U-0      | R/W-0                                                                                                                                                                                                                                                                                                                                                             | U-0                        | U-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0          | 1                                                                                                         |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----|-------|--------|--------|----------------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|

| <br>bit7 | ADIF <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                               | _                          | _   | SSPIF | CCP1IF | TMR2IF | TMR1IF<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |  |  |  |

| bit 7:   | Unimpler                                                                                                                                                                                                                                                                                                                                                          | Unimplemented: Read as '0' |     |       |        |        |                |                                                                                                           |  |  |  |  |

| bit 6:   | <b>ADIF</b> <sup>(1)</sup> : A/D Converter Interrupt Flag bit<br>1 = An A/D conversion completed (must be cleared in software)<br>0 = The A/D conversion is not complete                                                                                                                                                                                          |                            |     |       |        |        |                |                                                                                                           |  |  |  |  |

| bit 5-4: | Unimpler                                                                                                                                                                                                                                                                                                                                                          | Unimplemented: Read as '0' |     |       |        |        |                |                                                                                                           |  |  |  |  |

| bit 3:   | <pre>SSPIF: Synchronous Serial Port Interrupt Flag bit 1 = The transmission/reception is complete (must be cleared in software) 0 = Waiting to transmit/receive</pre>                                                                                                                                                                                             |                            |     |       |        |        |                |                                                                                                           |  |  |  |  |

| bit 2:   | CCP1IF: CCP1 Interrupt Flag bit<br><u>Capture Mode</u><br>1 = A TMR1 register capture occurred (must be cleared in software)<br>0 = No TMR1 register capture occurred<br><u>Compare Mode</u><br>1 = A TMR1 register compare match occurred (must be cleared in software)<br>0 = No TMR1 register compare match occurred<br><u>PWM Mode</u><br>Unused in this mode |                            |     |       |        |        |                |                                                                                                           |  |  |  |  |

| bit 1:   | <b>TMR2IF</b> : TMR2 to PR2 Match Interrupt Flag bit<br>1 = TMR2 to PR2 match occurred (must be cleared in software)<br>0 = No TMR2 to PR2 match occurred                                                                                                                                                                                                         |                            |     |       |        |        |                |                                                                                                           |  |  |  |  |

| bit 0:   | TMR1IF: TMR1 Overflow Interrupt Flag bit<br>1 = TMR1 register overflowed (must be cleared in software)<br>0 = TMR1 register did not overflow                                                                                                                                                                                                                      |                            |     |       |        |        |                |                                                                                                           |  |  |  |  |

| Note 1:  | The PIC16C62B does not have an A/D module. This bit location is reserved on these devices. Always maintain this bit clear.                                                                                                                                                                                                                                        |                            |     |       |        |        |                |                                                                                                           |  |  |  |  |

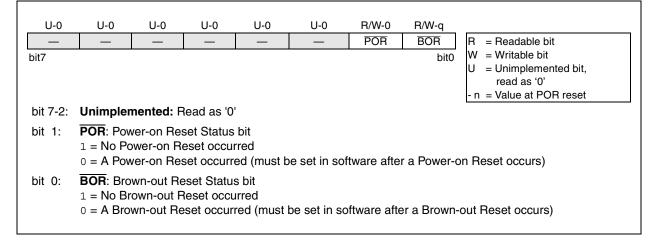

#### 2.2.2.6 PCON REGISTER

The Power Control register (PCON) contains flag bits to allow differentiation between a Power-on Reset (POR), Brown-Out Reset (BOR) and resets from other sources.

Note: On Power-on Reset, the state of the BOR bit is unknown and is not predictable. If the BODEN bit in the configuration word is set, the user must first set the BOR bit on a POR, and check it on subsequent resets. If BOR is cleared while POR remains set, a Brown-out reset has occurred. If the BODEN bit is clear, the BOR bit may be ignored.

## REGISTER 2-6: PCON REGISTER (ADDRESS 8Eh)

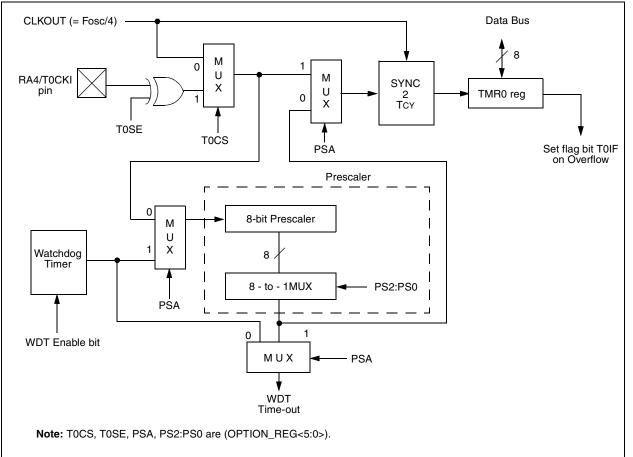

#### 4.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, (i.e., it can be changed "on-the-fly" during program execution).

Note: To avoid an unintended device RESET, a specific instruction sequence (shown in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, DS33023) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

#### 4.3 <u>Timer0 Interrupt</u>

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP since the timer is shut off during SLEEP.

#### FIGURE 4-2: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

## TABLE 4-1 REGISTERS ASSOCIATED WITH TIMER0

| Address | Name Bit   |        | Bit 6                                             | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0   | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|------------|--------|---------------------------------------------------|-------|-------|-------|-------|-------|---------|--------------------------|---------------------------|

| 01h     | TMR0       | Timer0 | imer0 module's register                           |       |       |       |       |       |         | xxxx xxxx                | uuuu uuuu                 |

| 0Bh,8Bh | INTCON     | GIE    | PEIE                                              | TOIE  | INTE  | RBIE  | T0IF  | INTF  | RBIF    | 0000 000x                | 0000 000u                 |

| 81h     | OPTION_REG | RBPU   | INTEDG                                            | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0     | 1111 1111                | 1111 1111                 |

| 85h     | TRISA      |        | <ul> <li>PORTA Data Direction Register</li> </ul> |       |       |       |       |       | 11 1111 | 11 1111                  |                           |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

NOTES:

| TABLE 8-1 | REGISTERS ASSOCIATED WITH SPI OPERATION |

|-----------|-----------------------------------------|

|           |                                         |

| Address | Name    | Bit 7      | Bit 6       | Bit 5                                  | Bit 4                         | Bit 3      | Bit 2    | Bit 1  | Bit 0  | Value<br>POR<br>BOF | l,  | Valu<br>all o<br>res |      |

|---------|---------|------------|-------------|----------------------------------------|-------------------------------|------------|----------|--------|--------|---------------------|-----|----------------------|------|

| 0Bh,8Bh | INTCON  | GIE        | PEIE        | TOIE                                   | INTE                          | RBIE       | T0IF     | INTF   | RBIF   | 0000 0              | 00x | 0000                 | 000u |

| 0Ch     | PIR1    | —          | ADIF        | —                                      | _                             | SSPIF      | CCP1IF   | TMR2IF | TMR1IF | -00                 | 000 | - 0                  | 0000 |

| 8Ch     | PIE1    | —          | ADIE        |                                        | —                             | SSPIE      | CCP1IE   | TMR2IE | TMR1IE | -00                 | 000 | - 0                  | 0000 |

| 13h     | SSPBUF  | Synchronou | s Serial P  | ort Receiv                             | e Buffer/                     | Transmit F | Register |        |        | xxxx x              | xxx | uuuu                 | uuuu |

| 14h     | SSPCON  | WCOL       | SSPOV       | SSPEN                                  | CKP                           | SSPM3      | SSPM2    | SSPM1  | SSPM0  | 0000 0              | 000 | 0000                 | 0000 |

| 94h     | SSPSTAT | SMP        | CKE         | D/Ā                                    | Р                             | S          | R/W      | UA     | BF     | 0000 0              | 000 | 0000                 | 0000 |

| 85h     | TRISA   | _          |             | PORTA D                                | PORTA Data Direction Register |            |          |        |        | 11 1                | 111 | 11                   | 1111 |

| 87h     | TRISC   | PORTC Data | a Direction | rection Register 1111 1111 1111 1111 1 |                               |            |          |        |        | 1111                |     |                      |      |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the SSP in SPI mode.

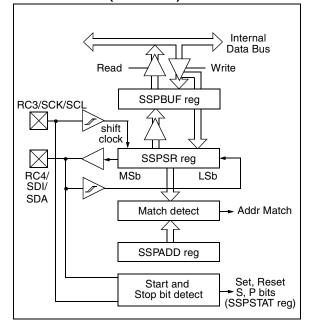

# 8.3 <u>SSP I<sup>2</sup>C Operation</u>

The SSP module in I<sup>2</sup>C mode fully implements all slave functions, except general call support, and provides interrupts on start and stop bits in hardware to support firmware implementations of the master functions. The SSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RC3/SCK/SCL pin, which is the clock (SCL), and the RC4/SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

The SSP module functions are enabled by setting SSP Enable bit SSPEN (SSPCON<5>).

FIGURE 8-2: SSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

The SSP module has five registers for  $I^2C$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with start and stop bit interrupts enabled for firmware master mode support

- I<sup>2</sup>C Slave mode (10-bit address), with start and stop bit interrupts enabled for firmware master mode support

- I<sup>2</sup>C start and stop bit interrupts enabled for firmware master mode support, slave mode idle

Selection of any  $I^2C$  mode, with the SSPEN bit set, forces the SCL and SDA pins to be operated as open drain outputs, provided these pins are programmed to inputs by setting the appropriate TRISC bits.

Additional information on SSP I<sup>2</sup>C operation may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

#### 8.3.1 SLAVE MODE

In slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched or the data transfer after an address match is received, the hardware automatically will generate the acknowledge ( $\overline{ACK}$ ) pulse, and load the SSPBUF register with the received value in the SSPSR register.

There are certain conditions that will cause the SSP module not to give this  $\overline{ACK}$  pulse. This happens if either of the following conditions occur:

- a) The buffer full bit BF (SSPSTAT<0>) was set before the transfer was completed.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was completed.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. Table 8-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

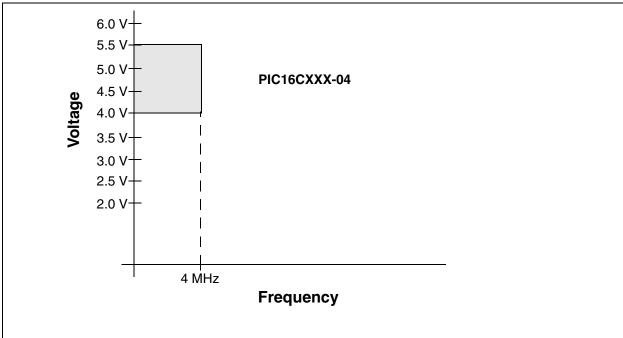

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the SSP module, is shown in timing parameter #100, THIGH, and parameter #101, TLOW.

# 9.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

Note: This section applies to the PIC16C72A only.

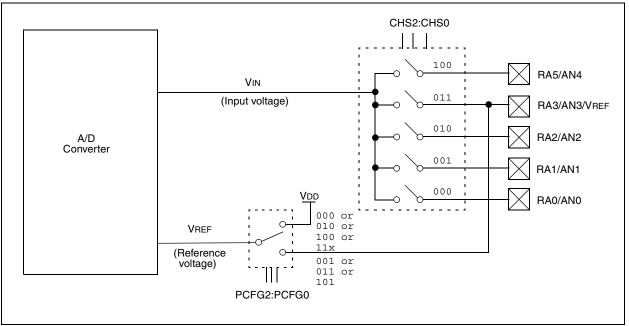

The analog-to-digital (A/D) converter module has five input channels.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number (refer to Application Note AN546 for use of A/D Converter). The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD) or the voltage level on the RA3/AN3/VREF pin.

The A/D converter has the feature of being able to operate while the device is in SLEEP mode. To operate in sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

Additional information on the A/D module is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

The A/D module has three registers. These registers are:

- A/D Result Register (ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

A device reset forces all registers to their reset state. This forces the A/D module to be turned off, and any conversion is aborted.

The ADCON0 register, shown in Figure 9-1, controls the operation of the A/D module. The ADCON1 register, shown in Figure 9-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference) or as digital I/O.

| R/W-0         | R/W-0                                                                                                                                                                                                                                                | R/W-0     | R/W-0      | R/W-0      | R/W-0   | U-0 | R/W-0        |                                                                               |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|------------|---------|-----|--------------|-------------------------------------------------------------------------------|--|--|

| ADCS1<br>bit7 | ADCS0                                                                                                                                                                                                                                                | CHS2      | CHS1       | CHS0       | GO/DONE | _   | ADON<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0' |  |  |

| bit 7-6:      | ADCS1:ADCS0: A/D Conversion Clock Select bits<br>00 = Fosc/2<br>01 = Fosc/8<br>10 = Fosc/32<br>11 = FRC (clock derived from an internal RC oscillator)                                                                                               |           |            |            |         |     |              |                                                                               |  |  |

| bit 5-3:      | CHS2:CHS0: Analog Channel Select bits<br>000 = channel 0, (RA0/AN0)<br>001 = channel 1, (RA1/AN1)<br>010 = channel 2, (RA2/AN2)<br>011 = channel 3, (RA3/AN3)<br>100 = channel 4, (RA5/AN4)                                                          |           |            |            |         |     |              |                                                                               |  |  |

| bit 2:        | GO/DON                                                                                                                                                                                                                                               | E: A/D Co | nversion   | Status bit |         |     |              |                                                                               |  |  |

|               | $\frac{\text{If ADON} = 1}{1 = A/D \text{ conversion not in progress (setting this bit starts the A/D conversion)}$ $0 = A/D \text{ conversion not in progress (This bit is automatically cleared by hardware when the A/D conversion is complete)}$ |           |            |            |         |     |              |                                                                               |  |  |

| bit 1:        | Unimpler                                                                                                                                                                                                                                             | nented: F | Read as '0 | ı          |         |     |              |                                                                               |  |  |

| bit 0:        | ADON: A/D On bit<br>1 = A/D converter module is operating<br>0 = A/D converter module is shutoff and consumes no operating current                                                                                                                   |           |            |            |         |     |              |                                                                               |  |  |

#### **REGISTER 9-1: ADCON0 REGISTER (ADDRESS 1Fh)**

When the A/D conversion is complete, the result is loaded into the ADRES register, the GO/DONE bit, ADCON0<2>, is cleared, and the A/D interrupt flag bit, ADIF, is set. The block diagram of the A/D module is shown in Figure 9-1.

The value that is in the ADRES register is not modified for a Power-on Reset. The ADRES register will contain unknown data after a Power-on Reset.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see Section 9.1. After this acquisition time has elapsed, the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins / voltage reference / and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:

Polling for the GO/DONE bit to be cleared

- OR

- Waiting for the A/D interrupt

- 6. Read A/D Result register (ADRES), clear bit ADIF if required.

- 7. For next conversion, go to step 1 or step 2 as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2TAD is required before next acquisition starts.

#### FIGURE 9-1: A/D BLOCK DIAGRAM

# 10.0 SPECIAL FEATURES OF THE CPU

The PIC16C62B/72A devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Mode Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- ID locations

- In-circuit serial programming<sup>™</sup> (ICSP)

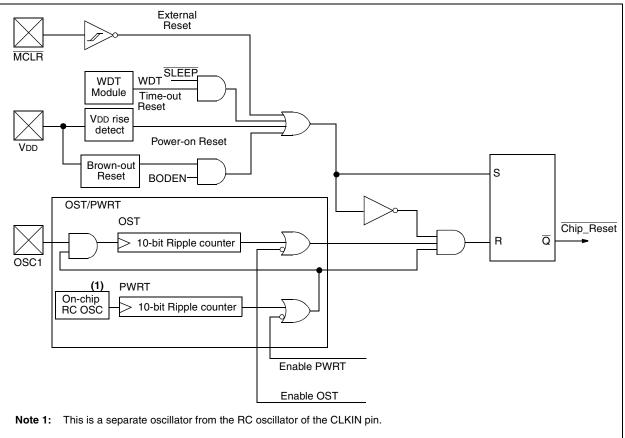

These devices have a Watchdog Timer, which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The

### FIGURE 10-1: CONFIGURATION WORD

other is the Power-up Timer (PWRT), which provides a fixed delay on power-up only and is designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

Additional information on special features is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

## 10.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

| CP1    | CP0                                                                                                                                                                                                     | CP1                                                                                                                                                                                                                                 | CP0 | CP1 | CP0 | _ | BODEN | CP1 | CP0 | PWRTE | WDTE | FOSC1 | FOSC0 | Register: | CONFIG |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|---|-------|-----|-----|-------|------|-------|-------|-----------|--------|

| bit13  |                                                                                                                                                                                                         | bit0 Address: 2007h                                                                                                                                                                                                                 |     |     |     |   |       |     |     |       |      |       |       |           |        |

|        | bit 13-8 <b>CP1:CP0</b> : Code Protection bits <sup>(2)</sup><br>5-4: 11 = Code protection off<br>10 = Upper half of program memory code protected<br>01 = Upper 3/4th of program memory code protected |                                                                                                                                                                                                                                     |     |     |     |   |       |     |     |       |      |       |       |           |        |

|        |                                                                                                                                                                                                         | 01 = Opper 3/4th of program memory code protected<br>00 = All memory is code protected                                                                                                                                              |     |     |     |   |       |     |     |       |      |       |       |           |        |

| bit 7: | I                                                                                                                                                                                                       | Unimplemented: Read as '1'                                                                                                                                                                                                          |     |     |     |   |       |     |     |       |      |       |       |           |        |

| bit 6: |                                                                                                                                                                                                         | BODEN: Brown-out Reset Enable bit <sup>(1)</sup><br>1 = BOR enabled<br>0 = BOR disabled                                                                                                                                             |     |     |     |   |       |     |     |       |      |       |       |           |        |

| bit 3: |                                                                                                                                                                                                         | <b>PWRTE</b> : Power-up Timer Enable bit <sup>(1)</sup><br>1 = PWRT disabled<br>0 = PWRT enabled                                                                                                                                    |     |     |     |   |       |     |     |       |      |       |       |           |        |

| bit 2: | :                                                                                                                                                                                                       | WDTE: Watchdog Timer Enable bit<br>1 = WDT enabled<br>0 = WDT disabled                                                                                                                                                              |     |     |     |   |       |     |     |       |      |       |       |           |        |

| bit 1- |                                                                                                                                                                                                         | FOSC1:FOSC0: Oscillator Selection bits<br>11 = RC oscillator<br>10 = HS oscillator<br>01 = XT oscillator<br>00 = LP oscillator                                                                                                      |     |     |     |   |       |     |     |       |      |       |       |           |        |

| Note   |                                                                                                                                                                                                         | Enabling Brown-out Reset automatically enables Power-up Timer (PWRT), regardless of the value of bit $\overline{\text{PWRTE}}$ . All of the CP1:CP0 pairs must be given the same value to enable the code protection scheme listed. |     |     |     |   |       |     |     |       |      |       |       |           |        |

#### FIGURE 10-5: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

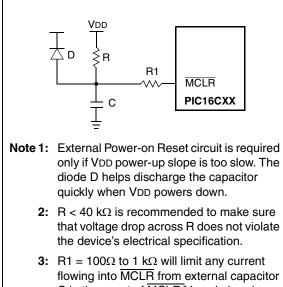

## 10.4 Power-On Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.5V - 2.1V). To take advantage of the POR, just tie the  $\overline{\text{MCLR}}$  pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified (SVDD, parameter D004). For a slow rise time, see Figure 10-6.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met. Brown-out Reset may be used to meet the start-up conditions.

#### FIGURE 10-6: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

#### R1 = 100Ω to 1 kΩ will limit any current flowing into $\overline{MCLR}$ from external capacitor C in the event of $\overline{MCLR}/VPP$ pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

## 10.5 Power-up Timer (PWRT)

The Power-up Timer provides a fixed nominal time-out (TPWRT, parameter #33) from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip-to-chip due to VDD, temperature and process variation. See DC parameters for details.

## 10.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a delay of 1024 oscillator cycles (from OSC1 input) after the PWRT delay is over (TOST, parameter #32). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

Note: The OST delay may not occur when the device wakes from SLEEP.

## 10.7 Brown-Out Reset (BOR)

The configuration bit, BODEN, can enable or disable the Brown-Out Reset circuit. If VPP falls below Vbor (parameter #35, about  $100\mu$ S), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a reset may not occur.

Once the brown-out occurs, the device will remain in brown-out reset until VDD rises above VBOR. The power-up timer then keeps the device in reset for TPWRT (parameter #33, about 72mS). If VDD should fall below VBOR during TPWRT, the brown-out reset process will restart when VDD rises above VBOR with the power-up timer reset. The power-up timer is always enabled when the brown-out reset circuit is enabled, regardless of the state of the PWRT configuration bit.

| COMF             | Complement f                                                                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] COMF f,d                                                                                                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                           |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                |

| Status Affected: | Z                                                                                                                                                         |

| Description:     | The contents of register 'f' are comple-<br>mented. If 'd' is 0, the result is stored<br>in W. If 'd' is 1, the result is stored<br>back in register 'f'. |

| GOTO             | Unconditional Branch                                                                                                                                                                          |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                       |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                            |  |  |  |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                               |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                          |  |  |  |  |  |  |

| Description:     | GOTO is an unconditional branch. The<br>eleven bit immediate value is loaded<br>into PC bits <10:0>. The upper bits of<br>PC are loaded from PCLATH<4:3>.<br>GOTO is a two cycle instruction. |  |  |  |  |  |  |

| DECF             | Decrement f                                                                                                                          |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECF f,d                                                                                                            |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                          |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                  |

| Status Affected: | Z                                                                                                                                    |

| Description:     | Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| INCF             | Increment f                                                                                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                       |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                     |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is 0, the result is placed<br>in the W register. If 'd' is 1, the result is<br>placed back in register 'f'. |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                      | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                          | Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                             | Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in[0,1] \end{array}$                                                                                                                                                                                                                                                            |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                  | Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                        | Status Affected: | None                                                                                                                                                                                                                                                                                                                  |

| Description:     | The contents of register 'f' are decre-<br>mented. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>placed back in register 'f'.<br>If the result is 1, the next instruction, is<br>executed. If the result is 0, then a NOP is<br>executed instead making it a $2Tcy$<br>instruction. | Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is 0, the result is placed<br>in the W register. If 'd' is 1, the result is<br>placed back in register 'f'.<br>If the result is 1, the next instruction is<br>executed. If the result is 0, a NOP is<br>executed instead making it a $2Tcy$<br>instruction. |

| IORLW            | Inclusive OR Literal with W                                                                                           |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] IORLW k                                                                                                     |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                     |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                          |  |  |  |

| Status Affected: | Z                                                                                                                     |  |  |  |

| Description:     | The contents of the W register is<br>OR'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |  |  |  |

| MOVLW            | Move Literal to W                                                                          |

|------------------|--------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                        |

| Operation:       | $k \rightarrow (W)$                                                                        |

| Status Affected: | None                                                                                       |

| Description:     | The eight bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |

| IORWF            | Inclusive OR W with f                                                                                                                                                  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] IORWF f,d                                                                                                                                                      |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                            |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                               |  |  |  |

| Status Affected: | Z                                                                                                                                                                      |  |  |  |

| Description:     | Inclusive OR the W register with regis-<br>ter 'f'. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>placed back in register 'f'. |  |  |  |

| MOVWF            | Move W to f                           |

|------------------|---------------------------------------|

| Syntax:          | [label] MOVWF f                       |

| Operands:        | $0 \leq f \leq 127$                   |

| Operation:       | $(W) \rightarrow (f)$                 |

| Status Affected: | None                                  |

| Description:     | Move data from W register to register |

| MOVF             | Move f                                                                                                                                                                                                                                                                                |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                           |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                                       |

| Status Affected: | Z                                                                                                                                                                                                                                                                                     |

| Description:     | The contents of register f is moved to<br>a destination dependant upon the sta-<br>tus of d. If $d = 0$ , destination is W reg-<br>ister. If $d = 1$ , the destination is file<br>register f itself. $d = 1$ is useful to test a<br>file register since status flag Z is<br>affected. |

| No Operation  |

|---------------|

| [label] NOP   |

| None          |

| No operation  |

| None          |

| No operation. |

|               |

## FIGURE 13-16: I<sup>2</sup>C BUS DATA TIMING

#### TABLE 13-12: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Param.<br>No. | Sym                | Characte               | eristic      | Min        | Max  | Units                     | Conditions                                       |

|---------------|--------------------|------------------------|--------------|------------|------|---------------------------|--------------------------------------------------|

| 100*          | Thigh              | Clock high time        | 100 kHz mode | 4.0        | —    | μS                        | Device must operate at a min-<br>imum of 1.5 MHz |

|               |                    |                        | 400 kHz mode | 0.6        | _    | μS                        | Device must operate at a min-<br>imum of 10 MHz  |

|               |                    |                        | SSP Module   | 1.5TCY     | —    |                           |                                                  |

| 101*          | TLOW               | Clock low time         | 100 kHz mode | 4.7        | -    | μS                        | Device must operate at a min-<br>imum of 1.5 MHz |

|               |                    |                        | 400 kHz mode | 1.3        | —    | μS                        | Device must operate at a min-<br>imum of 10 MHz  |

|               |                    |                        | SSP Module   | 1.5TCY     | —    |                           |                                                  |

| 102*          | TR                 | SDA and SCL rise       | 100 kHz mode | —          | 1000 | ns                        |                                                  |

|               |                    | time                   | 400 kHz mode | 20 + 0.1Cb | 300  | ns                        | Cb is specified to be from 10-400 pF             |

| 103*          | TF                 | SDA and SCL fall       | 100 kHz mode | —          | 300  | ns                        |                                                  |

|               |                    | time                   | 400 kHz mode | 20 + 0.1Cb | 300  | ns                        | Cb is specified to be from 10-400 pF             |

| 90*           | TSU:STA START o    | START condition        | 100 kHz mode | 4.7        | —    | μs                        | Only relevant for repeated                       |

|               |                    | setup time             | 400 kHz mode | 0.6        | —    | μs                        | START condition                                  |

| 91*           | THD:STA            | START condition hold   | 100 kHz mode | 4.0        | —    | μs                        | After this period the first clock                |

|               |                    | time                   | 400 kHz mode | 0.6        | —    | μS                        | pulse is generated                               |

| 106*          | THD:DAT            | Data input hold time   | 100 kHz mode | 0          | —    | ns                        |                                                  |

|               |                    |                        | 400 kHz mode | 0          | 0.9  | μs                        |                                                  |

| 107*          | TSU:DAT            | Data input setup time  | 100 kHz mode | 250        | —    | ns                        | Note 2                                           |

|               |                    |                        | 400 kHz mode | 100        |      | ns                        |                                                  |

| 92*           | TSU:STO            | STOP condition setup   | 100 kHz mode | 4.7        |      | μs                        |                                                  |

|               |                    | time                   | 400 kHz mode | 0.6        | _    | μS                        |                                                  |

| 109*          | ΤΑΑ                | Output valid from      | 100 kHz mode | —          | 3500 | ns                        | Note 1                                           |

|               |                    | clock                  | 400 kHz mode | —          |      | ns                        |                                                  |

| 110*          | TBUF Bus free time | 100 kHz mode           | 4.7          | _          | μS   | Time the bus must be free |                                                  |

|               |                    |                        | 400 kHz mode | 1.3        | —    | μs                        | before a new transmission<br>can start           |

|               | Cb                 | Bus capacitive loading |              | —          | 400  | pF                        |                                                  |

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

2: A fast-mode (400 kHz) I<sup>2</sup>C-bus device can be used in a standard-mode (100 kHz) I<sup>2</sup>C-bus system, but the requirement Tsu:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max.+tsu;DAT = 1000 + 250 = 1250 ns (according to the standard-mode I<sup>2</sup>C bus specification) before the SCL line is released.

# INDEX

# Α

| A/D  |                                             |    |       | 49 |

|------|---------------------------------------------|----|-------|----|

|      | A/D Converter Enable (ADIE Bit)             |    |       | 14 |

|      | A/D Converter Flag (ADIF Bit)               |    |       |    |

|      | A/D Converter Interrupt, Configuring        |    |       |    |

|      | ADCON0 Register                             |    |       |    |

|      | ADCON1 Register10                           |    |       |    |

|      | ADRES Register                              |    |       |    |

|      | Analog Port Pins                            |    | ····. | 6  |

|      | Analog Port Pins, Configuring               |    |       |    |

|      | Block Diagram                               |    |       |    |

|      | Block Diagram, Analog Input Model           |    |       |    |

|      | Channel Select (CHS2:CHS0 Bits)             |    |       |    |

|      | Clock Select (ADCS1:ADCS0 Bits)             |    |       |    |

|      | Configuring the Module                      |    |       |    |

|      | Conversion Clock (TAD)                      |    |       |    |

|      | Conversion Status (GO/DONE Bit)             |    |       |    |

|      | Conversions                                 |    |       |    |

|      | Converter Characteristics                   |    | 1     | 01 |

|      | Module On/Off (ADON Bit)                    |    |       |    |

|      | Port Configuration Control (PCFG2:PCFG0 Bit | s) |       | 50 |

|      | Sampling Requirements                       |    |       |    |

|      | Special Event Trigger (CCP)                 |    | 35,   | 54 |

|      | Timing Diagram                              |    | Í     | 02 |

| Abso | blute Maximum Ratings                       |    |       |    |

| ADC  | ON0 Register                                |    | . 9,  | 49 |

|      | ADCS1:ADCS0 Bits                            |    |       |    |

|      | ADON Bit                                    |    |       | 49 |

|      | CHS2:CHS0 Bits                              |    |       | 49 |

|      | GO/DONE Bit                                 |    | 49,   | 51 |

| ADC  | ON1 Register10                              | 0, | 49,   | 50 |

|      | PCFG2:PCFG0 Bits                            |    |       | 50 |

| ADR  | ES Register                                 |    |       |    |

|      | itecture                                    |    |       |    |

|      | PIC16C62B/PIC16C72A Block Diagram           |    |       | 5  |

| Asse | embler                                      |    |       |    |

|      | MPASM Assembler                             |    |       | 75 |

| в    |                                             |    |       |    |

| D    |                                             |    |       |    |

|  |   | ١. |

|--|---|----|

|  | 1 |    |

|  |   |    |

|  |   |    |

| Banking, Data Memory   |  |

|------------------------|--|

| Brown-out Reset (BOR)  |  |

| BOR Enable (BODEN Bit) |  |

| BOR Status (BOR Bit)   |  |

|                        |  |

## С

| Capture (CCP Module)                |    |

|-------------------------------------|----|

| Block Diagram                       |    |

| CCP Pin Configuration               |    |

| CCPR1H:CCPR1L Registers             |    |

| Changing Between Capture Prescalers |    |

| Software Interrupt                  |    |

| Timer1 Mode Selection               |    |

| Capture/Compare/PWM                 |    |

| Interaction of Two CCP Modules      |    |

| Capture/Compare/PWM (CCP)           |    |

| CCP1CON Register                    |    |

| CCPR1H Register                     |    |

| CCPR1L Register                     |    |

| Enable (CCP1IE Bit)                 | 14 |

| Flag (CCP1IF Bit)                   |    |

| RC2/CCP1 Pin                        | 6  |

| Timer Resources                     |    |

| Timing Diagram                      | 94 |

|                                     |    |

| CCP1CON Register                                                                                                                                                                           |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CCP1M3:CCP1M0 Bits 33                                                                                                                                                                      |  |

| CCP1X:CCP1Y Bits                                                                                                                                                                           |  |

| Code Protection55, 66                                                                                                                                                                      |  |

| CP1:CP0 Bits 55                                                                                                                                                                            |  |

| Compare (CCP Module)                                                                                                                                                                       |  |

| Block Diagram                                                                                                                                                                              |  |

| CCP Pin Configuration                                                                                                                                                                      |  |

| CCPR1H:CCPR1L Registers                                                                                                                                                                    |  |

| Software Interrupt                                                                                                                                                                         |  |

| Special Event Trigger                                                                                                                                                                      |  |

| Timer1 Mode Selection                                                                                                                                                                      |  |

| Configuration Bits                                                                                                                                                                         |  |

| Conversion Considerations                                                                                                                                                                  |  |

|                                                                                                                                                                                            |  |

| D                                                                                                                                                                                          |  |

| Data Memory8                                                                                                                                                                               |  |

| Bank Select (RP1:RP0 Bits)8, 11                                                                                                                                                            |  |

| General Purpose Registers                                                                                                                                                                  |  |

|                                                                                                                                                                                            |  |

| Register File Map                                                                                                                                                                          |  |

| Special Function Registers                                                                                                                                                                 |  |

| DC Characteristics                                                                                                                                                                         |  |

| Development Support                                                                                                                                                                        |  |

| Direct Addressing 18                                                                                                                                                                       |  |

| E                                                                                                                                                                                          |  |

| Electrical Characteristics                                                                                                                                                                 |  |

|                                                                                                                                                                                            |  |

| Errata                                                                                                                                                                                     |  |

| External Power-on Reset Circuit                                                                                                                                                            |  |

| F                                                                                                                                                                                          |  |

| Firmware Instructions67                                                                                                                                                                    |  |

|                                                                                                                                                                                            |  |

|                                                                                                                                                                                            |  |

| I/O Ports                                                                                                                                                                                  |  |