#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c72a-04i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

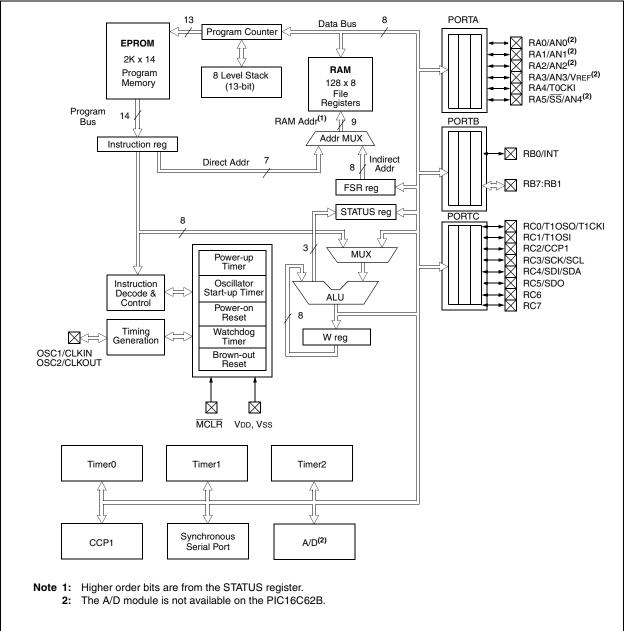

# 1.0 DEVICE OVERVIEW

This document contains device-specific information. Additional information may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

There are two devices (PIC16C62B, PIC16C72A) covered by this datasheet. The PIC16C62B does not have the A/D module implemented.

Figure 1-1 is the block diagram for both devices. The pinouts are listed in Table 1-1.

© 1998-2013 Microchip Technology Inc.

# 2.0 MEMORY ORGANIZATION

There are two memory blocks in each of these microcontrollers. Each block (Program Memory and Data Memory) has its own bus, so that concurrent access can occur.

Additional information on device memory may be found in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

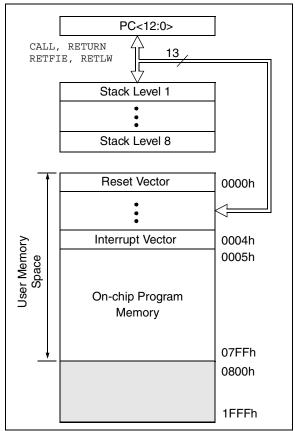

## 2.1 Program Memory Organization

The PIC16C62B/72A devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. Each device has 2K x 14 words of program memory. Accessing a location above 07FFh will cause a wraparound.

The reset vector is at 0000h and the interrupt vector is at 0004h.

#### FIGURE 2-1: PROGRAM MEMORY MAP AND STACK

| Addr    | Name                    | Bit 7              | Bit 6                                                            | Bit 5        | Bit 4         | Bit 3         | Bit 2           | Bit 1        | Bit 0         | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(4) |

|---------|-------------------------|--------------------|------------------------------------------------------------------|--------------|---------------|---------------|-----------------|--------------|---------------|--------------------------|-------------------------------------|

| Bank 1  |                         |                    |                                                                  |              |               |               |                 |              |               |                          |                                     |

| 80h     | INDF <sup>(1)</sup>     | Addressing         | this locatio                                                     | n uses conte | ents of FSR   | to address d  | ata memory      | (not a physi | cal register) | 0000 0000                | 0000 0000                           |

| 81h     | OPTION_REG              | RBPU               | INTEDG                                                           | T0CS         | TOSE          | PSA           | PS2             | PS1          | PS0           | 1111 1111                | 1111 1111                           |

| 82h     | PCL <sup>(1)</sup>      | Program C          | ounter's (PC                                                     | C) Least Sig | nificant Byte | 1             |                 |              |               | 0000 0000                | 0000 0000                           |

| 83h     | STATUS <sup>(1)</sup>   | IRP <sup>(5)</sup> | RP1 <sup>(5)</sup>                                               | RP0          | TO            | PD            | Z               | DC           | С             | 0001 1xxx                | 000q quuu                           |

| 84h     | FSR <sup>(1)</sup>      | Indirect dat       | a memory a                                                       | ddress poir  | nter          |               |                 |              |               | xxxx xxxx                | uuuu uuuu                           |

| 85h     | TRISA                   | —                  | —                                                                | PORTA Da     | ta Direction  | Register      |                 |              |               | 11 1111                  | 11 1111                             |

| 86h     | TRISB                   | PORTB Da           | ta Direction                                                     | Register     |               |               |                 |              |               | 1111 1111                | 1111 1111                           |

| 87h     | TRISC                   | PORTC Da           | ta Direction                                                     | Register     |               |               |                 |              |               | 1111 1111                | 1111 1111                           |

| 88h-89h | _                       | Unimpleme          | ented                                                            |              |               |               |                 |              |               | _                        | _                                   |

| 8Ah     | PCLATH <sup>(1,2)</sup> | —                  | _                                                                | —            | Write Buffe   | r for the upp | er 5 bits of th | e Program (  | Counter       | 0 0000                   | 0 0000                              |

| 8Bh     | INTCON <sup>(1)</sup>   | GIE                | PEIE                                                             | TOIE         | INTE          | RBIE          | TOIF            | INTF         | RBIF          | 0000 000x                | 0000 000u                           |

| 8Ch     | PIE1                    | —                  | ADIE <sup>(3)</sup>                                              | _            | —             | SSPIE         | CCP1IE          | TMR2IE       | TMR1IE        | -0 0000                  | -0 0000                             |

| 8Dh     | _                       | Unimpleme          | ented                                                            |              |               |               |                 |              |               | _                        | _                                   |

| 8Eh     | PCON                    | —                  | _                                                                | —            | —             | _             | —               | POR          | BOR           | dd                       | uu                                  |

| 8Fh-91h | _                       | Unimpleme          | Unimplemented —                                                  |              |               |               |                 |              |               | _                        |                                     |

| 92h     | PR2                     | Timer2 Per         | Timer2 Period Register                                           |              |               |               |                 |              |               | 1111 1111                | 1111 1111                           |

| 93h     | SSPADD                  | Synchrono          | Synchronous Serial Port (I <sup>2</sup> C mode) Address Register |              |               |               |                 |              | 0000 0000     | 0000 0000                |                                     |

| 94h     | SSPSTAT                 | SMP                | CKE                                                              | D/A          | Р             | S             | R/W             | UA           | BF            | 0000 0000                | 0000 0000                           |

| 95h-9Eh | —                       | Unimpleme          | ented                                                            |              |               |               |                 |              |               | —                        | —                                   |

| 9Fh     | ADCON1 <sup>(3)</sup>   | _                  | _                                                                | _            | _             | _             | PCFG2           | PCFG1        | PCFG0         | 000                      | 000                                 |

#### TABLE 2-1 SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0',

Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: A/D not implemented on the PIC16C62B, maintain as '0'.

4: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

5: The IRP and RP1 bits are reserved. Always maintain these bits clear.

**6:** On any device reset, these pins are configured as inputs.

7: This is the value that will be in the port output latch.

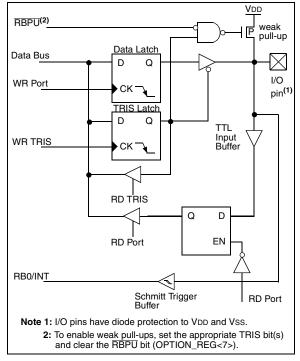

#### 3.2 PORTB and the TRISB Register

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (=1) will make the corresponding PORTB pin an input, (i.e., put the corresponding output driver in a hi-impedance mode). Clearing a TRISB bit (=0) will make the corresponding PORTB pin an output, (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit  $\overline{\text{RBPU}}$  (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

#### FIGURE 3-3: BLOCK DIAGRAM OF RB3:RB0 PINS

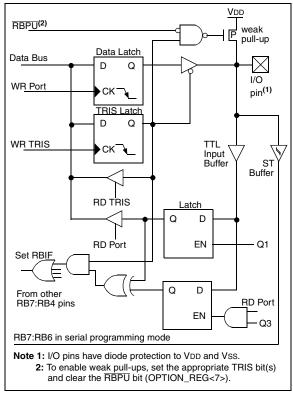

Four of PORTB's pins, RB7:RB4, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e. any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

RB0/INT is an external interupt pin and is configured using the INTEDG bit (OPTION\_REG<6>). RB0/INT is discussed in detail in Section 10.10.1.

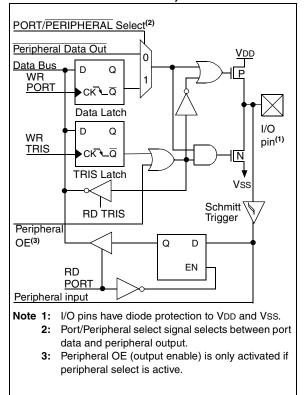

## 3.3 PORTC and the TRISC Register

PORTC is an 8-bit wide bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (=1) will make the corresponding PORTC pin an input, (i.e., put the corresponding output driver in a hi-impedance mode). Clearing a TRISC bit (=0) will make the corresponding PORTC pin an output, (i.e., put the contents of the output latch on the selected pin).

PORTC is multiplexed with several peripheral functions (Table 3-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override maybe in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

#### FIGURE 3-5: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

#### 5.2 <u>Timer1 Oscillator</u>

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). When the Timer1 oscillator is enabled, RC0 and RC1 pins become T1OSO and T1OSI inputs, overriding TRISC<1:0>.

The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal. Table 5-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

| TABLE 5-1 | CAPACITOR SELECTION FOR |

|-----------|-------------------------|

|           | THE TIMER1 OSCILLATOR   |

| Osc Type                                                                                                                                                                                                                                                                                          | Freq                        | C1            | C2            |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------|---------------|--|--|--|--|

| LP                                                                                                                                                                                                                                                                                                | 32 kHz                      | 33 pF         | 23.0F         |  |  |  |  |

|                                                                                                                                                                                                                                                                                                   | 100 kHz                     | 15 pF         | ्रीई वृष्ट्रे |  |  |  |  |

|                                                                                                                                                                                                                                                                                                   | 200 kHz                     | 15 pF         | (15°pF        |  |  |  |  |

| These va                                                                                                                                                                                                                                                                                          | alues are for (             | design guidar | ce only.      |  |  |  |  |

| Crystals Tested:                                                                                                                                                                                                                                                                                  |                             |               |               |  |  |  |  |

| 32.768 kHz                                                                                                                                                                                                                                                                                        | Epson C-00                  | (R32.768K-A   | $\pm$ 20 PPM  |  |  |  |  |

| 100 kHz                                                                                                                                                                                                                                                                                           | Epson C 21                  | 00.00 KC-P    | $\pm$ 20 PPM  |  |  |  |  |

| 200 kHz                                                                                                                                                                                                                                                                                           | STD XTL 200.000 kHz ± 20 PF |               |               |  |  |  |  |

| Note 1: Higher capacitance increases the stability<br>of oscillator but also increases the start-up<br>time.<br>2: Since each resonator/crystal has its own<br>characteristics, the user should consult the<br>resonator/crystal manufacturer for appropri-<br>ate values of external components. |                             |               |               |  |  |  |  |

## 5.3 <u>Timer1 Interrupt</u>

The TMR1 Register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow and is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled by setting TMR1 interrupt enable bit TMR1IE (PIE1<0>).

#### 5.4 <u>Resetting Timer1 using a CCP Trigger</u> <u>Output</u>

If the CCP module is configured in compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

| Note: | The special event trigger from the CCP1 |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|

|       | module will not set interrupt flag bit  |  |  |  |  |

|       | TMR1IF (PIR1<0>).                       |  |  |  |  |

Timer1 must be configured for either timer or synchronized counter mode to take advantage of this feature. If Timer1 is running in asynchronous counter mode, this reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPR1H:CCPR1L registers pair effectively becomes the period register for Timer1.

## TABLE 5-2 REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address | Name   | Bit 7   | Bit 6                                                                       | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|--------|---------|-----------------------------------------------------------------------------|---------|---------|---------|--------|--------|--------|-------------------------|---------------------------------|

| 0Bh,8Bh | INTCON | GIE     | PEIE                                                                        | TOIE    | INTE    | RBIE    | TOIF   | INTF   | RBIF   | 0000 000x               | 0000 000u                       |

| 0Ch     | PIR1   |         | ADIF                                                                        |         | -       | SSPIF   | CCP1IF | TMR2IF | TMR1IF | -0 0000                 | -0 0000                         |

| 8Ch     | PIE1   | _       | ADIE                                                                        | -       | -       | SSPIE   | CCP1IE | TMR2IE | TMR1IE | -0 0000                 | -0 0000                         |

| 0Eh     | TMR1L  | Holding | Holding register for the Least Significant Byte of the 16-bit TMR1 register |         |         |         |        |        |        | xxxx xxxx               | uuuu uuuu                       |

| 0Fh     | TMR1H  | Holding | Holding register for the Most Significant Byte of the 16-bit TMR1 register  |         |         |         |        |        |        | xxxx xxxx               | uuuu uuuu                       |

| 10h     | T1CON  | -       | _                                                                           | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR1ON | 00 0000                 | uu uuuu                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer1 module.

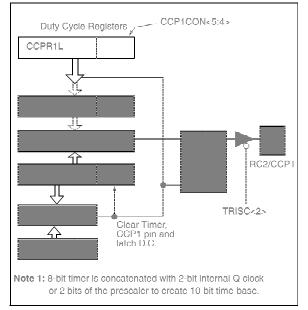

#### 7.3 <u>PWM Mode</u>

In Pulse Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force  |

|-------|-------------------------------------------|

|       | the CCP1 PWM output latch to the default  |

|       | low level. This is not the PORTC I/O data |

|       | latch.                                    |

Figure 7-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step by step procedure on how to set up the CCP module for PWM operation, see Section 7.3.3.

FIGURE 7-3: SIMPLIFIED PWM BLOCK DIAGRAM

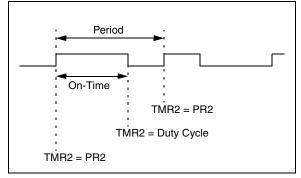

A PWM output (Figure 7-4) has a time base (period) and a time that the output stays high (on-time). The frequency of the PWM is the inverse of the period (1/period).

#### FIGURE 7-4: PWM OUTPUT

#### 7.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

| Note: | The Timer2 postscaler (see Section 6.0) is   |

|-------|----------------------------------------------|

|       | not used in the determination of the PWM     |

|       | frequency. The postscaler could be used to   |

|       | have a servo update rate at a different fre- |

|       | quency than the PWM output.                  |

#### 7.3.2 PWM ON-TIME

The PWM on-time is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. CCPR1L contains eight MSbs and CCP1CON<5:4> contains two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

CCPR1L and CCP1CON<5:4> can be written to at any time, but the on-time value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM on-time. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2 concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

Maximum PWM resolution (bits) for a given PWM frequency:

Resolution =

$$\frac{\log(\frac{Fosc}{Fpwm})}{\log(2)}$$

bits

Note: If the PWM on-time value is larger than the PWM period, the CCP1 pin will not be cleared.

For an example PWM period and on-time calculation, see the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

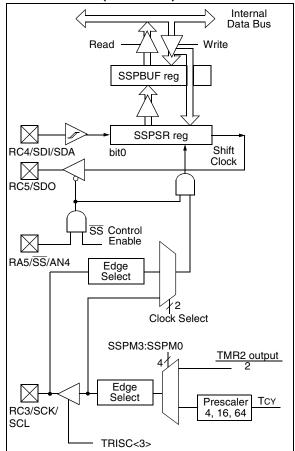

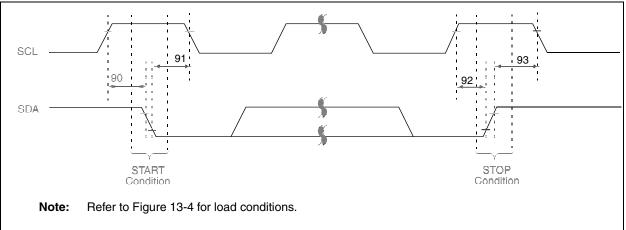

## 8.0 SYNCHRONOUS SERIAL PORT (SSP) MODULE

#### 8.1 SSP Module Overview

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

For more information on SSP operation (including an I<sup>2</sup>C Overview), refer to the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023). Also, refer to Application Note AN578, *"Use of the SSP Module in the I<sup>2</sup>C Multi-Master Environment."*

#### 8.2 SPI Mode

This section contains register definitions and operational characteristics of the SPI module.

Additional information on SPI operation may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

8.2.1 OPERATION OF SSP MODULE IN SPI MODE

A block diagram of the SSP Module in SPI Mode is shown in Figure 8-1.

The SPI mode allows 8-bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, three pins are used:

- Serial Data Out (SDO)RC5/SDO

- Serial Data In (SDI)RC4/SDI/SDA

- Serial Clock (SCK)RC3/SCK/SCL

Additionally, a fourth pin may be used when in a slave mode of operation:

Slave Select (SS)RA5/SS/AN4

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- Master Operation (SCK is the clock output)

- Slave Mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Clock Edge (Output data on rising/falling edge of SCK)

- Clock Rate (master operation only)

- Slave Select Mode (Slave mode only)

To enable the serial port, SSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON reg-

ister, and then set bit SSPEN. This configures the SDI, SDO, SCK and  $\overline{SS}$  pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISC register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (master operation) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set (if used)

Note: When the SPI is in Slave Mode with  $\overline{SS}$  pin control enabled, (SSPCON<3:0> = 0100) the SPI module will reset if the  $\overline{SS}$  pin is set to VDD.

**Note:** If the SPI is used in Slave Mode with CKE = '1', then the  $\overline{SS}$  pin control must be enabled.

#### FIGURE 8-1: SSP BLOCK DIAGRAM (SPI MODE)

## REGISTER 8-2: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)

| R/W-0    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0                                                                                                                                                           | R/W-0                                                                                                                        | R/W-0                                                                                                       | R/W-0                                                                                              | R/W-0                                                           | R/W-0                 |                                                                                      |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------|--|--|--|

| WCOL     | SSPOV                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SSPEN                                                                                                                                                           | CKP                                                                                                                          | SSPM3                                                                                                       | SSPM2                                                                                              | SSPM1                                                           | SSPM0                 | R = Readable bit                                                                     |  |  |  |

| bit7     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                 | -                                                                                                                            |                                                                                                             |                                                                                                    |                                                                 | bitO                  | W = Writable bit<br>U = Unimplemented bit, read<br>as '0'<br>- n =Value at POR reset |  |  |  |

| bit 7:   | <pre>WCOL: Write Collision Detect bit 1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software) 0 = No collision</pre>                                                                                                                                                                                                                                                                                    |                                                                                                                                                                 |                                                                                                                              |                                                                                                             |                                                                                                    |                                                                 |                       |                                                                                      |  |  |  |

| bit 6:   | SSPOV: R                                                                                                                                                                                                                                                                                                                                                                                                                                                          | eceive Ov                                                                                                                                                       | erflow Ind                                                                                                                   | cator bit                                                                                                   |                                                                                                    |                                                                 |                       |                                                                                      |  |  |  |

|          | In SPI mode<br>1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow,<br>the data in SSPSR is lost. Overflow can only occur in slave mode. The user must read the SSPBUF, even<br>if only transmitting data, to avoid setting overflow. In master operation, the overflow bit is not set since<br>each new reception (and transmission) is initiated by writing to the SSPBUF register.<br>0 = No overflow |                                                                                                                                                                 |                                                                                                                              |                                                                                                             |                                                                                                    |                                                                 |                       |                                                                                      |  |  |  |

|          | $\frac{\ln l^2 C \mod 1}{1 = A \text{ byte}}$<br>in transmit<br>0 = No over                                                                                                                                                                                                                                                                                                                                                                                       | is received<br>mode. SS                                                                                                                                         |                                                                                                                              |                                                                                                             |                                                                                                    |                                                                 |                       | us byte. SSPOV is a "don't care"                                                     |  |  |  |

| bit 5:   | SSPEN: S                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ynchronou                                                                                                                                                       | is Serial F                                                                                                                  | ort Enable                                                                                                  | bit                                                                                                |                                                                 |                       |                                                                                      |  |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                 |                                                                                                                              |                                                                                                             |                                                                                                    |                                                                 | s serial port<br>pins | t pins                                                                               |  |  |  |

|          | 0 = Disabl                                                                                                                                                                                                                                                                                                                                                                                                                                                        | es the seria<br>es serial p                                                                                                                                     | ort and co                                                                                                                   | nfigures th                                                                                                 | nese pins a                                                                                        | as I/O port                                                     |                       |                                                                                      |  |  |  |

| bit 4:   | In both modes, when enabled, these pins must be properly configured as input or output.<br><b>CKP</b> : Clock Polarity Select bit<br>In SPI mode<br>1 = Idle state for clock is a high level $0 = Idle state for clock is a low level In I2C mode SCK release control 1 = Enable clock0 = Holds clock low (clock stretch)$                                                                                                                                        |                                                                                                                                                                 |                                                                                                                              |                                                                                                             |                                                                                                    |                                                                 |                       |                                                                                      |  |  |  |

| bit 3-0: | $0001 = SF$ $0010 = SF$ $0100 = SF$ $0101 = SF$ $0110 = I^{2}C$ $0111 = I^{2}C$ $1011 = I^{2}C$ $1110 = I^{2}C$                                                                                                                                                                                                                                                                                                                                                   | PI master of<br>PI master of<br>PI master of<br>PI master of<br>PI slave mo<br>C slave mo<br>C slave mo<br>C slave mo<br>C slave mo<br>C slave mo<br>C slave mo | operation,<br>operation,<br>operation,<br>ode, clock<br>ode, clock<br>de, 7-bit a<br>de, 10-bit<br>controlled<br>de, 7-bit a | clock = Fo<br>clock = Fo<br>clock = Fo<br>clock = Th<br>= SCK pin<br>address<br>address<br>ddress<br>ddress | ISC/4<br>ISC/16<br>ISC/64<br>IR2 outpu<br>I. SS pin c<br>I. SS pin c<br>peration (s<br>th start an | t/2<br>ontrol ena<br>ontrol disa<br>slave idle)<br>d stop bit i |                       |                                                                                      |  |  |  |

Г

## 9.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

Note: This section applies to the PIC16C72A only.

The analog-to-digital (A/D) converter module has five input channels.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number (refer to Application Note AN546 for use of A/D Converter). The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD) or the voltage level on the RA3/AN3/VREF pin.

The A/D converter has the feature of being able to operate while the device is in SLEEP mode. To operate in sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

Additional information on the A/D module is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

The A/D module has three registers. These registers are:

- A/D Result Register (ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

A device reset forces all registers to their reset state. This forces the A/D module to be turned off, and any conversion is aborted.

The ADCON0 register, shown in Figure 9-1, controls the operation of the A/D module. The ADCON1 register, shown in Figure 9-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference) or as digital I/O.

| R/W-0         | R/W-0                                                                                                                                                                                                                          | R/W-0     | R/W-0    | R/W-0      | R/W-0   | U-0 | R/W-0        |                                                                               |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|------------|---------|-----|--------------|-------------------------------------------------------------------------------|

| ADCS1<br>bit7 | ADCS0                                                                                                                                                                                                                          | CHS2      | CHS1     | CHS0       | GO/DONE | _   | ADON<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0' |

| bit 7-6:      | ADCS1:ADCS0: A/D Conversion Clock Select bits<br>00 = Fosc/2<br>01 = Fosc/8<br>10 = Fosc/32<br>11 = FRC (clock derived from an internal RC oscillator)                                                                         |           |          |            |         |     |              |                                                                               |

| bit 5-3:      | CHS2:CHS0: Analog Channel Select bits<br>000 = channel 0, (RA0/AN0)<br>001 = channel 1, (RA1/AN1)<br>010 = channel 2, (RA2/AN2)<br>011 = channel 3, (RA3/AN3)<br>100 = channel 4, (RA5/AN4)                                    |           |          |            |         |     |              |                                                                               |

| bit 2:        | GO/DON                                                                                                                                                                                                                         | E: A/D Co | nversion | Status bit |         |     |              |                                                                               |

|               | <u>If ADON = 1</u><br>1 = A/D conversion in progress (setting this bit starts the A/D conversion)<br>0 = A/D conversion not in progress (This bit is automatically cleared by hardware when the A/D<br>conversion is complete) |           |          |            |         |     |              |                                                                               |

| bit 1:        | Unimplemented: Read as '0'                                                                                                                                                                                                     |           |          |            |         |     |              |                                                                               |

| bit 0:        | ADON: A/D On bit<br>1 = A/D converter module is operating<br>0 = A/D converter module is shutoff and consumes no operating current                                                                                             |           |          |            |         |     |              |                                                                               |

#### **REGISTER 9-1: ADCON0 REGISTER (ADDRESS 1Fh)**

#### 10.4 Power-On Reset (POR)

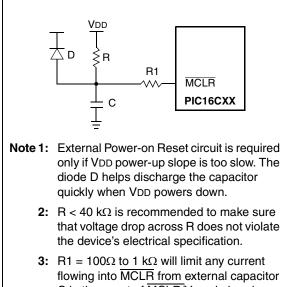

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.5V - 2.1V). To take advantage of the POR, just tie the  $\overline{\text{MCLR}}$  pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified (SVDD, parameter D004). For a slow rise time, see Figure 10-6.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met. Brown-out Reset may be used to meet the start-up conditions.

#### FIGURE 10-6: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

#### R1 = 100Ω to 1 kΩ will limit any current flowing into $\overline{MCLR}$ from external capacitor C in the event of $\overline{MCLR}/VPP$ pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

#### 10.5 Power-up Timer (PWRT)

The Power-up Timer provides a fixed nominal time-out (TPWRT, parameter #33) from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip-to-chip due to VDD, temperature and process variation. See DC parameters for details.

## 10.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a delay of 1024 oscillator cycles (from OSC1 input) after the PWRT delay is over (TOST, parameter #32). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

Note: The OST delay may not occur when the device wakes from SLEEP.

#### 10.7 Brown-Out Reset (BOR)

The configuration bit, BODEN, can enable or disable the Brown-Out Reset circuit. If VPP falls below Vbor (parameter #35, about  $100\mu$ S), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a reset may not occur.

Once the brown-out occurs, the device will remain in brown-out reset until VDD rises above VBOR. The power-up timer then keeps the device in reset for TPWRT (parameter #33, about 72mS). If VDD should fall below VBOR during TPWRT, the brown-out reset process will restart when VDD rises above VBOR with the power-up timer reset. The power-up timer is always enabled when the brown-out reset circuit is enabled, regardless of the state of the PWRT configuration bit.

| TABLE 10-6           | INITIALI | ZATION        | CONDITIONS FOR A                   | LL REGISTERS             |                                 |

|----------------------|----------|---------------|------------------------------------|--------------------------|---------------------------------|

| Register             |          | cable<br>ices | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

| W                    | 62B      | 72A           | XXXX XXXX                          | սսսս սսսս                | uuuu uuuu                       |

| INDF                 | 62B      | 72A           | N/A                                | N/A                      | N/A                             |

| TMR0                 | 62B      | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| PCL                  | 62B      | 72A           | 0000h                              | 0000h                    | PC + 1 <b>(2)</b>               |

| STATUS               | 62B      | 72A           | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu <b>(3)</b>            |

| FSR                  | 62B      | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| PORTA <sup>(4)</sup> | 62B      | 72A           | 0x 0000                            | 0u 0000                  | uu uuuu                         |

| PORTB <sup>(5)</sup> | 62B      | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PORTC <sup>(5)</sup> | 62B      | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PCLATH               | 62B      | 72A           | 0 0000                             | 0 0000                   | u uuuu                          |

| INTCON               | 62B      | 72A           | 0000 000x                          | 0000 000u                | uuuu uuuu <b>(1)</b>            |

|                      | 62B      | 72A           | 0000                               | 0000                     | uuuu <b>(1)</b>                 |

| PIR1                 | 62B      | 72A           | -0 0000                            | -0 0000                  | -u uuuu <b>(1)</b>              |

| TMR1L                | 62B      | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| TMR1H                | 62B      | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| T1CON                | 62B      | 72A           | 00 0000                            | uu uuuu                  | uu uuuu                         |

| TMR2                 | 62B      | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| T2CON                | 62B      | 72A           | -000 0000                          | -000 0000                | -uuu uuuu                       |

| SSPBUF               | 62B      | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| SSPCON               | 62B      | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| CCPR1L               | 62B      | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| CCPR1H               | 62B      | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| CCP1CON              | 62B      | 72A           | 00 0000                            | 00 0000                  | uu uuuu                         |

| ADRES                | 62B      | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| ADCON0               | 62B      | 72A           | 0000 00-0                          | 0000 00-0                | uuuu uu-u                       |

| OPTION_REG           | 62B      | 72A           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISA                | 62B      | 72A           | 11 1111                            | 11 1111                  | uu uuuu                         |

| TRISB                | 62B      | 72A           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISC                | 62B      | 72A           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| PIE1                 | 62B      | 72A           | 0000                               | 0000                     | uuuu                            |

|                      | 62B      | 72A           | -0 0000                            | -0 0000                  | -u uuuu                         |

| PCON                 | 62B      | 72A           | 0q                                 | uq                       | uq                              |

| PR2                  | 62B      | 72A           | 1111 1111                          | 1111 1111                | 1111 1111                       |

| SSPADD               | 62B      | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| SSPSTAT              | 62B      | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| ADCON1               | 62B      | 72A           | 000                                | 000                      | uuu                             |

| TABLE 10-6 | INITIALIZATION CONDITIONS FOR ALL REGISTERS |

|------------|---------------------------------------------|

|            |                                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', <math>q = value depends on condition

Note 1: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

**3:** See Table 10-5 for reset value for specific condition.

4: On any device reset, these pins are configured as inputs.

5: This is the value that will be in the port output latch.

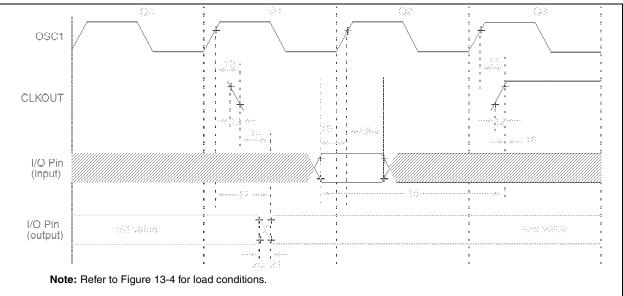

## FIGURE 10-10: WAKE-UP FROM SLEEP THROUGH INTERRUPT

| ; 01   02   03   04 ; 01   0<br>05C1 /       | 12  Q3  Q4; Q1        | a1  a2  a3  a | ; a1 a2 a3 a4;<br>_//_/       | a1  a2  a3   a4 ; | a1 a2 a3 a4; |

|----------------------------------------------|-----------------------|---------------|-------------------------------|-------------------|--------------|

|                                              |                       | Tost(2)       |                               | /                 |              |

| INT pin<br>INTF flag<br>(INTCON<1>)          |                       |               | Interrupt Latency<br>(Note 2) |                   |              |

| GIE bit<br>(INTCON<7>)                       | Processor in<br>SLEEP |               |                               | י<br>י<br>י<br>י  |              |

| INSTRUCTION FLOW                             |                       |               |                               | 1<br>1            |              |

| PC X PC X P                                  | C+1 <u>X</u> PC-      | +2 ·X PC+2    | X PC + 2                      | 0004h             | 0005h        |

| Instruction<br>fetched Inst(PC) = SLEEP Inst | (PC + 1)              | Inst(PC + 2)  |                               | Inst(0004h)       | Inst(0005h)  |

| Instruction Inst(PC - 1)                     | EEP                   | Inst(PC + 1)  | Dummy cycle                   | Dummy cycle       | Inst(0004h)  |

**Note 1:** XT, HS or LP oscillator mode assumed.

**2:** TOST = 1024TOSC (drawing not to scale) This delay will not be there for RC osc mode.

3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

#### 10.14 Program Verification/Code Protection

If the code protection bits have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip does not recommend code pro- |

|-------|----------------------------------------|

|       | tecting windowed devices.              |

#### 10.15 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution, but are readable and writable during program/verify. It is recommended that only the 4 least significant bits of the ID location are used.

For ROM devices, these values are submitted along with the ROM code.

#### 10.16 In-Circuit Serial Programming™

PIC16CXXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three more lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

For complete details of serial programming, please refer to the In-Circuit Serial Programming (ICSP<sup>™</sup>) Guide, DS30277.

| COMF             | Complement f                                                                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] COMF f,d                                                                                                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                           |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                |

| Status Affected: | Z                                                                                                                                                         |

| Description:     | The contents of register 'f' are comple-<br>mented. If 'd' is 0, the result is stored<br>in W. If 'd' is 1, the result is stored<br>back in register 'f'. |

| GOTO             | Unconditional Branch                                                                                                                                                                          |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                       |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                            |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                               |

| Status Affected: | None                                                                                                                                                                                          |

| Description:     | GOTO is an unconditional branch. The<br>eleven bit immediate value is loaded<br>into PC bits <10:0>. The upper bits of<br>PC are loaded from PCLATH<4:3>.<br>GOTO is a two cycle instruction. |

| DECF             | Decrement f                                                                                                                          |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECF f,d                                                                                                            |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                          |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                  |

| Status Affected: | Z                                                                                                                                    |

| Description:     | Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| INCF             | Increment f                                                                                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                       |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                     |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is 0, the result is placed<br>in the W register. If 'd' is 1, the result is<br>placed back in register 'f'. |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                      | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                          | Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                             | Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in[0,1] \end{array}$                                                                                                                                                                                                                                                            |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                  | Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                        | Status Affected: | None                                                                                                                                                                                                                                                                                                                  |

| Description:     | The contents of register 'f' are decre-<br>mented. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>placed back in register 'f'.<br>If the result is 1, the next instruction, is<br>executed. If the result is 0, then a NOP is<br>executed instead making it a $2Tcy$<br>instruction. | Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is 0, the result is placed<br>in the W register. If 'd' is 1, the result is<br>placed back in register 'f'.<br>If the result is 1, the next instruction is<br>executed. If the result is 0, a NOP is<br>executed instead making it a $2Tcy$<br>instruction. |

# PIC16C62B/72A

| IORLW            | Inclusive OR Literal with W                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] IORLW k                                                                                                     |

| Operands:        | $0 \leq k \leq 255$                                                                                                   |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                          |

| Status Affected: | Z                                                                                                                     |

| Description:     | The contents of the W register is<br>OR'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |

| MOVLW            | Move Literal to W                                                                          |

|------------------|--------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                        |

| Operation:       | $k \rightarrow (W)$                                                                        |

| Status Affected: | None                                                                                       |

| Description:     | The eight bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |

| IORWF            | Inclusive OR W with f                                                                                                                                                  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] IORWF f,d                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                            |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                               |

| Status Affected: | Z                                                                                                                                                                      |

| Description:     | Inclusive OR the W register with regis-<br>ter 'f'. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>placed back in register 'f'. |

| MOVWF            | Move W to f                           |

|------------------|---------------------------------------|

| Syntax:          | [label] MOVWF f                       |

| Operands:        | $0 \leq f \leq 127$                   |

| Operation:       | $(W) \rightarrow (f)$                 |

| Status Affected: | None                                  |

| Description:     | Move data from W register to register |

| MOVF             | Move f                                                                                                                                                                                                                                                                                |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                           |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                                       |

| Status Affected: | Z                                                                                                                                                                                                                                                                                     |

| Description:     | The contents of register f is moved to<br>a destination dependant upon the sta-<br>tus of d. If $d = 0$ , destination is W reg-<br>ister. If $d = 1$ , the destination is file<br>register f itself. $d = 1$ is useful to test a<br>file register since status flag Z is<br>affected. |

| No Operation  |

|---------------|

| [label] NOP   |

| None          |

| No operation  |

| None          |

| No operation. |

|               |

stand-alone mode the PRO MATE II can read, verify or program PIC devices. It can also set code-protect bits in this mode.

#### 12.11 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, lowcost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.