Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

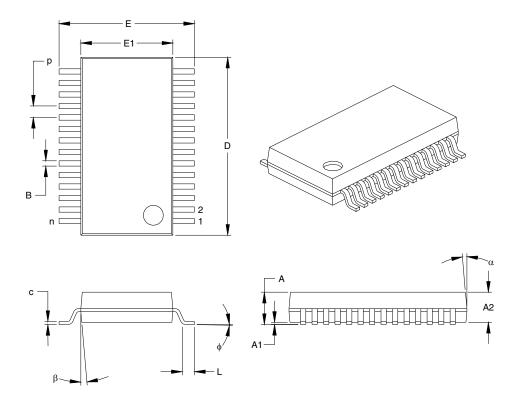

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c72a-20-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

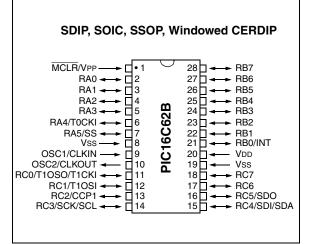

# **Pin Diagrams**

| Key Features<br>PIC <sup>®</sup> Mid-Range Reference Manual (DS33023) | PIC16C62B            | PIC16C72A            |

|-----------------------------------------------------------------------|----------------------|----------------------|

| Operating Frequency                                                   | DC - 20 MHz          | DC - 20 MHz          |

| Resets (and Delays)                                                   | POR, BOR (PWRT, OST) | POR, BOR (PWRT, OST) |

| Program Memory (14-bit words)                                         | 2K                   | 2K                   |

| Data Memory (bytes)                                                   | 128                  | 128                  |

| Interrupts                                                            | 7                    | 8                    |

| I/O Ports                                                             | Ports A,B,C          | Ports A,B,C          |

| Timers                                                                | 3                    | 3                    |

| Capture/Compare/PWM modules                                           | 1                    | 1                    |

| Serial Communications                                                 | SSP                  | SSP                  |

| 8-bit Analog-to-Digital Module                                        | —                    | 5 input channels     |

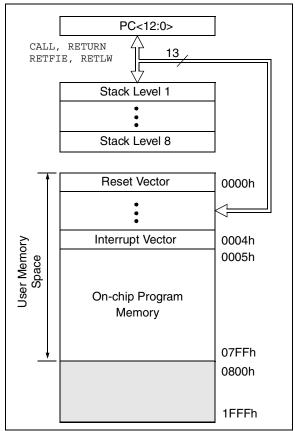

# 2.0 MEMORY ORGANIZATION

There are two memory blocks in each of these microcontrollers. Each block (Program Memory and Data Memory) has its own bus, so that concurrent access can occur.

Additional information on device memory may be found in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

# 2.1 Program Memory Organization

The PIC16C62B/72A devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. Each device has 2K x 14 words of program memory. Accessing a location above 07FFh will cause a wraparound.

The reset vector is at 0000h and the interrupt vector is at 0004h.

#### FIGURE 2-1: PROGRAM MEMORY MAP AND STACK

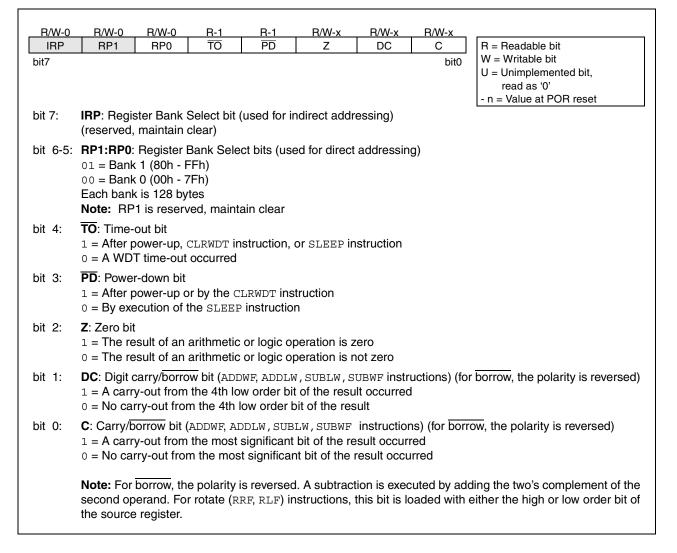

#### 2.2.2.1 STATUS REGISTER

The STATUS register, shown in Register 2-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, the write to these three bits is disabled. These bits are set or cleared according to the device logic. The TO and PD bits are not writable. The result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

- **Note 1:** The IRP and RP1 bits are reserved. Maintain these bits clear to ensure upward compatibility with future products.

- Note 2: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions.

# REGISTER 2-1: STATUS REGISTER (ADDRESS 03h, 83h)

# 6.1 <u>Timer2 Operation</u>

The Timer2 output is also used by the CCP module to generate the PWM "On-Time", and the PWM period with a match with PR2.

The TMR2 register is readable and writable, and is cleared on any device reset.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device reset (Power-on Reset, MCLR reset, Watchdog Timer reset or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

# 6.2 <u>Timer2 Interrupt</u>

The Timer2 module has an 8-bit period register PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon reset.

# 6.3 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module, which optionally uses it to generate shift clock.

# TABLE 6-1 REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Address | Name   | Bit 7       | Bit 6                    | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|--------|-------------|--------------------------|---------|---------|---------|--------|---------|---------|-------------------------|---------------------------------|

| 0Bh,8Bh | INTCON | GIE         | PEIE                     | TOIE    | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x               | 0000 000u                       |

| 0Ch     | PIR1   | _           | ADIF                     | _       | _       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | -00- 0000               | 0000 0000                       |

| 8Ch     | PIE1   | _           | ADIE                     | _       | _       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | -0 0000                 | 0000 0000                       |

| 11h     | TMR2   | Timer2 mod  | Timer2 module's register |         |         |         |        |         |         | 0000 0000               | 0000 0000                       |

| 12h     | T2CON  | _           | TOUTPS3                  | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000               | -000 0000                       |

| 92h     | PR2    | Timer2 Peri | imer2 Period Register    |         |         |         |        |         |         | 1111 1111               | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

| TABLE 8-1 | REGISTERS ASSOCIATED WITH SPI OPERATION |

|-----------|-----------------------------------------|

|           |                                         |

| Address | Name    | Bit 7      | Bit 6                                                    | Bit 5      | Bit 4     | Bit 3      | Bit 2                         | Bit 1  | Bit 0  | Value<br>POR<br>BOF | l,  | Valu<br>all o<br>res |      |

|---------|---------|------------|----------------------------------------------------------|------------|-----------|------------|-------------------------------|--------|--------|---------------------|-----|----------------------|------|

| 0Bh,8Bh | INTCON  | GIE        | PEIE                                                     | TOIE       | INTE      | RBIE       | T0IF                          | INTF   | RBIF   | 0000 0              | 00x | 0000                 | 000u |

| 0Ch     | PIR1    | —          | ADIF                                                     | —          | _         | SSPIF      | CCP1IF                        | TMR2IF | TMR1IF | -00                 | 000 | - 0                  | 0000 |

| 8Ch     | PIE1    | —          | ADIE                                                     |            | —         | SSPIE      | CCP1IE                        | TMR2IE | TMR1IE | -00                 | 000 | - 0                  | 0000 |

| 13h     | SSPBUF  | Synchronou | Synchronous Serial Port Receive Buffer/Transmit Register |            |           |            |                               |        |        | xxxx x              | xxx | uuuu                 | uuuu |

| 14h     | SSPCON  | WCOL       | SSPOV                                                    | SSPEN      | CKP       | SSPM3      | SSPM2                         | SSPM1  | SSPM0  | 0000 0              | 000 | 0000                 | 0000 |

| 94h     | SSPSTAT | SMP        | CKE                                                      | D/Ā        | Р         | S          | R/W                           | UA     | BF     | 0000 0              | 000 | 0000                 | 0000 |

| 85h     | TRISA   | _          |                                                          | PORTA D    | Data Dire | ction Regi | ster                          |        |        | 11 1                | 111 | 11                   | 1111 |

| 87h     | TRISC   | PORTC Data | a Direction                                              | n Register |           |            | PORTC Data Direction Register |        |        |                     |     |                      | 1111 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the SSP in SPI mode.

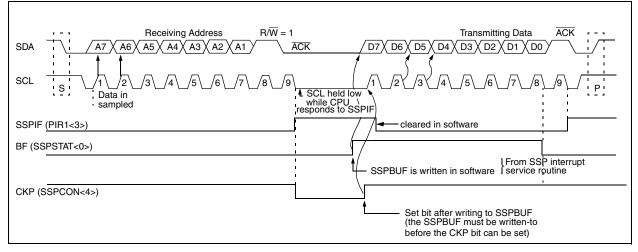

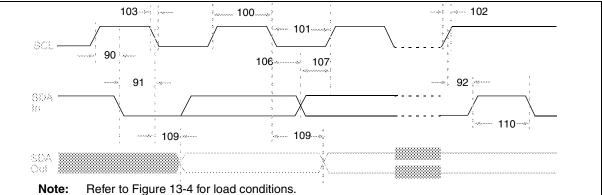

#### 8.3.1.3 TRANSMISSION

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and the CKP will be cleared by hardware, holding SCL low. Slave devices cause the master to wait by holding the SCL line low. The transmit data is loaded into the SSPBUF register, which in turn loads the SSPSR register. When bit CKP (SSP-CON<4>) is set, pin RC3/SCK/SCL releases SCL. When the SCL line goes high, the master may resume operating the SCL line and receiving data. The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 8-4).

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software, and the SSPSTAT register used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the masterreceiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not  $\overline{ACK}$ ), then the data transfer is complete. When the  $\overline{ACK}$  is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave then monitors for another occurrence of the START bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP.

FIGURE 8-4: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

# 9.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

Note: This section applies to the PIC16C72A only.

The analog-to-digital (A/D) converter module has five input channels.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number (refer to Application Note AN546 for use of A/D Converter). The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD) or the voltage level on the RA3/AN3/VREF pin.

The A/D converter has the feature of being able to operate while the device is in SLEEP mode. To operate in sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

Additional information on the A/D module is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

The A/D module has three registers. These registers are:

- A/D Result Register (ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

A device reset forces all registers to their reset state. This forces the A/D module to be turned off, and any conversion is aborted.

The ADCON0 register, shown in Figure 9-1, controls the operation of the A/D module. The ADCON1 register, shown in Figure 9-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference) or as digital I/O.

| R/W-0         | R/W-0                                                                                                                                                                                       | R/W-0                  | R/W-0      | R/W-0      | R/W-0                                | U-0 | R/W-0        |                                                                               |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------|------------|--------------------------------------|-----|--------------|-------------------------------------------------------------------------------|

| ADCS1<br>bit7 | ADCS0                                                                                                                                                                                       | CHS2                   | CHS1       | CHS0       | GO/DONE                              | _   | ADON<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0' |

| bit 7-6:      | ADCS1:ADCS0: A/D Conversion Clock Select bits<br>00 = Fosc/2<br>01 = Fosc/8<br>10 = Fosc/32<br>11 = FRC (clock derived from an internal RC oscillator)                                      |                        |            |            |                                      |     |              |                                                                               |

| bit 5-3:      | CHS2:CHS0: Analog Channel Select bits<br>000 = channel 0, (RA0/AN0)<br>001 = channel 1, (RA1/AN1)<br>010 = channel 2, (RA2/AN2)<br>011 = channel 3, (RA3/AN3)<br>100 = channel 4, (RA5/AN4) |                        |            |            |                                      |     |              |                                                                               |

| bit 2:        | GO/DON                                                                                                                                                                                      | E: A/D Co              | nversion   | Status bit |                                      |     |              |                                                                               |

|               |                                                                                                                                                                                             | onversion<br>onversion | not in pro |            | this bit starts t<br>s bit is automa |     |              | ware when the A/D                                                             |

| bit 1:        | Unimpler                                                                                                                                                                                    | nented: F              | Read as '0 | ı          |                                      |     |              |                                                                               |

| bit 0:        | <b>ADON</b> : $A_{1} = A/D c$                                                                                                                                                               | onverter r             |            |            | l consumes no                        |     | n ourront    |                                                                               |

## **REGISTER 9-1: ADCON0 REGISTER (ADDRESS 1Fh)**

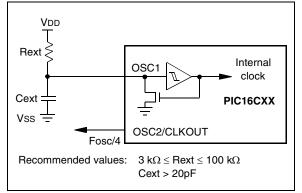

#### 10.2.3 RC OSCILLATOR

For timing insensitive applications, the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 10-4 shows how the R/C combination is connected to the PIC16CXXX.

#### FIGURE 10-4: RC OSCILLATOR MODE

# 10.3 <u>Reset</u>

The PIC16CXXX differentiates between various kinds of reset:

- Power-on Reset (POR)

- MCLR reset during normal operation

- MCLR reset during SLEEP

- WDT Reset (during normal operation)

- WDT Wake-up (during SLEEP)

- Brown-out Reset (BOR)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged by any other reset. Most other registers are reset to a "reset state" on Power-on Reset (POR), on the  $\overline{\text{MCLR}}$  and WDT Reset, on  $\overline{\text{MCLR}}$  reset during SLEEP, and on Brown-out Reset (BOR). They are not affected by a WDT Wake-up from SLEEP, which is viewed as the resumption of normal operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared depending on the reset situation, as indicated in Table 10-4. These bits are used in software to determine the nature of the reset. See Table 10-6 for a full description of reset states of all registers.

A simplified block diagram of the on-chip reset circuit is shown in Figure 10-5.

The PIC devices have a  $\overline{\text{MCLR}}$  noise filter in the  $\overline{\text{MCLR}}$  reset path. The filter will ignore small pulses. However, a valid  $\overline{\text{MCLR}}$  pulse must meet the minimum pulse width (TmcL, Specification #30).

No internal reset source (WDT, BOR, POR) will drive the  $\overline{\text{MCLR}}$  pin low.

# 10.8 <u>Time-out Sequence</u>

When a POR reset occurs, the PWRT delay starts (if enabled). When PWRT ends, the OST counts 1024 oscillator cycles (LP, XT, HS modes only). When OST completes, the device comes out of reset. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all.

If MCLR is kept low long enough, the time-outs will expire. Bringing MCLR high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16CXXX device operating in parallel.

#### **Status Register**

Table 10-5 shows the reset conditions for the STATUS, PCON and PC registers, while Table 10-6 shows the reset conditions for all the registers.

# 10.9 <u>Power Control/Status Register</u> (PCON)

The  $\overline{\text{BOR}}$  bit is unknown on Power-on Reset. If the Brown-out Reset circuit is used, the  $\overline{\text{BOR}}$  bit must be set by the user and checked on subsequent resets to see if it was cleared, indicating a Brown-out has occurred.

POR (Power-on Reset Status bit) is cleared on a Power-on Reset and unaffected otherwise. The user

| IRP            | RP1 | RP0 | TO | PD | Z | DC | С |

|----------------|-----|-----|----|----|---|----|---|

| DOON Berlieter |     |     |    |    |   |    |   |

| POR BOF |

|---------|

|---------|

TABLE 10-3 TIME-OUT IN VARIOUS SITUATIONS

| Oppillator Configuration | Power            | -up       | Brown out        | Wake-up from |  |

|--------------------------|------------------|-----------|------------------|--------------|--|

| Oscillator Configuration | <b>PWRTE</b> = 0 | PWRTE = 1 | Brown-out        | SLEEP        |  |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024Tosc     |  |

| RC                       | 72 ms            |           | 72 ms            | —            |  |

# TABLE 10-4 STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | ТО | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset                                          |

| 0   | x   | 0  | x  | Illegal, TO is set on POR                               |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

# TABLE 10-5 RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

#### 10.10.1 INT INTERRUPT

The external interrupt on RB0/INT pin is edge triggered: either rising, if bit INTEDG (OPTION\_REG<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 10.13 for details on SLEEP mode.

#### 10.10.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>). (Section 4.0)

#### 10.10.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>). (Section 3.2)

## 10.11 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt, (i.e., W register and STATUS register). This will have to be implemented in software.

Example 10-1 stores and restores the W and STATUS registers. The register, W\_TEMP, must be defined in each bank and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1).

The example:

- a) Stores the W register.

- b) Stores the STATUS register in bank 0.

- c) Stores the PCLATH register.

- d) Executes the interrupt service routine code (User-generated).

- e) Restores the STATUS register (and bank select bit).

- f) Restores the W and PCLATH registers.

#### EXAMPLE 10-1: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM

| MOVWF  | W_TEMP        | ;Copy W to TEMP register, could be bank one or zero     |

|--------|---------------|---------------------------------------------------------|

| SWAPF  | STATUS,W      | ;Swap status to be saved into W                         |

| CLRF   | STATUS        | ;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

| MOVWF  | STATUS_TEMP   | ;Save status to bank zero STATUS_TEMP register          |

| :      |               |                                                         |

| :(ISR) |               |                                                         |

| :      |               |                                                         |

| SWAPF  | STATUS_TEMP,W | ;Swap STATUS_TEMP register into W                       |

|        |               | ;(sets bank to original state)                          |

| MOVWF  | STATUS        | ;Move W into STATUS register                            |

| SWAPF  | W_TEMP,F      | ;Swap W_TEMP                                            |

| SWAPF  | W_TEMP,W      | ;Swap W_TEMP into W                                     |

|        |               |                                                         |

# TABLE 11-2 PIC16CXXX INSTRUCTION SET

| BYTE-ORIENTED FILE REGISTER OPERATIONS           ADDWF         f, d         Add W and f         1         0         0         0111         dfff         ffff         Z,DC,Z           ADDWF         f, d         Add W and f         1         0         0         0111         dfff         ffff         Z,DC,Z           ADDWF         f, d         Add W and f         1         0         0         0011         dfff         ffff         Z           CLRF         f         Clearf         1         0         0001         0000         0011         dfff         fff         Z           CLRW         -         Clear W         1         0         0001         0000         0011         dfff         fff         Z           DECFS         f, d         Decrement f, Skip if 0         1(2)         0         1111         dfff         Z           INCFS         f, d         Increment f, Skip if 0         1(2)         0         1111         dfff         Z           INCFF         f, d         Move f         1         00         0000         0xxx0         0000           INCF         f, d         Rotate Left fthrough Carry         1         0                                                                                                                                                                    | Mnemonic,<br>Operands |       | Description                 |       | 14-Bit Opcode |      |      |      | Status   | Notes |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|-----------------------------|-------|---------------|------|------|------|----------|-------|

| ADDWF         f, d         Add W and f         1         00         0111         dfff         ffff         C,DC,Z           ANDWF         f, d         AND W with f         1         00         0101         dfff         ffff         Z           CLRF         f         Clear W         1         00         0001         lfff         ffff         Z           COMF         f, d         Complement f         1         00         0011         dfff         ffff         Z           COMF         f, d         Decrement f         1         00         1011         dfff         ffff         Z           DECFS         f, d         Increment f         1         00         1010         dfff         fff         Z           INCF5         f, d         Increment f skip if 0         1(2)         00         1101         dfff         fff         Z           INCF52         f, d         Move f         1         00         0000         diff         fff         Z           MOVF         f, d         Move f         1         00         0100         dfff         fff         Z           MOVF         f, d         Rotate Leift through Carry <th>MSb</th> <th></th> <th></th> <th>LSb</th> <th>Affected</th> <th></th>                                                                                                  |                       |       |                             |       | MSb           |      |      | LSb  | Affected |       |

| ANDWF         f, d         AND W with f         1         00         0101         dfff         ffff         Z           CLRF         f         Clear W         1         00         0001         1fff         ffff         Z           COMF         f, d         Complement f         1         00         0011         dfff         ffff         Z           COMF         f, d         Decrement f, Skip if 0         1(2)         00         1011         dfff         ffff         Z           DECFSZ         f, d         Increment f, Skip if 0         1(2)         00         111         dfff         ffff         Z           MOVF         f, d         Move f         1         00         000         dffff         Z           MOVF f         d         Move f         1         00         000         000         000         000         000         000           RF         f, d         Rotate Left fhrough Carry         1         00         100         dfff         ffff         Z           SUBWF         f, d         Swap nibbles in f         1         00         010         dfff         ffff         Z           SUBWF         f, b </th <th>BYTE-ORIE</th> <th>NTED</th> <th>FILE REGISTER OPERATIONS</th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th>                            | BYTE-ORIE             | NTED  | FILE REGISTER OPERATIONS    |       |               |      |      |      |          |       |

| CLRF         f         Clear f         Clear f         1         00         0001         lfff         ffff         Z           COMF         f, d         Complement f         1         00         0001         dff         ffff         Z           DECF         f, d         Decrement f         1         00         1001         dff         ffff         Z           DECF         f, d         Decrement f, Skip if 0         1(2)         00         1010         dff         ffff         Z           INCFSZ         f, d         Increment f, Skip if 0         1(2)         00         1010         dfff         fff         Z           INCFSZ         f, d         Increment f, Skip if 0         1(2)         00         111         dfff         Z           INCFSZ         f, d         Increment f, Skip if C         1         00         000         dfff         Z           INCFSZ         f, d         Increment f, Skip if C         1         00         100         dfff         Z           MOVF         f, d         Move W to f         1         00         100         000         000         000         R         GR         GR         GR         GR                                                                                                                                                       | ADDWF                 | f, d  | Add W and f                 | 1     | 00            | 0111 | dfff | ffff | C,DC,Z   | 1,2   |

| CLRW         -         Clear W         1         00         0001         0000         0011         Z           COMF         f, d         Cormplement f         1         00         0011         dff ffff         Z           DECF         f, d         Decrement f, Skip if 0         1(2)         00         0011         dff ffff         Z           INCF f, d         Increment f, Skip if 0         1(2)         00         1010         dff ffff         Z           INCF f, d         Increment f, Skip if 0         1(2)         00         1010         dff ffff         Z           INCF f, d         Increment f, Skip if 0         1(2)         00         1011         dff ffff         Z           INCF f, d         Increment f, Skip if 0         1         00         0000         dff ffff         Z           MOVF f, d         Move f         1         00         0000         dff ffff         Z           SUBWF         f, d         Rotate Left ftmough Carry         1         00         0010         dff ffff         C,DC,Z           SUBWF         f, d         Subtract W from f         1         00         1010         dfff fffff         Z         Z           SUBWF                                                                                                                                   | ANDWF                 | f, d  | AND W with f                | 1     | 00            | 0101 | dfff | ffff | Z        | 1,2   |

| COMF         f, d         Complement f         1         00         1001         dfff         ffff         Z           DECFSZ         f, d         Decrement f, Skip if 0         1(2)         00         1011         dfff         ffff         Z           INCF         f, d         Increment f         1         00         1010         dfff         fffff         Z           INCFSZ         f, d         Increment f, Skip if 0         1(2)         00         1111         dfff         fffff         Z           IORWF         f, d         Increment f, Skip if 0         1(2)         00         1111         dfff         fffff         Z           MOVF         f         Move f         1         00         0000         dfff         fffff         Z           MOVF f         Move V to f         1         00         0000         dfff         fffff         Z           SUBWF f, d         Subtract W from f         1         00         100         dfff         fffff         C,DC,Z           SWAPF         f, d         Subtract W from f         1         00         0101         dfff         fffff         Z           BIT-ORIENTED FILE         Ecolusive OR W w                                                                                                                                             | CLRF                  | f     | Clear f                     | 1     | 00            | 0001 | lfff | ffff | Z        | 2     |

| DECF         f, d         Decrement f         1         00         0011         dfff         fff         Z           DECFSZ         f, d         Increment f         1         00         1010         dfff         fff         Z           INCF f, d         Increment f         1         00         1010         dfff         ffff         Z           INCFSZ         f, d         Increment f, Skip if 0         1(2)         00         1111         dfff         fff         Z           INCFSZ         f, d         Inclusive OR W with f         1         00         0100         dfff         fff         Z           MOVF         f, d         Move f         1         00         1000         dfff         ffff         Z           MOVWF         f, d         Rotate Left fthrough Carry         1         00         1101         dfff         fff         C         C         Z           SUBWF         f, d         Rotate Left fthrough Carry         1         00         1100         dfff         fff         C         C         C         C         C         C         C         C         C         C         C         C         C         C                                                                                                                                                                     | CLRW                  | -     | Clear W                     | 1     | 00            | 0001 | 0000 | 0011 |          |       |

| DECFSZ         f, d         Decrement f, Skip if 0         1(2)         0         1011         dfff ffff           INCF f, d         Increment f         1         0         1010         dfff ffff         Z           INCFSZ f, d         Increment f, Skip if 0         1(2)         0         1111         dfff ffff         Z           INCFSZ f, d         Inclusive CR W with f         1         0         0.000         dfff ffff         Z           MOVF f, d         Move f         1         0         0.000         dfff ffff         Z           MOVWF f         Move W to f         1         0         0.0000         0.000         C.C.C.C.C.C.C.C.C.C.C.C.C.C.C.C.C.C.C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | COMF                  | f, d  | Complement f                |       | 00            | 1001 | dfff | ffff | Z        | 1,2   |

| INCF         f, d         Increment f         1         00         1010         dfff         fff         Z           INCFSZ         f, d         Increment f, Skip if 0         1(2)         00         1111         dfff         fff         Z           IORWF         f, d         Move OR W with f         1         00         0100         dfff         fff         Z           MOVF         f, d         Move W to f         1         00         0000         lfff         fff         Z           MOVF         f         Move W to f         1         00         0000         lfff         Gff         Z           MOVF         f         Rotate Left fthrough Carry         1         00         1100         dfff         Gff         C         C           SUBWF         f, d         Rotate Left fthrough Carry         1         00         1100         dfff         fff         C         C,DC,Z           SUBWF         f, d         Subtract W from f         1         00         1010         dfff         ffff         C         C,DC,Z           SUBWF         f, d         Subtract W from f         1         01         010 bb         bfff         fffff                                                                                                                                                         | DECF                  | f, d  | Decrement f                 | 1     | 00            | 0011 | dfff | ffff | Z        | 1,2   |

| INCFSZ         f, d         Increment f, Skip if 0         1(2)         00         1111         dff ffff         Z           MOVF         f, d         Inclusive OR W with f         1         00         0100         dfff ffff         Z           MOVF         f, d         Move f         1         00         0000         dfff ffff         Z           MOVF         f, d         Move f         1         00         0000         dfff ffff         Z           MOVF         f, d         Move f         1         00         0000         dfff         ffff           NOP         No Operation         1         00         100         dfff         ffff         C           SUBWF         f, d         Rotate Left fthrough Carry         1         00         1100         dfff         ffff         C         C,DC,Z           SWAPF         f, d         Swap nibbles in f         1         00         110         dfff         ffff         Z           BIT-ORIENTED FILE         REGISTER OPERATIONS         1         1         01         0bb bfff         fffff         Z           BTFSS         f, b         Bit Test f, Skip if Set         1         1         1                                                                                                                                                    | DECFSZ                | f, d  | Decrement f, Skip if 0      | 1(2)  | 00            | 1011 | dfff | ffff |          | 1,2,3 |

| IORWF         f, d         Inclusive OR W with f         1         00         0100         dfff         ffff         Z           MOVF         f, d         Move f         1         00         0100         dfff         ffff         Z           MOVWF         f         Move W to f         1         00         0000         lfff         ffff         Z           MOVWF         f         Move W to f         1         00         0000         lfff         ffff         Z           NOP         No Operation         1         00         1000         dfff         ffff         C           RRF         f, d         Rotate Left fthrough Carry         1         00         1100         dfff         ffff         C,DC,Z           SWAPF         f, d         Subtract W from f         1         00         110         dfff         ffff         C,DC,Z           SWAPF         f, d         Exclusive OR W with f         1         01         00bb         bfff         ffff         Z           BIT-ORIENTED FILE         REGISTER OPERATIONS         1         11         01         01bb         bfff         ffff           BTFSS         f, b         Bit Test f, S                                                                                                                                                      | INCF                  | f, d  | Increment f                 |       | 00            | 1010 | dfff | ffff | Z        | 1,2   |

| MOVF         f, d         Move f         Move f         1         00         1000         dfff         ffff         Z           MOVWF         f         Move W to f         1         00         0000         0kx0         0000         Rff         ffff         C           NOP         -         No Operation         1         00         0000         0kx0         0000         Rk         ffff         C         C           RFF         f, d         Rotate Left fthrough Carry         1         00         1100         dfff         ffff         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C                                                                                                                                                                                                | INCFSZ                |       |                             | 1(2)  | 00            | 1111 | dfff | ffff |          | 1,2,3 |

| MOVWF         f         Move W to f         1         00         00000         lfff         ffff           NOP         -         No Operation         1         00         0000         0xx0         0000           RLF         f, d         Rotate Left fthrough Carry         1         00         1101         dfff         ffff         C           SUBWF         f, d         Subtract W from f         1         00         1100         dfff         ffff         C         D         C,DC,Z         D         C,DC,Z         D         D         D         1100         dfff         ffff         C         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D         D<                                                                                                                                                                                       |                       | ,     |                             | -     |               | 0100 |      |      | —        | 1,2   |

| NOP         -         No Operation         1         00         0000         0xxx         0000           RLF         f, d         Rotate Left f through Carry         1         00         1101         dfff ffff         C           SUBWF         f, d         Subtract W from f         1         00         0100         dfff ffff         C           SWAPF         f, d         Swap nibbles in f         1         00         0110         dfff ffff         C         C,DC,Z           SWAPF         f, d         Swap nibbles in f         1         00         0110         dfff ffff         C         C,DC,Z           XORWF         f, d         Exclusive OR W with f         1         00         0110         dfff ffff         Z           BIT-ORIENTED FILE REGISTER OPERATIONS         Bit Clear f         1         01         010bb         bfff fffff         Z           BFFSC         f, b         Bit Test f, Skip if Clear         1         1         11         11bb         bfff ffff           LITERAL AND CONTROL OPERATIONS         Interal with W         1         11         111         111k kkkk         kkkk         Z           ADDLW         k         Add literal and W         1                                                                                                                 | MOVF                  | f, d  | Move f                      | -     | 00            | 1000 | dfff | ffff | Z        | 1,2   |

| RLF         f, d         Rotate Leff through Carry         1         00         1101         dff ffff         C           RRF         f, d         State Right f through Carry         1         00         1101         dff ffff         C           SUBWF         f, d         Subtract W from f         1         00         1100         dff ffff         C         C,DC,Z           SWAPF         f, d         Swap nibbles in f         1         00         1101         dff ffff         C,DC,Z           SWAPF         f, d         Swap nibbles in f         1         00         1101         dff ffff         C,DC,Z           SWAPF         f, d         Swap nibbles in f         1         00         1101         dff ffff         Z           BIT-ORIENTED FILE         REGISTER OPERATIONS         I         1         01         00bb         bfff         ffff           BTFSS         f, b         Bit Test f, Skip if Clear         1         1         11         111b         bfff         ffff           LITERAL AND CONTROL OPERATIONS         I         11         111         1111         111k         kkkk kkkk         Z           CALL k         Calls subroutine         2         10 <td></td> <td>f</td> <td></td> <td>-</td> <td>00</td> <td>0000</td> <td>lfff</td> <td>ffff</td> <td></td> <td></td> |                       | f     |                             | -     | 00            | 0000 | lfff | ffff |          |       |

| RRFf, dRotate Right f through Carry1001100dfffffffCSUBWFf, dSubtract W from f1000010dfffffffC,DC,ZSWAPFf, dSwap nibbles in f1001110dfffffffC,DC,ZSWAPFf, dExclusive OR W with f1000110dfffffffZBIT-ORIENTED FILEREGISTER OPERATIONSBCFf, bBit Clear f10100bbbfffffffBSFf, bBit Set f10110bbbfffffffBTFSSf, bBit Test f, Skip if Clear1 (2)0111bbbfffffffBTFSSf, bBit Test f, Skip if Set1 (2)0111bbbfffffffLITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111kkkkkkkkZADDLWkAdd literal and W111111kkkk kkkkZClaulkCall subroutine2100kkk kkkkkTO,PDGOTOkGo to address2101kkk kkkkkZIORLWkInclusive OR literal with W1111000kkkk kkkkRETURReturn from interrupt20000000100IO,PDRETURNReturn from Subroutine200000000001000SLEEPGo into standby mode100 <td< td=""><td>NOP</td><td>-</td><td>No Operation</td><td>-</td><td>00</td><td>0000</td><td>0xx0</td><td>0000</td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                 | NOP                   | -     | No Operation                | -     | 00            | 0000 | 0xx0 | 0000 |          |       |

| SUBWFf, dSubtract W from f1000010dfffffffC,DC,ZSWAPFf, dSwap nibbles in f1001110dfffffffZBIT-ORIENTED FILE REGISTER OPERATIONSBCFf, bBit Clear f10100bbbfffffffBSFf, bBit Clear f10101bbbfffffffBTFSCf, bBit Test f, Skip if Clear1 (2)0110bbbfffffffBTFSSf, bBit Test f, Skip if Set1 (2)0111bbbfffffffLITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111111xkkkkkkkkZCALLkCall subroutine2100kkkkkkkZCALLkGo to address2101kkkkkkkZGOTOkGo to address210111100xkkkkZMOVLWkInclusive OR literal with W1111100xkkkkZMOVLWkReturn from interrupt20000001001TO,PDRETFIE-Return from interrupt21101xxkkkkkkkkRETURN-Return from Subroutine21101xxkkkkkkkkRETURN-Go into standby mode10000000101TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RLF                   | ,     | <b>o</b> ,                  | -     | 00            | 1101 | dfff | ffff | С        | 1,2   |

| SWAPFf, dSwap nibbles in f1001110dfffffffZBIT-ORIENTED FILE REGISTER OPERATIONSBCFf, bBit Clear f10100bbbfffffffZBSFf, bBit Clear f10101bbbfffffffZBTFSCf, bBit Test f, Skip if Clear110101bbbfffffffBTFSSf, bBit Test f, Skip if Set1120111bbbfffFfffLITERAL AND COVTROL OPERATIONSADDLWkAdd literal and W111111101kkkkkkkkZCALLkCall subroutine2100kkkkkkkKkkZCALLkCall subroutine2101kkkkkkkZGo to address2101kkkkkkkZOVUW1111000kkkkKkkZMOVLW1110000000001001Return from interrupt200000000001001Return from subroutine21101xxkkkkkkkRETURN -Return from Subroutine20000001001Go into standby mode10000000101 <td>RRF</td> <td>,</td> <td></td> <td></td> <td>00</td> <td>1100</td> <td>dfff</td> <td>ffff</td> <td>-</td> <td>1,2</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RRF                   | ,     |                             |       | 00            | 1100 | dfff | ffff | -        | 1,2   |

| XORWFf, dExclusive OR W with f1000110dfffffffZBIT-ORIENTED FILE REGISTER OPERATIONSBCFf, bBit Clear f10100bbbffffffffBSFf, bBit Set f10101bbbffffffffBTFSCf, bBit Test f, Skip if Clear1 (2)0110bbbffffffffBTFSSf, bBit Test f, Skip if Set1 (2)0111bbbfffffffLITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111111xkkkkkkkkZCALLkCall subroutine2100kkkkkkkZTO,PDGOTOkGo to address2101kkkkkkkKkkkZMOVLWkInclusive OR literal with W11100xkkkkKkkkZMOVLWkReturn from interrupt20000000001TO,PDRETFIE-Return from Subroutine21101xxkkkkKkkkFO,PDRETURN-Return from Subroutine20000000001TO,PDRETURN-Go into standby mode10000001001TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SUBWF                 | f, d  | Subtract W from f           | -     | 00            | 0010 | dfff | ffff | C,DC,Z   | 1,2   |

| Bit Clear fBSFf, bBit Clear f10100bbbfffffffBFFSCf, bBit Test f, Skip if Clear1 (2)0110bbbfffffffBTFSCf, bBit Test f, Skip if Clear1 (2)0110bbbfffffffBTFSSf, bBit Test f, Skip if Set1 (2)0110bbbfffffffLITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111111.kkkkkkkkZCALLkAdd literal and W1111001kkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkZCALLkGo to address210111000kkkkkkkkZGOTOkGo to address210111000kkkkZMOVLWkInclusive OR literal with W1111000kkkkZMOVLWkReturn from interrupt20000001001TO,PDGo into standby mode101000000001001TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SWAPF                 | f, d  | Swap nibbles in f           |       | 00            | 1110 | dfff | ffff |          | 1,2   |

| BCFf, bBit Clear f10100bbbfffffffBSFf, bBit Set f10101bbbfffffffBTFSCf, bBit Test f, Skip if Clear110101bbbfffffffBTFSSf, bBit Test f, Skip if Set11111bbbfffffffLITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111 xkkkkkkkZADDLWkAdd literal with W1111001 kkkkkkkkC,DC,ZCALLkCall subroutine2100000001101000GOTOkGo to address2101kkkkkkkkkkkZIORLWkInclusive OR literal with W1111000 kkkkkkkkZMOVLWkReturn from interrupt200000000001001RETFIE-Return with literal in W21101xxkkkkkkkkKRETURN-Return from Subroutine200000000001000SLEEP-Go into standby mode10000000110TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                     |       |                             | 1     | 00            | 0110 | dfff | ffff | Z        | 1,2   |

| BSFf, bBit Set f10101bbbfffffffBTFSCf, bBit Test f, Skip if Clear110110bbbfffffffBTFSSf, bBit Test f, Skip if Set110110bbbfffffffLITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111kkkkkkkC,DC,ZADDLWkAdd literal with W1111001kkkkkkkkZCALLkCall subroutine210000001100100TO,PDGOTOkGo to address21011kkkkkkkkkkkkZIORLWkInclusive OR literal with W1111000kkkkKkkkZMOVLWkReturn from interrupt200000000011001TO,PDRETLWkReturn with literal in W21101xxkkkkkkkkKkkkRETURN-Return from Subroutine200000000001001TO,PDSLEEP-Go into standby mode100000001100101TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -                     |       |                             |       |               |      |      |      |          |       |

| BTFSC<br>BTFSSf, b<br>bBit Test f, Skip if Clear<br>Bit Test f, Skip if Set1 (2)<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                       | ,     |                             |       | 01            | 00bb |      |      |          | 1,2   |

| BTFSSf, bBit Test f, Skip if Set1 (2)0111bbbfffffffLITERAL AND COVERATIONSADDLWkAdd literal and W111111 x kkkkkkkkC,DC,ZANDLWkAND literal with W111111 x kkkkkkkkC,DC,ZCALLkCall subroutine2100kkkkkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkZGOTOkGo to address2101kkkkkkkkkkkZIORLWkInclusive OR literal with W1111000kkkkKkkkZMOVLWkMove literal to W1111000kkkkkkkkZRETFIE-Return from interrupt200000000011001RETLWkReturn from Subroutine200000000001000SLEEP-Go into standby mode10000000110TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                     |       |                             | -     | 01            | 01bb | bfff | ffff |          | 1,2   |

| LITERAL AND CONTROL OPERATIONSADDLWkAdd literal and W111111 111xkkkkkkkkC,DC,ZANDLWkAND literal with W1111001kkkkkkkkC,DC,ZCALLkCall subroutine2100kkkkkkkkkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkZCALLkCall subroutine21000000011001000GOTOkGo to address2101kkkkkkkkkkkZIORLWkInclusive OR literal with W1111000kkkkkkkkZMOVLWkMove literal to W1110000000001001Return from interrupt200000000010011RETLIPReturn from interrupt20000000000100010001000SLEEP-Go into standby mode100000001101001TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                       |       |                             |       | 01            | 10bb | bfff | ffff |          | 3     |

| ADDLWkAdd literal and W111111 x kkkkkkkkC,DC,ZANDLWkAND literal with W1111001 kkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkZCLRWDT-Clear Watchdog Timer100000001100100TO,PDGOTOkGo to address2101kkkkkkkkkkkZIORLWkInclusive OR literal with W1111000kkkkkkkkZMOVLWkMove literal to W1110000000001001RETFIE-Return from interrupt200000000001001RETURN-Return with literal in W21101xxkkkkkkkkRETURN-Return from Subroutine200000000001000TO,PDSLEEP-Go into standby mode10000000110011TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                       |       |                             | 1 (2) | 01            | 11bb | bfff | ffff |          | 3     |

| ANDLWkAND literal with W1111001kkkkkkkkZCALLkCall subroutine2100kkkkkkkkkkkKkkkZCLRWDT-Clear Watchdog Timer100000001100100TO,PDGOTOkGo to address2101kkkkkkkkkkkKkkkZIORLWkInclusive OR literal with W1111000kkkkkkkkZMOVLWkMove literal to W111000000001001RETFIE-Return from interrupt200000000001001RETLWReturn with literal in W21101xxkkkkkkkkRETURN-Return from Subroutine200000000001000TO,PDSLEEP-Go into standby mode100000001100011TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                       | ND CO |                             |       |               |      |      |      |          | •     |

| CALL         k         Call subroutine         2         10         0kkk         kkkk         kkkkk         kkkk         kkkk         kkkkk         kkkk         kkkkk         kkkkkkkkkkkkkkkkkkkkkkkkkkkkkkkkkkkk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |       |                             | -     | 11            |      |      |      |          |       |

| CLRWDT         -         Clear Watchdog Timer         1         00         0000         0110         100           GOTO         k         Go to address         2         10         1kkk         kkkk         kkkk           IORLW         k         Inclusive OR literal with W         1         11         1000         kkkk         kkkk         Z           MOVLW         k         Move literal to W         1         11         1000         kkkk         kkkk         Z           RETFIE         -         Return from interrupt         2         00         0000         0000         1001           RETLW         k         Return with literal in W         2         11         01xx         kkkk         kkkk           RETURN         -         Return from Subroutine         2         00         0000         0000         1000           SLEEP         -         Go into standby mode         1         00         0000         0110         TO,PD                                                                                                                                                                                                                                                                                                                                                                    |                       |       |                             |       | 11            | 1001 | kkkk | kkkk | Z        |       |

| GOTO         k         Go to address         2         10         1kkk         kkkk         kkkk           IORLW         k         Inclusive OR literal with W         1         11         1000         kkkk         kkkk         Z           MOVLW         k         Move literal to W         1         11         1000         kkkk         kkkk         Z           RETFIE         -         Return from interrupt         2         00         0000         1001           RETLW         k         Return with literal in W         2         11         01xx         kkkk         kkkk           RETURN         -         Return from Subroutine         2         00         0000         1000           SLEEP         -         Go into standby mode         1         00         0000         011         TO, PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                     |       |                             |       | 10            | 0kkk | kkkk |      |          |       |

| IORLW         k         Inclusive OR literal with W         1         11         1000         kkkk         kkkk         Z           MOVLW         k         Move literal to W         1         11         1000         kkkk         kkkk         Z           MOVLW         k         Move literal to W         1         11         1000         kkkk         kkkk         kkkk           RETFIE         -         Return from interrupt         2         00         0000         0000         1001           RETLW         k         Return with literal in W         2         11         01xx         kkkk         kkkk           RETURN         -         Return from Subroutine         2         00         0000         0000         1000           SLEEP         -         Go into standby mode         1         00         0000         011         TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                       |       | 5                           | -     | 00            |      |      |      | TO,PD    |       |

| MOVLW         k         Move literal to W         1         11         00xx         kkkk         kkkk           RETFIE         -         Return from interrupt         2         00         0000         0000         1001           RETLW         k         Return with literal in W         2         11         01xx         kkkk         kkkk           RETURN         -         Return from Subroutine         2         00         0000         0000         1000           SLEEP         -         Go into standby mode         1         00         0000         011         TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                       |       |                             |       | 10            | 1kkk |      |      |          |       |

| RETFIE         -         Return from interrupt         2         00         0000         0000         1001           RETLW         k         Return with literal in W         2         11         01xx         kkkk         kkkk           RETURN         -         Return from Subroutine         2         00         0000         0000         1000           SLEEP         -         Go into standby mode         1         00         0000         011         TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                     |       |                             |       | 11            |      |      |      | Z        |       |

| RETLW         k         Return with literal in W         2         11         01xx         kkkk         kkkk           RETURN         -         Return from Subroutine         2         00         0000         0000         1000           SLEEP         -         Go into standby mode         1         00         0000         011         TO,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -                     | k     |                             | -     | 11            | 00xx | kkkk | kkkk |          |       |