Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c72a-20i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets; core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral feature section.

| Addr    | Name                    | Bit 7              | Bit 6                               | Bit 5         | Bit 4          | Bit 3           | Bit 2           | Bit 1       | Bit 0   | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(4) |

|---------|-------------------------|--------------------|-------------------------------------|---------------|----------------|-----------------|-----------------|-------------|---------|--------------------------|-------------------------------------|

| Bank 0  |                         |                    |                                     |               | •              |                 |                 |             |         |                          |                                     |

| 00h     | INDF <sup>(1)</sup>     | Addressing         | this locatio                        | cal register) | 0000 0000      | 0000 0000       |                 |             |         |                          |                                     |

| 01h     | TMR0                    | Timer0 mo          | dule's regist                       | er            |                |                 |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 02h     | PCL <sup>(1)</sup>      | Program C          | ounter's (PC                        | C) Least Sig  | nificant Byte  | !               |                 |             |         | 0000 0000                | 0000 0000                           |

| 03h     | STATUS <sup>(1)</sup>   | IRP <sup>(5)</sup> | RP1 <sup>(5)</sup>                  | RP0           | TO             | PD              | Z               | DC          | С       | 0001 1xxx                | 000q quuu                           |

| 04h     | FSR <sup>(1)</sup>      | Indirect dat       | a memory a                          | ddress poir   | nter           |                 |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 05h     | PORTA <sup>(6,7)</sup>  | —                  | _                                   | PORTA Da      | ta Latch whe   | en written: P   | ORTA pins w     | hen read    |         | 0x 0000                  | 0u 0000                             |

| 06h     | PORTB <sup>(6,7)</sup>  | PORTB Da           | ta Latch wh                         | en written: F | PORTB pins     | when read       |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 07h     | PORTC <sup>(6,7)</sup>  | PORTC Da           | ita Latch wh                        | en written: I | PORTC pins     | when read       |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 08h-09h | _                       | Unimpleme          | ented                               |               |                |                 |                 |             |         | —                        | —                                   |

| 0Ah     | PCLATH <sup>(1,2)</sup> | —                  | _                                   | _             | Write Buffe    | r for the uppe  | er 5 bits of th | e Program ( | Counter | 0 0000                   | 0 0000                              |

| 0Bh     | INTCON <sup>(1)</sup>   | GIE                | PEIE                                | TOIE          | INTE           | RBIE            | TOIF            | INTF        | RBIF    | 0000 000x                | 0000 000u                           |

| 0Ch     | PIR1                    | —                  | ADIF <sup>(3)</sup>                 | _             | _              | SSPIF           | CCP1IF          | TMR2IF      | TMR1IF  | -0 0000                  | -0 0000                             |

| 0Dh     | _                       | Unimpleme          | ented                               |               |                |                 |                 |             |         | —                        | —                                   |

| 0Eh     | TMR1L                   | Holding reg        | jister for the                      | Least Signi   | ificant Byte o | of the 16-bit 1 | MR1 registe     | r           |         | xxxx xxxx                | uuuu uuuu                           |

| 0Fh     | TMR1H                   | Holding reg        | jister for the                      | Most Signif   | icant Byte o   | f the 16-bit T  | MR1 register    | r           |         | xxxx xxxx                | uuuu uuuu                           |

| 10h     | T1CON                   | _                  | —                                   | T1CKPS1       | T1CKPS0        | T1OSCEN         | T1SYNC          | TMR1CS      | TMR1ON  | 00 0000                  | uu uuuu                             |

| 11h     | TMR2                    | Timer2 mo          | dule's regist                       | er            |                |                 |                 |             |         | 0000 0000                | 0000 0000                           |

| 12h     | T2CON                   | _                  | TOUTPS3                             | TOUTPS2       | TOUTPS1        | TOUTPS0         | TMR2ON          | T2CKPS1     | T2CKPS0 | -000 0000                | -000 0000                           |

| 13h     | SSPBUF                  | Synchrono          | us Serial Po                        | rt Receive E  | Buffer/Transr  | nit Register    |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 14h     | SSPCON                  | WCOL               | SSPOV                               | SSPEN         | СКР            | SSPM3           | SSPM2           | SSPM1       | SSPM0   | 0000 0000                | 0000 0000                           |

| 15h     | CCPR1L                  | Capture/Co         | Capture/Compare/PWM Register1 (LSB) |               |                |                 |                 |             |         |                          | uuuu uuuu                           |

| 16h     | CCPR1H                  | Capture/Co         | Capture/Compare/PWM Register1 (MSB) |               |                |                 |                 |             |         |                          | uuuu uuuu                           |

| 17h     | CCP1CON                 | —                  | _                                   | CCP1X         | CCP1Y          | CCP1M3          | CCP1M2          | CCP1M1      | CCP1M0  | 00 0000                  | 00 0000                             |

| 18h-1Dh | _                       | Unimpleme          | Unimplemented                       |               |                |                 |                 |             |         |                          | —                                   |

| 1Eh     | ADRES <sup>(3)</sup>    | A/D Result         | A/D Result Register                 |               |                |                 |                 |             |         |                          | uuuu uuuu                           |

| 1Fh     | ADCON0 <sup>(3)</sup>   | ADCS1              | ADCS0                               | CHS2          | CHS1           | CHS0            | GO/DONE         | —           | ADON    | 0000 00-0                | 0000 00-0                           |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0',

Shaded locations are unimplemented, read as '0'. **Note 1:** These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: A/D not implemented on the PIC16C62B, maintain as '0'.

4: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

5: The IRP and RP1 bits are reserved. Always maintain these bits clear.

6: On any device reset, these pins are configured as inputs.

7: This is the value that will be in the port output latch.

| Addr    | Name                    | Bit 7                                                                                         | Bit 6                                                            | Bit 5         | Bit 4         | Bit 3         | Bit 2           | Bit 1       | Bit 0   | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(4) |

|---------|-------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------|---------------|---------------|-----------------|-------------|---------|--------------------------|-------------------------------------|

| Bank 1  |                         |                                                                                               |                                                                  |               |               |               |                 |             |         |                          |                                     |

| 80h     | INDF <sup>(1)</sup>     | Addressing                                                                                    | this locatio                                                     | cal register) | 0000 0000     | 0000 0000     |                 |             |         |                          |                                     |

| 81h     | OPTION_REG              | RBPU         INTEDG         TOCS         TOSE         PSA         PS2         PS1         PS0 |                                                                  |               |               |               |                 |             |         | 1111 1111                | 1111 1111                           |

| 82h     | PCL <sup>(1)</sup>      | Program C                                                                                     | ounter's (PC                                                     | C) Least Sig  | nificant Byte | 1             |                 |             |         | 0000 0000                | 0000 0000                           |

| 83h     | STATUS <sup>(1)</sup>   | IRP <sup>(5)</sup>                                                                            | RP1 <sup>(5)</sup>                                               | RP0           | TO            | PD            | Z               | DC          | С       | 0001 1xxx                | 000q quuu                           |

| 84h     | FSR <sup>(1)</sup>      | Indirect dat                                                                                  | a memory a                                                       | ddress poir   | nter          |               |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 85h     | TRISA                   | —                                                                                             | —                                                                | PORTA Da      | ta Direction  | Register      |                 |             |         | 11 1111                  | 11 1111                             |

| 86h     | TRISB                   | PORTB Da                                                                                      | ta Direction                                                     | Register      |               |               |                 |             |         | 1111 1111                | 1111 1111                           |

| 87h     | TRISC                   | PORTC Da                                                                                      | PORTC Data Direction Register                                    |               |               |               |                 |             |         | 1111 1111                | 1111 1111                           |

| 88h-89h | _                       | Unimpleme                                                                                     | Unimplemented                                                    |               |               |               |                 |             |         | _                        | _                                   |

| 8Ah     | PCLATH <sup>(1,2)</sup> | —                                                                                             | _                                                                | —             | Write Buffe   | r for the upp | er 5 bits of th | e Program ( | Counter | 0 0000                   | 0 0000                              |

| 8Bh     | INTCON <sup>(1)</sup>   | GIE                                                                                           | PEIE                                                             | TOIE          | INTE          | RBIE          | TOIF            | INTF        | RBIF    | 0000 000x                | 0000 000u                           |

| 8Ch     | PIE1                    | —                                                                                             | ADIE <sup>(3)</sup>                                              | _             | —             | SSPIE         | CCP1IE          | TMR2IE      | TMR1IE  | -0 0000                  | -0 0000                             |

| 8Dh     | _                       | Unimpleme                                                                                     | ented                                                            |               |               |               |                 |             |         | _                        | _                                   |

| 8Eh     | PCON                    | —                                                                                             | _                                                                | —             | —             | _             | —               | POR         | BOR     | dd                       | uu                                  |

| 8Fh-91h | _                       | Unimpleme                                                                                     | ented                                                            |               |               |               |                 | •           |         | _                        | _                                   |

| 92h     | PR2                     | Timer2 Per                                                                                    | Timer2 Period Register                                           |               |               |               |                 |             |         |                          | 1111 1111                           |

| 93h     | SSPADD                  | Synchrono                                                                                     | Synchronous Serial Port (I <sup>2</sup> C mode) Address Register |               |               |               |                 |             |         |                          | 0000 0000                           |

| 94h     | SSPSTAT                 | SMP CKE D/Ā P S R/W UA BF                                                                     |                                                                  |               |               |               |                 |             |         | 0000 0000                | 0000 0000                           |

| 95h-9Eh | —                       | Unimpleme                                                                                     | ented                                                            |               |               |               |                 |             |         | —                        | —                                   |

| 9Fh     | ADCON1 <sup>(3)</sup>   | _                                                                                             | _                                                                | _             | _             | _             | PCFG2           | PCFG1       | PCFG0   | 000                      | 000                                 |

#### TABLE 2-1 SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0',

Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: A/D not implemented on the PIC16C62B, maintain as '0'.

4: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

5: The IRP and RP1 bits are reserved. Always maintain these bits clear.

**6:** On any device reset, these pins are configured as inputs.

7: This is the value that will be in the port output latch.

#### 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*).

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-1.

#### EXAMPLE 2-1: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

|          | movlw<br>movwf |       | ;initialize pointer<br>; to RAM |

|----------|----------------|-------|---------------------------------|

| NEXT     | clrf           | INDF  | ;clear INDF register            |

|          | incf           | FSR   | ;inc pointer                    |

|          | btfss          | FSR,4 | ;all done?                      |

|          | goto           | NEXT  | ;NO, clear next                 |

| CONTINUE |                |       |                                 |

|          | :              |       | ;YES, continue                  |

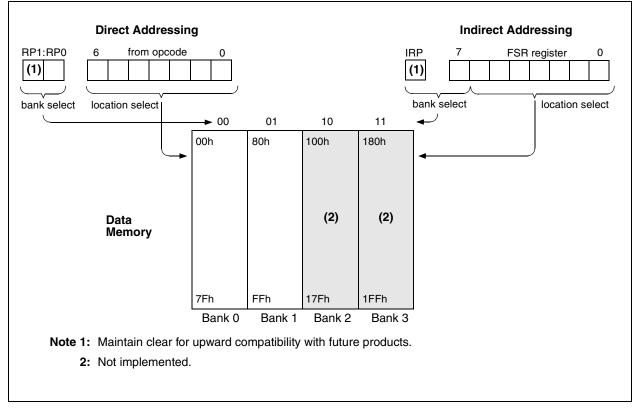

An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-3. However, IRP is not used in the PIC16C62B/72A.

#### FIGURE 2-3: DIRECT/INDIRECT ADDRESSING

#### TABLE 3-5 PORTC FUNCTIONS

| Name            | Bit# | Buffer<br>Type | Function                                                                    | TRISC<br>Override |

|-----------------|------|----------------|-----------------------------------------------------------------------------|-------------------|

| RC0/T1OSO/T1CKI | bit0 | ST             | Input/output port pin or Timer1 oscillator output/Timer1 clock input        | Yes               |

| RC1/T1OSI       | bit1 | ST             | Input/output port pin or Timer1 oscillator input                            | Yes               |

| RC2/CCP1        | bit2 | ST             | Input/output port pin or Capture1 input/Compare1 output/PWM1 output         | No                |

| RC3/SCK/SCL     | bit3 | ST             | RC3 can also be the synchronous serial clock for both SPI and $I^2C$ modes. | No                |

| RC4/SDI/SDA     | bit4 | ST             | RC4 can also be the SPI Data In (SPI mode) or data $I/O$ ( $I^2C$ mode).    | No                |

| RC5/SDO         | bit5 | ST             | Input/output port pin or Synchronous Serial Port data output                | No                |

| RC6             | bit6 | ST             | Input/output port pin                                                       | No                |

| RC7             | bit7 | ST             | Input/output port pin                                                       | No                |

Legend: ST = Schmitt Trigger input

#### TABLE 3-6SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7                         | Bit 6                           | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|-------------------------------|---------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 07h     | PORTC | RC7                           | RC7 RC6 RC5 RC4 RC3 RC2 RC1 RC0 |       |       |       |       |       |       |                          | uuuu uuuu                 |

| 87h     | TRISC | PORTC Data Direction Register |                                 |       |       |       |       |       |       | 1111 1111                | 1111 1111                 |

Legend: x = unknown, u = unchanged.

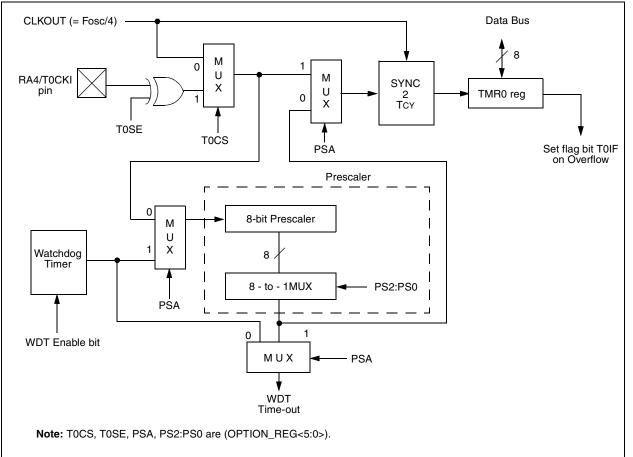

#### 4.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, (i.e., it can be changed "on-the-fly" during program execution).

Note: To avoid an unintended device RESET, a specific instruction sequence (shown in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, DS33023) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

#### 4.3 <u>Timer0 Interrupt</u>

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP since the timer is shut off during SLEEP.

#### FIGURE 4-2: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

#### TABLE 4-1 REGISTERS ASSOCIATED WITH TIMER0

| Address | Name       | Bit 7  | Bit 6                                 | Bit 5                         | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|------------|--------|---------------------------------------|-------------------------------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 01h     | TMR0       | Timer0 | imer0 module's register               |                               |       |       |       |       |       | xxxx xxxx                | uuuu uuuu                 |

| 0Bh,8Bh | INTCON     | GIE    | PEIE                                  | TOIE                          | INTE  | RBIE  | T0IF  | INTF  | RBIF  | 0000 000x                | 0000 000u                 |

| 81h     | OPTION_REG | RBPU   | RBPU INTEDG TOCS TOSE PSA PS2 PS1 PS0 |                               |       |       |       |       |       | 1111 1111                | 1111 1111                 |

| 85h     | TRISA      |        | _                                     | PORTA Data Direction Register |       |       |       |       |       | 11 1111                  | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

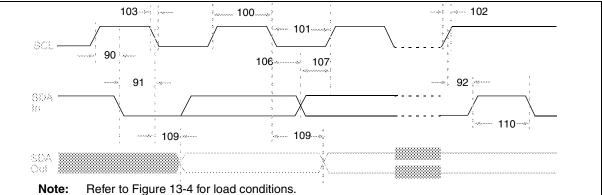

#### 8.3.1.2 RECEPTION

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no acknowledge ( $\overline{ACK}$ ) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set or bit SSPOV (SSPCON<6>) is set.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

#### FIGURE 8-3: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

| Receiving Address         R/W           SDA         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - </th <th>=0Receiving Data<br/>_ACK_D7XD6XD5XD4XD3XD2XD1XE<br/></th> <th></th> <th></th> | =0Receiving Data<br>_ACK_D7XD6XD5XD4XD3XD2XD1XE<br>                      |                                       |                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------|--------------------------------------|

| SSPI <u>F (PIR1&lt;3&gt;)</u><br>BF ( <u>SSPSTAT&lt;0&gt;)</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>Cleared in software</li> <li>SSPBUF register is read</li> </ul> |                                       | Bus Master<br>terminates<br>transfer |

| SSP <u>OV (SSPCON&lt;6&gt;)</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Bit SSPOV is set b                                                       | ecause the SSPBUF register is still f |                                      |

## 9.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

Note: This section applies to the PIC16C72A only.

The analog-to-digital (A/D) converter module has five input channels.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number (refer to Application Note AN546 for use of A/D Converter). The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD) or the voltage level on the RA3/AN3/VREF pin.

The A/D converter has the feature of being able to operate while the device is in SLEEP mode. To operate in sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

Additional information on the A/D module is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

The A/D module has three registers. These registers are:

- A/D Result Register (ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

A device reset forces all registers to their reset state. This forces the A/D module to be turned off, and any conversion is aborted.

The ADCON0 register, shown in Figure 9-1, controls the operation of the A/D module. The ADCON1 register, shown in Figure 9-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference) or as digital I/O.

| R/W-0         | R/W-0                                                                                                                                                                                       | R/W-0                                                                                                                                                  | R/W-0      | R/W-0      | R/W-0                                | U-0 | R/W-0        |                                                                               |  |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|--------------------------------------|-----|--------------|-------------------------------------------------------------------------------|--|--|--|--|--|

| ADCS1<br>bit7 | ADCS0                                                                                                                                                                                       | CHS2                                                                                                                                                   | CHS1       | CHS0       | GO/DONE                              | _   | ADON<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0' |  |  |  |  |  |

| bit 7-6:      | 00 = Foso<br>01 = Foso<br>10 = Foso                                                                                                                                                         | ADCS1:ADCS0: A/D Conversion Clock Select bits<br>00 = Fosc/2<br>01 = Fosc/8<br>10 = Fosc/32<br>11 = FRC (clock derived from an internal RC oscillator) |            |            |                                      |     |              |                                                                               |  |  |  |  |  |

| bit 5-3:      | CHS2:CHS0: Analog Channel Select bits<br>000 = channel 0, (RA0/AN0)<br>001 = channel 1, (RA1/AN1)<br>010 = channel 2, (RA2/AN2)<br>011 = channel 3, (RA3/AN3)<br>100 = channel 4, (RA5/AN4) |                                                                                                                                                        |            |            |                                      |     |              |                                                                               |  |  |  |  |  |

| bit 2:        | GO/DON                                                                                                                                                                                      | E: A/D Co                                                                                                                                              | nversion   | Status bit |                                      |     |              |                                                                               |  |  |  |  |  |

|               |                                                                                                                                                                                             | onversion<br>onversion                                                                                                                                 | not in pro |            | this bit starts t<br>s bit is automa |     |              | ware when the A/D                                                             |  |  |  |  |  |

| bit 1:        | Unimpler                                                                                                                                                                                    | nented: F                                                                                                                                              | Read as '0 | ı          |                                      |     |              |                                                                               |  |  |  |  |  |

| bit 0:        | <b>ADON</b> : $A_{1} = A/D c$                                                                                                                                                               | onverter r                                                                                                                                             |            |            | l consumes no                        |     | n ourront    |                                                                               |  |  |  |  |  |

#### **REGISTER 9-1: ADCON0 REGISTER (ADDRESS 1Fh)**

# 10.0 SPECIAL FEATURES OF THE CPU

The PIC16C62B/72A devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Mode Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- ID locations

- In-circuit serial programming<sup>™</sup> (ICSP)

These devices have a Watchdog Timer, which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The

#### FIGURE 10-1: CONFIGURATION WORD

other is the Power-up Timer (PWRT), which provides a fixed delay on power-up only and is designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

Additional information on special features is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

#### 10.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

| CP1    | CP0                                                                                                                                                                                               | CP1                                                                                              | CP0                           | CP1                     | CP0      | _                  | BODEN      | CP1 | CP0 | PWRTE | WDTE | FOSC1 | FOSC0                      | Register:                    | CONFIG |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------|-------------------------|----------|--------------------|------------|-----|-----|-------|------|-------|----------------------------|------------------------------|--------|

| bit13  |                                                                                                                                                                                                   |                                                                                                  |                               |                         |          |                    |            |     |     |       |      |       | bit0                       | Address:                     | 2007h  |

|        | <pre>bit 13-8 CP1:CP0: Code Protection bits <sup>(2)</sup> 5-4: 11 = Code protection off 10 = Upper half of program memory code protected 01 = Upper 3/4th of program memory code protected</pre> |                                                                                                  |                               |                         |          |                    |            |     |     |       |      |       |                            |                              |        |

|        |                                                                                                                                                                                                   | 00 = AII                                                                                         |                               |                         |          |                    |            |     |     |       |      |       |                            |                              |        |

| bit 7: | I                                                                                                                                                                                                 | Jnimpl                                                                                           | emen                          | ted: R                  | ead as   | s '1'              |            |     |     |       |      |       |                            |                              |        |

| bit 6: |                                                                                                                                                                                                   | BODEN: Brown-out Reset Enable bit <sup>(1)</sup><br>1 = BOR enabled<br>0 = BOR disabled          |                               |                         |          |                    |            |     |     |       |      |       |                            |                              |        |

| bit 3: |                                                                                                                                                                                                   | <b>PWRTE</b> : Power-up Timer Enable bit <sup>(1)</sup><br>1 = PWRT disabled<br>0 = PWRT enabled |                               |                         |          |                    |            |     |     |       |      |       |                            |                              |        |

| bit 2: | :                                                                                                                                                                                                 | WDTE: Watchdog Timer Enable bit<br>1 = WDT enabled<br>0 = WDT disabled                           |                               |                         |          |                    |            |     |     |       |      |       |                            |                              |        |

| bit 1- |                                                                                                                                                                                                   | FOSC1<br>11 = RC<br>10 = HS<br>01 = X1<br>00 = LF                                                | C oscil<br>S oscil<br>T oscil | lator<br>lator<br>lator | cillator | <sup>·</sup> Selec | ction bits |     |     |       |      |       |                            |                              |        |

| Note   |                                                                                                                                                                                                   |                                                                                                  |                               |                         |          |                    |            |     |     |       |      |       | dless of the<br>tion schem | e value of bit<br>ne listed. | PWRTE. |

#### 10.2 Oscillator Configurations

#### 10.2.1 OSCILLATOR TYPES

The PIC16CXXX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

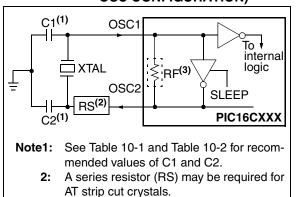

# 10.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

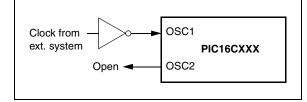

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 10-2). The PIC16CXXX oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can use an external clock source to drive the OSC1/CLKIN pin (Figure 10-3).

#### FIGURE 10-2: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

3: RF varies with the crystal chosen.

#### FIGURE 10-3: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

#### TABLE 10-1 CERAMIC RESONATORS

# Ranges Tested:

| Ranges Tested:                                                          |                                       |                      |             |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------|---------------------------------------|----------------------|-------------|--|--|--|--|--|--|--|--|

| Mode                                                                    | Freq                                  | OSC1                 | 0\$C2       |  |  |  |  |  |  |  |  |

| XT                                                                      | 455 kHz                               | 68 - 100 pF          | 68 - 100 pF |  |  |  |  |  |  |  |  |

|                                                                         | 2.0 MHz 15 - 68 pF                    |                      |             |  |  |  |  |  |  |  |  |

|                                                                         | 4.0 MHz 15 - 68 pF                    |                      |             |  |  |  |  |  |  |  |  |

| HS                                                                      | 8.0 MHz                               | 8.0 MHz 10 - 68 pF   |             |  |  |  |  |  |  |  |  |

|                                                                         | 16.0 MHz                              | 10,-22,0F            | 10 - 22 pF  |  |  |  |  |  |  |  |  |

| These values are for design guidance only. See notes at bottom of gage. |                                       |                      |             |  |  |  |  |  |  |  |  |

| Resonator                                                               | rs Used: 🔨                            | Par -                |             |  |  |  |  |  |  |  |  |

| 455 kHz                                                                 | Panasonie E                           | FO-A455K04B          | ± 0.3%      |  |  |  |  |  |  |  |  |

| 2.0 MHz                                                                 | Murata Érie (                         | CSA2.00MG            | $\pm 0.5\%$ |  |  |  |  |  |  |  |  |

| 4.0 MHz                                                                 | MHz Murata Erie CSA4.00MG ± 0.5%      |                      |             |  |  |  |  |  |  |  |  |

| 8.0 MAHZ                                                                | Murata Erie CSA8.00MT ± 0.5%          |                      |             |  |  |  |  |  |  |  |  |

| 16.0 MHz                                                                | 6.0 MHz Murata Erie CSA16.00MX ± 0.5% |                      |             |  |  |  |  |  |  |  |  |

| Resona                                                                  | ators did not hav                     | ve built-in capacito | ors.        |  |  |  |  |  |  |  |  |

# TABLE 10-2CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq  | Cap. Range<br>C1                   | Cap. Range<br>C2      |  |  |  |

|----------|------------------|------------------------------------|-----------------------|--|--|--|

| LP       | 32 kHz           | 33 pF                              |                       |  |  |  |

|          | 200 kHz          | 15 pF                              | 15 pF                 |  |  |  |

| XT       | 200 kHz 47-68 pF |                                    | 47-68 pF              |  |  |  |

|          | 1 MHz            | 15 pF 🔍                            | ↓15.pF<br>15.pF       |  |  |  |

|          | 4 MHz            | 15 pF 🕟                            | √15 pF                |  |  |  |

| HS       | 4 MHz            | ✓ 15 pF                            |                       |  |  |  |

|          | 8 MHz            | 15-33 pE>                          | 15-33 pF              |  |  |  |

|          | 20 MHz           | 15-33 pF                           | 15-33 pF              |  |  |  |

|          | values are       | <b>for design guida</b> r<br>page. | n <b>ce only.</b> See |  |  |  |

|          | Crys             | tals Used                          |                       |  |  |  |

| 32 kHz   | Epson C-00       | Epson C-001R32.768K-A ±            |                       |  |  |  |

| 200 kt/2 | STO XTL 2        | ± 20 PPM                           |                       |  |  |  |

| 1 MHz    | ECS ECS-         | ± 50 PPM                           |                       |  |  |  |

| 4 MHz    | ECS ECS-4        | 40-20-1                            | ± 50 PPM              |  |  |  |

| 8 MHz    | EPSON CA         | -301 8.000M-C                      | ± 30 PPM              |  |  |  |

**Note 1:** Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

EPSON CA-301 20.000M-C

20 MHz

2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

± 30 PPM

- **3:** Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- 4: Oscillator performance should be verified when migrating between devices (including PIC16C62A to PIC16C62B and PIC16C72 to PIC16C72A)

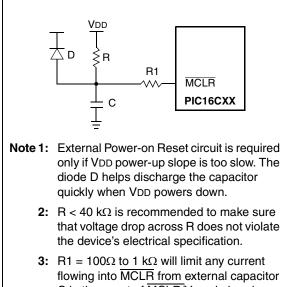

#### 10.4 Power-On Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.5V - 2.1V). To take advantage of the POR, just tie the  $\overline{\text{MCLR}}$  pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified (SVDD, parameter D004). For a slow rise time, see Figure 10-6.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met. Brown-out Reset may be used to meet the start-up conditions.

#### FIGURE 10-6: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

#### R1 = 100Ω to 1 kΩ will limit any current flowing into $\overline{MCLR}$ from external capacitor C in the event of $\overline{MCLR}/VPP$ pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

#### 10.5 Power-up Timer (PWRT)

The Power-up Timer provides a fixed nominal time-out (TPWRT, parameter #33) from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip-to-chip due to VDD, temperature and process variation. See DC parameters for details.

#### 10.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a delay of 1024 oscillator cycles (from OSC1 input) after the PWRT delay is over (TOST, parameter #32). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

Note: The OST delay may not occur when the device wakes from SLEEP.

#### 10.7 Brown-Out Reset (BOR)

The configuration bit, BODEN, can enable or disable the Brown-Out Reset circuit. If VPP falls below Vbor (parameter #35, about  $100\mu$ S), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a reset may not occur.

Once the brown-out occurs, the device will remain in brown-out reset until VDD rises above VBOR. The power-up timer then keeps the device in reset for TPWRT (parameter #33, about 72mS). If VDD should fall below VBOR during TPWRT, the brown-out reset process will restart when VDD rises above VBOR with the power-up timer reset. The power-up timer is always enabled when the brown-out reset circuit is enabled, regardless of the state of the PWRT configuration bit.

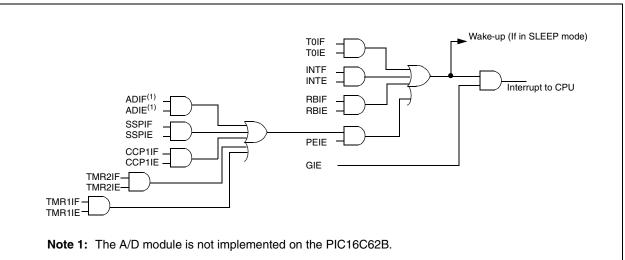

#### 10.10 Interrupts

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set regard- |

|-------|------------------------------------------------|

|       | less of the status of their corresponding      |

|       | mask bit or the GIE bit.                       |

A global interrupt enable bit, GIE (INTCON<7>) enables or disables all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt flag bits are set regardless of the status of the GIE bit. The GIE bit is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit, which reenables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register. The peripheral interrupt flags are contained in the special function registers PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupts, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine, the source of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles, depending on when the interrupt event occurs. The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit

#### FIGURE 10-7: INTERRUPT LOGIC

#### 10.13 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D and disable external clocks. Pull all I/O pins that are hi-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC, parameter D042).

#### 10.13.1 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- 1. External reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change, or some Peripheral Interrupts.

External  $\overline{\text{MCLR}}$  Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from SLEEP:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. CCP capture mode interrupt.

- 3. Special event trigger (Timer1 in asynchronous mode using an external clock. CCP1 is in compare mode).

- 4. SSP (Start/Stop) bit detect interrupt.

- 5. SSP transmit or receive in slave mode (SPI/I<sup>2</sup>C).

- 6. USART RX or TX (synchronous slave mode).

Other peripherals cannot generate interrupts since during SLEEP, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is

regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device resumes execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, a NOP should follow the SLEEP instruction.

#### 10.13.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

<sup>© 1998-2013</sup> Microchip Technology Inc.

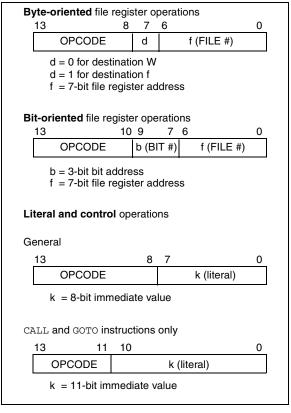

# 11.0 INSTRUCTION SET SUMMARY

Each PIC16CXXX instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16CXX instruction set summary in Table 11-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 11-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

#### TABLE 11-1 OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                           |

| W     | Working register (accumulator)                                                                                                                                                 |

| b     | Bit address within an 8-bit file register                                                                                                                                      |

| k     | Literal field, constant data or label                                                                                                                                          |

| x     | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                   |

| PC    | Program Counter                                                                                                                                                                |

| TO    | Time-out bit                                                                                                                                                                   |

| PD    | Power-down bit                                                                                                                                                                 |

| Z     | Zero bit                                                                                                                                                                       |

| DC    | Digit Carry bit                                                                                                                                                                |

| С     | Carry bit                                                                                                                                                                      |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 11-2 lists the instructions recognized by the MPASM assembler.

Figure 11-1 shows the general formats that the instructions can have.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

#### FIGURE 11-1: GENERAL FORMAT FOR INSTRUCTIONS

A description of each instruction is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

# PIC16C62B/72A

| RETFIE                  | Return from Interrupt       | RLF              | Rotate Left f through Carry                                                                                                                                                                                   |

|-------------------------|-----------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                 | [ label ] RETFIE            | Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                      |

| Operands:<br>Operation: | None $TOS \rightarrow PC$ , | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                             |

| -                       | $1 \rightarrow \text{GIE}$  | Operation:       | See description below                                                                                                                                                                                         |

| Status Affected:        | None                        | Status Affected: | С                                                                                                                                                                                                             |

|                         |                             | Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>stored back in register 'f'. |

| - | C 🚽 | Register f | ] |  |

|---|-----|------------|---|--|

|   |     |            |   |  |

| RETLW            | Return with Literal in W                                                                                                                                                            | RRF              | Rotate Right f through Carry                                                                                                                                                                                   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            | Syntax:          | [label] RRF f,d                                                                                                                                                                                                |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                   | Operands:        | $0 \leq f \leq 127$                                                                                                                                                                                            |

| Operation:       | $k \rightarrow (W);$                                                                                                                                                                |                  | d ∈ [0,1]                                                                                                                                                                                                      |

|                  | $TOS \rightarrow PC$                                                                                                                                                                | Operation:       | See description below                                                                                                                                                                                          |

| Status Affected: | None                                                                                                                                                                                | Status Affected: | С                                                                                                                                                                                                              |

| Description:     | The W register is loaded with the eight<br>bit literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a two cycle<br>instruction. | Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>placed back in register 'f'. |

|                  |                                                                                                                                                                                     |                  | C Register f                                                                                                                                                                                                   |

| RETURN           | Return from Subroutine                                                                                                                                  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] RETURN                                                                                                                                          |  |  |  |  |  |

| Operands:        | None                                                                                                                                                    |  |  |  |  |  |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                    |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                    |  |  |  |  |  |

| Description:     | Return from subroutine. The stack is<br>POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a two cycle instruction. |  |  |  |  |  |

| SLEEP            |                                                                                                                                                                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                                                                             |

| Operands:        | None                                                                                                                                                                                                                                                                                      |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \ \text{prescaler}, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                                                                               |

| Status Affected: | TO, PD                                                                                                                                                                                                                                                                                    |

| Description:     | The power-down status bit, $\overline{\text{PD}}$ is<br>cleared. Time-out status bit, $\overline{\text{TO}}$ is<br>set. Watchdog Timer and its pres-<br>caler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped.<br>See Section 10.13 for more details. |

© 1998-2013 Microchip Technology Inc.

# 12.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB™ IDE Software

- Assemblers/Compilers/Linkers

- MPASM Assembler

- MPLAB-C17 and MPLAB-C18 C Compilers

- MPLINK/MPLIB Linker/Librarian

- Simulators

- MPLAB-SIM Software Simulator

- Emulators

- MPLAB-ICE Real-Time In-Circuit Emulator

- PICMASTER<sup>®</sup>/PICMASTER-CE In-Circuit Emulator

- ICEPIC™

- In-Circuit Debugger

- MPLAB-ICD for PIC16F877

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- Low-Cost Demonstration Boards

- SIMICE

- PICDEM-1

- PICDEM-2

- PICDEM-3

- PICDEM-17

- SEEVAL®

- KEELOQ<sup>®</sup>