Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Betans                     |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

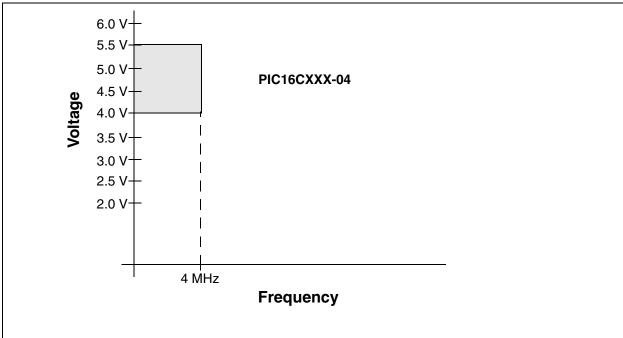

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c72at-04-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 MEMORY ORGANIZATION

There are two memory blocks in each of these microcontrollers. Each block (Program Memory and Data Memory) has its own bus, so that concurrent access can occur.

Additional information on device memory may be found in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

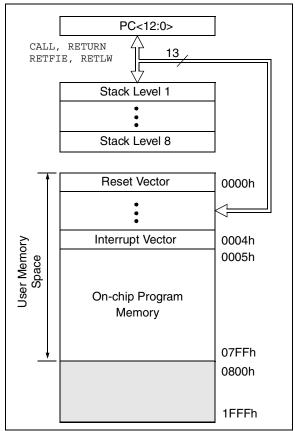

# 2.1 Program Memory Organization

The PIC16C62B/72A devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. Each device has 2K x 14 words of program memory. Accessing a location above 07FFh will cause a wraparound.

The reset vector is at 0000h and the interrupt vector is at 0004h.

## FIGURE 2-1: PROGRAM MEMORY MAP AND STACK

#### 2.2.2.3 INTCON REGISTER

The INTCON Register is a readable and writable register, which contains various interrupt enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts. Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# REGISTER 2-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| R/W-0<br>GIE | R/W-0<br>PEIE                                                                                                                                                                                      | R/W-0<br>T0IE                                                                                                         | R/W-0<br>INTE | R/W-0<br>RBIE | R/W-0<br>T0IF | R/W-0      | R/W-x<br>RBIF | R = Readable bit                                                 |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------|---------------|---------------|------------|---------------|------------------------------------------------------------------|--|--|--|

| bit7         | PEIE                                                                                                                                                                                               | TUIE                                                                                                                  | INTE          | RBIE          | TUIF          | INTE       | BIF<br>bit0   | R = Readable bit<br>W = Writable bit<br>- n = Value at POR reset |  |  |  |

| bit 7:       | 1 = Enab                                                                                                                                                                                           | GIE: Global Interrupt Enable bit<br>1 = Enables all un-masked interrupts<br>0 = Disables all interrupts               |               |               |               |            |               |                                                                  |  |  |  |

| bit 6:       | <b>PEIE</b> : Peripheral Interrupt Enable bit<br>1 = Enables all un-masked peripheral interrupts<br>0 = Disables all peripheral interrupts                                                         |                                                                                                                       |               |               |               |            |               |                                                                  |  |  |  |

| bit 5:       | 1 = Enab                                                                                                                                                                                           | <b>TOIE</b> : TMR0 Overflow Interrupt Enable bit<br>1 = Enables the TMR0 interrupt<br>0 = Disables the TMR0 interrupt |               |               |               |            |               |                                                                  |  |  |  |

| bit 4:       | IINTE: RB0/INT External Interrupt Enable bit<br>1 = Enables the RB0/INT external interrupt<br>0 = Disables the RB0/INT external interrupt                                                          |                                                                                                                       |               |               |               |            |               |                                                                  |  |  |  |

| bit 3:       | 1 = Enab                                                                                                                                                                                           | 3 Port Cha<br>les the RE<br>bles the RE                                                                               | port char     | nge interru   | pt            |            |               |                                                                  |  |  |  |

| bit 2:       | 1 = TMR(                                                                                                                                                                                           | R0 Overflo<br>0 register l<br>0 register o                                                                            | has overflo   | owed (soft    | ware must     | clear bit) |               |                                                                  |  |  |  |

| bit 1:       | INTF: RB0/INT External Interrupt Flag bit<br>1 = The RB0/INT external interrupt occurred (software must clear bit)<br>0 = The RB0/INT external interrupt did not occur                             |                                                                                                                       |               |               |               |            |               |                                                                  |  |  |  |

| bit 0:       | <b>RBIF</b> : RB Port Change Interrupt Flag bit<br>1 = At least one of the RB7:RB4 input pins have changed state (clear by reading PORTB)<br>0 = None of the RB7:RB4 input pins have changed state |                                                                                                                       |               |               |               |            |               |                                                                  |  |  |  |

# PIC16C62B/72A

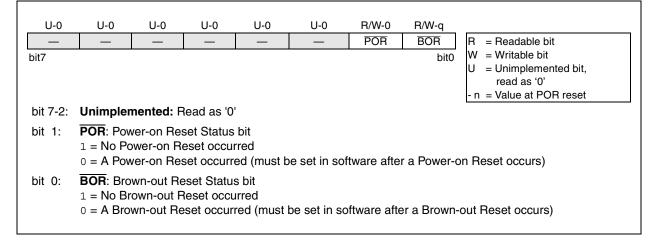

### 2.2.2.6 PCON REGISTER

The Power Control register (PCON) contains flag bits to allow differentiation between a Power-on Reset (POR), Brown-Out Reset (BOR) and resets from other sources.

Note: On Power-on Reset, the state of the BOR bit is unknown and is not predictable. If the BODEN bit in the configuration word is set, the user must first set the BOR bit on a POR, and check it on subsequent resets. If BOR is cleared while POR remains set, a Brown-out reset has occurred. If the BODEN bit is clear, the BOR bit may be ignored.

# REGISTER 2-6: PCON REGISTER (ADDRESS 8Eh)

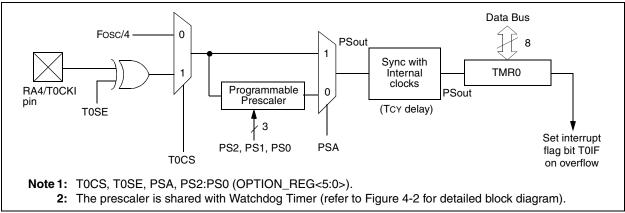

# 4.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Read and write

- INT on overflow

- 8-bit software programmable prescaler

- INT or EXT clock select

- EXT clock edge select

Figure 4-1 is a simplified block diagram of the Timer0 module.

Additional information on timer modules is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

# 4.1 <u>Timer0 Operation</u>

Timer0 can operate as a timer or as a counter.

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed below.

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization. Additional information on external clock requirements is available in the Electrical Specifications section of this manual, and in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

# 4.2 <u>Prescaler</u>

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 4-2). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. There is only one prescaler available which is shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The prescaler is not readable or writable.

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

Clearing bit PSA will assign the prescaler to the Timer0 module. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable.

Setting bit PSA will assign the prescaler to the Watchdog Timer (WDT). When the prescaler is assigned to the WDT, prescale values of 1:1, 1:2, ..., 1:128 are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment or ratio.

### FIGURE 4-1: TIMER0 BLOCK DIAGRAM

# 6.1 <u>Timer2 Operation</u>

The Timer2 output is also used by the CCP module to generate the PWM "On-Time", and the PWM period with a match with PR2.

The TMR2 register is readable and writable, and is cleared on any device reset.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device reset (Power-on Reset, MCLR reset, Watchdog Timer reset or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

# 6.2 <u>Timer2 Interrupt</u>

The Timer2 module has an 8-bit period register PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon reset.

# 6.3 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module, which optionally uses it to generate shift clock.

# TABLE 6-1 REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Address | Name   | Bit 7       | Bit 6                 | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|--------|-------------|-----------------------|---------|---------|---------|--------|---------|---------|-------------------------|---------------------------------|

| 0Bh,8Bh | INTCON | GIE         | PEIE                  | TOIE    | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x               | 0000 000u                       |

| 0Ch     | PIR1   | _           | ADIF                  | _       | _       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | -00- 0000               | 0000 0000                       |

| 8Ch     | PIE1   | _           | ADIE                  | _       | _       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | -0 0000                 | 0000 0000                       |

| 11h     | TMR2   | Timer2 mod  | dule's registe        | r       |         |         |        |         |         | 0000 0000               | 0000 0000                       |

| 12h     | T2CON  | _           | TOUTPS3               | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000               | -000 0000                       |

| 92h     | PR2    | Timer2 Peri | imer2 Period Register |         |         |         |        |         |         | 1111 1111               | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

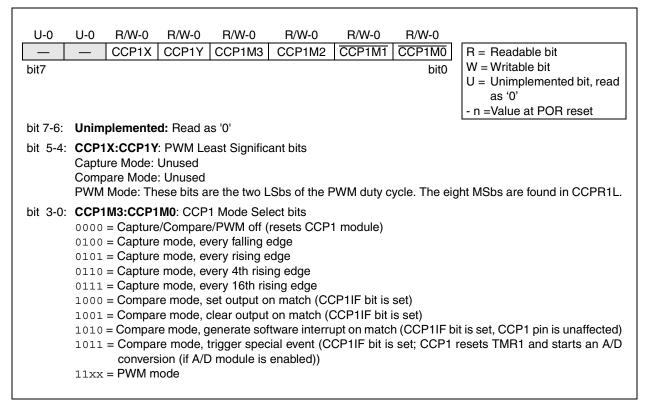

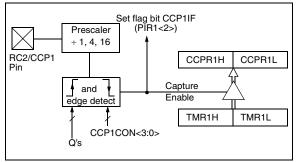

# 7.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The CCP (Capture/Compare/PWM) module contains a 16-bit register, which can operate as a 16-bit capture register, as a 16-bit compare register or as a PWM master/slave duty cycle register. Table 7-1 shows the timer resources of the CCP module modes.

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable. Additional information on the CCP module is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

# TABLE 7-1CCP MODE - TIMER<br/>RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

# TABLE 7-2INTERACTION OF TWO CCP MODULES

| CCPx Mode | CCPy Mode | Interaction                                                                           |

|-----------|-----------|---------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time-base.                                                                  |

| Capture   | Compare   | The compare should be configured for the special event trigger, which clears TMR1.    |

| Compare   | Compare   | The compare(s) should be configured for the special event trigger, which clears TMR1. |

| PWM       | PWM       | The PWMs will have the same frequency and update rate (TMR2 interrupt).               |

| PWM       | Capture   | None.                                                                                 |

| PWM       | Compare   | None.                                                                                 |

# **REGISTER 7-1:CCP1CON REGISTER (ADDRESS 17h)**

# 7.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register, when an event occurs on pin RC2/CCP1. An event is defined as:

- every falling edge

- · every rising edge

- every 4th rising edge

- every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit ,CCP1IF (PIR1<2>), is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### FIGURE 7-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

### 7.1.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

**Note:** If the RC2/CCP1 is configured as an output, a write to the port can cause a capture condition.

### 7.1.2 TIMER1 MODE SELECTION

Timer1 must be running in timer mode or synchronized counter mode for the CCP module to use the capture feature. In asynchronous counter mode, the capture operation may not work consistently.

### 7.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should clear CCP1IE (PIE1<2>) before changing the capture mode to avoid false interrupts. Clear the interrupt flag bit, CCP1IE before setting CCP1IE.

# 7.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in capture mode, the prescaler counter is cleared. This means that any reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 7-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

# EXAMPLE 7-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;Turn CCP module off    |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | ;Load the W reg with    |

|       |             | ; the new prescaler     |

|       |             | ; mode value and CCP ON |

| MOVWF | CCP1CON     | ;Load CCP1CON with this |

|       |             | ; value                 |

#### 7.3.3 SET-UP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM on-time by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

# TABLE 7-4 EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 5.5       |

### TABLE 7-5 REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address | Name    | Bit 7     | Bit 6                               | Bit 5      | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|---------|-----------|-------------------------------------|------------|---------|---------|--------|---------|---------|-------------------------|---------------------------------|

| 0Bh,8Bh | INTCON  | GIE       | PEIE                                | T0IE       | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x               | 0000 000u                       |

| 0Ch     | PIR1    | —         | ADIF                                | _          | —       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | -0 0000                 | -0 0000                         |

| 8Ch     | PIE1    | —         | ADIE                                | _          | —       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | -0 0000                 | -0 0000                         |

| 87h     | TRISC   | PORTC D   | PORTC Data Direction Register       |            |         |         |        |         |         |                         | 1111 1111                       |

| 11h     | TMR2    | Timer2 mo | odule's regis                       | ter        |         |         |        |         |         | 0000 0000               | 0000 0000                       |

| 92h     | PR2     | Timer2 mo | odule's perio                       | d register |         |         |        |         |         | 1111 1111               | 1111 1111                       |

| 12h     | T2CON   | —         | TOUTPS3                             | TOUTPS2    | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000               | -000 0000                       |

| 15h     | CCPR1L  | Capture/C | Capture/Compare/PWM register1 (LSB) |            |         |         |        |         |         |                         | uuuu uuuu                       |

| 16h     | CCPR1H  | Capture/C | Capture/Compare/PWM register1 (MSB) |            |         |         |        |         |         |                         | uuuu uuuu                       |

| 17h     | CCP1CON | —         | _                                   | CCP1X      | CCP1Y   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00 0000                 | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PWM and Timer2.

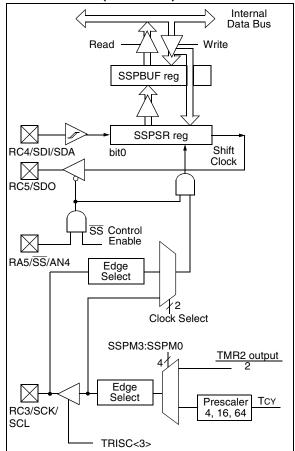

# 8.0 SYNCHRONOUS SERIAL PORT (SSP) MODULE

# 8.1 SSP Module Overview

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

For more information on SSP operation (including an I<sup>2</sup>C Overview), refer to the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023). Also, refer to Application Note AN578, *"Use of the SSP Module in the I<sup>2</sup>C Multi-Master Environment."*

# 8.2 SPI Mode

This section contains register definitions and operational characteristics of the SPI module.

Additional information on SPI operation may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

8.2.1 OPERATION OF SSP MODULE IN SPI MODE

A block diagram of the SSP Module in SPI Mode is shown in Figure 8-1.

The SPI mode allows 8-bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, three pins are used:

- Serial Data Out (SDO)RC5/SDO

- Serial Data In (SDI)RC4/SDI/SDA

- Serial Clock (SCK)RC3/SCK/SCL

Additionally, a fourth pin may be used when in a slave mode of operation:

Slave Select (SS)RA5/SS/AN4

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- Master Operation (SCK is the clock output)

- Slave Mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Clock Edge (Output data on rising/falling edge of SCK)

- Clock Rate (master operation only)

- Slave Select Mode (Slave mode only)

To enable the serial port, SSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON reg-

ister, and then set bit SSPEN. This configures the SDI, SDO, SCK and  $\overline{SS}$  pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISC register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (master operation) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set (if used)

Note: When the SPI is in Slave Mode with  $\overline{SS}$  pin control enabled, (SSPCON<3:0> = 0100) the SPI module will reset if the  $\overline{SS}$  pin is set to VDD.

**Note:** If the SPI is used in Slave Mode with CKE = '1', then the  $\overline{SS}$  pin control must be enabled.

# FIGURE 8-1: SSP BLOCK DIAGRAM (SPI MODE)

#### 8.3.2 MASTER OPERATION

Master operation is supported in firmware using interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared by a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is idle and both the S and P bits are clear.

In master operation, the SCL and SDA lines are manipulated in software by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt if enabled):

- START condition

- STOP condition

- Byte transfer completed

Master operation can be done with either the slave mode idle (SSPM3:SSPM0 = 1011) or with the slave active. When both master operation and slave modes are used, the software needs to differentiate the source(s) of the interrupt.

For more information on master operation, see AN554 - Software Implementation of  $I^2C$  Bus Master.

# 8.3.3 MULTI-MASTER OPERATION

In multi-master operation, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle and both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In multi-master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost, these are:

- Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed, an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to re-transfer the data at a later time.

For more information on master operation, see AN578 - Use of the SSP Module in the of  $l^2C$  Multi-Master Environment.

| Address  | Name    | Bit 7                         | Bit 6              | Bit 5                    | Bit 4     | Bit 3     | Bit 2    | Bit 1  | Bit 0  | PC   | e on<br>DR,<br>DR | all o | e on<br>ther<br>ets |

|----------|---------|-------------------------------|--------------------|--------------------------|-----------|-----------|----------|--------|--------|------|-------------------|-------|---------------------|

| 0Bh, 8Bh | INTCON  | GIE                           | PEIE               | TOIE                     | INTE      | RBIE      | T0IF     | INTF   | RBIF   | 0000 | 000x              | 0000  | 000u                |

| 0Ch      | PIR1    | _                             | ADIF               | _                        |           | SSPIF     | CCP1IF   | TMR2IF | TMR1IF | - 0  | 0000              | - 0   | 0000                |

| 8Ch      | PIE1    | _                             | ADIE               | _                        | —         | SSPIE     | CCP1IE   | TMR2IE | TMR1IE | - 0  | 0000              | - 0   | 0000                |

| 13h      | SSPBUF  | Synchronou                    | is Serial F        | Port Recei               | ve Buffer | /Transmit | Register | •      | •      | xxxx | xxxx              | uuuu  | uuuu                |

| 93h      | SSPADD  | Synchronou                    | is Serial F        | Port (I <sup>2</sup> C n | node) Ad  | dress Reg | jister   |        |        | 0000 | 0000              | 0000  | 0000                |

| 14h      | SSPCON  | WCOL                          | SSPOV              | SSPEN                    | CKP       | SSPM3     | SSPM2    | SSPM1  | SSPM0  | 0000 | 0000              | 0000  | 0000                |

| 94h      | SSPSTAT | SMP <sup>(1)</sup>            | CKE <sup>(1)</sup> | D/A                      | Р         | S         | R/W      | UA     | BF     | 0000 | 0000              | 0000  | 0000                |

| 87h      | TRISC   | PORTC Data Direction register |                    |                          |           |           |          |        | •      | 1111 | 1111              | 1111  | 1111                |

# TABLE 8-3REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in SPI mode.

**Note 1:** Maintain these bits clear in  $I^2C$  mode.

# 9.4 <u>A/D Conversions</u>

| Note: | The GO/DONE bit should NOT be set in        |

|-------|---------------------------------------------|

|       | the same instruction that turns on the A/D. |

#### 9.5 Use of the CCP Trigger

An A/D conversion can be started by the "special event trigger" of the CCP1 module. This requires that the CCP1M3:CCP1M0 bits (CCP1CON<3:0>) be programmed as 1011 and that the A/D module be enabled (ADON bit is set). When the trigger occurs, the

TABLE 9-2 SUMMARY OF A/D REGISTERS

GO/DONE bit will be set, starting the A/D conversion, and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D acquisition period with minimal software overhead. The appropriate analog input channel must be selected and the minimum acquisition time must pass before the "special event trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), then the "special event trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

| Address | Name   | Bit 7   | Bit 6      | Bit 5   | Bit 4       | Bit 3   | Bit 2   | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all other Resets |

|---------|--------|---------|------------|---------|-------------|---------|---------|--------|--------|-------------------------|---------------------------|

| 0Bh,8Bh | INTCON | GIE     | PEIE       | TOIE    | INTE        | RBIE    | T0IF    | INTF   | RBIF   | 0000 000x               | 0000 000u                 |

| 0Ch     | PIR1   | _       | ADIF       | —       | _           | SSPIF   | CCP1IF  | TMR2IF | TMR1IF | -0 0000                 | -0 0000                   |

| 8Ch     | PIE1   | _       | ADIE       | —       | _           | SSPIE   | CCP1IE  | TMR2IE | TMR1IE | -0 0000                 | -0 0000                   |

| 1Eh     | ADRES  | A/D Res | ult Regist | er      |             |         |         |        |        | xxxx xxxx               | uuuu uuuu                 |

| 1Fh     | ADCON0 | ADCS1   | ADCS0      | CHS2    | CHS1        | CHS0    | GO/DONE | —      | ADON   | 0000 00-0               | 0000 00-0                 |

| 9Fh     | ADCON1 | _       | —          | —       | —           | —       | PCFG2   | PCFG1  | PCFG0  | 000                     | 000                       |

| 05h     | PORTA  | _       | _          | RA5     | RA4         | RA3     | RA2     | RA1    | RA0    | 0x 0000                 | 0u 0000                   |

| 85h     | TRISA  |         | —          | PORTA D | Data Direct | 11 1111 | 11 1111 |        |        |                         |                           |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D conversion.

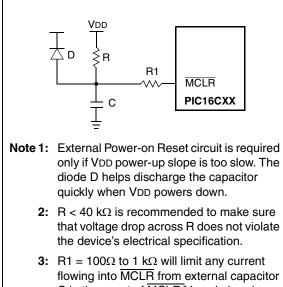

# 10.4 Power-On Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.5V - 2.1V). To take advantage of the POR, just tie the  $\overline{\text{MCLR}}$  pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified (SVDD, parameter D004). For a slow rise time, see Figure 10-6.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met. Brown-out Reset may be used to meet the start-up conditions.

## FIGURE 10-6: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

#### R1 = 100Ω to 1 kΩ will limit any current flowing into $\overline{MCLR}$ from external capacitor C in the event of $\overline{MCLR}/VPP$ pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

# 10.5 Power-up Timer (PWRT)

The Power-up Timer provides a fixed nominal time-out (TPWRT, parameter #33) from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip-to-chip due to VDD, temperature and process variation. See DC parameters for details.

# 10.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a delay of 1024 oscillator cycles (from OSC1 input) after the PWRT delay is over (TOST, parameter #32). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

Note: The OST delay may not occur when the device wakes from SLEEP.

# 10.7 Brown-Out Reset (BOR)

The configuration bit, BODEN, can enable or disable the Brown-Out Reset circuit. If VPP falls below Vbor (parameter #35, about  $100\mu$ S), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a reset may not occur.

Once the brown-out occurs, the device will remain in brown-out reset until VDD rises above VBOR. The power-up timer then keeps the device in reset for TPWRT (parameter #33, about 72mS). If VDD should fall below VBOR during TPWRT, the brown-out reset process will restart when VDD rises above VBOR with the power-up timer reset. The power-up timer is always enabled when the brown-out reset circuit is enabled, regardless of the state of the PWRT configuration bit.

#### 10.10.1 INT INTERRUPT

The external interrupt on RB0/INT pin is edge triggered: either rising, if bit INTEDG (OPTION\_REG<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 10.13 for details on SLEEP mode.

#### 10.10.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>). (Section 4.0)

#### 10.10.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>). (Section 3.2)

# 10.11 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt, (i.e., W register and STATUS register). This will have to be implemented in software.

Example 10-1 stores and restores the W and STATUS registers. The register, W\_TEMP, must be defined in each bank and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1).

The example:

- a) Stores the W register.

- b) Stores the STATUS register in bank 0.

- c) Stores the PCLATH register.

- d) Executes the interrupt service routine code (User-generated).

- e) Restores the STATUS register (and bank select bit).

- f) Restores the W and PCLATH registers.

#### EXAMPLE 10-1: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM

| MOVWF  | W_TEMP        | ;Copy W to TEMP register, could be bank one or zero     |

|--------|---------------|---------------------------------------------------------|

| SWAPF  | STATUS,W      | ;Swap status to be saved into W                         |

| CLRF   | STATUS        | ;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

| MOVWF  | STATUS_TEMP   | ;Save status to bank zero STATUS_TEMP register          |

| :      |               |                                                         |

| :(ISR) |               |                                                         |

| :      |               |                                                         |

| SWAPF  | STATUS_TEMP,W | ;Swap STATUS_TEMP register into W                       |

|        |               | ;(sets bank to original state)                          |

| MOVWF  | STATUS        | ;Move W into STATUS register                            |

| SWAPF  | W_TEMP,F      | ;Swap W_TEMP                                            |

| SWAPF  | W_TEMP,W      | ;Swap W_TEMP into W                                     |

|        |               |                                                         |

|                 |               |                                                                         | Standar     | d Opera | ating Co | ondition | s (unless otherwise stated)                                                                                  |

|-----------------|---------------|-------------------------------------------------------------------------|-------------|---------|----------|----------|--------------------------------------------------------------------------------------------------------------|

| DC CHA          | RACTE         | RISTICS                                                                 | Operatir    | ng temp | erature  |          | $\leq$ TA $\leq$ +70°C for commercial                                                                        |

|                 | 1             | 1                                                                       | 1           | 1       | 1        | -40°C    |                                                                                                              |

| Param<br>No.    | Sym           | Characteristic                                                          | Min         | Тур†    | Мах      | Units    | Conditions                                                                                                   |

| D001            | Vdd           | Supply Voltage                                                          | 2.5         | -       | 5.5      | V        | LP, XT, RC osc modes (DC - 4 MHz)                                                                            |

|                 |               |                                                                         | VBOR*       | -       | 5.5      | V        | BOR enabled (Note 7)                                                                                         |

| D002*           | Vdr           | RAM Data Retention<br>Voltage (Note 1)                                  | -           | 1.5     | -        | V        |                                                                                                              |

| D003            | VPOR          | <b>VDD Start Voltage</b> to<br>ensure internal<br>Power-on Reset signal | -           | Vss     | -        | V        | See section on Power-on Reset for details                                                                    |

| D004*<br>D004A* | SVDD          | <b>VDD Rise Rate</b> to<br>ensure internal<br>Power-on Reset signal     | 0.05<br>TBD | -<br>-  | -        | V/ms     | PWRT enabled (PWRTE bit clear)<br>PWRT disabled (PWRTE bit set)<br>See section on Power-on Reset for details |

| D005            | VBOR          | Brown-out Reset<br>voltage trip point                                   | 3.65        | -       | 4.35     | V        | BODEN bit set                                                                                                |

| D010            | IDD           | Supply Current<br>(Note 2, 5)                                           | -           | 2.0     | 3.8      | mA       | XT, RC osc modes<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                        |

| D010A           |               |                                                                         | -           | 22.5    | 48       | μA       | LP OSC MODE<br>FOSC = 32 kHz, VDD = 3.0V, WDT disabled                                                       |

| D020            | IPD           | Power-down Current                                                      | -           | 7.5     | 30       | μA       | VDD = 3.0V, WDT enabled, -40°C to +85°C                                                                      |

| D021            |               | (Note 3, 5)                                                             | -           | 0.9     | 5        | μA       | VDD = $3.0V$ , WDT disabled, $0^{\circ}C$ to $+70^{\circ}C$                                                  |

| D021A           |               |                                                                         | -           | 0.9     | 5        | μA       | VDD = 3.0V, WDT disabled, -40°C to +85°C                                                                     |

|                 |               | Module Differential<br>Current (Note 6)                                 |             |         |          |          |                                                                                                              |

| D022*           | $\Delta$ IWDT | Watchdog Timer                                                          | -           | 6.0     | 20       | μA       | WDTE BIT SET, VDD = 4.0V                                                                                     |

| D022A*          | $\Delta$ IBOR | Brown-out Reset                                                         | -           | TBD     | 200      | μA       | BODEN bit set, VDD = 5.0V                                                                                    |

#### 13.2 DC Characteristics: PIC16LC62B/72A-04 (Commercial, Industrial)

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD,

$\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- 4: For RC osc mode, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: This is the voltage where the device enters the Brown-out Reset. When BOR is enabled, the device will perform a brown-out reset when VDD falls below VBOR.

| DC CHA       | RISTICS | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |         |      |     |       |                                                                         |

|--------------|---------|------------------------------------------------------|---------|------|-----|-------|-------------------------------------------------------------------------|

| Param<br>No. | Sym     | Characteristic                                       | Min     | Тур† | Мах | Units | Conditions                                                              |

|              |         |                                                      | -       | -    | 0.6 | V     | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C                            |

| D083         |         | OSC2/CLKOUT<br>(RC osc mode)                         | -       | -    | 0.6 | V     | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                             |

|              |         |                                                      | -       | -    | 0.6 | V     | IOL = 1.2 mA, VDD = 4.5V,<br>-40°C to +125°C                            |

|              |         | Output High Voltage                                  |         |      |     |       |                                                                         |

| D090         | Vон     | I/O ports (Note 3)                                   | VDD-0.7 | -    | -   | V     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +85°C                            |

|              |         |                                                      | Vdd-0.7 | -    | -   | V     | IOH = -2.5 mA, VDD = 4.5V,<br>-40°С to +125°С                           |

| D092         |         | OSC2/CLKOUT (RC osc<br>mode)                         | VDD-0.7 | -    | -   | V     | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                            |

|              |         |                                                      | VDD-0.7 | -    | -   | V     | IOH = -1.0 mA, VDD = 4.5V,<br>-40°C to +125°C                           |

| D150*        | Vod     | Open-Drain High Voltage                              | -       | -    | 8.5 | V     | RA4 pin                                                                 |

|              |         | Capacitive Loading Specs<br>on Output Pins           |         |      |     |       |                                                                         |

| D100         | Cosc2   | OSC2 pin                                             | -       | -    | 15  | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1. |

| D101         | Сю      | All I/O pins and OSC2 (in RC mode)                   | -       | -    | 50  | pF    |                                                                         |

| D102         | Cb      | SCL, SDA in I <sup>2</sup> C mode                    | -       | -    | 400 | pF    |                                                                         |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the device be driven with external clock in RC mode.

2: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

# 14.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

The graphs and tables provided in this section are for **design guidance** and are **not tested**.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are guaranteed to operate properly only within the specified range.

The data presented in this section is a **statistical summary** of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution at 25°C. 'Max' or 'min' represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is standard deviation, over the whole temperature range.

# Graphs and Tables not available at this time.

Data is not available at this time but you may reference the *PIC16C72 Series Data Sheet* (DS39016,) DC and AC characteristic section, which contains data similar to what is expected.

# **15.0 PACKAGING INFORMATION**

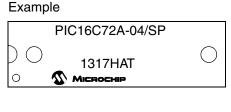

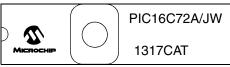

# 15.1 Package Marking Information

28-Lead SOIC

# Example

# Example PIC16C62B-20/SO

| 28-Lead SSOP                            | Example                |

|-----------------------------------------|------------------------|

| xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx | PIC16C62B<br>20I/SS025 |

|                                         | ○                      |

| ,                                                                                |                               |                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|----------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| be carried over to the next line thus limiting the number of available character | <br>XXX<br>AA<br>BB<br>C<br>D | <ul> <li>Customer specific information*</li> <li>Year code (last 2 digits of calendar year)</li> <li>Week code (week of January 1 is week '01')</li> <li>Facility code of the plant at which wafer is manufactured</li> <li>O = Outside Vendor</li> <li>C = 5" Line</li> <li>S = 6" Line</li> <li>H = 8" Line</li> <li>Mask revision number</li> <li>Assembly code of the plant or country of origin in which</li> </ul> |  |  |

|                                                                                  | be carrie                     | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line thus limiting the number of available characters<br>for customer specific information.                                                                                                                                                                                                             |  |  |

Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask rev#, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

© 1998-2013 Microchip Technology Inc.

# READER RESPONSE

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE: | Technical Publications Manager<br>Reader Response                                          | Total Pages Sent                |  |  |  |  |

|------------|--------------------------------------------------------------------------------------------|---------------------------------|--|--|--|--|

| Fror       | n: Name                                                                                    |                                 |  |  |  |  |

|            | Company                                                                                    |                                 |  |  |  |  |

|            | Address                                                                                    |                                 |  |  |  |  |

|            | City / State / ZIP / Country                                                               |                                 |  |  |  |  |

|            | Telephone: ()                                                                              | FAX: ()                         |  |  |  |  |

| Арр        | lication (optional):                                                                       |                                 |  |  |  |  |

| Wou        | Ild you like a reply?YN                                                                    |                                 |  |  |  |  |

| Dev        | ice: 24xx010                                                                               | Literature Number: DS35008C     |  |  |  |  |

| Que        | stions:                                                                                    |                                 |  |  |  |  |

| 1.         | What are the best features of this document?                                               |                                 |  |  |  |  |

|            |                                                                                            |                                 |  |  |  |  |

| 2.         | How does this document meet your hardware and softw                                        | are development needs?          |  |  |  |  |

|            |                                                                                            |                                 |  |  |  |  |

| 3.         | Do you find the organization of this document easy to fo                                   | llow? If not, why?              |  |  |  |  |

|            |                                                                                            |                                 |  |  |  |  |

|            |                                                                                            |                                 |  |  |  |  |

| 4.         | What additions to the document do you think would enh                                      | ance the structure and subject? |  |  |  |  |

|            |                                                                                            |                                 |  |  |  |  |

| 5.         | . What deletions from the document could be made without affecting the overall usefulness? |                                 |  |  |  |  |

|            |                                                                                            |                                 |  |  |  |  |

|            |                                                                                            |                                 |  |  |  |  |

| 6.         | Is there any incorrect or misleading information (what ar                                  | nd where)?                      |  |  |  |  |

|            |                                                                                            |                                 |  |  |  |  |

| 7.         | How would you improve this document?                                                       |                                 |  |  |  |  |

|            |                                                                                            |                                 |  |  |  |  |

|            |                                                                                            |                                 |  |  |  |  |