Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

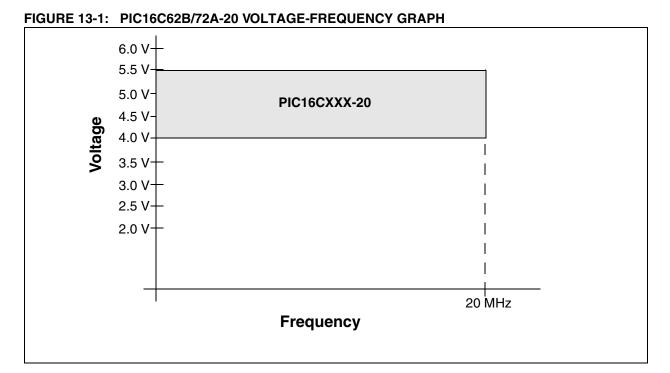

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c72at-04-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

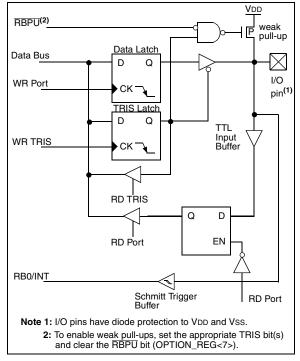

# 3.2 PORTB and the TRISB Register

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (=1) will make the corresponding PORTB pin an input, (i.e., put the corresponding output driver in a hi-impedance mode). Clearing a TRISB bit (=0) will make the corresponding PORTB pin an output, (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit  $\overline{\text{RBPU}}$  (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

#### FIGURE 3-3: BLOCK DIAGRAM OF RB3:RB0 PINS

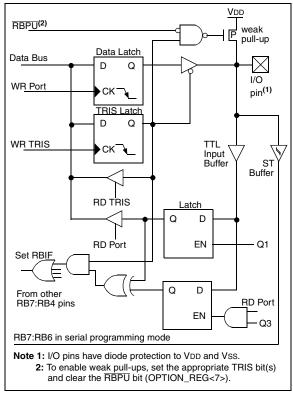

Four of PORTB's pins, RB7:RB4, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e. any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

RB0/INT is an external interupt pin and is configured using the INTEDG bit (OPTION\_REG<6>). RB0/INT is discussed in detail in Section 10.10.1.

| TABLE 3-3 | PORTB FUNCTIONS |

|-----------|-----------------|

| IADLE 3-3 | PURID FUNCTIONS |

| Name    | Bit# | Buffer                | Function                                                                                                               |

|---------|------|-----------------------|------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input.<br>Internal software programmable weak pull-up.                          |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB3     | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                         |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt on change).<br>Internal software programmable weak pull-up.                           |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt on change).<br>Internal software programmable weak pull-up.                           |

| RB6     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change).<br>Internal software programmable weak pull-up. Serial programming clock. |

| RB7     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change).<br>Internal software programmable weak pull-up. Serial programming data.  |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

#### TABLE 3-4 SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address | Name       | Bit 7   | Bit 6                        | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|------------|---------|------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 06h     | PORTB      | RB7     | RB6                          | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   | xxxx xxxx                | uuuu uuuu                 |

| 86h     | TRISB      | PORTB I | ORTB Data Direction Register |       |       |       |       |       |       |                          | 1111 1111                 |

| 81h     | OPTION_REG | RBPU    | INTEDG                       | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                 |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

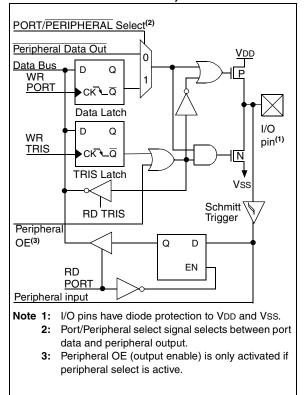

# 3.3 PORTC and the TRISC Register

PORTC is an 8-bit wide bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (=1) will make the corresponding PORTC pin an input, (i.e., put the corresponding output driver in a hi-impedance mode). Clearing a TRISC bit (=0) will make the corresponding PORTC pin an output, (i.e., put the contents of the output latch on the selected pin).

PORTC is multiplexed with several peripheral functions (Table 3-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override maybe in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

#### FIGURE 3-5: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

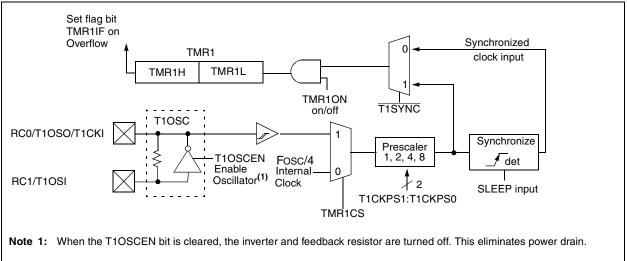

# FIGURE 5-1: TIMER1 BLOCK DIAGRAM

# 5.2 <u>Timer1 Oscillator</u>

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). When the Timer1 oscillator is enabled, RC0 and RC1 pins become T1OSO and T1OSI inputs, overriding TRISC<1:0>.

The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal. Table 5-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

| TABLE 5-1 | CAPACITOR SELECTION FOR |

|-----------|-------------------------|

|           | THE TIMER1 OSCILLATOR   |

| Osc Type                                                                                                                                                                                                                                                                                                   | Freq                            | C1            | C2            |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------|---------------|--|--|--|--|

| LP                                                                                                                                                                                                                                                                                                         | 32 kHz                          | 33 pF         | 23.0F         |  |  |  |  |

|                                                                                                                                                                                                                                                                                                            | 100 kHz                         | 15 pF         | ्रीई वृष्ट्रे |  |  |  |  |

|                                                                                                                                                                                                                                                                                                            | 200 kHz                         | 15 pF         | (15°pF        |  |  |  |  |

| These va                                                                                                                                                                                                                                                                                                   | alues are for (                 | design guidar | ce only.      |  |  |  |  |

| Crystals Tested:                                                                                                                                                                                                                                                                                           |                                 |               |               |  |  |  |  |

| 32.768 kHz                                                                                                                                                                                                                                                                                                 | Epson C-00(1R32.768K-A ± 20 PPM |               |               |  |  |  |  |

| 100 kHz                                                                                                                                                                                                                                                                                                    | Epson C-2 100.00 KC-P ± 20 PPM  |               |               |  |  |  |  |

| 200 kHz                                                                                                                                                                                                                                                                                                    | STD XTL 20                      | 0.000 kHz     | $\pm$ 20 PPM  |  |  |  |  |

| <ul> <li>Note 1: Higher capacitance increases the stability of oscillator but also increases the start-up time.</li> <li>2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.</li> </ul> |                                 |               |               |  |  |  |  |

# 5.3 <u>Timer1 Interrupt</u>

The TMR1 Register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow and is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled by setting TMR1 interrupt enable bit TMR1IE (PIE1<0>).

### 5.4 <u>Resetting Timer1 using a CCP Trigger</u> <u>Output</u>

If the CCP module is configured in compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

| Note: | The special event trigger from the CCP1 |

|-------|-----------------------------------------|

|       | module will not set interrupt flag bit  |

|       | TMR1IF (PIR1<0>).                       |

Timer1 must be configured for either timer or synchronized counter mode to take advantage of this feature. If Timer1 is running in asynchronous counter mode, this reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPR1H:CCPR1L registers pair effectively becomes the period register for Timer1.

# TABLE 5-2 REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address | Name   | Bit 7                                                                       | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|--------|-----------------------------------------------------------------------------|-------|---------|---------|---------|--------|--------|--------|-------------------------|---------------------------------|

| 0Bh,8Bh | INTCON | GIE                                                                         | PEIE  | TOIE    | INTE    | RBIE    | TOIF   | INTF   | RBIF   | 0000 000x               | 0000 000u                       |

| 0Ch     | PIR1   |                                                                             | ADIF  |         | -       | SSPIF   | CCP1IF | TMR2IF | TMR1IF | -0 0000                 | -0 0000                         |

| 8Ch     | PIE1   | _                                                                           | ADIE  | -       | -       | SSPIE   | CCP1IE | TMR2IE | TMR1IE | -0 0000                 | -0 0000                         |

| 0Eh     | TMR1L  | Holding register for the Least Significant Byte of the 16-bit TMR1 register |       |         |         |         |        |        |        |                         | uuuu uuuu                       |

| 0Fh     | TMR1H  | Holding register for the Most Significant Byte of the 16-bit TMR1 register  |       |         |         |         |        |        |        | xxxx xxxx               | uuuu uuuu                       |

| 10h     | T1CON  | -                                                                           | _     | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR1ON | 00 0000                 | uu uuuu                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer1 module.

NOTES:

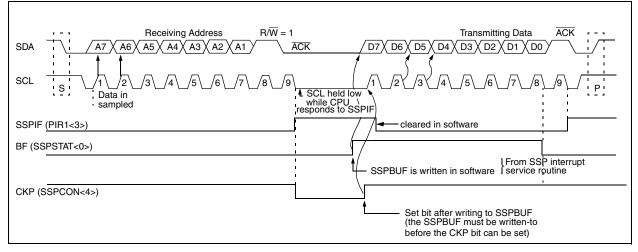

#### 8.3.1.3 TRANSMISSION

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and the CKP will be cleared by hardware, holding SCL low. Slave devices cause the master to wait by holding the SCL line low. The transmit data is loaded into the SSPBUF register, which in turn loads the SSPSR register. When bit CKP (SSP-CON<4>) is set, pin RC3/SCK/SCL releases SCL. When the SCL line goes high, the master may resume operating the SCL line and receiving data. The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 8-4).

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software, and the SSPSTAT register used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the masterreceiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not  $\overline{ACK}$ ), then the data transfer is complete. When the  $\overline{ACK}$  is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave then monitors for another occurrence of the START bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP.

FIGURE 8-4: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

#### 8.3.2 MASTER OPERATION

Master operation is supported in firmware using interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared by a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is idle and both the S and P bits are clear.

In master operation, the SCL and SDA lines are manipulated in software by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt if enabled):

- START condition

- STOP condition

- Byte transfer completed

Master operation can be done with either the slave mode idle (SSPM3:SSPM0 = 1011) or with the slave active. When both master operation and slave modes are used, the software needs to differentiate the source(s) of the interrupt.

For more information on master operation, see AN554 - Software Implementation of  $I^2C$  Bus Master.

### 8.3.3 MULTI-MASTER OPERATION

In multi-master operation, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle and both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In multi-master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost, these are:

- Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed, an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to re-transfer the data at a later time.

For more information on master operation, see AN578 - Use of the SSP Module in the of  $l^2C$  Multi-Master Environment.

| Address  | Name    | Bit 7                         | Bit 6              | Bit 5                    | Bit 4     | Bit 3     | Bit 2    | Bit 1  | Bit 0  | PC   | e on<br>DR,<br>DR | all o | e on<br>ther<br>ets |

|----------|---------|-------------------------------|--------------------|--------------------------|-----------|-----------|----------|--------|--------|------|-------------------|-------|---------------------|

| 0Bh, 8Bh | INTCON  | GIE                           | PEIE               | TOIE                     | INTE      | RBIE      | T0IF     | INTF   | RBIF   | 0000 | 000x              | 0000  | 000u                |

| 0Ch      | PIR1    | _                             | ADIF               | _                        |           | SSPIF     | CCP1IF   | TMR2IF | TMR1IF | - 0  | 0000              | - 0   | 0000                |

| 8Ch      | PIE1    | _                             | ADIE               | _                        | —         | SSPIE     | CCP1IE   | TMR2IE | TMR1IE | - 0  | 0000              | - 0   | 0000                |

| 13h      | SSPBUF  | Synchronou                    | is Serial F        | Port Recei               | ve Buffer | /Transmit | Register | •      | •      | xxxx | xxxx              | uuuu  | uuuu                |

| 93h      | SSPADD  | Synchronou                    | is Serial F        | Port (I <sup>2</sup> C n | node) Ad  | dress Reg | jister   |        |        | 0000 | 0000              | 0000  | 0000                |

| 14h      | SSPCON  | WCOL                          | SSPOV              | SSPEN                    | CKP       | SSPM3     | SSPM2    | SSPM1  | SSPM0  | 0000 | 0000              | 0000  | 0000                |

| 94h      | SSPSTAT | SMP <sup>(1)</sup>            | CKE <sup>(1)</sup> | D/A                      | Р         | S         | R/W      | UA     | BF     | 0000 | 0000              | 0000  | 0000                |

| 87h      | TRISC   | PORTC Data Direction register |                    |                          |           |           |          |        |        | 1111 | 1111              | 1111  | 1111                |

# TABLE 8-3REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in SPI mode.

**Note 1:** Maintain these bits clear in  $I^2C$  mode.

NOTES:

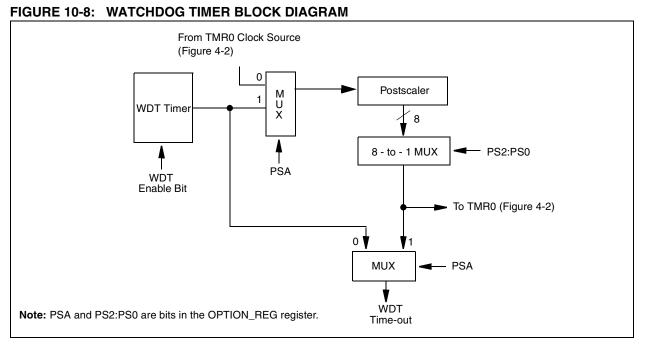

# 10.12 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. The WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit WDTE (Section 10.1).

The WDT time-out period (TWDT, parameter #31) is multiplied by the prescaler ratio, when the prescaler is assigned to the WDT. The prescaler assignment (assigned to either the WDT or Timer0) and prescaler ratio are set in the OPTION\_REG register.

Note: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

**Note:** When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

# FIGURE 10-9: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name         | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|--------------|-------|--------|-------|-------|-------|-------|-------|-------|

| 2007h   | Config. bits |       | BODEN  | CP1   | CP0   | PWRTE | WDTE  | FOSC1 | FOSC0 |

| 81h     | OPTION_REG   | RBPU  | INTEDG | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

# FIGURE 10-10: WAKE-UP FROM SLEEP THROUGH INTERRUPT

| ; a1   a2   a3   a4 ; (<br>osc1 /~//        | 21   Q2   Q3   Q4 ;<br>\/ |                       | 01 02 03 04  | a1 a2 a3 a4                   | a1 a2 a3 a4      | 01 02 03 04 |

|---------------------------------------------|---------------------------|-----------------------|--------------|-------------------------------|------------------|-------------|

| CLKOUT(4)                                   |                           | Tost(2)               | /            | /                             | //               |             |

| INTF flag<br>(INTCON<1>)                    |                           |                       |              | Interrupt Latency<br>(Note 2) | -<br> <br> <br>  |             |

| GIE bit<br>(INTCON<7>)                      | <br> <br> +<br> <br>      | Processor in<br>SLEEP |              |                               | 1<br>1<br>1<br>1 |             |

| INSTRUCTION FLOW                            | 1                         |                       |              |                               |                  | · · · ·     |

| PC <u>X PC X</u>                            | PC+1                      | PC+2                  | PC+2         | X PC + 2                      | X 0004h          | X 0005h     |

| Instruction {<br>fetched { Inst(PC) = SLEEP | Inst(PC + 1)              | ,<br>,<br>,           | Inst(PC + 2) |                               | Inst(0004h)      | Inst(0005h) |

| Instruction<br>executed Inst(PC - 1)        | SLEEP                     | 1<br>1<br>1           | Inst(PC + 1) | Dummy cycle                   | Dummy cycle      | Inst(0004h) |

**Note 1:** XT, HS or LP oscillator mode assumed.

**2:** TOST = 1024TOSC (drawing not to scale) This delay will not be there for RC osc mode.

3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

#### 10.14 Program Verification/Code Protection

If the code protection bits have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip does not recommend code pro- |

|-------|----------------------------------------|

|       | tecting windowed devices.              |

#### 10.15 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution, but are readable and writable during program/verify. It is recommended that only the 4 least significant bits of the ID location are used.

For ROM devices, these values are submitted along with the ROM code.

#### 10.16 In-Circuit Serial Programming™

PIC16CXXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three more lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

For complete details of serial programming, please refer to the In-Circuit Serial Programming (ICSP™) Guide, DS30277.

# 11.1 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                       |

|------------------|-------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                |

| Operands:        | $0 \leq k \leq 255$                                                                                                     |

| Operation:       | $(W) + k \to (W)$                                                                                                       |

| Status Affected: | C, DC, Z                                                                                                                |

| Description:     | The contents of the W register are<br>added to the eight bit literal 'k' and the<br>result is placed in the W register. |

| ANDWF            | AND W with f                                                                                                                                                |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                             |  |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                   |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |  |  |  |  |

| Description:     | AND the W register with register 'f'. If<br>'d' is 0, the result is stored in the W<br>register. If 'd' is 1, the result is stored<br>back in register 'f'. |  |  |  |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                           |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                       |

| Status Affected: | C, DC, Z                                                                                                                                                                    |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result is<br>stored in the W register. If 'd' is 1, the<br>result is stored back in register 'f'. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BCF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ANDLW            | AND Literal with W                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                            |

| Operands:        | $0 \le k \le 255$                                                                                                   |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                     |

| Status Affected: | Z                                                                                                                   |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal 'k'.<br>The result is placed in the W register. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

# PIC16C62B/72A

and test the sample code. In addition, PICDEM-17 supports down-loading of programs to and executing out of external FLASH memory on board. The PICDEM-17 is also usable with the MPLAB-ICE or PICMASTER emulator, and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

# 12.17 <u>SEEVAL Evaluation and Programming</u> <u>System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in tradeoff analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

# 12.18 <u>KEELOQ Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

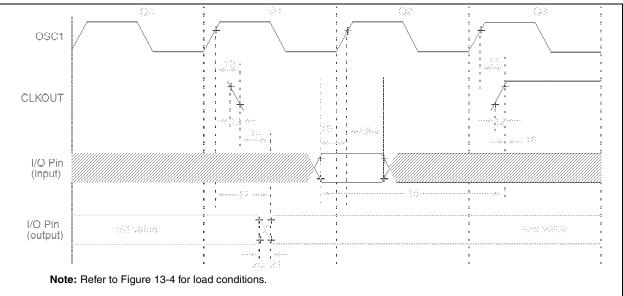

| Param<br>No. | Sym      | Characteristic                          | Min                | Тур† | Мах | Units       | Conditions |        |

|--------------|----------|-----------------------------------------|--------------------|------|-----|-------------|------------|--------|

| 10*          | TosH2ckL | OSC1↑ to CLKOUT↓                        |                    | —    | 75  | 200         | ns         | Note 1 |

| 11*          | TosH2ckH | OSC1↑ to CLKOUT↑                        |                    | —    | 75  | 200         | ns         | Note 1 |

| 12*          | TckR     | CLKOUT rise time                        |                    | _    | 35  | 100         | ns         | Note 1 |

| 13*          | TckF     | CLKOUT fall time                        |                    | _    | 35  | 100         | ns         | Note 1 |

| 14*          | TckL2ioV | CLKOUT ↓ to Port out valid              |                    | —    |     | 0.5TCY + 20 | ns         | Note 1 |

| 15*          | TioV2ckH | Port in valid before CLKOU              | Tosc + 200         |      | _   | ns          | Note 1     |        |

| 16*          | TckH2iol | Port in hold after CLKOUT               | 0                  |      | _   | ns          | Note 1     |        |

| 17*          | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to Port of | —                  | 50   | 150 | ns          |            |        |

| 18*          | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to Port    | PIC16CXX           | 100  |     | _           | ns         |        |

| 18A*         |          | input invalid (I/O in hold<br>time)     | PIC16LCXX          | 200  |     |             | ns         |        |

| 19*          | TioV2osH | Port input valid to OSC1 <sup>↑</sup> ( | I/O in setup time) | 0    | _   | —           | ns         |        |

| 20*          | TioR     | Port output rise time                   | PIC16CXX           | —    | 10  | 40          | ns         |        |

| 20A*         |          |                                         | PIC16LCXX          | _    |     | 80          | ns         |        |

| 21*          | TioF     | Port output fall time                   | PIC16CXX           | _    | 10  | 40          | ns         |        |

| 21A*         | 1        |                                         | PIC16LCXX          | —    | —   | 80          | ns         |        |

| 22††*        | Tinp     | INT pin high or low time                |                    | Тсү  | _   | —           | ns         |        |

| 23††*        | Trbp     | RB7:RB4 change INT high                 | or low time        | Тсү  | _   |             | ns         |        |

| TABLE 13-3: | CLKOUT AND I/O TIMING REQUIREMENTS |

|-------------|------------------------------------|

|             |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

tt These parameters are asynchronous events not related to any internal clock edge.

**Note 1:** Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

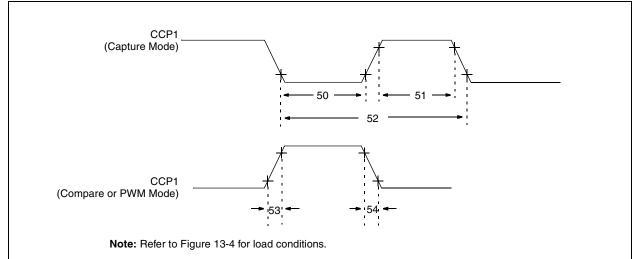

# FIGURE 13-10: CAPTURE/COMPARE/PWM TIMINGS

#### TABLE 13-6: CAPTURE/COMPARE/PWM REQUIREMENTS

| Param<br>No. | Sym                                  |                   | Characteristi   | Min          | Тур†                  | Max | Units | Conditions |                                    |

|--------------|--------------------------------------|-------------------|-----------------|--------------|-----------------------|-----|-------|------------|------------------------------------|

| 50*          | TccL                                 | CCP1 input low    | No Prescaler    | No Prescaler |                       | —   | —     | ns         |                                    |

|              | time                                 | With Prescaler    | PIC16CXX        | 10           | _                     | _   | ns    |            |                                    |

|              |                                      |                   |                 | PIC16LCXX    | 20                    | _   | _     | ns         |                                    |

| 51*          | 1* TccH CCP1 input high No Prescaler |                   |                 | 0.5TCY + 20  | _                     | _   | ns    |            |                                    |

| time         | With Prescaler                       | PIC16CXX          | 10              | -            | —                     | ns  |       |            |                                    |

|              |                                      |                   |                 | PIC16LCXX    | 20                    | _   | _     | ns         |                                    |

| 52*          | TccP                                 | CCP1 input perior | P1 input period |              | <u>3Tcy + 40</u><br>N | -   | —     | ns         | N = prescale<br>value (1,4, or 16) |

| 53*          | TccR                                 | CCP1 output rise  | time            | PIC16CXX     | —                     | 10  | 25    | ns         |                                    |

|              |                                      |                   | PIC16LCXX       | —            | 25                    | 45  | ns    |            |                                    |

| 54*          | 54* TccF CCP1 output fall time       |                   | PIC16CXX        | —            | 10                    | 25  | ns    |            |                                    |

|              |                                      |                   |                 | PIC16LCXX    | —                     | 25  | 45    | ns         |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC16C62B/72A

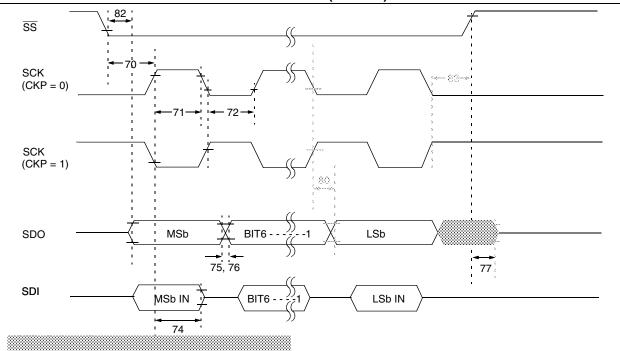

# FIGURE 13-14: EXAMPLE SPI SLAVE MODE TIMING (CKE = 1)

### TABLE 13-10: EXAMPLE SPI SLAVE MODE REQUIREMENTS (CKE = 1)

| Param.<br>No. | Symbol                    | Characteris                                                        | Min         | Тур†         | Мах | Units | Conditions |        |

|---------------|---------------------------|--------------------------------------------------------------------|-------------|--------------|-----|-------|------------|--------|

| 70            | TssL2scH,<br>TssL2scL     | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ in | Тсү         | —            |     | ns    |            |        |

| 71            | TscH                      | SCK input high time                                                | Continuous  | 1.25Tcy + 30 | —   | _     | ns         |        |

| 71A           |                           | (slave mode)                                                       | Single Byte | 40           | —   | _     | ns         | Note 1 |

| 72            | TscL                      | SCK input low time                                                 | Continuous  | 1.25Tcy + 30 | —   | _     | ns         |        |

| 72A           |                           | (slave mode)                                                       | Single Byte | 40           | —   |       | ns         | Note 1 |

| 73A           | Тв2в                      | Last clock edge of Byte1<br>edge of Byte2                          | 1.5Tcy + 40 | —            | _   | ns    | Note 1     |        |

| 74            | TscH2diL,<br>TscL2diL     | Hold time of SDI data input to SCK edge                            |             | 100          | —   | —     | ns         |        |

| 75            | TdoR SDO data output rise |                                                                    | PIC16CXX    | —            | 10  | 25    | ns         |        |

|               |                           | time                                                               | PIC16LCXX   |              | 20  | 45    | ns         |        |

| 76            | TdoF                      | SDO data output fall time                                          | Э           |              | 10  | 25    | ns         |        |

| 77            | TssH2doZ                  | SS <sup>↑</sup> to SDO output hi-im                                | pedance     | 10           | —   | 50    | ns         |        |

| 78            | TscR                      | SCK output rise time                                               | PIC16CXX    |              | 10  | 25    | ns         |        |

|               |                           | (master mode)                                                      | PIC16LCXX   |              | 20  | 45    | ns         |        |

| 79            | TscF                      | SCK output fall time (ma                                           | ster mode)  |              | 10  | 25    | ns         |        |

| 80            | TscH2doV,                 | SDO data output valid                                              | PIC16CXX    |              | —   | 50    | ns         |        |

|               | TscL2doV                  | after SCK edge                                                     | PIC16LCXX   |              | —   | 100   | ns         |        |

| 82            | TssL2doV                  | SDO data output valid                                              | PIC16CXX    |              | —   | 50    | ns         |        |

|               |                           | after SS↓ edge                                                     | PIC16LCXX   |              | —   | 100   | ns         |        |

| 83            | TscH2ssH,<br>TscL2ssH     | SS ↑ after SCK edge                                                |             | 1.5TCY + 40  | —   | —     | ns         |        |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Specification 73A is only required if specifications 71A and 72A are used.

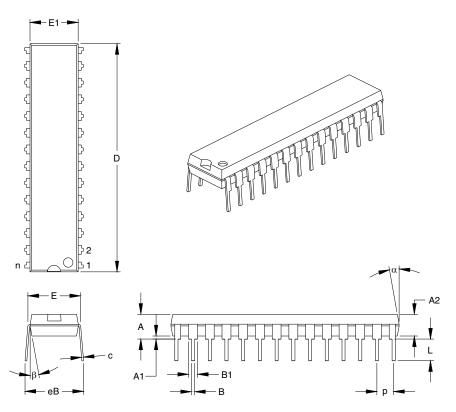

#### 28-Lead Skinny Plastic Dual In-line (SP) – 300 mil (PDIP) 15.2

|                            |        | INCHES* |       | MILLIMETERS |       |       |       |

|----------------------------|--------|---------|-------|-------------|-------|-------|-------|

| Dimension                  | Limits | MIN     | NOM   | MAX         | MIN   | NOM   | MAX   |

| Number of Pins             | n      |         | 28    |             |       | 28    |       |

| Pitch                      | р      |         | .100  |             |       | 2.54  |       |

| Top to Seating Plane       | Α      | .140    | .150  | .160        | 3.56  | 3.81  | 4.06  |

| Molded Package Thickness   | A2     | .125    | .130  | .135        | 3.18  | 3.30  | 3.43  |

| Base to Seating Plane      | A1     | .015    |       |             | 0.38  |       |       |

| Shoulder to Shoulder Width | E      | .300    | .313  | .325        | 7.62  | 7.94  | 8.26  |

| Molded Package Width       | E1     | .279    | .307  | .335        | 7.09  | 7.80  | 8.51  |

| Overall Length             | D      | 1.345   | 1.365 | 1.385       | 34.16 | 34.67 | 35.18 |

| Tip to Seating Plane       | L      | .125    | .130  | .135        | 3.18  | 3.30  | 3.43  |

| Lead Thickness             | С      | .008    | .012  | .015        | 0.20  | 0.29  | 0.38  |

| Upper Lead Width           | B1     | .040    | .053  | .065        | 1.02  | 1.33  | 1.65  |

| Lower Lead Width           | В      | .016    | .019  | .022        | 0.41  | 0.48  | 0.56  |

| Overall Row Spacing        | eB     | .320    | .350  | .430        | 8.13  | 8.89  | 10.92 |

| Mold Draft Angle Top       | α      | 5       | 10    | 15          | 5     | 10    | 15    |

| Mold Draft Angle Bottom    | β      | 5       | 10    | 15          | 5     | 10    | 15    |

\*Controlling Parameter

Notes: Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-095 Drawing No. C04-070

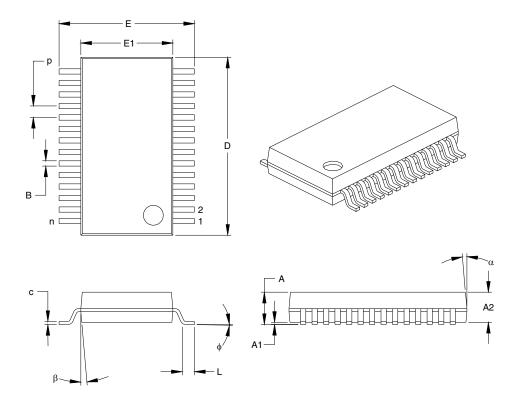

#### 28-Lead Plastic Shrink Small Outline (SS) - 209 mil, 5.30 mm (SSOP) 15.5

| Units    |                                                                                                                             |                                                                                                                                                                                                                                                                                               | INCHES                                                 |                                                        |                                                        | MILLIMETERS*                                           |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--|--|--|

| n Limits | MIN                                                                                                                         | NOM                                                                                                                                                                                                                                                                                           | MAX                                                    | MIN                                                    | NOM                                                    | MAX                                                    |  |  |  |

| n        |                                                                                                                             | 28                                                                                                                                                                                                                                                                                            |                                                        |                                                        | 28                                                     |                                                        |  |  |  |

| р        |                                                                                                                             | .026                                                                                                                                                                                                                                                                                          |                                                        |                                                        | 0.66                                                   |                                                        |  |  |  |

| Α        | .068                                                                                                                        | .073                                                                                                                                                                                                                                                                                          | .078                                                   | 1.73                                                   | 1.85                                                   | 1.98                                                   |  |  |  |

| A2       | .064                                                                                                                        | .068                                                                                                                                                                                                                                                                                          | .072                                                   | 1.63                                                   | 1.73                                                   | 1.83                                                   |  |  |  |

| A1       | .002                                                                                                                        | .006                                                                                                                                                                                                                                                                                          | .010                                                   | 0.05                                                   | 0.15                                                   | 0.25                                                   |  |  |  |

| E        | .299                                                                                                                        | .309                                                                                                                                                                                                                                                                                          | .319                                                   | 7.59                                                   | 7.85                                                   | 8.10                                                   |  |  |  |

| E1       | .201                                                                                                                        | .207                                                                                                                                                                                                                                                                                          | .212                                                   | 5.11                                                   | 5.25                                                   | 5.38                                                   |  |  |  |

| D        | .396                                                                                                                        | .402                                                                                                                                                                                                                                                                                          | .407                                                   | 10.06                                                  | 10.20                                                  | 10.34                                                  |  |  |  |

| L        | .022                                                                                                                        | .030                                                                                                                                                                                                                                                                                          | .037                                                   | 0.56                                                   | 0.75                                                   | 0.94                                                   |  |  |  |

| С        | .004                                                                                                                        | .007                                                                                                                                                                                                                                                                                          | .010                                                   | 0.10                                                   | 0.18                                                   | 0.25                                                   |  |  |  |

| ¢        | 0                                                                                                                           | 4                                                                                                                                                                                                                                                                                             | 8                                                      | 0.00                                                   | 101.60                                                 | 203.20                                                 |  |  |  |

| В        | .010                                                                                                                        | .013                                                                                                                                                                                                                                                                                          | .015                                                   | 0.25                                                   | 0.32                                                   | 0.38                                                   |  |  |  |

| α        | 0                                                                                                                           | 5                                                                                                                                                                                                                                                                                             | 10                                                     | 0                                                      | 5                                                      | 10                                                     |  |  |  |

| β        | 0                                                                                                                           | 5                                                                                                                                                                                                                                                                                             | 10                                                     | 0                                                      | 5                                                      | 10                                                     |  |  |  |

|          | p           A           A2           A1           E           D           L           c           φ           B           α | n           p           A         .068           A2         .064           A1         .002           E         .299           E1         .201           D         .396           L         .022           c         .004           φ         0           B         .010           α         0 | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |  |  |  |

\*Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-150

Drawing No. C04-073

| Instruction Set |                                   | 67     |

|-----------------|-----------------------------------|--------|

| ADDLW .         |                                   | 69     |

|                 |                                   |        |

|                 |                                   |        |

|                 |                                   |        |

|                 |                                   |        |

|                 |                                   |        |

|                 |                                   |        |

|                 |                                   |        |

|                 |                                   |        |

| -               |                                   |        |

| -               | ·                                 |        |

|                 |                                   |        |

|                 |                                   |        |

| -               |                                   |        |

|                 |                                   |        |

|                 |                                   |        |

| INCFSZ          |                                   | 71     |

| IORLW           |                                   | 72     |

| IORWF           |                                   | 72     |

| MOVF            |                                   | 72     |

|                 |                                   |        |

| -               |                                   |        |

|                 |                                   |        |

|                 |                                   | -      |

|                 |                                   |        |

|                 |                                   |        |

|                 |                                   | -      |

|                 |                                   | -      |

|                 |                                   |        |

|                 |                                   |        |

|                 |                                   |        |

|                 |                                   |        |

| -               |                                   |        |

| -               | , Table                           |        |

|                 | ster                              |        |

| 0               |                                   |        |

|                 |                                   | -      |

|                 |                                   |        |

|                 |                                   | -      |

| RBIE Bit        |                                   | 13     |

| RBIF Bit        |                                   | 13, 21 |

| T0IE Bit        |                                   | 13     |

| T0IF Bit        |                                   | 13     |

|                 | ces                               |        |

|                 | version Complete                  |        |

|                 | gram                              |        |

|                 | Complete (CCP)                    |        |

|                 | Complete (CCP)                    |        |

| Interrupt of    | on Change (RB7:RB4)               | 21     |

|                 | Pin, External                     |        |

|                 | eive/Transmit Complete<br>/erflow |        |

|                 | reflow                            |        |

|                 | PR2 Match                         |        |

|                 | PR2 Match (PWM)                   |        |

|                 | ntext Saving During               |        |

| Interrupts, Ena |                                   |        |

|                 | verter Enable (ADIE Bit)          | 14     |

|                 | able (CCP1IE Bit)                 |        |

| Global Int      | terrupt Enable (GIE Bit)          | 13, 62 |

|                 | on Change (RB7:RB4)               | ,      |

| Enable (F       | RBIE Bit)                         |        |

|                 | al Interrupt Enable (PEIE Bit)    |        |

| RB0/INT Enable (INTE Bit)13<br>SSP Enable (SSPIE Bit)14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSP Enable (SSPIE Bit)14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TMR0 Overflow Enable (T0IE Bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TMR1 Overflow Enable (TMR1IE Bit)14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TMR2 to PR2 Match Enable (TMR2IE Bit) 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Interrupts, Flag Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A/D Converter Flag (ADIF Bit)15, 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CCP1 Flag (CCP1IF Bit)15, 34, 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Interrupt on Change (RB7:RB4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |