Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                   |

| Data Converters            | A/D 5x8b                                                                    |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c72at-20i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

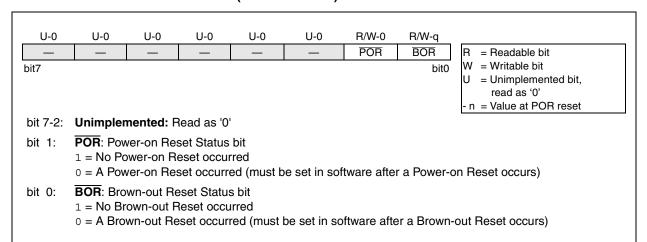

#### 2.2.2.6 PCON REGISTER

The Power Control register (PCON) contains flag bits to allow differentiation between a Power-on Reset (POR), Brown-Out Reset (BOR) and resets from other sources. .

Note: On Power-on Reset, the state of the BOR bit is unknown and is not predictable.

If the BODEN bit in the configuration word is set, the user must first set the BOR bit on a POR, and check it on subsequent resets.

If BOR is cleared while POR remains set, a Brown-out reset has occurred.

If the BODEN bit is clear, the BOR bit may be ignored.

#### REGISTER 2-6: PCON REGISTER (ADDRESS 8Eh)

TABLE 3-3 PORTB FUNCTIONS

| Name    | Bit# | Buffer                | Function                                                                                                            |

|---------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                          |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB3     | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB6     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming clock. |

| RB7     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming data.  |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

#### TABLE 3-4 SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address | Name       | Bit 7   | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |  |

|---------|------------|---------|-------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------|--|

| 06h     | PORTB      | RB7     | RB6                           | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   | xxxx xxxx                | uuuu uuuu                 |  |

| 86h     | TRISB      | PORTB I | PORTB Data Direction Register |       |       |       |       |       |       | 1111 1111                | 1111 1111                 |  |

| 81h     | OPTION_REG | RBPU    | INTEDG                        | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                 |  |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

#### REGISTER 8-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94h)

| R/W-0 | R/W-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |

|-------|-------|-----|-----|-----|-----|-----|-----|

| SMP   | CKE   | D/Ā | Р   | S   | R/W | UA  | BF  |

bit7

bit0

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as '0'

- n =Value at POR reset

bit 7: SMP: SPI data input sample phase

**SPI Master Operation**

- 1 = Input data sampled at end of data output time

- 0 = Input data sampled at middle of data output time

**SPI Slave Mode**

SMP must be cleared when SPI is used in slave mode

<u>I<sup>2</sup>C Mode</u>

This bit must be maintained clear

bit 6: CKE: SPI Clock Edge Select

SPI Mode

CKP = 0

- 1 = Data transmitted on rising edge of SCK

- 0 = Data transmitted on falling edge of SCK

CKP = 1

- 1 = Data transmitted on falling edge of SCK

- 0 = Data transmitted on rising edge of SCK

I<sup>2</sup>C Mode

This bit must be maintained clear

- bit 5: **D/A**: Data/Address bit (I<sup>2</sup>C mode only)

- 1 = Indicates that the last byte received or transmitted was data

- 0 = Indicates that the last byte received or transmitted was address

- bit 4: **P**: Stop bit (I<sup>2</sup>C mode only. This bit is cleared when the SSP module is disabled, or when the Start bit is detected last, SSPEN is cleared)

- 1 = Indicates that a stop bit has been detected last (this bit is '0' on RESET)

- 0 = Stop bit was not detected last

- bit 3: **S**: Start bit (I<sup>2</sup>C mode only. This bit is cleared when the SSP module is disabled, or when the Stop bit is detected last, SSPEN is cleared)

- 1 = Indicates that a start bit has been detected last (this bit is '0' on RESET)

- 0 = Start bit was not detected last

- bit 2:  $\mathbf{R}/\overline{\mathbf{W}}$ : Read/Write bit information (I<sup>2</sup>C mode only)

This bit holds the R/W bit information following the last address match. This bit is only valid from the address match to the next start bit, stop bit, or  $\overline{ACK}$  bit.

- 1 = Read

- 0 = Write

- bit 1: **UA**: Update Address (10-bit I<sup>2</sup>C mode only)

- 1 = Indicates that the user needs to update the address in the SSPADD register

- 0 = Address does not need to be updated

- bit 0: BF: Buffer Full Status bit

Receive (SPI and I<sup>2</sup>C modes)

- 1 = Receive complete, SSPBUF is full

- 0 = Receive not complete, SSPBUF is empty

Transmit (I<sup>2</sup>C mode only)

- 1 = Transmit in progress, SSPBUF is full

- 0 = Transmit complete, SSPBUF is empty

**NOTES:**

#### 10.8 <u>Time-out Sequence</u>

When a POR reset occurs, the PWRT delay starts (if enabled). When PWRT ends, the OST counts 1024 oscillator cycles (LP, XT, HS modes only). When OST completes, the device comes out of reset. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all.

If  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Bringing  $\overline{\text{MCLR}}$  high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16CXXX device operating in parallel.

Table 10-5 shows the reset conditions for the STATUS, PCON and PC registers, while Table 10-6 shows the reset conditions for all the registers.

#### 10.9 <u>Power Control/Status Register</u> (PCON)

The BOR bit is unknown on Power-on Reset. If the Brown-out Reset circuit is used, the BOR bit must be set by the user and checked on subsequent resets to see if it was cleared, indicating a Brown-out has occurred.

POR (Power-on Reset Status bit) is cleared on a Power-on Reset and unaffected otherwise. The user

#### **Status Register**

| IRP RP1 RP0 TO PD Z DC C |

|--------------------------|

|--------------------------|

#### **PCON Register**

#### TABLE 10-3 TIME-OUT IN VARIOUS SITUATIONS

| Ossillator Configuration | Power-           | -up       | Brown out        | Wake-up from |  |

|--------------------------|------------------|-----------|------------------|--------------|--|

| Oscillator Configuration | PWRTE = 0        | PWRTE = 1 | Brown-out        | SLEEP        |  |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024Tosc     |  |

| RC                       | 72 ms            | _         | 72 ms            | _            |  |

#### TABLE 10-4 STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | TO | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset                                          |

| 0   | x   | 0  | х  | Illegal, TO is set on POR                               |

| 0   | х   | х  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

#### TABLE 10-5 RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 1uuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 1uuu          | u0               |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

TABLE 10-6 INITIALIZATION CONDITIONS FOR ALL REGISTERS

| Register             | Appli<br>Dev | cable<br>ices | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

|----------------------|--------------|---------------|------------------------------------|--------------------------|---------------------------------|

| W                    | 62B          | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| INDF                 | 62B          | 72A           | N/A                                | N/A                      | N/A                             |

| TMR0                 | 62B          | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PCL                  | 62B          | 72A           | 0000h                              | 0000h                    | PC + 1 <b>(2)</b>               |

| STATUS               | 62B          | 72A           | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu(3)                    |

| FSR                  | 62B          | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PORTA <sup>(4)</sup> | 62B          | 72A           | 0x 0000                            | 0u 0000                  | uu uuuu                         |

| PORTB <sup>(5)</sup> | 62B          | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PORTC <sup>(5)</sup> | 62B          | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PCLATH               | 62B          | 72A           | 0 0000                             | 0 0000                   | u uuuu                          |

| INTCON               | 62B          | 72A           | 0000 000x                          | 0000 000u                | uuuu uuuu(1)                    |

| DID4                 | 62B          | 72A           | 0000                               | 0000                     | uuuu(1)                         |

| PIR1                 | 62B          | 72A           | -0 0000                            | -0 0000                  | -u uuuu(1)                      |

| TMR1L                | 62B          | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| TMR1H                | 62B          | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| T1CON                | 62B          | 72A           | 00 0000                            | uu uuuu                  | uu uuuu                         |

| TMR2                 | 62B          | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| T2CON                | 62B          | 72A           | -000 0000                          | -000 0000                | -uuu uuuu                       |

| SSPBUF               | 62B          | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| SSPCON               | 62B          | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| CCPR1L               | 62B          | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| CCPR1H               | 62B          | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| CCP1CON              | 62B          | 72A           | 00 0000                            | 00 0000                  | uu uuuu                         |

| ADRES                | 62B          | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| ADCON0               | 62B          | 72A           | 0000 00-0                          | 0000 00-0                | uuuu uu-u                       |

| OPTION_REG           | 62B          | 72A           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISA                | 62B          | 72A           | 11 1111                            | 11 1111                  | uu uuuu                         |

| TRISB                | 62B          | 72A           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISC                | 62B          | 72A           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| DIE                  | 62B          | 72A           | 0000                               | 0000                     | uuuu                            |

| PIE1                 | 62B          | 72A           | -0 0000                            | -0 0000                  | -u uuuu                         |

| PCON                 | 62B          | 72A           | 0q                                 | uq                       | uq                              |

| PR2                  | 62B          | 72A           | 1111 1111                          | 1111 1111                | 1111 1111                       |

| SSPADD               | 62B          | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| SSPSTAT              | 62B          | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| ADCON1               | 62B          | 72A           | 000                                | 000                      | uuu                             |

$\mbox{Legend:} \ \ u \ \ = \mbox{unchanged,} \ \ \ x \ \ = \ \mbox{unknown,} \ \ \ - = \ \mbox{unimplemented bit, read as '0', $q$ = value depends on condition }$

Note 1: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

<sup>2:</sup> When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

<sup>3:</sup> See Table 10-5 for reset value for specific condition.

<sup>4:</sup> On any device reset, these pins are configured as inputs.

<sup>5:</sup> This is the value that will be in the port output latch.

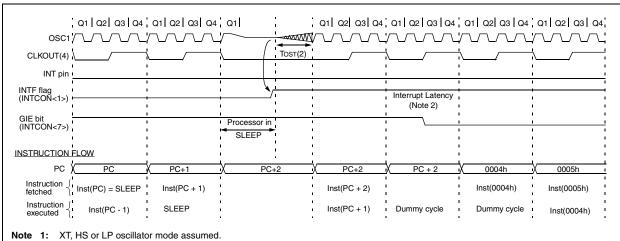

#### FIGURE 10-10: WAKE-UP FROM SLEEP THROUGH INTERRUPT

- 2: Tost = 1024Tosc (drawing not to scale) This delay will not be there for RC osc mode.

- 3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

- 4: CLKOUT is not available in these osc modes, but shown here for timing reference.

#### 10.14 Program Verification/Code Protection

If the code protection bits have not been programmed, the on-chip program memory can be read out for verification purposes.

**Note:** Microchip does not recommend code protecting windowed devices.

#### 10.15 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution, but are readable and writable during program/verify. It is recommended that only the 4 least significant bits of the ID location are used.

For ROM devices, these values are submitted along with the ROM code.

#### 10.16 <u>In-Circuit Serial Programming</u>™

PIC16CXXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three more lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

For complete details of serial programming, please refer to the In-Circuit Serial Programming (ICSP™) Guide, DS30277.

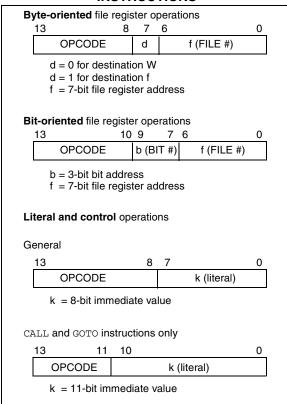

#### 11.0 INSTRUCTION SET SUMMARY

Each PIC16CXXX instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16CXX instruction set summary in Table 11-2 lists byte-oriented, bit-oriented, and literal and control operations. Table 11-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

TABLE 11-1 OPCODE FIELD DESCRIPTIONS

| Field                 | Description                                                                                                                                                        |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f                     | Register file address (0x00 to 0x7F)                                                                                                                               |

| W                     | Working register (accumulator)                                                                                                                                     |

| b                     | Bit address within an 8-bit file register                                                                                                                          |

| k                     | Literal field, constant data or label                                                                                                                              |

| x                     | Don't care location (= 0 or 1) The assembler will generate code with x = 0. It is the recommended form of use for compatibility with all Microchip software tools. |

| d                     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                       |

| PC                    | Program Counter                                                                                                                                                    |

| TO                    | Time-out bit                                                                                                                                                       |

| $\overline{	ext{PD}}$ | Power-down bit                                                                                                                                                     |

| Z                     | Zero bit                                                                                                                                                           |

| DC                    | Digit Carry bit                                                                                                                                                    |

| С                     | Carry bit                                                                                                                                                          |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- · Literal and control operations

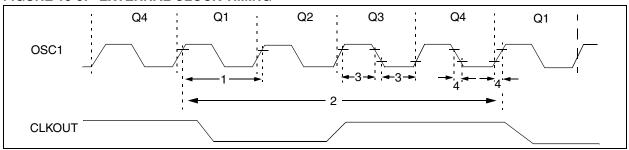

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction

execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 11-2 lists the instructions recognized by the MPASM assembler.

Figure 11-1 shows the general formats that the instructions can have.

Note: To maintain upward compatibility with future PIC16CXXX products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

## FIGURE 11-1: GENERAL FORMAT FOR INSTRUCTIONS

A description of each instruction is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

TABLE 11-2 PIC16CXXX INSTRUCTION SET

| MSb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Mnemonic,                                                                                                                                        |        | Description                  | Cycles                |     | 14-Bit | Opcode | •    | Status   | Notes |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------|-----------------------|-----|--------|--------|------|----------|-------|--|

| ADDWF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Operands                                                                                                                                         |        |                              |                       | MSb |        |        | LSb  | Affected |       |  |

| ANDWF   f, d   AND W with f   1   00   0101   deff   feff   Z   2   2   CLRF   f   Clear W   1   00   0001   1   1   1   1   1   2   2   COMF   f, d   Complement f   1   00   0001   0000   0001   Z   COMF   f, d   Decrement f   1   00   0101   deff   feff   Z   1,2   1,2   DECF   f, d   Decrement f   1   00   0101   deff   feff   Z   1,2   DECFSZ   f, d   Decrement f, Skip if 0   1(2)   00   1011   deff   feff   Z   1,2   DECFSZ   f, d   Increment f   1   00   0101   deff   feff   Z   1,2   DECFSZ   f, d   Increment f   1   00   0101   deff   feff   Z   1,2   DECFSZ   f, d   Increment f   1   00   0100   deff   feff   Z   1,2   DECFSZ   f, d   Increment f   1   00   0100   deff   feff   Z   1,2   DECFSZ   f, d   Increment f   f   00   0100   deff   feff   Z   1,2   DECFSZ   f, d   Increment f   f   00   0100   deff   feff   Z   1,2   DECFSZ   f, d   Increment f   f   00   0100   deff   feff   Z   1,2   DECFSZ   f, d   Increment f   f   00   0100   deff   feff   Z   1,2   DECFSZ   f, d   Increment f   f   00   0100   deff   feff   Z   1,2   DECFSZ   f, d   Inclusive OR W with f   f   00   0100   deff   feff   Z   1,2   DECFSZ   f, d   Inclusive OR W with f   f   00   0100   deff   feff   Z   f,2   DECFSZ   DECFSZ   f, d   Inclusive OR W with f   f   00   0100   deff   feff   Z   f,2   DECFSZ   DECFSZ   f, d   Inclusive OR W with f   f   00   0100   deff   feff   Z   f,2   DECFSZ   f,4   DECFSZ   f,5   DECFS | BYTE-ORIE                                                                                                                                        | NTED   | FILE REGISTER OPERATIONS     |                       |     |        |        |      |          |       |  |

| CLRF         f         Clear W         1         00         0001         left         fff         Z         Z         CCRW         CLRW         1         00         0001         0001         QZ         Z         CCOMF         1         00         0010         deff         fff         Z         1,2         DECFSC         f, d         Decrement f         1         00         0011         dfff         ffff         Z         1,2         1,2         DECFSZ         f, d         Increment f         1         00         0011         dfff         ffff         Z         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ADDWF                                                                                                                                            | f, d   | Add W and f                  | 1                     | 00  | 0111   | dfff   | ffff | C,DC,Z   | 1,2   |  |

| CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ANDWF                                                                                                                                            | f, d   | AND W with f                 | 1                     | 00  | 0101   | dfff   | ffff | Z        | 1,2   |  |

| COMF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CLRF                                                                                                                                             | f      | Clear f                      | 1                     | 00  | 0001   | lfff   | ffff | Z        | 2     |  |

| DECF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CLRW                                                                                                                                             | -      | Clear W                      | 1                     | 00  | 0001   | 0000   | 0011 | Z        |       |  |

| DECFSZ   f, d   Increment   f, Skip if 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | COMF                                                                                                                                             | f, d   | Complement f                 | 1                     | 00  | 1001   | dfff   | ffff | Z        |       |  |

| INCF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DECF                                                                                                                                             | f, d   | Decrement f                  | 1                     | 00  | 0011   | dfff   | ffff | Z        | 1,2   |  |

| INCFSZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DECFSZ                                                                                                                                           | f, d   |                              | 1(2)                  | 00  | 1011   | dfff   | ffff |          | 1,2,3 |  |

| Inclusive OR W with f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | INCF                                                                                                                                             | f, d   | Increment f                  | 1                     | 00  | 1010   | dfff   | ffff | Z        | 1,2   |  |

| MOVF         f, d         Move W to f         1         00         1000         defff         ffff         Z         1,2           MOVWF         f         Move W to f         1         00         1000         0000         leftf         ffff         C         1,2           NOP         -         No Operation         1         00         0000         0xx0         0000         RF         Ffff         C         1,2           RRF         f, d         Rotate Right fthrough Carry         1         00         1100         dfff         ffff         C         1,2           SUBWF         f, d         Subtract W from f         1         00         1100         dfff         ffff         C         1,2           SWAPF         f, d         Swap nibbles in f         1         00         0110         dfff         ffff         Z         1,2           SWAPF         f, d         Swap nibbles in f         1         00         0110         dfff         ffff         Z         1,2           SWAPF         f, d         Sit Clear         1         0         010b         bfff         ffff         Z         1,2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | INCFSZ                                                                                                                                           | f, d   | Increment f, Skip if 0       | 1(2)                  | 00  | 1111   | dfff   | ffff |          | 1,2,3 |  |

| MOVF         f, d         Move W to f         1         00         1000         defff         fefff         Z         1,2           MOVWF         f         Move W to f         1         00         0000         leftf         fefff         C         1,2           NOP         -         No Operation         1         00         0000         0xx0         0000         RLF         ffff         C         1,2           RRF         f, d         Rotate Right f through Carry         1         00         1100         dfff         ffff         C         1,2           SUBWF         f, d         Subtract W from f         1         00         1100         dfff         ffff         C,DC,Z         1,2           SWAPF         f, d         Swap nibbles in f         1         00         0110         dfff         ffff         1,2         1,2           SWAPF         f, d         Exclusive OR W with f         1         0         0100         dfff         ffff         Z         1,2           BFF         f, b         Bit Clear f         1         0         010b         bfff         ffff         2         1,2 <th cols<="" th=""><th>IORWF</th><th>f, d</th><th>Inclusive OR W with f</th><th></th><th>00</th><th>0100</th><th>dfff</th><th>ffff</th><th>Z</th><th></th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <th>IORWF</th> <th>f, d</th> <th>Inclusive OR W with f</th> <th></th> <th>00</th> <th>0100</th> <th>dfff</th> <th>ffff</th> <th>Z</th> <th></th> | IORWF  | f, d                         | Inclusive OR W with f |     | 00     | 0100   | dfff | ffff     | Z     |  |

| MOVWF NOP         f NO Operation         Move W to f         1         00 0000 0000 0000 0000 0000 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MOVF                                                                                                                                             | f, d   | Move f                       | 1                     | 00  | 1000   | dfff   | ffff | Z        |       |  |

| RLF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MOVWF                                                                                                                                            | f      | Move W to f                  | 1                     | 00  | 0000   | lfff   | ffff |          |       |  |

| RRF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | NOP                                                                                                                                              | -      | No Operation                 | 1                     | 0.0 | 0000   | 0xx0   | 0000 |          |       |  |

| SUBWF   f, d   Subtract W from f   1   00   0010   dfff   ffff   C,DC,Z   1,2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RLF                                                                                                                                              | f, d   | Rotate Left f through Carry  | 1                     | 00  | 1101   | dfff   | ffff | С        | 1,2   |  |

| SWAPF (n) A CORNER         Swap nibbles in f Exclusive OR W with f         1 00 0110 dfff ffff ffff         1,2 1,2 1,2           BIT-ORIENTED FILE REGISTER OPERATIONS           BCF f, b Bit Clear f Skp if Clear f BFFS (n) Bit Test f, Skip if Clear f St, b Bit Test f, Skip if Clear f St, b Bit Test f, Skip if Set f Skip if Clear f St, b Bit Test f, Skip if Set f Skip if Set skip if Set f Skip if Set s                                                                                                                             | RRF                                                                                                                                              | f, d   | Rotate Right f through Carry | 1                     | 0.0 | 1100   | dfff   | ffff | С        | 1,2   |  |

| SWAPF (n) A CORNER         Swap nibbles in f Exclusive OR W with f         1 00 0110 dfff ffff ffff         1,2 1,2 1,2           BIT-ORIENTED FILE REGISTER OPERATIONS           BCF f, b Bit Clear f Skp if Clear f BFFS (n) Bit Test f, Skip if Clear f St, b Bit Test f, Skip if Clear f St, b Bit Test f, Skip if Set f Skip if Clear f St, b Bit Test f, Skip if Set f Skip if Set skip if Set f Skip if Set s                                                                                                                             | SUBWF                                                                                                                                            | f, d   | Subtract W from f            | 1                     | 00  | 0010   | dfff   | ffff | C,DC,Z   | 1,2   |  |

| Topic   State   Topic   Topi | SWAPF                                                                                                                                            |        | Swap nibbles in f            | 1                     | 0.0 | 1110   | dfff   | ffff |          |       |  |

| BCF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | XORWF                                                                                                                                            | f, d   | Exclusive OR W with f        | 1                     | 00  | 0110   | dfff   | ffff | Z        |       |  |

| BSF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | BIT-ORIENT                                                                                                                                       | ED FIL | E REGISTER OPERATIONS        |                       |     |        |        |      |          |       |  |

| BTFSC f, b BIT Test f, Skip if Clear         1 (2) 01 10bb bfff fffff         3 3           LITERAL AND CONTROL OPERATIONS           ADDLW k AND literal and W AND literal with W CALL k Call subroutine         1 11 111 111x kkkk kkkk kkkk         C,DC,Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BCF                                                                                                                                              | f, b   | Bit Clear f                  | 1                     | 01  | 00bb   | bfff   | ffff |          | 1,2   |  |

| BTFSS   f, b   Bit Test f, Skip if Set   1 (2)   01   11bb   bfff   ffff     3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | BSF                                                                                                                                              | f, b   | Bit Set f                    | 1                     | 01  | 01bb   | bfff   | ffff |          | 1,2   |  |