Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc62b-04-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

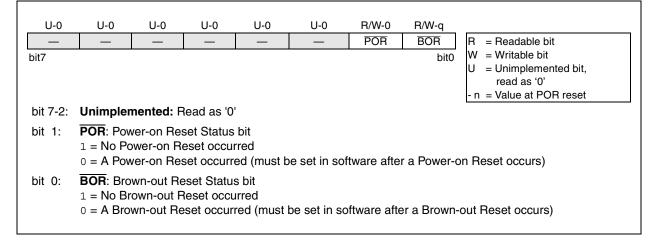

#### 2.2.2.6 PCON REGISTER

The Power Control register (PCON) contains flag bits to allow differentiation between a Power-on Reset (POR), Brown-Out Reset (BOR) and resets from other sources.

Note: On Power-on Reset, the state of the BOR bit is unknown and is not predictable. If the BODEN bit in the configuration word is set, the user must first set the BOR bit on a POR, and check it on subsequent resets. If BOR is cleared while POR remains set, a Brown-out reset has occurred. If the BODEN bit is clear, the BOR bit may be ignored.

## REGISTER 2-6: PCON REGISTER (ADDRESS 8Eh)

# 2.3 PCL and PCLATH

The program counter (PC) specifies the address of the instruction to fetch for execution. The PC is 13 bits wide. The low byte is called the PCL register and is readable and writable. The high byte is called the PCH register. This register contains the PC<12:8> bits and is not directly accessible. All updates to the PCH register go through the PCLATH register.

#### 2.3.1 STACK

The stack allows any combination of up to 8 program calls and interrupts to occur. The stack contains the return address from this branch in program execution.

Mid-range devices have an 8 level deep hardware stack. The stack space is not part of either program or data space and the stack pointer is not accessible. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RET-FIE instruction execution. PCLATH is not modified when the stack is PUSHed or POPed.

After the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

## 2.4 Program Memory Paging

The CALL and GOTO instructions provide 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper bit of the address is provided by PCLATH<3>. The user must ensure that the page select bit is programmed to address the proper program memory page. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is popped from the stack. Therefore, manipulation of the PCLATH<3> bit is not required for the return instructions.

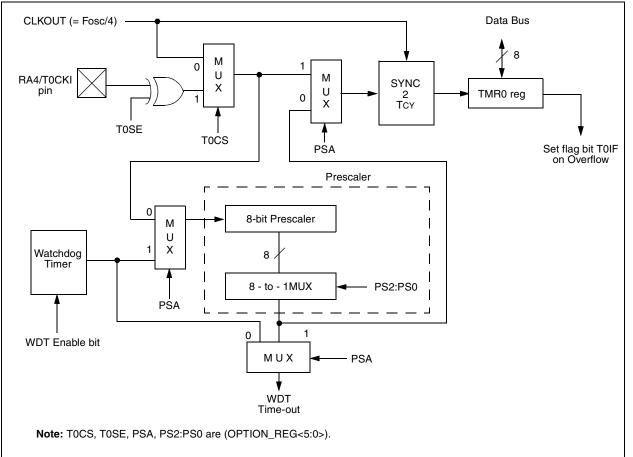

#### 4.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, (i.e., it can be changed "on-the-fly" during program execution).

Note: To avoid an unintended device RESET, a specific instruction sequence (shown in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, DS33023) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

#### 4.3 <u>Timer0 Interrupt</u>

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP since the timer is shut off during SLEEP.

#### FIGURE 4-2: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

### TABLE 4-1 REGISTERS ASSOCIATED WITH TIMER0

| Address | Name       | Bit 7  | Bit 6                   | Bit 5                         | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|------------|--------|-------------------------|-------------------------------|-------|-------|-------|-------|-----------|--------------------------|---------------------------|

| 01h     | TMR0       | Timer0 | imer0 module's register |                               |       |       |       |       |           | xxxx xxxx                | uuuu uuuu                 |

| 0Bh,8Bh | INTCON     | GIE    | PEIE                    | TOIE                          | INTE  | RBIE  | T0IF  | INTF  | RBIF      | 0000 000x                | 0000 000u                 |

| 81h     | OPTION_REG | RBPU   | INTEDG                  | TOCS TOSE PSA PS2 PS1 PS0     |       |       |       |       | 1111 1111 | 1111 1111                |                           |

| 85h     | TRISA      |        | _                       | PORTA Data Direction Register |       |       |       |       | 11 1111   | 11 1111                  |                           |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

NOTES:

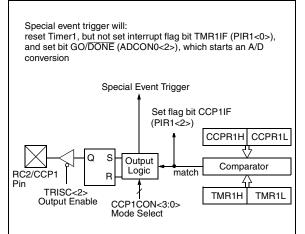

### 7.2 <u>Compare Mode</u>

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- driven High

- driven Low

- remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). The interrupt flag bit, CCP1IF, is set on all compare matches.

#### FIGURE 7-2: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 7.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

| Note: | Clearing the CCP1CON register will force       |

|-------|------------------------------------------------|

|       | the RC2/CCP1 compare output latch to the       |

|       | default low level. This is not the data latch. |

#### 7.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 7.2.3 SOFTWARE INTERRUPT MODE

When a generated software interrupt is chosen, the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 7.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated, which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special trigger output of CCP1 resets the TMR1 register pair and starts an A/D conversion (if the A/D module is enabled).

### TABLE 7-3 REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

| Address | Name    | Bit 7                               | Bit 6                                                                       | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1     | Bit 0     | Value on<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|---------|-------------------------------------|-----------------------------------------------------------------------------|-------|-------|--------|--------|-----------|-----------|-------------------------|---------------------------------|

| 0Bh,8Bh | INTCON  | GIE                                 | PEIE                                                                        | TOIE  | INTE  | RBIE   | TOIF   | INTF      | RBIF      | 0000 0003               | : 0000 000u                     |

| 0Ch     | PIR1    | —                                   | ADIF                                                                        | —     | —     | SSPIF  | CCP1IF | TMR2IF    | TMR1IF    | -0 0000                 | -0 0000                         |

| 8Ch     | PIE1    | —                                   | ADIE                                                                        | _     | —     | SSPIE  | CCP1IE | TMR2IE    | TMR1IE    | -0 0000                 | -0 0000                         |

| 87h     | TRISC   | PORTC Da                            | PORTC Data Direction Register                                               |       |       |        |        |           |           | 1111 1111               | 1111 1111                       |

| 0Eh     | TMR1L   | Holding reg                         | Holding register for the Least Significant Byte of the 16-bit TMR1 register |       |       |        |        |           | XXXX XXXX | uuuu uuuu               |                                 |

| 0Fh     | TMR1H   | Holding reg                         | Holding register for the Most Significant Byte of the 16-bit TMR1register   |       |       |        |        |           | XXXX XXXX | uuuu uuuu               |                                 |

| 10h     | T1CON   | —                                   | - T1CKPS1 T1CKPS0 T1OSCEN T1SYNC TMR1CS TMR10N                              |       |       |        |        |           | 00 0000   | uu uuuu                 |                                 |

| 15h     | CCPR1L  | Capture/Compare/PWM register1 (LSB) |                                                                             |       |       |        |        | XXXX XXXX | uuuu uuuu |                         |                                 |

| 16h     | CCPR1H  | Capture/Co                          | Capture/Compare/PWM register1 (MSB)                                         |       |       |        |        |           | XXXX XXXX | uuuu uuuu               |                                 |

| 17h     | CCP1CON | —                                   |                                                                             | CCP1X | CCP1Y | CCP1M3 | CCP1M2 | CCP1M1    | CCP1M0    | 00 0000                 | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by Capture and Timer1.

#### 9.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 9.5TAD per 8-bit conversion. The source of the A/D conversion clock is software selectable. The four possible options for TAD are:

- 2Tosc

- 8Tosc

- 32Tosc

- Internal RC oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu s.$

The A/D module can operate during sleep mode, but the RC oscillator must be selected as the A/D clock source prior to the SLEEP instruction.

Table 9-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

## 9.3 Configuring Analog Port Pins

The ADCON1 and TRISA registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS2:CHS0 bits and the TRIS bits.

- Note 1: When reading the port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs, will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- **Note 2:** Analog levels on any pin that is defined as a digital input (including the AN4:AN0 pins) may cause the input buffer to consume current that is out of the devices specification.

## TABLE 9-1TAD vs. DEVICE OPERATING FREQUENCIES

| AD Cloc           | k Source (TAD) | Device Frequency          |                           |                           |                         |  |  |  |

|-------------------|----------------|---------------------------|---------------------------|---------------------------|-------------------------|--|--|--|

| Operation         | ADCS1:ADCS0    | 20 MHz                    | 5 MHz                     | 1.25 MHz                  | 333.33 kHz              |  |  |  |

| 2Tosc             | 00             | 100 ns <sup>(2)</sup>     | 400 ns <sup>(2)</sup>     | 1.6 μs                    | 6 μs                    |  |  |  |

| 8Tosc             | 01             | 400 ns <sup>(2)</sup>     | 1.6 μs                    | 6.4 μs                    | 24 μs <sup>(3)</sup>    |  |  |  |

| 32Tosc            | 10             | 1.6 μs                    | 6.4 μs                    | 25.6 μs <sup>(3)</sup>    | 96 μs <sup>(3)</sup>    |  |  |  |

| RC <sup>(5)</sup> | 11             | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1)</sup> |  |  |  |

Legend: Shaded cells are outside of recommended range.

Note 1: The RC source has a typical TAD time of 4  $\mu$ s.

- 2: These values violate the minimum required TAD time.

- **3:** For faster conversion times, the selection of another clock source is recommended.

- 4: When device frequency is greater than 1 MHz, the RC A/D conversion clock source is recommended for sleep operation only.

- 5: For extended voltage devices (LC), please refer to Electrical Specifications section.

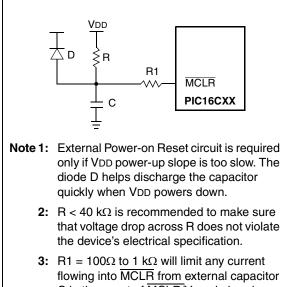

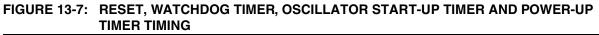

### 10.4 Power-On Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.5V - 2.1V). To take advantage of the POR, just tie the  $\overline{\text{MCLR}}$  pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified (SVDD, parameter D004). For a slow rise time, see Figure 10-6.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met. Brown-out Reset may be used to meet the start-up conditions.

#### FIGURE 10-6: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

#### R1 = 100Ω to 1 kΩ will limit any current flowing into $\overline{MCLR}$ from external capacitor C in the event of $\overline{MCLR}/VPP$ pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

### 10.5 Power-up Timer (PWRT)

The Power-up Timer provides a fixed nominal time-out (TPWRT, parameter #33) from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip-to-chip due to VDD, temperature and process variation. See DC parameters for details.

## 10.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a delay of 1024 oscillator cycles (from OSC1 input) after the PWRT delay is over (TOST, parameter #32). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

Note: The OST delay may not occur when the device wakes from SLEEP.

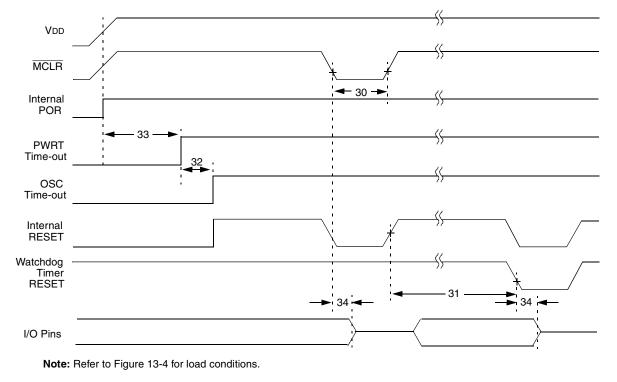

### 10.7 Brown-Out Reset (BOR)

The configuration bit, BODEN, can enable or disable the Brown-Out Reset circuit. If VPP falls below Vbor (parameter #35, about  $100\mu$ S), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a reset may not occur.

Once the brown-out occurs, the device will remain in brown-out reset until VDD rises above VBOR. The power-up timer then keeps the device in reset for TPWRT (parameter #33, about 72mS). If VDD should fall below VBOR during TPWRT, the brown-out reset process will restart when VDD rises above VBOR with the power-up timer reset. The power-up timer is always enabled when the brown-out reset circuit is enabled, regardless of the state of the PWRT configuration bit.

#### 10.13 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D and disable external clocks. Pull all I/O pins that are hi-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC, parameter D042).

#### 10.13.1 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- 1. External reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change, or some Peripheral Interrupts.

External  $\overline{\text{MCLR}}$  Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from SLEEP:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. CCP capture mode interrupt.

- Special event trigger (Timer1 in asynchronous mode using an external clock. CCP1 is in compare mode).

- 4. SSP (Start/Stop) bit detect interrupt.

- 5. SSP transmit or receive in slave mode (SPI/I<sup>2</sup>C).

- 6. USART RX or TX (synchronous slave mode).

Other peripherals cannot generate interrupts since during SLEEP, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is

regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device resumes execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, a NOP should follow the SLEEP instruction.

#### 10.13.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

<sup>© 1998-2013</sup> Microchip Technology Inc.

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSS f,b                                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                        |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                                    |

| Description:     | If bit 'b' in register 'f' is '0', then the next instruction is executed.<br>If bit 'b' is '1', then the next instruction is discarded and a $NOP$ is executed instead, making this a 2TCY instruction. |

| CLRF             | Clear f                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CLRF f                                               |

| Operands:        | $0 \le f \le 127$                                                     |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSC f,b                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                    |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                   |

| Description:     | If bit 'b' in register 'f' is '1', then the next instruction is executed.<br>If bit 'b' in register 'f' is '0', then the next instruction is discarded, and a NOP is executed instead, making this a 2TCY instruction. |

| CLRW             | Clear W                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                          |

| Operands:        | None                                                                  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | W register is cleared. Zero bit (Z) is set.                           |

| CALL             | Call Subroutine                                                                                                                                                                                | CLRWDT           | Clear Watchdog Timer                                                                                                             |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                        | Syntax:          | [label] CLRWDT                                                                                                                   |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                             | Operands:        | None                                                                                                                             |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                               | Operation:       | $00h \rightarrow WDT$<br>0 $\rightarrow WDT$ prescaler,<br>1 $\rightarrow \overline{TO}$                                         |

| Status Affected: | None                                                                                                                                                                                           |                  | $1 \rightarrow \overline{PD}$                                                                                                    |

| Description:     | Call Subroutine. First, return address                                                                                                                                                         | Status Affected: | TO, PD                                                                                                                           |

|                  | (PC+1) is pushed onto the stack. The<br>eleven bit immediate address is loaded<br>into PC bits <10:0>. The upper bits of<br>the PC are loaded from PCLATH.<br>CALL is a two cycle instruction. | Description:     | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT. Status bits TO and PD<br>are set. |

MPLIB is a librarian for pre-compiled code to be used with MPLINK. When a routine from a library is called from another source file, only the modules that contains that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications. MPLIB manages the creation and modification of library files.

MPLINK features include:

- MPLINK works with MPASM and MPLAB-C17 and MPLAB-C18.

- MPLINK allows all memory areas to be defined as sections to provide link-time flexibility.

MPLIB features include:

- MPLIB makes linking easier because single libraries can be included instead of many smaller files.

- MPLIB helps keep code maintainable by grouping related modules together.

- MPLIB commands allow libraries to be created and modules to be added, listed, replaced, deleted, or extracted.

## 12.5 MPLAB-SIM Software Simulator

The MPLAB-SIM Software Simulator allows code development in a PC host environment by simulating the PIC series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file or user-defined key press to any of the pins. The execution can be performed in single step, execute until break, or trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C17 and MPLAB-C18 and MPASM. The Software Simulator offers the flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

#### 12.6 <u>MPLAB-ICE High Performance</u> <u>Universal In-Circuit Emulator with</u> <u>MPLAB IDE</u>

The MPLAB-ICE Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers (MCUs). Software control of MPLAB-ICE is provided by the MPLAB Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB-ICE allows expansion to support new PIC microcontrollers.

The MPLAB-ICE Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows 3.x/95/98 environment were chosen to best make these features available to you, the end user.

MPLAB-ICE 2000 is a full-featured emulator system with enhanced trace, trigger, and data monitoring features. Both systems use the same processor modules and will operate across the full operating speed range of the PIC MCU.

## 12.7 PICMASTER/PICMASTER CE

The PICMASTER system from Microchip Technology is a full-featured, professional quality emulator system. This flexible in-circuit emulator provides a high-quality, universal platform for emulating Microchip 8-bit PIC microcontrollers (MCUs). PICMASTER systems are sold worldwide, with a CE compliant model available for European Union (EU) countries.

# 12.8 <u>ICEPIC</u>

ICEPIC is a low-cost in-circuit emulation solution for the Microchip Technology PIC16C5X, PIC16C6X, PIC16C7X, and PIC16CXXX families of 8-bit one-timeprogrammable (OTP) microcontrollers. The modular system can support different subsets of PIC16C5X or PIC16CXXX products through the use of interchangeable personality modules or daughter boards. The emulator is capable of emulating without target application circuitry being present.

### 12.9 MPLAB-ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB-ICD, is a powerful, low-cost run-time development tool. This tool is based on the flash PIC16F877 and can be used to develop for this and other PIC microcontrollers from the PIC16CXXX family. MPLAB-ICD utilizes the In-Circuit Debugging capability built into the PIC16F87X. This feature, along with Microchip's In-Circuit Serial Programming protocol, offers cost-effective in-circuit flash programming and debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time. The MPLAB-ICD is also a programmer for the flash PIC16F87X family.

### 12.10 PRO MATE II Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode. PRO MATE II is CE compliant.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In

stand-alone mode the PRO MATE II can read, verify or program PIC devices. It can also set code-protect bits in this mode.

#### 12.11 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, lowcost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

PICSTART Plus supports all PIC devices with up to 40 pins. Larger pin count devices such as the PIC16C92X, and PIC17C76X may be supported with an adapter socket. PICSTART Plus is CE compliant.

#### 12.12 <u>SIMICE Entry-Level</u> <u>Hardware Simulator</u>

SIMICE is an entry-level hardware development system designed to operate in a PC-based environment with Microchip's simulator MPLAB-SIM. Both SIMICE and MPLAB-SIM run under Microchip Technology's MPLAB Integrated Development Environment (IDE) software. Specifically, SIMICE provides hardware simulation for Microchip's PIC12C5XX, PIC12CE5XX, and PIC16C5X families of PIC 8-bit microcontrollers. SIM-ICE works in conjunction with MPLAB-SIM to provide non-real-time I/O port emulation. SIMICE enables a developer to run simulator code for driving the target system. In addition, the target system can provide input to the simulator code. This capability allows for simple and interactive debugging without having to manually generate MPLAB-SIM stimulus files. SIMICE is a valuable debugging tool for entry-level system development.

### 12.13 <u>PICDEM-1 Low-Cost PIC MCU</u> <u>Demonstration Board</u>

The PICDEM-1 is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The users can program the sample microcontrollers provided with the PICDEM-1 board, on a PRO MATE II or PICSTART-Plus programmer, and easily test firmware. The user can also connect the PICDEM-1 board to the MPLAB-ICE emulator and download the firmware to the emulator for testing. Additional prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push-button switches and eight LEDs connected to PORTB.

## 12.14 PICDEM-2 Low-Cost PIC16CXX Demonstration Board

The PICDEM-2 is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-2 board, on a PRO MATE II programmer or PICSTART-Plus, and easily test firmware. The MPLAB-ICE emulator may also be used with the PICDEM-2 board to test firmware. Additional prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push-button switches, a potentiometer for simulated analog input, a Serial EEPROM to demonstrate usage of the I<sup>2</sup>C bus and separate headers for connection to an LCD module and a keypad.

## 12.15 <u>PICDEM-3 Low-Cost PIC16CXXX</u> <u>Demonstration Board</u>

The PICDEM-3 is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with a LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-3 board, on a PRO MATE II programmer or PICSTART Plus with an adapter socket, and easily test firmware. The MPLAB-ICE emulator may also be used with the PICDEM-3 board to test firmware. Additional prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include an RS-232 interface, push-button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM-3 board is an LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM-3 provides an additional RS-232 interface and Windows 3.1 software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

# 12.16 PICDEM-17

The PICDEM-17 is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756, PIC17C762, and PIC17C766. All necessary hardware is included to run basic demo programs, which are supplied on a 3.5-inch disk. A programmed sample is included, and the user may erase it and program it with the other sample programs using the PRO MATE II or PICSTART Plus device programmers and easily debug

© 1998-2013 Microchip Technology Inc.

NOTES:

# **13.0 ELECTRICAL CHARACTERISTICS**

#### Absolute Maximum Ratings (†)

| Ambient temperature under bias                                                                              | 55°C to +125°C            |

|-------------------------------------------------------------------------------------------------------------|---------------------------|

| Storage temperature                                                                                         |                           |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)                                          |                           |

| Voltage on VDD with respect to VSS                                                                          |                           |

| Voltage on MCLR with respect to Vss (Note 2)                                                                |                           |

| Voltage on RA4 with respect to Vss                                                                          |                           |

| Total power dissipation (Note 1)                                                                            |                           |

| Maximum current out of Vss pin                                                                              |                           |

| Maximum current into VDD pin                                                                                |                           |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                | ±20 mA                    |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                              |                           |

| Maximum output current sunk by any I/O pin                                                                  | 25 mA                     |

| Maximum output current sourced by any I/O pin                                                               | 25 mA                     |

| Maximum current sunk by PORTA and PORTB (combined)                                                          | 200 mA                    |

| Maximum current sourced by PORTA and PORTB (combined)                                                       | 200 mA                    |

| Maximum current sunk by PORTC                                                                               | 200 mA                    |

| Maximum current sourced by PORTC                                                                            | 200 mA                    |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-V | ЮН) x IOH} + ∑(VOI x IOL) |

**2:** Voltage spikes below Vss at the MCLR/VPP pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR/VPP pin, rather than pulling this pin directly to Vss.

**†** NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### FIGURE 13-8: BROWN-OUT RESET TIMING

# TABLE 13-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                                   | Min | Тур†         | Max | Units | Conditions                                         |

|--------------|-------|--------------------------------------------------|-----|--------------|-----|-------|----------------------------------------------------|

| 30           | TmcL  | MCLR Pulse Width (low)                           | 2   |              | _   | μs    | VDD = 5V, -40°C to +125°C                          |

| 31*          | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler) | 7   | 18           | 33  | ms    | VDD = 5V, -40°C to +125°C                          |

| 32           | Tost  | Oscillator Start-up Timer Period                 |     | 1024<br>Tosc | —   | —     | Tosc = OSC1 period                                 |

| 33*          | Tpwrt | Power-up Timer Period                            | 28  | 72           | 132 | ms    | $VDD = 5V, -40^{\circ}C \text{ to } +125^{\circ}C$ |

| 34           | Tıoz  | I/O Hi-impedance from MCLR<br>Low or WDT reset   | _   | _            | 2.1 | μS    |                                                    |

| 35           | TBOR  | Brown-out Reset Pulse Width                      | 100 | _            | _   | μS    | $VDD \le BVDD$ (D005)                              |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

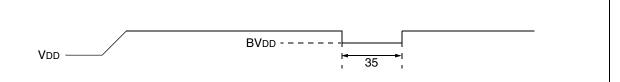

# FIGURE 13-16: I<sup>2</sup>C BUS DATA TIMING

#### TABLE 13-12: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Param.<br>No. | Sym     | Characte                          | eristic      | Min        | Max  | Units | Conditions                                           |

|---------------|---------|-----------------------------------|--------------|------------|------|-------|------------------------------------------------------|

| 100*          | Thigh   | Clock high time                   | 100 kHz mode | 4.0        | —    | μS    | Device must operate at a min-<br>imum of 1.5 MHz     |

|               |         |                                   | 400 kHz mode | 0.6        | _    | μS    | Device must operate at a min-<br>imum of 10 MHz      |

|               |         |                                   | SSP Module   | 1.5TCY     | —    |       |                                                      |

| 101*          | TLOW    | Clock low time                    | 100 kHz mode | 4.7        | -    | μS    | Device must operate at a min-<br>imum of 1.5 MHz     |

|               |         |                                   | 400 kHz mode | 1.3        | —    | μS    | Device must operate at a min-<br>imum of 10 MHz      |

|               |         |                                   | SSP Module   | 1.5TCY     | —    |       |                                                      |

| 102*          | TR      | SDA and SCL rise                  | 100 kHz mode | —          | 1000 | ns    |                                                      |

|               | time    | time                              | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from 10-400 pF                 |

| 103*          | TF      | SDA and SCL fall time             | 100 kHz mode | —          | 300  | ns    |                                                      |

|               |         |                                   | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from 10-400 pF                 |

| 90*           | TSU:STA | START condition setup time        | 100 kHz mode | 4.7        | —    | μs    | Only relevant for repeated START condition           |

|               |         |                                   | 400 kHz mode | 0.6        | —    | μs    |                                                      |

| 91*           | THD:STA | START condition hold              | 100 kHz mode | 4.0        |      | μs    | After this period the first clock pulse is generated |

|               |         | time                              | 400 kHz mode | 0.6        | —    | μS    |                                                      |

| 106*          | THD:DAT | Data input hold time              | 100 kHz mode | 0          |      | ns    |                                                      |

|               |         |                                   | 400 kHz mode | 0          | 0.9  | μs    |                                                      |

| 107*          | TSU:DAT | U:DAT Data input setup time       | 100 kHz mode | 250        | —    | ns    | Note 2                                               |

|               |         |                                   | 400 kHz mode | 100        |      | ns    |                                                      |

| 92*           | Tsu:sto | TSU:STO STOP condition setup time | 100 kHz mode | 4.7        |      | μs    |                                                      |

|               |         |                                   | 400 kHz mode | 0.6        | _    | μS    |                                                      |

| 109*          | ΤΑΑ     | Output valid from clock           | 100 kHz mode | —          | 3500 | ns    | Note 1                                               |

|               |         |                                   | 400 kHz mode | —          |      | ns    |                                                      |

| 110*          | TBUF    | Bus free time                     | 100 kHz mode | 4.7        | _    | μS    | Time the bus must be free                            |

|               |         |                                   | 400 kHz mode | 1.3        | —    | μs    | before a new transmission<br>can start               |

|               | Cb      | Bus capacitive loading            |              | —          | 400  | pF    |                                                      |

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

2: A fast-mode (400 kHz) I<sup>2</sup>C-bus device can be used in a standard-mode (100 kHz) I<sup>2</sup>C-bus system, but the requirement Tsu:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max.+tsu;DAT = 1000 + 250 = 1250 ns (according to the standard-mode I<sup>2</sup>C bus specification) before the SCL line is released.

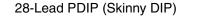

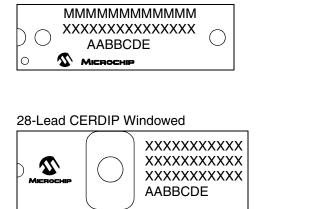

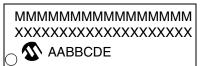

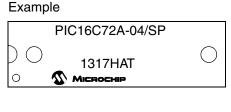

# **15.0 PACKAGING INFORMATION**

## 15.1 Package Marking Information

28-Lead SOIC

#### Example

# Example PIC16C62B-20/SO

| 28-Lead SSOP                            | Example                |  |  |

|-----------------------------------------|------------------------|--|--|

| xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx | PIC16C62B<br>20I/SS025 |  |  |

|                                         | ○                      |  |  |

| ,                                                                                |                               |                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|----------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| be carried over to the next line thus limiting the number of available character | <br>XXX<br>AA<br>BB<br>C<br>D | <ul> <li>Customer specific information*</li> <li>Year code (last 2 digits of calendar year)</li> <li>Week code (week of January 1 is week '01')</li> <li>Facility code of the plant at which wafer is manufactured</li> <li>O = Outside Vendor</li> <li>C = 5" Line</li> <li>S = 6" Line</li> <li>H = 8" Line</li> <li>Mask revision number</li> <li>Assembly code of the plant or country of origin in which</li> </ul> |  |

|                                                                                  | be carrie                     | In the event the full Microchip part number cannot be marked on one line, it wi<br>be carried over to the next line thus limiting the number of available characters<br>for customer specific information.                                                                                                                                                                                                               |  |

Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask rev#, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

© 1998-2013 Microchip Technology Inc.

# **APPENDIX A: REVISION HISTORY**

| Version | Date | Revision Description                                                                                                                                                                                         |

|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A       | 7/98 | This is a new data sheet. However, the devices described in this data sheet are the upgrades to the devices found in the <i>PIC16C6X Data Sheet</i> , DS30234, and the <i>PIC16C7X Data Sheet</i> , DS30390. |

# APPENDIX B: CONVERSION CONSIDERATIONS

Considerations for converting from previous versions of devices to the ones listed in this data sheet are listed in Table B-1.

## TABLE B-1: CONVERSION CONSIDERATIONS

| Difference    | PIC16C62A/72                                                         | PIC16C62B/72A    |

|---------------|----------------------------------------------------------------------|------------------|

| Voltage Range | 2.5V - 6.0V                                                          | 2.5V - 5.5V      |

| SSP module    | Basic SSP (2 mode SPI)                                               | SSP (4 mode SPI) |

| CCP module    | CCP does not reset TMR1 when in special event trigger mode.          | N/A              |

| Timer1 module | Writing to TMR1L register can cause over-<br>flow in TMR1H register. | N/A              |

# APPENDIX C: MIGRATION FROM BASE-LINE TO MID-RANGE DEVICES

This section discusses how to migrate from a baseline device (i.e., PIC16C5X) to a mid-range device (i.e., PIC16CXXX).

The following are the list of modifications over the PIC16C5X microcontroller family:

- 1. Instruction word length is increased to 14-bits. This allows larger page sizes both in program memory (2K now as opposed to 512 before) and register file (128 bytes now versus 32 bytes before).

- A PC high latch register (PCLATH) is added to handle program memory paging. Bits PA2, PA1, PA0 are removed from STATUS register.

- 3. Data memory paging is redefined slightly. STATUS register is modified.

- Four new instructions have been added: RETURN, RETFIE, ADDLW, and SUBLW. Two instructions TRIS and OPTION are being phased out although they are kept for compati-bility with PIC16C5X.

- 5. OPTION\_REG and TRIS registers are made addressable.

- 6. Interrupt capability is added. Interrupt vector is at 0004h.

- 7. Stack size is increased to 8 deep.

- 8. Reset vector is changed to 0000h.

- 9. Reset of all registers is revisited. Five different reset (and wake-up) types are recognized. Registers are reset differently.

- 10. Wake up from SLEEP through interrupt is added.

- 11. Two separate timers, Oscillator Start-up Timer (OST) and Power-up Timer (PWRT) are included for more reliable power-up. These timers are invoked selectively to avoid unnecessary delays on power-up and wake-up.

- 12. PORTB has weak pull-ups and interrupt on change feature.

- 13. T0CKI pin is also a port pin (RA4) now.

- 14. FSR is made a full eight bit register.

- 15. "In-circuit serial programming" is made possible. The user can program PIC16CXX devices using only five pins: VDD, Vss, MCLR/VPP, RB6 (clock) and RB7 (data in/out).

- 16. PCON status register is added with a Power-on Reset status bit (POR).

- 17. Code protection scheme is enhanced such that portions of the program memory can be protected, while the remainder is unprotected.

- Brown-out protection circuitry has been added. Controlled by configuration word bit BODEN. Brown-out reset ensures the device is placed in a reset condition if VDD dips below a fixed setpoint.

To convert code written for PIC16C5X to PIC16CXXX, the user should take the following steps:

- 1. Remove any program memory page select operations (PA2, PA1, PA0 bits) for CALL, GOTO.

- 2. Revisit any computed jump operations (write to PC or add to PC, etc.) to make sure page bits are set properly under the new scheme.

- 3. Eliminate any data memory page switching. Redefine data variables to reallocate them.

- 4. Verify all writes to STATUS, OPTION, and FSR registers since these have changed.

- 5. Change reset vector to 0000h.

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

# READER RESPONSE

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE: | Technical Publications Manager<br>Reader Response                                        | Total Pages Sent                |  |  |

|------------|------------------------------------------------------------------------------------------|---------------------------------|--|--|

| Fror       | n: Name                                                                                  |                                 |  |  |

|            | Company                                                                                  |                                 |  |  |

|            | Address                                                                                  |                                 |  |  |

|            | City / State / ZIP / Country                                                             |                                 |  |  |

|            | Telephone: ()                                                                            | FAX: ()                         |  |  |

| Арр        | lication (optional):                                                                     |                                 |  |  |

| Wou        | Ild you like a reply?YN                                                                  |                                 |  |  |

| Dev        | ice: 24xx010                                                                             | Literature Number: DS35008C     |  |  |

| Que        | stions:                                                                                  |                                 |  |  |

| 1.         | What are the best features of this document?                                             |                                 |  |  |

|            |                                                                                          |                                 |  |  |

| 2.         | How does this document meet your hardware and softw                                      | are development needs?          |  |  |

|            |                                                                                          |                                 |  |  |

| 3.         | Do you find the organization of this document easy to fo                                 | llow? If not, why?              |  |  |

|            |                                                                                          |                                 |  |  |

|            |                                                                                          |                                 |  |  |

| 4.         | What additions to the document do you think would enh                                    | ance the structure and subject? |  |  |

|            |                                                                                          |                                 |  |  |

| 5.         | What deletions from the document could be made without affecting the overall usefulness? |                                 |  |  |

|            |                                                                                          |                                 |  |  |

|            |                                                                                          |                                 |  |  |

| 6.         | Is there any incorrect or misleading information (what ar                                | nd where)?                      |  |  |

|            |                                                                                          |                                 |  |  |

| 7.         | How would you improve this document?                                                     |                                 |  |  |

|            |                                                                                          |                                 |  |  |

|            |                                                                                          |                                 |  |  |