Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc62b-04-ss |

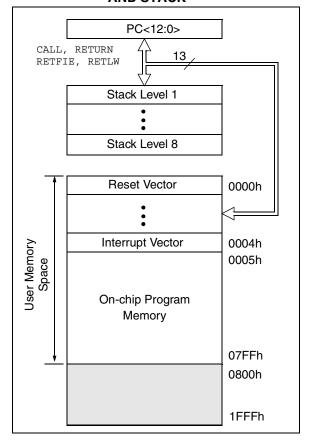

## 2.0 MEMORY ORGANIZATION

There are two memory blocks in each of these microcontrollers. Each block (Program Memory and Data Memory) has its own bus, so that concurrent access can occur.

Additional information on device memory may be found in the  $PICmicro^{TM}$  Mid-Range Reference Manual, (DS33023).

## 2.1 <u>Program Memory Organization</u>

The PIC16C62B/72A devices have a 13-bit program counter capable of addressing an 8K  $\times$  14 program memory space. Each device has 2K  $\times$  14 words of program memory. Accessing a location above 07FFh will cause a wraparound.

The reset vector is at 0000h and the interrupt vector is at 0004h.

FIGURE 2-1: PROGRAM MEMORY MAP AND STACK

#### 2.2.2.1 STATUS REGISTER

The STATUS register, shown in Register 2-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, the write to these three bits is disabled. These bits are set or cleared according to the device logic. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are not writable. The result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

- **Note 1:** The IRP and RP1 bits are reserved. Maintain these bits clear to ensure upward compatibility with future products.

- Note 2: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions.

## REGISTER 2-1: STATUS REGISTER (ADDRESS 03h, 83h)

| R/W-0    | R/W-0                               | R/W-0                                                               | R-1               | R-1         | R/W-x                                        | R/W-x        | R/W-x |                                                                              |

|----------|-------------------------------------|---------------------------------------------------------------------|-------------------|-------------|----------------------------------------------|--------------|-------|------------------------------------------------------------------------------|

| IRP      | RP1                                 | RP0                                                                 | TO                | PD          | Z                                            | DC           | С     | R = Readable bit                                                             |

| bit7     |                                     |                                                                     |                   |             |                                              |              | bit0  | W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset |

| oit 7:   |                                     | ster Bank S<br>maintain c                                           |                   | (used for i | ndirect add                                  | ressing)     |       |                                                                              |

| bit 6-5: | 01 = Bank<br>00 = Bank<br>Each bank | Register E<br>1 (80h - F<br>0 (00h - 7<br>is 128 byt<br>1 is reserv | Fh)<br>Fh)<br>tes | ·           | ed for direc                                 | t addressin  | g)    |                                                                              |

| bit 4:   |                                     |                                                                     |                   | struction,  | or SLEEP i                                   | nstruction   |       |                                                                              |

| bit 3:   |                                     | r-down bit<br>power-up o<br>ecution of t                            | •                 |             |                                              |              |       |                                                                              |

| bit 2:   |                                     | sult of an a                                                        |                   |             | peration is peration is                      |              |       |                                                                              |

| bit 1:   | 1 = A carr                          | y-out from                                                          | the 4th lo        | w order bi  | W,SUBLW,S<br>it of the resi<br>bit of the re | ult occurred |       | r borrow, the polarity is reverse                                            |

| bit 0:   | 1 = A carr                          | y-out from                                                          | the most          | significant | BLW, SUBWF<br>t bit of the rent bit of the   | esult occur  | red   | ow, the polarity is reversed)                                                |

|          |                                     | erand. For                                                          |                   |             |                                              |              |       | ding the two's complement of the either the high or low order bit            |

#### 2.2.2.3 INTCON REGISTER

The INTCON Register is a readable and writable register, which contains various interrupt enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts.

Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## REGISTER 2-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| R/W-0  | R/W-0             | R/W-0                                      | R/W-0                  | R/W-0                                    | R/W-0        | R/W-0      | R/W-x         |                                   |

|--------|-------------------|--------------------------------------------|------------------------|------------------------------------------|--------------|------------|---------------|-----------------------------------|

| GIE    | PEIE              | TOIE                                       | INTE                   | RBIE                                     | T0IF         | INTF       | RBIF          | R = Readable bit W = Writable bit |

| bit7   |                   |                                            |                        |                                          |              |            | bit0          | - n = Value at POR reset          |

| bit 7: |                   | al Interrup<br>es all un-r<br>les all inte | nasked in              |                                          |              |            |               |                                   |

| bit 6: | <b>PEIE</b> : Per | ripheral Int                               | errupt En<br>nasked pe | eripheral ir                             | nterrupts    |            |               |                                   |

| bit 5: |                   | R0 Overflo<br>es the TM<br>les the TM      | R0 interru             | ıpt                                      | bit          |            |               |                                   |

| bit 4: |                   | es the RB                                  | 0/INT exte             | rrupt Enat<br>ernal inter<br>ernal inter | rupt         |            |               |                                   |

| bit 3: |                   | es the RB                                  | port char              | upt Enable<br>nge interru<br>nge interru | pt           |            |               |                                   |

| bit 2: |                   |                                            | nas overflo            | owed (soft                               | ware must o  | clear bit) |               |                                   |

| bit 1: |                   | RB0/INT ex                                 | cternal into           |                                          | urred (softw | are must o | clear bit)    |                                   |

| bit 0: |                   | st one of t                                | he RB7:R               | B4 input p                               |              |            | ite (clear by | reading PORTB)                    |

Note:

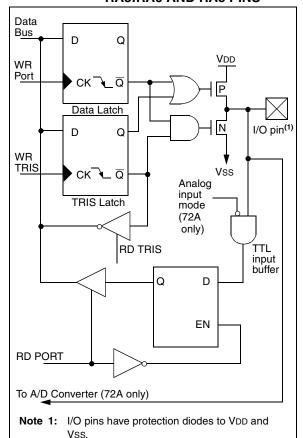

## 3.0 I/O PORTS

Some I/O port pins are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the  $PIC^{@}$  MCU Mid-Range Reference Manual, (DS33023).

## 3.1 PORTA and the TRISA Register

PORTA is a 6-bit wide bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (=1) will make the corresponding PORTA pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISA bit (=0) will make the corresponding PORTA pin an output, (i.e., put the contents of the output latch on the selected pin).

The PORTA register reads the state of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

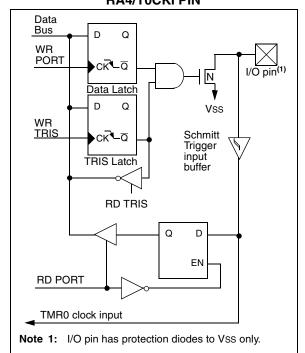

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers.

Pin RA5 is multiplexed with the SSP to become the RA5/SS pin.

On the PIC16C72A device, other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

**Note:** On a Power-on Reset, pins with analog functions are configured as analog inputs with digital input buffers disabled. A digital read of these pins will return '0'.

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

# FIGURE 3-1: BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

FIGURE 3-2: BLOCK DIAGRAM OF RA4/T0CKI PIN

TABLE 3-3 PORTB FUNCTIONS

| Name    | Bit# | Buffer                | Function                                                                                                            |

|---------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                          |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB3     | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB6     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming clock. |

| RB7     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming data.  |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

## TABLE 3-4 SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address | Name       | Bit 7   | Bit 6          | Bit 5     | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|------------|---------|----------------|-----------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 06h     | PORTB      | RB7     | RB6            | RB5       | RB4   | RB3   | RB2   | RB1   | RB0   | xxxx xxxx                | uuuu uuuu                 |

| 86h     | TRISB      | PORTB I | Data Direction | on Regist | er    |       |       |       |       | 1111 1111                | 1111 1111                 |

| 81h     | OPTION_REG | RBPU    | INTEDG         | T0CS      | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                 |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

## 6.1 <u>Timer2 Operation</u>

The Timer2 output is also used by the CCP module to generate the PWM "On-Time", and the PWM period with a match with PR2.

The TMR2 register is readable and writable, and is cleared on any device reset.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The match output of TMR2 goes through a 4-bit post-scaler (which gives a 1:1 to 1:16 scaling) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

The prescaler and postscaler counters are cleared when any of the following occurs:

- · a write to the TMR2 register

- · a write to the T2CON register

- any device reset (Power-on Reset, MCLR reset, Watchdog Timer reset or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

## 6.2 <u>Timer2 Interrupt</u>

The Timer2 module has an 8-bit period register PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon reset.

### 6.3 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module, which optionally uses it to generate shift clock.

TABLE 6-1 REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Address | Name   | Bit 7       | Bit 6          | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|--------|-------------|----------------|---------|---------|---------|--------|---------|---------|-------------------------|---------------------------------|

| 0Bh,8Bh | INTCON | GIE         | PEIE           | TOIE    | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x               | 0000 000u                       |

| 0Ch     | PIR1   | _           | ADIF           | -       | -       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | -00- 0000               | 0000 0000                       |

| 8Ch     | PIE1   | _           | ADIE           | _       | _       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | -0 0000                 | 0000 0000                       |

| 11h     | TMR2   | Timer2 mod  | dule's registe | r       |         |         |        |         |         | 0000 0000               | 0000 0000                       |

| 12h     | T2CON  | _           | TOUTPS3        | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000               | -000 0000                       |

| 92h     | PR2    | Timer2 Peri | od Register    |         |         |         |        |         |         | 1111 1111               | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

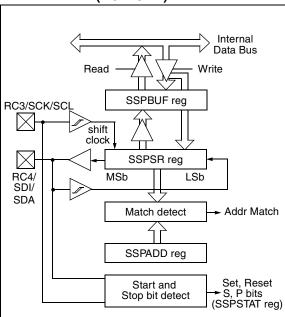

## 8.3 SSP I<sup>2</sup>C Operation

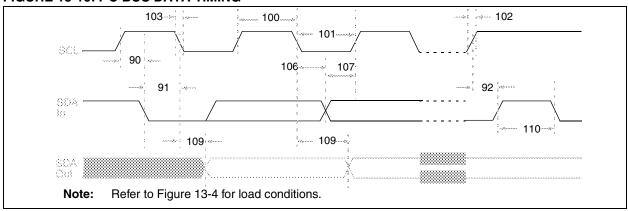

The SSP module in I<sup>2</sup>C mode fully implements all slave functions, except general call support, and provides interrupts on start and stop bits in hardware to support firmware implementations of the master functions. The SSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RC3/SCK/SCL pin, which is the clock (SCL), and the RC4/SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

The SSP module functions are enabled by setting SSP Enable bit SSPEN (SSPCON<5>).

FIGURE 8-2: SSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

The SSP module has five registers for  $I^2C$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the I<sup>2</sup>C operation. Four mode selection bits (SSPCON<3:0>) allow one of the following I<sup>2</sup>C modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with start and stop bit interrupts enabled for firmware master mode support

- I<sup>2</sup>C Slave mode (10-bit address), with start and stop bit interrupts enabled for firmware master mode support

- I<sup>2</sup>C start and stop bit interrupts enabled for firmware master mode support, slave mode idle

Selection of any  $I^2C$  mode, with the SSPEN bit set, forces the SCL and SDA pins to be operated as open drain outputs, provided these pins are programmed to inputs by setting the appropriate TRISC bits.

Additional information on SSP  $I^2C$  operation may be found in the  $PIC^{\textcircled{\tiny{B}}}$  MCU Mid-Range Reference Manual, (DS33023).

#### 8.3.1 SLAVE MODE

In slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched or the data transfer after an address match is received, the hardware automatically will generate the acknowledge ( $\overline{ACK}$ ) pulse, and load the SSPBUF register with the received value in the SSPSR register.

There are certain conditions that will cause the SSP module not to give this  $\overline{ACK}$  pulse. This happens if either of the following conditions occur:

- a) The buffer full bit BF (SSPSTAT<0>) was set before the transfer was completed.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was completed.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. Table 8-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the I<sup>2</sup>C specification, as well as the requirement of the SSP module, is shown in timing parameter #100, THIGH, and parameter #101, TLOW.

## 12.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- · Integrated Development Environment

- MPLAB™ IDE Software

- Assemblers/Compilers/Linkers

- MPASM Assembler

- MPLAB-C17 and MPLAB-C18 C Compilers

- MPLINK/MPLIB Linker/Librarian

- Simulators

- MPLAB-SIM Software Simulator

- Emulators

- MPLAB-ICE Real-Time In-Circuit Emulator

- PICMASTER®/PICMASTER-CE In-Circuit Emulator

- ICEPIC™

- · In-Circuit Debugger

- MPLAB-ICD for PIC16F877

- · Device Programmers

- PRO MATE® II Universal Programmer

- PICSTART® Plus Entry-Level Prototype Programmer

- · Low-Cost Demonstration Boards

- SIMICE

- PICDEM-1

- PICDEM-2

- PICDEM-3

- PICDEM-17

- SEEVAL®

- KEELOQ®

## 12.1 <u>MPLAB Integrated Development</u> Environment Software

- The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a Windows®-based application which contains:

- Multiple functionality

- editor

- simulator

- programmer (sold separately)

- emulator (sold separately)

- A full featured editor

- A project manager

- · Customizable tool bar and key mapping

- · A status bar

- On-line help

MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU tools (automatically updates all project information)

- · Debug using:

- source files

- absolute listing file

- object code

The ability to use MPLAB with Microchip's simulator, MPLAB-SIM, allows a consistent platform and the ability to easily switch from the cost-effective simulator to the full featured emulator with minimal retraining.

## 12.2 MPASM Assembler

MPASM is a full featured universal macro assembler for all PIC MCUs. It can produce absolute code directly in the form of HEX files for device programmers, or it can generate relocatable objects for MPLINK.

MPASM has a command line interface and a Windows shell and can be used as a standalone application on a Windows 3.x or greater system. MPASM generates relocatable object files, Intel standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file which contains source lines and generated machine code, and a COD file for MPLAB debugging.

MPASM features include:

- MPASM and MPLINK are integrated into MPLAB projects.

- MPASM allows user defined macros to be created for streamlined assembly.

- MPASM allows conditional assembly for multi purpose source files.

- MPASM directives allow complete control over the assembly process.

# 12.3 MPLAB-C17 and MPLAB-C18 C Compilers

The MPLAB-C17 and MPLAB-C18 Code Development Systems are complete ANSI 'C' compilers and integrated development environments for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

#### 12.4 MPLINK/MPLIB Linker/Librarian

MPLINK is a relocatable linker for MPASM and MPLAB-C17 and MPLAB-C18. It can link relocatable objects from assembly or C source files along with precompiled libraries using directives from a linker script.

and test the sample code. In addition, PICDEM-17 supports down-loading of programs to and executing out of external FLASH memory on board. The PICDEM-17 is also usable with the MPLAB-ICE or PICMASTER emulator, and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

## 12.17 <u>SEEVAL Evaluation and Programming</u> <u>System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials™ and secure serials. The Total Endurance™ Disk is included to aid in trade-off analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

## 12.18 <u>KEELog Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

**TABLE 12-1: DEVELOPMENT TOOLS FROM MICROCHIP**

|   | ∠ bic12CX)  | ✓ bIC14000 | ✓ biC1eC2) | ✓ PIC16C6X | FIC16CXX    | <ul> <li>✓ biC16F62</li> </ul> | (ZO91Old > | ✓ PIC16C7X | V PIC16C8X | ✓ biC16F8X3 | > bic1ec6XX | ✓  ✓       blc17C4X | CXTOTION > | ← BIC18CXXS  ← BIC18CXXS | 59CXX\ | нсеххх | WCBFXXX | WCb5210 |

|---|-------------|------------|------------|------------|-------------|--------------------------------|------------|------------|------------|-------------|-------------|---------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|---------|---------|

|   | <u> </u>    | >          | >          | >          | >           | >                              | >          | >          | >          | >           | >           | >                   | >          | > >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | >      | >      |         |         |

|   | <b>&gt;</b> | ` `        | >          | >          | >           | **>                            | >          | >          | >          | >           | >           | >                   | >          | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |        |         |         |

|   | >           | `          | >          | `          | >           |                                | ^          | >          | >          |             | >           | >                   | >          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        |         |         |

|   | ` <u>`</u>  |            | >          | >          | >           |                                | ^          | >          | >          |             | >           |                     |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        |         |         |

|   |             |            |            | *          |             |                                | *>         |            |            | >           |             |                     |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        |         |         |

|   | `           | `          | >          | >          | `           | **/                            | `          | >          | >          | >           | >           | >                   | >          | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |        |         |         |

|   | `           | `          | >          | >          | <i>&gt;</i> | **                             | >          | >          | <b>,</b>   | >           | >           | >                   | >          | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | >      | >      |         |         |

|   | ^           |            | >          |            |             |                                |            |            |            |             |             |                     |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        |         |         |

|   |             |            | ^          |            | ^           |                                | <b>√</b>   |            | >          |             |             | ^                   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        |         |         |

|   |             |            |            | ✓t         |             |                                | √t         |            |            |             |             |                     |            | ^                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |        |         |         |

|   |             |            |            |            |             |                                |            |            |            |             | >           |                     |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        |         |         |

|   |             | ^          |            |            |             |                                |            |            |            |             |             |                     |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        |         |         |

|   |             |            |            |            |             |                                |            |            |            |             |             |                     | >          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        |         |         |

|   |             |            |            |            |             |                                |            |            |            |             |             |                     |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | ^      |         |         |

|   |             |            |            |            |             |                                |            |            |            |             |             |                     |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | ^      |         |         |

|   |             |            |            |            |             |                                |            |            |            |             |             |                     |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        | >       |         |

|   |             |            |            |            |             |                                |            |            |            |             |             |                     |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        | >       |         |

|   |             |            |            |            |             |                                |            |            |            |             |             |                     |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        | ^       |         |

| 1 |             |            |            |            |             |                                |            |            |            |             |             |                     |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        | `       |         |

|   |             |            |            |            |             |                                |            |            |            |             |             |                     |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        |         | >       |

\*\* Contact Microchip Technology Inc. for availability date.

† Development tool is available on select devices.

## 13.0 ELECTRICAL CHARACTERISTICS

## Absolute Maximum Ratings (†)

| Ambient temperature under bias                                     | 55°C to +125°C       |

|--------------------------------------------------------------------|----------------------|

| Storage temperature                                                | 65°C to +150°C       |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4) | 0.3V to (VDD + 0.3V) |

| Voltage on VDD with respect to Vss                                 | 0.3V to +7.5V        |

| Voltage on MCLR with respect to Vss (Note 2)                       | 0V to +13.25V        |

| Voltage on RA4 with respect to Vss                                 | 0V to +8.5V          |

| Total power dissipation (Note 1)                                   | 1.0W                 |

| Maximum current out of Vss pin                                     | 300 mA               |

| Maximum current into VDD pin                                       |                      |

| Input clamp current, IIK (VI < 0 or VI > VDD)                      | ±20 mA               |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                     | ±20 mA               |

| Maximum output current sunk by any I/O pin                         | 25 mA                |

| Maximum output current sourced by any I/O pin                      | 25 mA                |

| Maximum current sunk by PORTA and PORTB (combined)                 | 200 mA               |

| Maximum current sourced by PORTA and PORTB (combined)              | 200 mA               |

| Maximum current sunk by PORTC                                      | 200 mA               |

| Maximum current sourced by PORTC                                   | 200 mA               |

**Note 1:** Power dissipation is calculated as follows: Pdis = VDD x {IDD -  $\sum$  IOH} +  $\sum$  {(VDD-VOH) x IOH} +  $\sum$ (VOI x IOL)

2: Voltage spikes below Vss at the  $\overline{\text{MCLR}/\text{VPP}}$  pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100 $\Omega$  should be used when applying a "low" level to the  $\overline{\text{MCLR}/\text{VPP}}$  pin, rather than pulling this pin directly to Vss.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.