Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                 |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc62b-04i-ml |

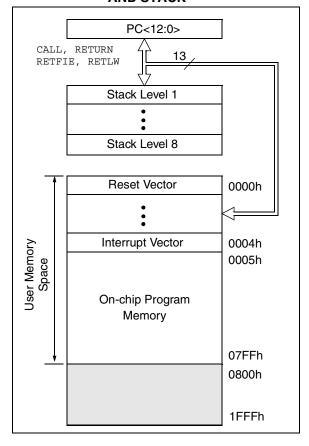

### 2.0 MEMORY ORGANIZATION

There are two memory blocks in each of these microcontrollers. Each block (Program Memory and Data Memory) has its own bus, so that concurrent access can occur.

Additional information on device memory may be found in the  $PICmicro^{TM}$  Mid-Range Reference Manual, (DS33023).

## 2.1 <u>Program Memory Organization</u>

The PIC16C62B/72A devices have a 13-bit program counter capable of addressing an 8K  $\times$  14 program memory space. Each device has 2K  $\times$  14 words of program memory. Accessing a location above 07FFh will cause a wraparound.

The reset vector is at 0000h and the interrupt vector is at 0004h.

FIGURE 2-1: PROGRAM MEMORY MAP AND STACK

#### 2.2.2.1 STATUS REGISTER

The STATUS register, shown in Register 2-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, the write to these three bits is disabled. These bits are set or cleared according to the device logic. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are not writable. The result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

- **Note 1:** The IRP and RP1 bits are reserved. Maintain these bits clear to ensure upward compatibility with future products.

- Note 2: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions.

#### REGISTER 2-1: STATUS REGISTER (ADDRESS 03h, 83h)

| R/W-0    | R/W-0                               | R/W-0                                                               | R-1               | R-1         | R/W-x                                          | R/W-x        | R/W-x |                                                                              |

|----------|-------------------------------------|---------------------------------------------------------------------|-------------------|-------------|------------------------------------------------|--------------|-------|------------------------------------------------------------------------------|

| IRP      | RP1                                 | RP0                                                                 | TO                | PD          | Z                                              | DC           | С     | R = Readable bit                                                             |

| bit7     |                                     |                                                                     |                   |             |                                                |              | bit0  | W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset |

| oit 7:   |                                     | ster Bank S<br>maintain c                                           |                   | (used for i | ndirect add                                    | ressing)     |       |                                                                              |

| bit 6-5: | 01 = Bank<br>00 = Bank<br>Each bank | Register E<br>1 (80h - F<br>0 (00h - 7<br>is 128 byt<br>1 is reserv | Fh)<br>Fh)<br>tes | ·           | ed for direc                                   | t addressin  | g)    |                                                                              |

| bit 4:   |                                     |                                                                     |                   | struction,  | or SLEEP i                                     | nstruction   |       |                                                                              |

| bit 3:   |                                     | r-down bit<br>power-up o<br>ecution of t                            | •                 |             |                                                |              |       |                                                                              |

| bit 2:   |                                     | sult of an a                                                        |                   |             | peration is peration is                        |              |       |                                                                              |

| bit 1:   | 1 = A carr                          | y-out from                                                          | the 4th lo        | w order bi  | W, SUBLW, S<br>it of the resi<br>bit of the re | ult occurred |       | r borrow, the polarity is reverse                                            |

| bit 0:   | 1 = A carr                          | y-out from                                                          | the most          | significant | BLW, SUBWF<br>t bit of the rent bit of the     | esult occur  | red   | ow, the polarity is reversed)                                                |

|          |                                     | erand. For                                                          |                   |             |                                                |              |       | ding the two's complement of the either the high or low order bit            |

### 2.2.2.2 OPTION\_REG REGISTER

The OPTION\_REG register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known as the prescaler), the External INT Interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

## REGISTER 2-2: OPTION\_REG REGISTER (ADDRESS 81h)

| R/W-1    | R/W-1                                                                                                                | R/W-1            | R/W-1      | R/W-1      | R/W-1                  | R/W-1 | R/W-1 |                  |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------|------------------|------------|------------|------------------------|-------|-------|------------------|--|--|

| RBPU     | INTEDG                                                                                                               | T0CS             | T0SE       | PSA        | PS2                    | PS1   | PS0   | R = Readable bit |  |  |

| bit7     | bit0 W = Writable bit<br>- n = Value at POR reset                                                                    |                  |            |            |                        |       |       |                  |  |  |

| bit 7:   | RBPU: PORTB Pull-up Enable bit  1 = PORTB pull-ups are disabled  0 = PORTB pull-ups are enabled for all PORTB inputs |                  |            |            |                        |       |       |                  |  |  |

| bit 6:   | INTEDG: Interru<br>1 = Interru<br>0 = Interru                                                                        | pt on risir      | ng edge o  | f RB0/INT  | •                      |       |       |                  |  |  |

| bit 5:   | TOCS: TMI  1 = Transit  0 = Interna                                                                                  | ion on R         | A4/T0CKI   | pin        | (OUT)                  |       |       |                  |  |  |

| bit 4:   |                                                                                                                      | ent on hi        | gh-to-low  | transition | on RA4/T0<br>on RA4/T0 |       |       |                  |  |  |

| bit 3:   | PSA: Prescaler Assignment bit  1 = Prescaler is assigned to the WDT  0 = Prescaler is assigned to the Timer0 module  |                  |            |            |                        |       |       |                  |  |  |

| bit 2-0: | PS2:PS0:                                                                                                             | Prescale         | r Rate Sel | lect bits  |                        |       |       |                  |  |  |

|          | Bit Value                                                                                                            | TMR0 R           | ate WD     | ΓRate      |                        |       |       |                  |  |  |

|          | 000                                                                                                                  | 1:2<br>1:4       | 1:         |            |                        |       |       |                  |  |  |

|          | 010                                                                                                                  | 1:8              |            | : 4        |                        |       |       |                  |  |  |

|          | 011<br>100                                                                                                           | 011              |            |            |                        |       |       |                  |  |  |

|          | 100                                                                                                                  | 1 : 32<br>1 : 64 | -          | : 32       |                        |       |       |                  |  |  |

|          | 110                                                                                                                  | 1:12             |            | : 64       |                        |       |       |                  |  |  |

|          | 111                                                                                                                  | 1:25             | 6 1        | : 128      |                        |       |       |                  |  |  |

|          |                                                                                                                      |                  |            |            |                        |       |       |                  |  |  |

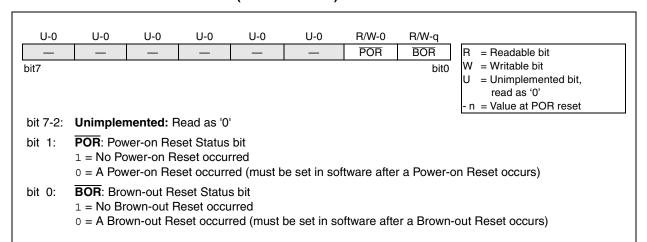

#### 2.2.2.6 PCON REGISTER

The Power Control register (PCON) contains flag bits to allow differentiation between a Power-on Reset (POR), Brown-Out Reset (BOR) and resets from other sources. .

Note: On Power-on Reset, the state of the BOR bit is unknown and is not predictable.

If the BODEN bit in the configuration word is set, the user must first set the BOR bit on a POR, and check it on subsequent resets.

If BOR is cleared while POR remains set, a Brown-out reset has occurred.

If the BODEN bit is clear, the BOR bit may be ignored.

### REGISTER 2-6: PCON REGISTER (ADDRESS 8Eh)

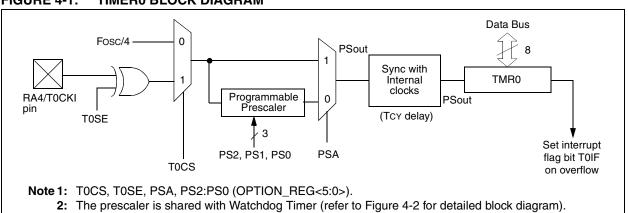

#### 4.0 TIMERO MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Read and write

- INT on overflow

- · 8-bit software programmable prescaler

- · INT or EXT clock select

- EXT clock edge select

Figure 4-1 is a simplified block diagram of the Timer0 module.

Additional information on timer modules is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

### 4.1 <u>Timer0 Operation</u>

Timer0 can operate as a timer or as a counter.

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed below.

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization. Additional information on external clock requirements is available in the Electrical Specifications section of this manual, and in the PIC® MCU Mid-Range Reference Manual, (DS33023).

#### 4.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 4-2). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. There is only one prescaler available which is shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The prescaler is not readable or writable.

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

Clearing bit PSA will assign the prescaler to the Timer0 module. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable.

Setting bit PSA will assign the prescaler to the Watchdog Timer (WDT). When the prescaler is assigned to the WDT, prescale values of 1:1, 1:2, ..., 1:128 are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

**Note:** Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment or ratio.

FIGURE 4-1: TIMERO BLOCK DIAGRAM

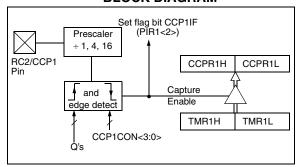

# 7.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The CCP (Capture/Compare/PWM) module contains a 16-bit register, which can operate as a 16-bit capture register, as a 16-bit compare register or as a PWM master/slave duty cycle register. Table 7-1 shows the timer resources of the CCP module modes.

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

Additional information on the CCP module is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

TABLE 7-1 CCP MODE - TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

#### TABLE 7-2 INTERACTION OF TWO CCP MODULES

| CCPx Mode | <b>CCPy Mode</b> | Interaction                                                                           |

|-----------|------------------|---------------------------------------------------------------------------------------|

| Capture   | Capture          | Same TMR1 time-base.                                                                  |

| Capture   | Compare          | The compare should be configured for the special event trigger, which clears TMR1.    |

| Compare   | Compare          | The compare(s) should be configured for the special event trigger, which clears TMR1. |

| PWM       | PWM              | The PWMs will have the same frequency and update rate (TMR2 interrupt).               |

| PWM       | Capture          | None.                                                                                 |

| PWM       | Compare          | None.                                                                                 |

## **REGISTER 7-1:CCP1CON REGISTER (ADDRESS 17h)**

| U-0  | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |                                                                              |

|------|-----|-------|-------|--------|--------|--------|--------|------------------------------------------------------------------------------|

| _    | _   | CCP1X | CCP1Y | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 | R = Readable bit                                                             |

| bit7 |     |       |       |        |        |        | bit0   | W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset |

bit 7-6: Unimplemented: Read as '0'

bit 5-4: CCP1X:CCP1Y: PWM Least Significant bits

Capture Mode: Unused Compare Mode: Unused

PWM Mode: These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPR1L.

bit 3-0: CCP1M3:CCP1M0: CCP1 Mode Select bits

0000 = Capture/Compare/PWM off (resets CCP1 module)

0100 = Capture mode, every falling edge

0101 = Capture mode, every rising edge

0110 = Capture mode, every 4th rising edge

0111 = Capture mode, every 16th rising edge

1000 = Compare mode, set output on match (CCP1IF bit is set)

1001 = Compare mode, clear output on match (CCP1IF bit is set)

1010 = Compare mode, generate software interrupt on match (CCP1IF bit is set, CCP1 pin is unaffected)

1011 = Compare mode, trigger special event (CCP1IF bit is set; CCP1 resets TMR1 and starts an A/D conversion (if A/D module is enabled))

11xx = PWM mode

#### 7.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register, when an event occurs on pin RC2/CCP1. An event is defined as:

- every falling edge

- · every rising edge

- · every 4th rising edge

- · every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit ,CCP1IF (PIR1<2>), is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

# FIGURE 7-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 7.1.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

**Note:** If the RC2/CCP1 is configured as an output, a write to the port can cause a capture condition.

#### 7.1.2 TIMER1 MODE SELECTION

Timer1 must be running in timer mode or synchronized counter mode for the CCP module to use the capture feature. In asynchronous counter mode, the capture operation may not work consistently.

#### 7.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should clear CCP1IE (PIE1<2>) before changing the capture mode to avoid false interrupts. Clear the interrupt flag bit, CCP1IE before setting CCP1IE.

#### 7.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in capture mode, the prescaler counter is cleared. This means that any reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 7-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

# EXAMPLE 7-1: CHANGING BETWEEN CAPTURE PRESCALERS

```

CLRF CCP1CON ;Turn CCP module off

MOVLW NEW_CAPT_PS ;Load the W reg with

; the new prescaler

; mode value and CCP ON

MOVWF CCP1CON ;Load CCP1CON with this

; value

```

**NOTES:**

#### 8.3.2 MASTER OPERATION

Master operation is supported in firmware using interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared by a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the I<sup>2</sup>C bus may be taken when the P bit is set, or the bus is idle and both the S and P bits are clear.

In master operation, the SCL and SDA lines are manipulated in software by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt if enabled):

- · START condition

- · STOP condition

- · Byte transfer completed

Master operation can be done with either the slave mode idle (SSPM3:SSPM0 = 1011) or with the slave active. When both master operation and slave modes are used, the software needs to differentiate the source(s) of the interrupt.

For more information on master operation, see *AN554* - *Software Implementation of I<sup>2</sup>C Bus Master.*

#### 8.3.3 MULTI-MASTER OPERATION

In multi-master operation, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the I<sup>2</sup>C bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle and both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In multi-master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost, these are:

- · Address Transfer

- · Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed, an  $\overline{ACK}$  pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to re-transfer the data at a later time.

For more information on master operation, see *AN578* - *Use of the SSP Module in the of I<sup>2</sup>C Multi-Master Environment.*

TABLE 8-3 REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

| Address  | Name    | Bit 7                                                            | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1     | Bit 0     | Value on<br>POR,<br>BOR | Value on<br>all other<br>resets |

|----------|---------|------------------------------------------------------------------|-------------------------------|-------|-------|-------|--------|-----------|-----------|-------------------------|---------------------------------|

| 0Bh, 8Bh | INTCON  | GIE                                                              | PEIE                          | TOIE  | INTE  | RBIE  | TOIF   | INTF      | RBIF      | 0000 000x               | 0000 000u                       |

| 0Ch      | PIR1    | _                                                                | ADIF                          | _     | _     | SSPIF | CCP1IF | TMR2IF    | TMR1IF    | -0 0000                 | -0 0000                         |

| 8Ch      | PIE1    | _                                                                | ADIE                          | _     | _     | SSPIE | CCP1IE | TMR2IE    | TMR1IE    | -0 0000                 | -0 0000                         |

| 13h      | SSPBUF  | Synchronous Serial Port Receive Buffer/Transmit Register         |                               |       |       |       |        |           |           | xxxx xxxx               | uuuu uuuu                       |

| 93h      | SSPADD  | Synchronous Serial Port (I <sup>2</sup> C mode) Address Register |                               |       |       |       |        | 0000 0000 | 0000 0000 |                         |                                 |

| 14h      | SSPCON  | WCOL                                                             | SSPOV                         | SSPEN | CKP   | SSPM3 | SSPM2  | SSPM1     | SSPM0     | 0000 0000               | 0000 0000                       |

| 94h      | SSPSTAT | SMP <sup>(1)</sup>                                               | CKE <sup>(1)</sup>            | D/A   | Р     | S     | R/W    | UA        | BF        | 0000 0000               | 0000 0000                       |

| 87h      | TRISC   | PORTC Dat                                                        | PORTC Data Direction register |       |       |       |        |           |           | 1111 1111               | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in SPI mode.

Note 1: Maintain these bits clear in I<sup>2</sup>C mode.

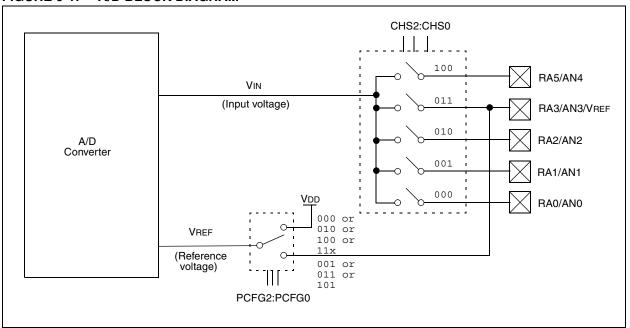

When the A/D conversion is complete, the result is loaded into the ADRES register, the GO/DONE bit, ADCON0<2>, is cleared, and the A/D interrupt flag bit, ADIF, is set. The block diagram of the A/D module is shown in Figure 9-1.

The value that is in the ADRES register is not modified for a Power-on Reset. The ADRES register will contain unknown data after a Power-on Reset.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see Section 9.1. After this acquisition time has elapsed, the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins / voltage reference / and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- · Clear ADIF bit

- · Set ADIE bit

- · Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:

- Polling for the GO/DONE bit to be cleared OR

- · Waiting for the A/D interrupt

- Read A/D Result register (ADRES), clear bit ADIF if required.

- 7. For next conversion, go to step 1 or step 2 as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2TAD is required before next acquisition starts.

FIGURE 9-1: A/D BLOCK DIAGRAM

### 11.0 INSTRUCTION SET SUMMARY

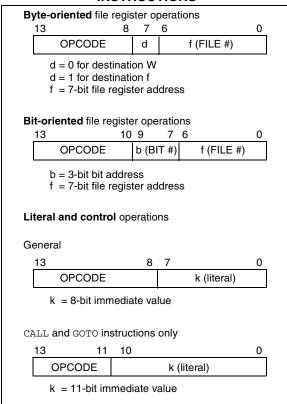

Each PIC16CXXX instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16CXX instruction set summary in Table 11-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 11-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

TABLE 11-1 OPCODE FIELD DESCRIPTIONS

| Field                 | Description                                                                                                                                                        |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f                     | Register file address (0x00 to 0x7F)                                                                                                                               |

| W                     | Working register (accumulator)                                                                                                                                     |

| b                     | Bit address within an 8-bit file register                                                                                                                          |

| k                     | Literal field, constant data or label                                                                                                                              |

| x                     | Don't care location (= 0 or 1) The assembler will generate code with x = 0. It is the recommended form of use for compatibility with all Microchip software tools. |

| d                     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                       |

| PC                    | Program Counter                                                                                                                                                    |

| TO                    | Time-out bit                                                                                                                                                       |

| $\overline{	ext{PD}}$ | Power-down bit                                                                                                                                                     |

| Z                     | Zero bit                                                                                                                                                           |

| DC                    | Digit Carry bit                                                                                                                                                    |

| С                     | Carry bit                                                                                                                                                          |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- · Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction

execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 11-2 lists the instructions recognized by the MPASM assembler.

Figure 11-1 shows the general formats that the instructions can have.

Note: To maintain upward compatibility with future PIC16CXXX products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

# FIGURE 11-1: GENERAL FORMAT FOR INSTRUCTIONS

A description of each instruction is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

# 11.1 <u>Instruction Descriptions</u>

| ADDLW            | Add Literal and W                                                                                                 |

|------------------|-------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDLW k                                                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                                               |

| Operation:       | $(W) + k \rightarrow (W)$                                                                                         |

| Status Affected: | C, DC, Z                                                                                                          |

| Description:     | The contents of the W register are added to the eight bit literal 'k' and the result is placed in the W register. |

| ANDWF            | AND W with f                                                                                                                                       |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDWF f,d                                                                                                                                  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                 |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                          |

| Status Affected: | Z                                                                                                                                                  |

| Description:     | AND the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| ADDWF            | Add W and f                                                                                                                                                        |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                 |

| Operation:       | $(W) + (f) \rightarrow (destination)$                                                                                                                              |

| Status Affected: | C, DC, Z                                                                                                                                                           |

| Description:     | Add the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label] BCF f,b                                                     |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ANDLW            | AND Literal with W                                                                                            |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                      |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                           |  |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                               |  |  |  |  |

| Status Affected: | Z                                                                                                             |  |  |  |  |

| Description:     | The contents of W register are AND'ed with the eight bit literal 'k'. The result is placed in the W register. |  |  |  |  |

| BSF              | Bit Set f                            |

|------------------|--------------------------------------|

| Syntax:          | [label] BSF f,b                      |

| Operands:        | $0 \le f \le 127$<br>$0 \le b \le 7$ |

| Operation:       | $1 \rightarrow (f < b >)$            |

| Status Affected: | None                                 |

| Description:     | Bit 'b' in register 'f' is set.      |

|                  |                                      |

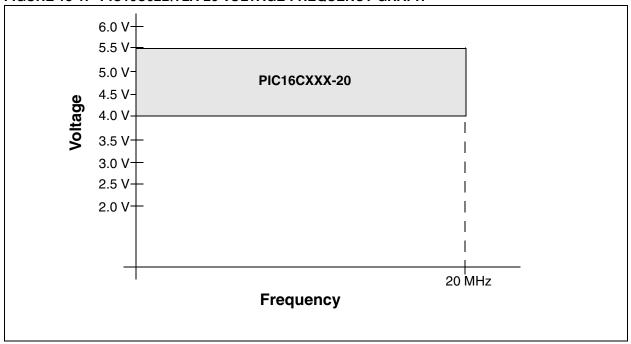

FIGURE 13-1: PIC16C62B/72A-20 VOLTAGE-FREQUENCY GRAPH

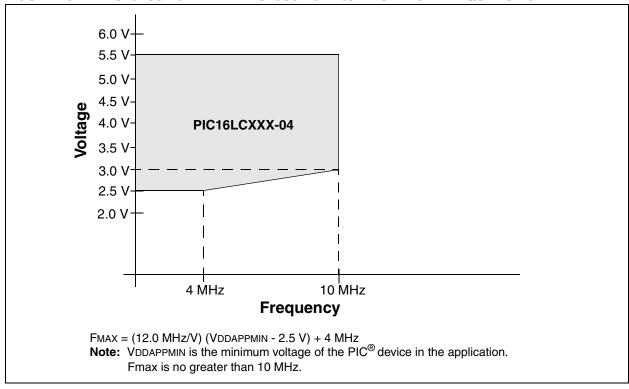

FIGURE 13-2: PIC16LC62B/72A AND PIC16C62B/72A/JW VOLTAGE-FREQUENCY GRAPH

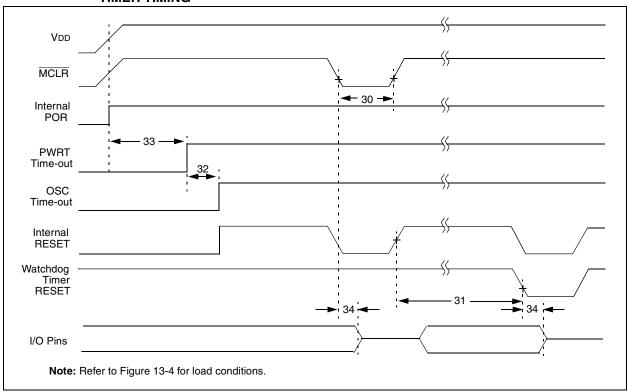

FIGURE 13-7: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

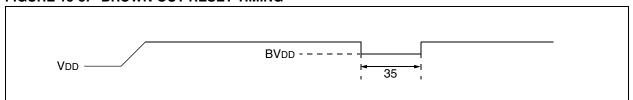

FIGURE 13-8: BROWN-OUT RESET TIMING

TABLE 13-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER AND BROWN-OUT RESET REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                                 | Min | Typ†         | Max | Units | Conditions                                         |

|--------------|-------|------------------------------------------------|-----|--------------|-----|-------|----------------------------------------------------|

| 30           | TmcL  | MCLR Pulse Width (low)                         | 2   | _            | _   | μS    | VDD = 5V, -40°C to +125°C                          |

| 31*          | Twdt  | Watchdog Timer Time-out Period (No Prescaler)  | 7   | 18           | 33  | ms    | VDD = 5V, -40°C to +125°C                          |

| 32           | Tost  | Oscillator Start-up Timer Period               | _   | 1024<br>Tosc | _   | _     | Tosc = OSC1 period                                 |

| 33*          | Tpwrt | Power-up Timer Period                          | 28  | 72           | 132 | ms    | $VDD = 5V, -40^{\circ}C \text{ to } +125^{\circ}C$ |

| 34           | Tıoz  | I/O Hi-impedance from MCLR<br>Low or WDT reset | _   | _            | 2.1 | μS    |                                                    |

| 35           | Твоп  | Brown-out Reset Pulse Width                    | 100 | _            | _   | μS    | VDD ≤ BVDD (D005)                                  |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

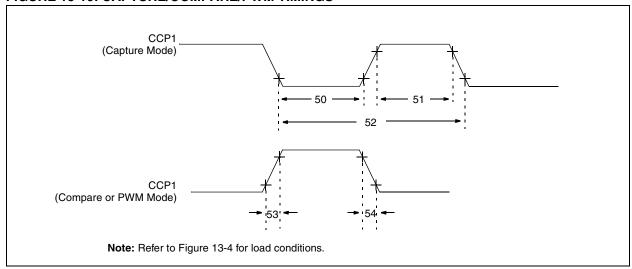

## FIGURE 13-10: CAPTURE/COMPARE/PWM TIMINGS

TABLE 13-6: CAPTURE/COMPARE/PWM REQUIREMENTS

| Param<br>No. | Sym                           |                          | Characteristi  | С         | Min            | Тур† | Max | Units | Conditions                         |

|--------------|-------------------------------|--------------------------|----------------|-----------|----------------|------|-----|-------|------------------------------------|

| 50*          | TccL                          | CCP1 input low           | No Prescaler   |           | 0.5Tcy + 20    | _    | _   | ns    |                                    |

|              |                               | time                     | With Prescaler | PIC16CXX  | 10             | _    | _   | ns    |                                    |

|              |                               |                          |                | PIC16LCXX | 20             | _    | _   | ns    |                                    |

| 51* TccH     | TccH                          | CCH CCP1 input high time | No Prescaler   |           | 0.5Tcy + 20    | _    | _   | ns    |                                    |

|              |                               |                          | With Prescaler | PIC16CXX  | 10             | _    | _   | ns    |                                    |

|              |                               |                          |                | PIC16LCXX | 20             | _    | _   | ns    |                                    |

| 52*          | TccP                          | CCP1 input period        |                |           | 3Tcy + 40<br>N | _    | _   | ns    | N = prescale<br>value (1,4, or 16) |

| 53*          | TccR                          | CCP1 output rise         | time           | PIC16CXX  | _              | 10   | 25  | ns    |                                    |

|              |                               |                          |                | PIC16LCXX | _              | 25   | 45  | ns    |                                    |

| 54*          | 4* TccF CCP1 output fall time |                          | PIC16CXX       | _         | 10             | 25   | ns  |       |                                    |

|              |                               |                          |                | PIC16LCXX | _              | 25   | 45  | ns    |                                    |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

TABLE 13-13: A/D CONVERTER CHARACTERISTICS:

PIC16C72A-04 (COMMERCIAL, INDUSTRIAL, EXTENDED) PIC16C72A-20 (COMMERCIAL, INDUSTRIAL, EXTENDED) PIC16LC72A-04 (COMMERCIAL, INDUSTRIAL)

| Param<br>No. | Sym                                  | Characte                                 | ristic    | Min       | Тур†                   | Max        | Units                                                                                                                        | Conditions                                                                                                                   |

|--------------|--------------------------------------|------------------------------------------|-----------|-----------|------------------------|------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| A01          | NR                                   | Resolution                               |           | _         | 8-bits                 | bit        | $VREF = VDD = 5.12V$ , $VSS \le VAIN \le VREF$                                                                               |                                                                                                                              |

| A02          | Eabs                                 | Total Absolute error                     | _         | _         | < ± 1                  | LSB        | $VREF = VDD = 5.12V$ , $VSS \le VAIN \le VREF$                                                                               |                                                                                                                              |

| A03          | EIL                                  | Integral linearity error                 |           | _         | _                      | < ± 1      | LSB                                                                                                                          | $\begin{aligned} & \text{VREF} = \text{VDD} = 5.12\text{V}, \\ & \text{VSS} \leq \text{VAIN} \leq \text{VREF} \end{aligned}$ |

| A04          | EDL                                  | Differential linearity e                 | rror      | _         | _                      | < ± 1      | LSB                                                                                                                          | $\begin{aligned} & \text{VREF} = \text{VDD} = 5.12\text{V}, \\ & \text{VSS} \leq \text{VAIN} \leq \text{VREF} \end{aligned}$ |

| A05          | EFS                                  | Full scale error                         |           | _         | < ± 1                  | LSB        | $\begin{aligned} & \text{VREF} = \text{VDD} = 5.12\text{V}, \\ & \text{VSS} \leq \text{VAIN} \leq \text{VREF} \end{aligned}$ |                                                                                                                              |

| A06          | Eoff                                 | Offset error                             |           | _         | _                      | < ± 1      | LSB                                                                                                                          | $\begin{aligned} & \text{VREF} = \text{VDD} = 5.12\text{V}, \\ & \text{VSS} \leq \text{VAIN} \leq \text{VREF} \end{aligned}$ |

| A10          | _                                    | Monotonicity                             |           | _         | guaranteed<br>(Note 3) | _          | _                                                                                                                            | $Vss \leq Vain \leq Vref$                                                                                                    |

| A20          | VREF                                 | Reference voltage                        |           | 2.5V      | _                      | VDD + 0.3  | V                                                                                                                            |                                                                                                                              |

| A25          | VAIN                                 | Analog input voltage                     |           | Vss - 0.3 | _                      | VREF + 0.3 | V                                                                                                                            |                                                                                                                              |

| A30          | ZAIN                                 | Recommended impe<br>analog voltage sourc |           | _         | _                      | 10.0       | kΩ                                                                                                                           |                                                                                                                              |

| A40          | IAD                                  | A/D conversion                           | PIC16CXX  | _         | 180                    | _          | μΑ                                                                                                                           | Average current con-                                                                                                         |

|              |                                      | current (VDD)                            | PIC16LCXX | _         | 90                     | ı          | μΑ                                                                                                                           | sumption when A/D is on. (Note 1)                                                                                            |

| A50          | A50 IREF VREF input current (Note 2) |                                          | 10        | _         | 1000                   | μА         | During VAIN acquisition. Based on differential of VHOLD to VAIN to charge CHOLD, see                                         |                                                                                                                              |

|              |                                      |                                          | _         | _         | 10                     | μΑ         | Section 9.1. During A/D conversion cycle                                                                                     |                                                                                                                              |

<sup>\*</sup> These parameters are characterized but not tested.

- **Note 1:** When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

- 2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

- 3: The A/D conversion result never decreases with an increase in the Input Voltage and has no missing codes.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**NOTES:**

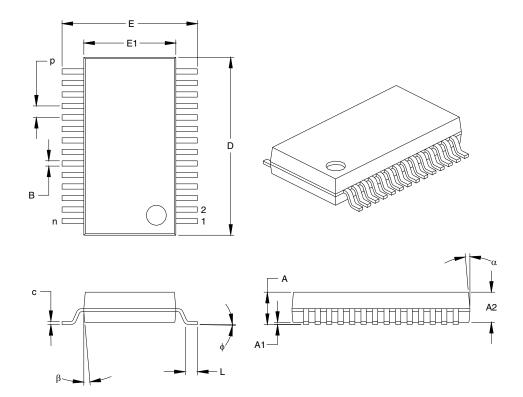

#### 28-Lead Plastic Shrink Small Outline (SS) - 209 mil, 5.30 mm (SSOP) 15.5

|                          | Units  |      | INCHES |      | N     | 1ILLIMETERS | S*     |

|--------------------------|--------|------|--------|------|-------|-------------|--------|

| Dimension                | Limits | MIN  | NOM    | MAX  | MIN   | NOM         | MAX    |

| Number of Pins           | n      |      | 28     |      |       | 28          |        |

| Pitch                    | р      |      | .026   |      |       | 0.66        |        |

| Overall Height           | Α      | .068 | .073   | .078 | 1.73  | 1.85        | 1.98   |

| Molded Package Thickness | A2     | .064 | .068   | .072 | 1.63  | 1.73        | 1.83   |

| Standoff                 | A1     | .002 | .006   | .010 | 0.05  | 0.15        | 0.25   |

| Overall Width            | E      | .299 | .309   | .319 | 7.59  | 7.85        | 8.10   |

| Molded Package Width     | E1     | .201 | .207   | .212 | 5.11  | 5.25        | 5.38   |

| Overall Length           | D      | .396 | .402   | .407 | 10.06 | 10.20       | 10.34  |

| Foot Length              | L      | .022 | .030   | .037 | 0.56  | 0.75        | 0.94   |

| Lead Thickness           | С      | .004 | .007   | .010 | 0.10  | 0.18        | 0.25   |

| Foot Angle               | ф      | 0    | 4      | 8    | 0.00  | 101.60      | 203.20 |

| Lead Width               | В      | .010 | .013   | .015 | 0.25  | 0.32        | 0.38   |

| Mold Draft Angle Top     | α      | 0    | 5      | 10   | 0     | 5           | 10     |

| Mold Draft Angle Bottom  | β      | 0    | 5      | 10   | 0     | 5           | 10     |

<sup>\*</sup>Controlling Parameter

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MS-150

Deputer No. 2014 2015

Drawing No. C04-073

# **APPENDIX A: REVISION HISTORY**

| Version | Date | Revision Description                                                                                                                                                                                         |

|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A       | 7/98 | This is a new data sheet. However, the devices described in this data sheet are the upgrades to the devices found in the <i>PIC16C6X Data Sheet</i> , DS30234, and the <i>PIC16C7X Data Sheet</i> , DS30390. |

# APPENDIX B: CONVERSION CONSIDERATIONS

Considerations for converting from previous versions of devices to the ones listed in this data sheet are listed in Table B-1.

## TABLE B-1: CONVERSION CONSIDERATIONS

| Difference    | PIC16C62A/72                                                         | PIC16C62B/72A    |

|---------------|----------------------------------------------------------------------|------------------|

| Voltage Range | 2.5V - 6.0V                                                          | 2.5V - 5.5V      |

| SSP module    | Basic SSP (2 mode SPI)                                               | SSP (4 mode SPI) |

| CCP module    | CCP does not reset TMR1 when in special event trigger mode.          | N/A              |

| Timer1 module | Writing to TMR1L register can cause over-<br>flow in TMR1H register. | N/A              |

| SSP                                     | .39 Tir          | mer1                                       | 27   |

|-----------------------------------------|------------------|--------------------------------------------|------|

| Enable (SSPIE Bit)                      |                  | Block Diagram                              |      |

| Flag (SSPIF Bit)                        |                  | Capacitor Selection                        |      |

| RA5/SS/AN4 Pin                          |                  | Clock Source Select (TMR1CS Bit)           |      |

| RC3/SCK/SCL Pin                         |                  | External Clock Input Sync (T1SYNC Bit)     |      |

| RC4/SDI/SDA Pin                         |                  | Module On/Off (TMR1ON Bit)                 |      |

| RC5/SDO Pin                             |                  | Oscillator27                               |      |

| SSPADD Register                         | . 10             | Oscillator Enable (T1OSCEN Bit)            | _    |

| SSPBUF Register                         |                  | Overflow Enable (TMR1IE Bit)               |      |

| SSPCON Register9,                       |                  | Overflow Flag (TMR1IF Bit)                 |      |

| SSPSTAT Register10,                     |                  | Overflow Interrupt27                       |      |

| TMR2 Output for Clock Shift             |                  | RC0/T1OSO/T1CKI Pin                        |      |

| Write Collision Detect (WCOL Bit)       |                  | RC1/T10SI                                  | 6    |

| SSPCON Register                         |                  | Special Event Trigger (CCP)29              | , 35 |

| CKP Bit                                 |                  | T1CON Register9                            |      |

| SSPEN Bit                               | . 47             | Timing Diagram                             | -    |

| SSPM3:SSPM0 Bits                        | . 47             | TMR1H Register                             | 9    |

| SSPOV Bit                               | . 47             | TMR1L Register                             |      |

| WCOL Bit                                | . 47 Tir         | mer2                                       |      |

| SSPSTAT Register                        | . 46             | Block Diagram                              | 32   |

| BF Bit                                  |                  | PR2 Register10, 31                         |      |

| CKE Bit                                 | .46              | SSP Clock Shift                            |      |

| D/A Bit                                 | .46              | T2CON Register9                            |      |

| P bit                                   |                  | TMR2 Register9                             |      |

| R/W Bit42, 43, 44,                      |                  | TMR2 to PR2 Match Enable (TMR2IE Bit)      | /    |

| S Bit                                   |                  | TMR2 to PR2 Match Flag (TMR2IF Bit)        |      |

| SMP Bit                                 |                  | TMR2 to PR2 Match Interrupt31, 32          |      |

| UA Bit                                  |                  | ming Diagrams                              | ,    |

| Stack                                   |                  | I <sup>2</sup> C Reception (7-bit Address) | 43   |

| STATUS Register                         |                  | Wake-up from SLEEP via Interrupt           |      |

| C Bit                                   |                  | ning Diagrams and Specifications           |      |

| DC Bit                                  |                  | A/D Conversion                             |      |

| IRP Bit                                 |                  | Brown-out Reset (BOR)                      |      |

| PD Bit                                  |                  | Capture/Compare/PWM (CCP)                  |      |

| RP1:RP0 Bits                            |                  | CLKOUT and I/O                             |      |

| TO Bit                                  |                  | External Clock                             |      |

| Z Bit                                   |                  | I <sup>2</sup> C Bus Data                  |      |

| _                                       |                  | I <sup>2</sup> C Bus Start/Stop Bits       |      |

| Т                                       |                  | Oscillator Start-up Timer (OST)            |      |

| T1CON Register9,                        | 27               | Power-up Timer (PWRT)                      |      |

| T1CKPS1:T1CKPS0 Bits                    |                  | Reset                                      |      |

| T10SCEN Bit                             | . 27             | Timer0 and Timer1                          |      |

| T1SYNC Bit                              | . 27             | Watchdog Timer (WDT)                       |      |

| TMR1CS Bit                              | .27              |                                            |      |

| TMR1ON Bit                              | <sub>.27</sub> W |                                            |      |

| T2CON Register9,                        | 31 W             | Register                                   | 63   |

| T2CKPS1:T2CKPS0 Bits                    |                  | ake-up from SLEEP55                        |      |

| TMR2ON Bit                              | .31              | Interrupts60                               | , 61 |

| TOUTPS3:TOUTPS0 Bits                    | .31              | MCLR Reset                                 |      |

| Timer0                                  | . 25             | Timing Diagram                             | 66   |

| Block Diagram                           | . 25             | WDT Reset                                  |      |

| Clock Source Edge Select (T0SE Bit) 12, |                  | atchdog Timer (WDT)55                      | , 64 |

| Clock Source Select (T0CS Bit)12,       |                  | Block Diagram                              |      |

| Overflow Enable (T0IE Bit)              |                  | Enable (WDTE Bit)55                        |      |

| Overflow Flag (T0IF Bit)                |                  | Programming Considerations                 |      |

| Overflow Interrupt                      |                  | RC Oscillator                              |      |

| RA4/T0CKI Pin, External Clock           |                  | Timing Diagram                             |      |

| Timing Diagram                          |                  | WDT Reset, Normal Operation57, 60          |      |

| TMR0 Register                           |                  | WDT Reset, SLEEP57, 60                     |      |

| <u> </u>                                |                  | WW, On-Line Support                        | -    |

|                                         |                  | • •                                        |      |