Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | ОТР                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                 |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc62b-04i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table of Contents

| 1.0  | Device Overview                                       | F     |

|------|-------------------------------------------------------|-------|

|      | Memory Organization                                   |       |

|      |                                                       |       |

|      | I/O Ports                                             |       |

| 4.0  | Timer0 Module                                         |       |

|      | Timer1 Module                                         |       |

| 6.0  | Timer2 Module                                         | 31    |

| 7.0  | Capture/Compare/PWM (CCP) Module                      | 33    |

|      | Synchronous Serial Port (SSP) Module                  |       |

| 9.0  | Analog-to-Digital Converter (A/D) Module              | 49    |

| 10.0 | Special Features of the CPU                           | 55    |

| 11.0 | Instruction Set Summary                               | 67    |

| 12.0 | Development Support                                   | 75    |

| 13.0 | Electrical Characteristics                            | 81    |

| 14.0 | DC and AC Characteristics Graphs and Tables           | . 103 |

| 15.0 | Packaging Information                                 | . 105 |

| Appe | ndix A. Revision History                              | . 111 |

|      | ndix B: Conversion Considerations                     |       |

|      | ndix C: Migration from Base-line to Mid-Range Devices |       |

|      | · · · · · · · · · · · · · · · · · · ·                 |       |

| On-L | ne Support                                            | . 117 |

|      | er Response                                           |       |

|      | 6C62B/72A Product Identification System               |       |

|      |                                                       |       |

## To Our Valued Customers

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

#### **New Customer Notification System**

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

#### Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended workarounds. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Corrections to this Data Sheet**

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please:

- Fill out and mail in the reader response form in the back of this data sheet.

- E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

#### 2.2.2.3 INTCON REGISTER

The INTCON Register is a readable and writable register, which contains various interrupt enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts. Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| R/W-0<br>GIE | R/W-0<br>PEIE                                                                                                                                                                                      | R/W-0<br>T0IE                                                                                           | R/W-0<br>INTE | R/W-0<br>RBIE | R/W-0<br>T0IF | R/W-0      | R/W-x<br>RBIF | R = Readable bit                                                 |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------|---------------|---------------|------------|---------------|------------------------------------------------------------------|--|--|--|--|

| bit7         | PEIE                                                                                                                                                                                               | TUIE                                                                                                    | INTE          | RBIE          | TUIF          | INTE       | BIF<br>bit0   | R = Readable bit<br>W = Writable bit<br>- n = Value at POR reset |  |  |  |  |

| bit 7:       | 1 = Enab                                                                                                                                                                                           | GIE: Global Interrupt Enable bit<br>1 = Enables all un-masked interrupts<br>0 = Disables all interrupts |               |               |               |            |               |                                                                  |  |  |  |  |

| bit 6:       | PEIE: Peripheral Interrupt Enable bit<br>1 = Enables all un-masked peripheral interrupts<br>0 = Disables all peripheral interrupts                                                                 |                                                                                                         |               |               |               |            |               |                                                                  |  |  |  |  |

| bit 5:       | <b>TOIE</b> : TMR0 Overflow Interrupt Enable bit<br>1 = Enables the TMR0 interrupt<br>0 = Disables the TMR0 interrupt                                                                              |                                                                                                         |               |               |               |            |               |                                                                  |  |  |  |  |

| bit 4:       | 1 = Enab                                                                                                                                                                                           | B0/INT Ext<br>les the RE<br>bles the RE                                                                 | 80/INT ext    | ernal inter   | rupt          |            |               |                                                                  |  |  |  |  |

| bit 3:       | 1 = Enab                                                                                                                                                                                           | 3 Port Cha<br>les the RE<br>bles the RE                                                                 | port char     | nge interru   | pt            |            |               |                                                                  |  |  |  |  |

| bit 2:       | 1 = TMR(                                                                                                                                                                                           | R0 Overflo<br>0 register l<br>0 register o                                                              | has overflo   | owed (soft    | ware must     | clear bit) |               |                                                                  |  |  |  |  |

| bit 1:       | INTF: RB0/INT External Interrupt Flag bit<br>1 = The RB0/INT external interrupt occurred (software must clear bit)<br>0 = The RB0/INT external interrupt did not occur                             |                                                                                                         |               |               |               |            |               |                                                                  |  |  |  |  |

| bit 0:       | <b>RBIF</b> : RB Port Change Interrupt Flag bit<br>1 = At least one of the RB7:RB4 input pins have changed state (clear by reading PORTB)<br>0 = None of the RB7:RB4 input pins have changed state |                                                                                                         |               |               |               |            |               |                                                                  |  |  |  |  |

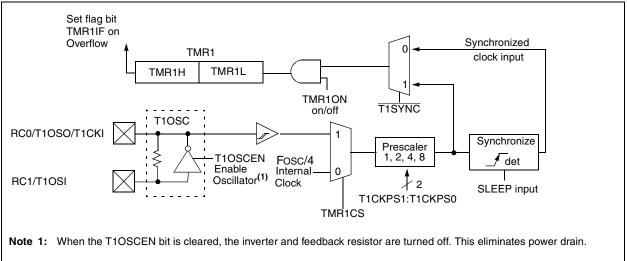

## TABLE 3-5 PORTC FUNCTIONS

| Name            | Bit# | Buffer<br>Type | Function                                                                    | TRISC<br>Override |

|-----------------|------|----------------|-----------------------------------------------------------------------------|-------------------|

| RC0/T1OSO/T1CKI | bit0 | ST             | Input/output port pin or Timer1 oscillator output/Timer1 clock input        | Yes               |

| RC1/T1OSI       | bit1 | ST             | Input/output port pin or Timer1 oscillator input                            | Yes               |

| RC2/CCP1        | bit2 | ST             | Input/output port pin or Capture1 input/Compare1 output/PWM1 output         | No                |

| RC3/SCK/SCL     | bit3 | ST             | RC3 can also be the synchronous serial clock for both SPI and $I^2C$ modes. | No                |

| RC4/SDI/SDA     | bit4 | ST             | RC4 can also be the SPI Data In (SPI mode) or data $I/O$ ( $I^2C$ mode).    | No                |

| RC5/SDO         | bit5 | ST             | Input/output port pin or Synchronous Serial Port data output                | No                |

| RC6             | bit6 | ST             | Input/output port pin                                                       | No                |

| RC7             | bit7 | ST             | Input/output port pin                                                       | No                |

Legend: ST = Schmitt Trigger input

## TABLE 3-6SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7   | Bit 6                                        | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|---------|----------------------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 07h     | PORTC | RC7     | RC6                                          | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   | xxxx xxxx                | uuuu uuuu                 |

| 87h     | TRISC | PORTC I | PORTC Data Direction Register 1111 1111 1111 |       |       |       |       |       |       |                          |                           |

Legend: x = unknown, u = unchanged.

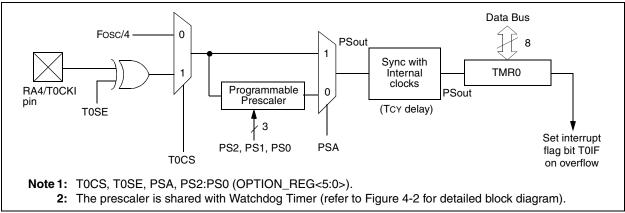

## 4.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Read and write

- INT on overflow

- 8-bit software programmable prescaler

- INT or EXT clock select

- EXT clock edge select

Figure 4-1 is a simplified block diagram of the Timer0 module.

Additional information on timer modules is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

#### 4.1 <u>Timer0 Operation</u>

Timer0 can operate as a timer or as a counter.

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed below.

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization. Additional information on external clock requirements is available in the Electrical Specifications section of this manual, and in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

#### 4.2 <u>Prescaler</u>

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 4-2). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. There is only one prescaler available which is shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The prescaler is not readable or writable.

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

Clearing bit PSA will assign the prescaler to the Timer0 module. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable.

Setting bit PSA will assign the prescaler to the Watchdog Timer (WDT). When the prescaler is assigned to the WDT, prescale values of 1:1, 1:2, ..., 1:128 are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment or ratio.

#### FIGURE 4-1: TIMER0 BLOCK DIAGRAM

### FIGURE 5-1: TIMER1 BLOCK DIAGRAM

| TABLE 8-1 | REGISTERS ASSOCIATED WITH SPI OPERATION |

|-----------|-----------------------------------------|

|           |                                         |

| Address | Name    | Bit 7      | Bit 6                                       | Bit 5                         | Bit 4     | Bit 3      | Bit 2    | Bit 1  | Bit 0  | Value<br>POR<br>BOF | l,  | Valu<br>all o<br>res |      |

|---------|---------|------------|---------------------------------------------|-------------------------------|-----------|------------|----------|--------|--------|---------------------|-----|----------------------|------|

| 0Bh,8Bh | INTCON  | GIE        | PEIE                                        | TOIE                          | INTE      | RBIE       | T0IF     | INTF   | RBIF   | 0000 0              | 00x | 0000                 | 000u |

| 0Ch     | PIR1    | —          | ADIF                                        | —                             | _         | SSPIF      | CCP1IF   | TMR2IF | TMR1IF | -00                 | 000 | - 0                  | 0000 |

| 8Ch     | PIE1    | —          | ADIE                                        |                               | —         | SSPIE      | CCP1IE   | TMR2IE | TMR1IE | -00                 | 000 | - 0                  | 0000 |

| 13h     | SSPBUF  | Synchronou | s Serial P                                  | ort Receiv                    | e Buffer/ | Transmit F | Register |        |        | xxxx x              | xxx | uuuu                 | uuuu |

| 14h     | SSPCON  | WCOL       | SSPOV                                       | SSPEN                         | CKP       | SSPM3      | SSPM2    | SSPM1  | SSPM0  | 0000 0              | 000 | 0000                 | 0000 |

| 94h     | SSPSTAT | SMP        | CKE                                         | D/Ā                           | Р         | S          | R/W      | UA     | BF     | 0000 0              | 000 | 0000                 | 0000 |

| 85h     | TRISA   | _          |                                             | PORTA Data Direction Register |           |            |          |        |        | 11 1                | 111 | 11                   | 1111 |

| 87h     | TRISC   | PORTC Data | Data Direction Register 1111 1111 1111 1111 |                               |           |            |          |        | 1111   |                     |     |                      |      |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the SSP in SPI mode.

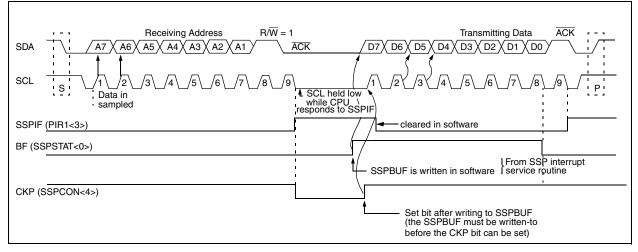

#### 8.3.1.3 TRANSMISSION

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and the CKP will be cleared by hardware, holding SCL low. Slave devices cause the master to wait by holding the SCL line low. The transmit data is loaded into the SSPBUF register, which in turn loads the SSPSR register. When bit CKP (SSP-CON<4>) is set, pin RC3/SCK/SCL releases SCL. When the SCL line goes high, the master may resume operating the SCL line and receiving data. The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 8-4).

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software, and the SSPSTAT register used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the masterreceiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not  $\overline{ACK}$ ), then the data transfer is complete. When the  $\overline{ACK}$  is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave then monitors for another occurrence of the START bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP.

FIGURE 8-4: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

#### 8.3.2 MASTER OPERATION

Master operation is supported in firmware using interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared by a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is idle and both the S and P bits are clear.

In master operation, the SCL and SDA lines are manipulated in software by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt if enabled):

- START condition

- STOP condition

- Byte transfer completed

Master operation can be done with either the slave mode idle (SSPM3:SSPM0 = 1011) or with the slave active. When both master operation and slave modes are used, the software needs to differentiate the source(s) of the interrupt.

For more information on master operation, see AN554 - Software Implementation of  $I^2C$  Bus Master.

#### 8.3.3 MULTI-MASTER OPERATION

In multi-master operation, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle and both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In multi-master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost, these are:

- Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed, an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to re-transfer the data at a later time.

For more information on master operation, see AN578 - Use of the SSP Module in the of  $l^2C$  Multi-Master Environment.

| Address  | Name    | Bit 7                         | Bit 6              | Bit 5                    | Bit 4     | Bit 3     | Bit 2    | Bit 1  | Bit 0  | PC   | e on<br>DR,<br>DR | all o | e on<br>ther<br>ets |

|----------|---------|-------------------------------|--------------------|--------------------------|-----------|-----------|----------|--------|--------|------|-------------------|-------|---------------------|

| 0Bh, 8Bh | INTCON  | GIE                           | PEIE               | TOIE                     | INTE      | RBIE      | T0IF     | INTF   | RBIF   | 0000 | 000x              | 0000  | 000u                |

| 0Ch      | PIR1    | _                             | ADIF               | _                        |           | SSPIF     | CCP1IF   | TMR2IF | TMR1IF | - 0  | 0000              | - 0   | 0000                |

| 8Ch      | PIE1    | _                             | ADIE               | _                        | —         | SSPIE     | CCP1IE   | TMR2IE | TMR1IE | - 0  | 0000              | - 0   | 0000                |

| 13h      | SSPBUF  | Synchronou                    | is Serial F        | Port Recei               | ve Buffer | /Transmit | Register | •      | •      | xxxx | xxxx              | uuuu  | uuuu                |

| 93h      | SSPADD  | Synchronou                    | is Serial F        | Port (I <sup>2</sup> C n | node) Ad  | dress Reg | jister   |        |        | 0000 | 0000              | 0000  | 0000                |

| 14h      | SSPCON  | WCOL                          | SSPOV              | SSPEN                    | CKP       | SSPM3     | SSPM2    | SSPM1  | SSPM0  | 0000 | 0000              | 0000  | 0000                |

| 94h      | SSPSTAT | SMP <sup>(1)</sup>            | CKE <sup>(1)</sup> | D/A                      | Р         | S         | R/W      | UA     | BF     | 0000 | 0000              | 0000  | 0000                |

| 87h      | TRISC   | PORTC Data Direction register |                    |                          |           |           |          |        | •      | 1111 | 1111              | 1111  | 1111                |

#### TABLE 8-3REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in SPI mode.

**Note 1:** Maintain these bits clear in  $I^2C$  mode.

#### 10.2.3 RC OSCILLATOR

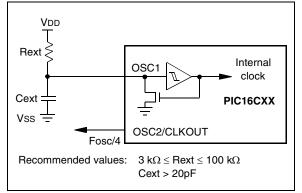

For timing insensitive applications, the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 10-4 shows how the R/C combination is connected to the PIC16CXXX.

#### FIGURE 10-4: RC OSCILLATOR MODE

### 10.3 <u>Reset</u>

The PIC16CXXX differentiates between various kinds of reset:

- Power-on Reset (POR)

- MCLR reset during normal operation

- MCLR reset during SLEEP

- WDT Reset (during normal operation)

- WDT Wake-up (during SLEEP)

- Brown-out Reset (BOR)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged by any other reset. Most other registers are reset to a "reset state" on Power-on Reset (POR), on the  $\overline{\text{MCLR}}$  and WDT Reset, on  $\overline{\text{MCLR}}$  reset during SLEEP, and on Brown-out Reset (BOR). They are not affected by a WDT Wake-up from SLEEP, which is viewed as the resumption of normal operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared depending on the reset situation, as indicated in Table 10-4. These bits are used in software to determine the nature of the reset. See Table 10-6 for a full description of reset states of all registers.

A simplified block diagram of the on-chip reset circuit is shown in Figure 10-5.

The PIC devices have a  $\overline{\text{MCLR}}$  noise filter in the  $\overline{\text{MCLR}}$  reset path. The filter will ignore small pulses. However, a valid  $\overline{\text{MCLR}}$  pulse must meet the minimum pulse width (TmcL, Specification #30).

No internal reset source (WDT, BOR, POR) will drive the  $\overline{\text{MCLR}}$  pin low.

| TABLE 10-6 INITIALIZATION CONDITIONS FOR ALL REGISTERS |     |               |                                    |                          |                                 |  |  |  |

|--------------------------------------------------------|-----|---------------|------------------------------------|--------------------------|---------------------------------|--|--|--|

| Register                                               |     | cable<br>ices | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT or<br>Interrupt |  |  |  |

| W                                                      | 62B | 72A           | XXXX XXXX                          | uuuu uuuu                | սսսս սսսս                       |  |  |  |

| INDF                                                   | 62B | 72A           | N/A                                | N/A                      | N/A                             |  |  |  |

| TMR0                                                   | 62B | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |

| PCL                                                    | 62B | 72A           | 0000h                              | 0000h                    | PC + 1 <sup>(2)</sup>           |  |  |  |

| STATUS                                                 | 62B | 72A           | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu <b>(3)</b>            |  |  |  |

| FSR                                                    | 62B | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |

| PORTA <sup>(4)</sup>                                   | 62B | 72A           | 0x 0000                            | 0u 0000                  | uu uuuu                         |  |  |  |

| PORTB <sup>(5)</sup>                                   | 62B | 72A           | xxxx xxxx                          | սսսս սսսս                | սսսս սսսս                       |  |  |  |

| PORTC <sup>(5)</sup>                                   | 62B | 72A           | xxxx xxxx                          | սսսս սսսս                | uuuu uuuu                       |  |  |  |

| PCLATH                                                 | 62B | 72A           | 0 0000                             | 0 0000                   | u uuuu                          |  |  |  |

| INTCON                                                 | 62B | 72A           | 0000 000x                          | 0000 000u                | uuuu uuuu <b>(1)</b>            |  |  |  |

|                                                        | 62B | 72A           | 0000                               | 0000                     | uuuu <b>(1)</b>                 |  |  |  |

| PIR1                                                   | 62B | 72A           | -0 0000                            | -0 0000                  | -u uuuu <b>(1)</b>              |  |  |  |

| TMR1L                                                  | 62B | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |

| TMR1H                                                  | 62B | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |

| T1CON                                                  | 62B | 72A           | 00 0000                            | uu uuuu                  | uu uuuu                         |  |  |  |

| TMR2                                                   | 62B | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |  |

| T2CON                                                  | 62B | 72A           | -000 0000                          | -000 0000                | -uuu uuuu                       |  |  |  |

| SSPBUF                                                 | 62B | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |

| SSPCON                                                 | 62B | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |  |

| CCPR1L                                                 | 62B | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |

| CCPR1H                                                 | 62B | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |

| CCP1CON                                                | 62B | 72A           | 00 0000                            | 00 0000                  | uu uuuu                         |  |  |  |

| ADRES                                                  | 62B | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |

| ADCON0                                                 | 62B | 72A           | 0000 00-0                          | 0000 00-0                | uuuu uu-u                       |  |  |  |

| OPTION_REG                                             | 62B | 72A           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |  |  |  |

| TRISA                                                  | 62B | 72A           | 11 1111                            | 11 1111                  | uu uuuu                         |  |  |  |

| TRISB                                                  | 62B | 72A           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |  |  |  |

| TRISC                                                  | 62B | 72A           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |  |  |  |

| PIE1                                                   | 62B | 72A           | 0000                               | 0000                     | uuuu                            |  |  |  |

|                                                        | 62B | 72A           | -0 0000                            | -0 0000                  | -u uuuu                         |  |  |  |

| PCON                                                   | 62B | 72A           | 0q                                 | uq                       | uq                              |  |  |  |

| PR2                                                    | 62B | 72A           | 1111 1111                          | 1111 1111                | 1111 1111                       |  |  |  |

| SSPADD                                                 | 62B | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |  |

| SSPSTAT                                                | 62B | 72A           | 0000 0000                          | 0000 0000                | սսսս սսսս                       |  |  |  |

| ADCON1                                                 | 62B | 72A           | 000                                | 000                      | uuu                             |  |  |  |

| TABLE 10-6 | INITIALIZATION CONDITIONS FOR ALL REGISTERS |

|------------|---------------------------------------------|

|            |                                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', <math>q = value depends on condition

Note 1: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

**3:** See Table 10-5 for reset value for specific condition.

4: On any device reset, these pins are configured as inputs.

5: This is the value that will be in the port output latch.

# PIC16C62B/72A

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSS f,b                                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                        |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                                    |

| Description:     | If bit 'b' in register 'f' is '0', then the next instruction is executed.<br>If bit 'b' is '1', then the next instruction is discarded and a $NOP$ is executed instead, making this a 2TCY instruction. |

| CLRF             | Clear f                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CLRF f                                               |

| Operands:        | $0 \le f \le 127$                                                     |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSC f,b                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                    |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                   |

| Description:     | If bit 'b' in register 'f' is '1', then the next instruction is executed.<br>If bit 'b' in register 'f' is '0', then the next instruction is discarded, and a NOP is executed instead, making this a 2TCY instruction. |

| CLRW             | Clear W                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                          |

| Operands:        | None                                                                  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | W register is cleared. Zero bit (Z) is set.                           |

| CALL             | Call Subroutine                                                                                                                                                                                | CLRWDT           | Clear Watchdog Timer                                                                                                             |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                        | Syntax:          | [label] CLRWDT                                                                                                                   |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                             | Operands:        | None                                                                                                                             |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                               | Operation:       | $00h \rightarrow WDT$<br>0 $\rightarrow WDT$ prescaler,<br>1 $\rightarrow \overline{TO}$                                         |

| Status Affected: | None                                                                                                                                                                                           |                  | $1 \rightarrow \overline{PD}$                                                                                                    |

| Description:     | Call Subroutine. First, return address                                                                                                                                                         | Status Affected: | TO, PD                                                                                                                           |

|                  | (PC+1) is pushed onto the stack. The<br>eleven bit immediate address is loaded<br>into PC bits <10:0>. The upper bits of<br>the PC are loaded from PCLATH.<br>CALL is a two cycle instruction. | Description:     | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT. Status bits TO and PD<br>are set. |

# PIC16C62B/72A

| SUBLW            | Subtract W from Literal                                                                                                                   |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] SUBLW k                                                                                                                           |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                                       |  |  |  |  |  |

| Operation:       | $k - (W) \rightarrow (W)$                                                                                                                 |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                  |  |  |  |  |  |

| Description:     | The W register is subtracted (2's com-<br>plement method) from the eight bit lit-<br>eral 'k'. The result is placed in the W<br>register. |  |  |  |  |  |

| XORLW            | Exclusive OR Literal with W                                                                                                  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                                     |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                          |  |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                                |  |  |  |  |  |

| Status Affected: | Z                                                                                                                            |  |  |  |  |  |

| Description:     | The contents of the W register are<br>XOR'ed with the eight bit literal 'k'.<br>The result is placed in the W regis-<br>ter. |  |  |  |  |  |

| SUBWF        | Subtract W from f                                                                                                                                                                    | XORWF    |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Syntax:      | [label] SUBWF f,d                                                                                                                                                                    | Syntax:  |

| Operands:    | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                   | Operan   |

| Operation:   | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                | Operatio |

| Status       | C, DC, Z                                                                                                                                                                             | Status A |

| Affected:    |                                                                                                                                                                                      | Descrip  |

| Description: | Subtract (2's complement method) W<br>register from register 'f'. If 'd' is 0, the<br>result is stored in the W register. If 'd' is<br>1, the result is stored back in register 'f'. |          |

| XORWF            | Exclusive OR W with f                                                                                                                                                                     |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                                |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                               |  |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                                 |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                         |  |  |  |  |  |

| Description:     | Exclusive OR the contents of the W<br>register with register 'f'. If 'd' is 0, the<br>result is stored in the W register. If 'd'<br>is 1, the result is stored back in regis-<br>ter 'f'. |  |  |  |  |  |

| SWAPF            | Swap Nibbles in f                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                                |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                               |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>), (f<7:4>) \rightarrow (destination<3:0>)$                                                                                        |

| Status Affected: | None                                                                                                                                                                      |

| Description:     | The upper and lower nibbles of regis-<br>ter 'f' are exchanged. If 'd' is 0, the<br>result is placed in W register. If 'd' is 1,<br>the result is placed in register 'f'. |

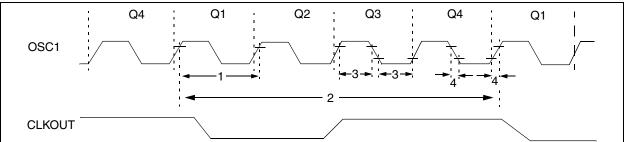

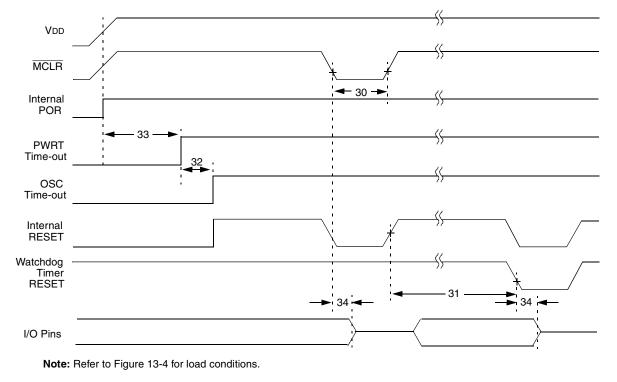

#### 13.4.3 TIMING DIAGRAMS AND SPECIFICATIONS

#### FIGURE 13-5: EXTERNAL CLOCK TIMING

| Param<br>No. | Sym   | Characteristic                  | Min | Тур† | Мах    | Units | Conditions          |

|--------------|-------|---------------------------------|-----|------|--------|-------|---------------------|

| 1A           | Fosc  | External CLKIN Frequency        | DC  |      | 4      | MHz   | RC and XT osc modes |

|              |       | (Note 1)                        | DC  | —    | 4      | MHz   | HS osc mode (-04)   |

|              |       |                                 | DC  | —    | 20     | MHz   | HS osc mode (-20)   |

|              |       |                                 | DC  | _    | 200    | kHz   | LP osc mode         |

|              |       | Oscillator Frequency            | DC  |      | 4      | MHz   | RC osc mode         |

|              |       | (Note 1)                        | 0.1 | —    | 4      | MHz   | XT osc mode         |

|              |       |                                 | 4   | —    | 20     | MHz   | HS osc mode         |

|              |       |                                 | 5   | _    | 200    | kHz   | LP osc mode         |

| 1            | Tosc  | External CLKIN Period           | 250 | —    | —      | ns    | RC and XT osc modes |

|              |       | (Note 1)                        | 250 | —    | —      | ns    | HS osc mode (-04)   |

|              |       |                                 | 50  | —    | —      | ns    | HS osc mode (-20)   |

|              |       |                                 | 5   | _    | —      | μS    | LP osc mode         |

|              |       | Oscillator Period               | 250 | —    | —      | ns    | RC osc mode         |

|              |       | (Note 1)                        | 250 | —    | 10,000 | ns    | XT osc mode         |

|              |       |                                 | 250 | —    | 250    | ns    | HS osc mode (-04)   |

|              |       |                                 | 50  | —    | 250    | ns    | HS osc mode (-20)   |

|              |       |                                 | 5   | _    | _      | μS    | LP osc mode         |

| 2            | Тсү   | Instruction Cycle Time (Note 1) | 200 | _    | DC     | ns    | Tcy = 4/Fosc        |

| 3*           | TosL, | External Clock in (OSC1) High   | 100 | —    | —      | ns    | XT oscillator       |

|              | TosH  | or Low Time                     | 2.5 | —    | —      | μS    | LP oscillator       |

|              |       |                                 | 15  | _    | —      | ns    | HS oscillator       |

| 4*           | TosR, | External Clock in (OSC1) Rise   | —   |      | 25     | ns    | XT oscillator       |

|              | TosF  | or Fall Time                    | —   | —    | 50     | ns    | LP oscillator       |

|              |       |                                 | —   | —    | 15     | ns    | HS oscillator       |

#### TABLE 13-2: EXTERNAL CLOCK TIMING REQUIREMENTS

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin.

When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

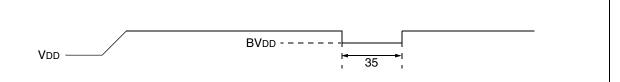

#### FIGURE 13-8: BROWN-OUT RESET TIMING

# TABLE 13-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                                   | Min | Тур†         | Max | Units | Conditions                                         |

|--------------|-------|--------------------------------------------------|-----|--------------|-----|-------|----------------------------------------------------|

| 30           | TmcL  | MCLR Pulse Width (low)                           | 2   |              | _   | μs    | VDD = 5V, -40°C to +125°C                          |

| 31*          | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler) | 7   | 18           | 33  | ms    | VDD = 5V, -40°C to +125°C                          |

| 32           | Tost  | Oscillator Start-up Timer Period                 |     | 1024<br>Tosc | —   | —     | Tosc = OSC1 period                                 |

| 33*          | Tpwrt | Power-up Timer Period                            | 28  | 72           | 132 | ms    | $VDD = 5V, -40^{\circ}C \text{ to } +125^{\circ}C$ |

| 34           | Tıoz  | I/O Hi-impedance from MCLR<br>Low or WDT reset   | _   | _            | 2.1 | μS    |                                                    |

| 35           | TBOR  | Brown-out Reset Pulse Width                      | 100 | _            | _   | μS    | $VDD \le BVDD$ (D005)                              |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

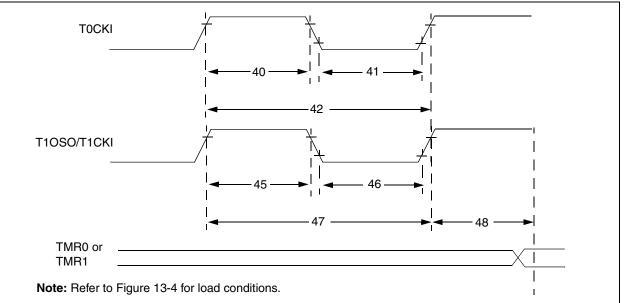

### FIGURE 13-9: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| TABLE 13-5: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|-------------|-----------------------------------------------|

| IADEE IV V. |                                               |

| Param<br>No. | Sym               |                                                 | Characteristic                                    |                | Min                                       | Тур† | Max   | Units | Conditions                         |  |

|--------------|-------------------|-------------------------------------------------|---------------------------------------------------|----------------|-------------------------------------------|------|-------|-------|------------------------------------|--|

| 40*          | Tt0H              | 0H T0CKI High Pulse Width                       |                                                   | No Prescaler   | 0.5Tcy + 20                               | -    | -     | ns    | Must also meet                     |  |

|              |                   |                                                 |                                                   | With Prescaler | 10                                        | -    |       | ns    | parameter 42                       |  |

| 41*          | Tt0L              | T0CKI Low Pulse W                               | T0CKI Low Pulse Width                             |                | 0.5TCY + 20                               | -    |       | ns    | Must also meet                     |  |

|              |                   | N N                                             |                                                   | With Prescaler | 10                                        | -    |       | ns    | parameter 42                       |  |

| 42*          | Tt0P T0CKI Period |                                                 |                                                   | No Prescaler   | Tcy + 40                                  | —    | -     | ns    |                                    |  |

|              |                   |                                                 |                                                   | With Prescaler | Greater of:<br>20 or <u>Tcy + 40</u><br>N | -    | -     | ns    | N = prescale value<br>(2, 4,, 256) |  |

| 45*          | Tt1H              | T1CKI High Time                                 | Synchronous, P                                    | rescaler = 1   | 0.5Tcy + 20                               | —    | -     | ns    | Must also meet                     |  |

|              |                   |                                                 | Synchronous,                                      | PIC16CXX       | 15                                        | -    |       | ns    | parameter 47                       |  |

|              |                   |                                                 | Prescaler = 2,4,8                                 | PIC16LCXX      | 25                                        | —    | _     | ns    | -                                  |  |

|              |                   |                                                 | Asynchronous                                      | PIC16CXX       | 30                                        |      | _     | ns    |                                    |  |

|              |                   |                                                 |                                                   | PIC16LCXX      | 50                                        |      | _     | ns    |                                    |  |

| 46*          | Tt1L              | 1L T1CKI Low Time                               | Synchronous, Prescaler = 1                        |                | 0.5TCY + 20                               | -    |       | ns    | Must also meet                     |  |

|              |                   |                                                 | Synchronous,<br>Prescaler =<br>2,4,8              | PIC16CXX       | 15                                        | —    | -     | ns    | parameter 47                       |  |

|              |                   |                                                 |                                                   | PIC16LCXX      | 25                                        | —    |       | ns    |                                    |  |

|              |                   |                                                 | Asynchronous                                      | PIC16CXX       | 30                                        | -    |       | ns    |                                    |  |

|              |                   |                                                 |                                                   | PIC16LCXX      | 50                                        | -    |       | ns    |                                    |  |

| 47*          | Tt1P              | T1CKI input period                              | Synchronous                                       | PIC16CXX       | GREATER OF:<br>30 OR <u>TCY + 40</u><br>N | _    | _     | ns    | N = prescale value<br>(1, 2, 4, 8) |  |

|              |                   |                                                 |                                                   | PIC16LCXX      | GREATER OF:<br>50 OR <u>TCY + 40</u><br>N |      |       |       | N = prescale value<br>(1, 2, 4, 8) |  |

|              |                   |                                                 | Asynchronous                                      | PIC16CXX       | 60                                        | -    |       | ns    |                                    |  |

|              |                   |                                                 |                                                   | PIC16LCXX      | 100                                       | —    | —     | ns    |                                    |  |

|              | Ft1               | Timer1 oscillator inp<br>(oscillator enabled by |                                                   |                | DC                                        | -    | 200   | kHz   |                                    |  |

| 48           | TCKEZtmr1         | Delay from external                             | Delay from external clock edge to timer increment |                |                                           |      | 7Tosc | -     |                                    |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

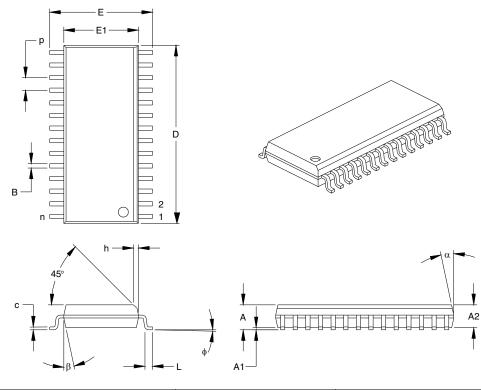

#### 28-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC) 15.4

|                          | Units  | INCHES* |      | MILLIMETERS |       |       |       |

|--------------------------|--------|---------|------|-------------|-------|-------|-------|

| Dimension                | Limits | MIN     | NOM  | MAX         | MIN   | NOM   | MAX   |

| Number of Pins           | n      |         | 28   |             |       | 28    |       |

| Pitch                    | р      |         | .050 |             |       | 1.27  |       |

| Overall Height           | Α      | .093    | .099 | .104        | 2.36  | 2.50  | 2.64  |

| Molded Package Thickness | A2     | .088    | .091 | .094        | 2.24  | 2.31  | 2.39  |

| Standoff                 | A1     | .004    | .008 | .012        | 0.10  | 0.20  | 0.30  |

| Overall Width            | E      | .394    | .407 | .420        | 10.01 | 10.34 | 10.67 |

| Molded Package Width     | E1     | .288    | .295 | .299        | 7.32  | 7.49  | 7.59  |

| Overall Length           | D      | .695    | .704 | .712        | 17.65 | 17.87 | 18.08 |

| Chamfer Distance         | h      | .010    | .020 | .029        | 0.25  | 0.50  | 0.74  |

| Foot Length              | L      | .016    | .033 | .050        | 0.41  | 0.84  | 1.27  |

| Foot Angle Top           | φ      | 0       | 4    | 8           | 0     | 4     | 8     |

| Lead Thickness           | С      | .009    | .011 | .013        | 0.23  | 0.28  | 0.33  |

| Lead Width               | В      | .014    | .017 | .020        | 0.36  | 0.42  | 0.51  |

| Mold Draft Angle Top     | α      | 0       | 12   | 15          | 0     | 12    | 15    |

| Mold Draft Angle Bottom  | β      | 0       | 12   | 15          | 0     | 12    | 15    |

\*Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MS-013 Drawing No. C04-052

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

## READER RESPONSE

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE: | Technical Publications Manager<br>Reader Response                                        | Total Pages Sent                |  |  |  |  |  |

|------------|------------------------------------------------------------------------------------------|---------------------------------|--|--|--|--|--|

| Fror       | n: Name                                                                                  |                                 |  |  |  |  |  |

|            | Company                                                                                  |                                 |  |  |  |  |  |

|            | Address                                                                                  |                                 |  |  |  |  |  |

|            | City / State / ZIP / Country                                                             |                                 |  |  |  |  |  |

|            | Telephone: ()                                                                            | FAX: ()                         |  |  |  |  |  |

| Арр        | lication (optional):                                                                     |                                 |  |  |  |  |  |

| Wou        | Ild you like a reply?YN                                                                  |                                 |  |  |  |  |  |

| Dev        | ice: 24xx010                                                                             | Literature Number: DS35008C     |  |  |  |  |  |

| Que        | stions:                                                                                  |                                 |  |  |  |  |  |

| 1.         | What are the best features of this document?                                             |                                 |  |  |  |  |  |

|            |                                                                                          |                                 |  |  |  |  |  |

| 2.         | How does this document meet your hardware and softw                                      | are development needs?          |  |  |  |  |  |

|            |                                                                                          |                                 |  |  |  |  |  |

| 3.         | 3. Do you find the organization of this document easy to follow? If not, why?            |                                 |  |  |  |  |  |

|            |                                                                                          |                                 |  |  |  |  |  |

|            |                                                                                          |                                 |  |  |  |  |  |

| 4.         | What additions to the document do you think would enh                                    | ance the structure and subject? |  |  |  |  |  |

|            |                                                                                          |                                 |  |  |  |  |  |

| 5.         | What deletions from the document could be made without affecting the overall usefulness? |                                 |  |  |  |  |  |

|            |                                                                                          |                                 |  |  |  |  |  |

|            |                                                                                          |                                 |  |  |  |  |  |

| 6.         | Is there any incorrect or misleading information (what ar                                | nd where)?                      |  |  |  |  |  |

|            |                                                                                          |                                 |  |  |  |  |  |

| 7.         | How would you improve this document?                                                     |                                 |  |  |  |  |  |

|            |                                                                                          |                                 |  |  |  |  |  |

|            |                                                                                          |                                 |  |  |  |  |  |

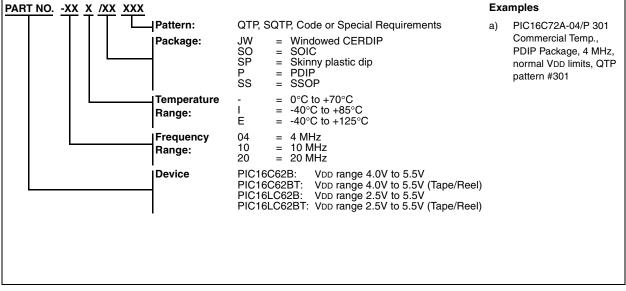

# PIC16C62B/72A PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery refer to the factory or the listed sales office.

\* JW Devices are UV erasable and can be programmed to any device configuration. JW Devices meet the electrical requirement of each oscillator type (including LC devices).

#### Sales and Support

#### Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

1. Your local Microchip sales office

- 2. The Microchip Corporate Literature Center U.S. FAX: (480) 786-7277

- 3. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

#### **New Customer Notification System**

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.