#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Decalis                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | ОТР                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                 |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 28-SPDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc62b-04i-sp |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

## PIC16C62B/72A

#### TABLE 1-1 PIC16C62B/PIC16C72A PINOUT DESCRIPTION

| Pin Name                    | DIP<br>Pin#         | SOIC<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                                  |

|-----------------------------|---------------------|--------------|---------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN                  | 9                   | 9            | I             | ST/CMOS <sup>(3)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                        |

| OSC2/CLKOUT                 | 10                  | 10           | 0             | _                      | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/Vpp                    | 1                   | 1            | I/P           | ST                     | Master clear (reset) input or programming voltage input. This pin is an active low reset to the device.                                                                                                      |

|                             |                     |              |               |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                          |

| RA0/AN0 <sup>(4)</sup>      | 2                   | 2            | I/O           | TTL                    | RA0 can also be analog input 0                                                                                                                                                                               |

| RA1/AN1 <sup>(4)</sup>      | 3                   | 3            | I/O           | TTL                    | RA1 can also be analog input 1                                                                                                                                                                               |

| RA2/AN2 <sup>(4)</sup>      | 4                   | 4            | I/O           | TTL                    | RA2 can also be analog input 2                                                                                                                                                                               |

| RA3/AN3/VREF <sup>(4)</sup> | 5                   | 5            | I/O           | TTL                    | RA3 can also be analog input 3 or analog reference voltage                                                                                                                                                   |

| RA4/T0CKI                   | 6                   | 6            | I/O           | ST                     | RA4 can also be the clock input to the Timer0 module.<br>Output is open drain type.                                                                                                                          |

| RA5/SS/AN4 <sup>(4)</sup>   | 7                   | 7            | I/O           | TTL                    | RA5 can also be analog input 4 or the slave select for the synchronous serial port.                                                                                                                          |

|                             |                     |              |               |                        | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                                |

| RB0/INT                     | 21                  | 21           | I/O           | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                                  |

| RB1                         | 22                  | 22           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB2                         | 23                  | 23           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB3                         | 24                  | 24           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB4                         | 25                  | 25           | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                     |

| RB5                         | 26                  | 26           | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                     |

| RB6                         | 27                  | 27           | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming clock.                                                                                                                                                           |

| RB7                         | 28                  | 28           | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming data.                                                                                                                                                            |

|                             |                     |              |               |                        | PORTC is a bi-directional I/O port.                                                                                                                                                                          |

| RC0/T1OSO/T1CKI             | 11                  | 11           | I/O           | ST                     | RC0 can also be the Timer1 oscillator output or Timer1<br>clock input.                                                                                                                                       |

| RC1/T1OSI                   | 12                  | 12           | I/O           | ST                     | RC1 can also be the Timer1 oscillator input.                                                                                                                                                                 |

| RC2/CCP1                    | 13                  | 13           | I/O           | ST                     | RC2 can also be the Capture1 input/Compare1 output/<br>PWM1 output.                                                                                                                                          |

| RC3/SCK/SCL                 | 14                  | 14           | I/O           | ST                     | RC3 can also be the synchronous serial clock input/output for both SPI and I <sup>2</sup> C modes.                                                                                                           |

| RC4/SDI/SDA                 | 15                  | 15           | I/O           | ST                     | RC4 can also be the SPI Data In (SPI mode) or data I/O ( $I^2C$ mode).                                                                                                                                       |

| RC5/SDO                     | 16                  | 16           | I/O           | ST                     | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                                 |

| RC6                         | 17                  | 17           | I/O           | ST                     |                                                                                                                                                                                                              |

| RC7                         | 18                  | 18           | I/O           | ST                     |                                                                                                                                                                                                              |

| Vss                         | 8, 19               | 8, 19        | Р             | _                      | Ground reference for logic and I/O pins.                                                                                                                                                                     |

| Vdd                         | 20                  | 20           | Р             | —                      | Positive supply for logic and I/O pins.                                                                                                                                                                      |

| Legend: I = input           | O = outp<br>— = Not |              | I/O =         | input/output           | P = power or program<br>ST = Schmitt Trigger input                                                                                                                                                           |

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in serial programming mode.

This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

4: The A/D module is not available on the PIC16C62B.

## 2.0 MEMORY ORGANIZATION

There are two memory blocks in each of these microcontrollers. Each block (Program Memory and Data Memory) has its own bus, so that concurrent access can occur.

Additional information on device memory may be found in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

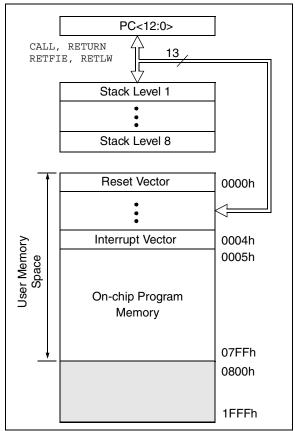

### 2.1 Program Memory Organization

The PIC16C62B/72A devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. Each device has 2K x 14 words of program memory. Accessing a location above 07FFh will cause a wraparound.

The reset vector is at 0000h and the interrupt vector is at 0004h.

#### FIGURE 2-1: PROGRAM MEMORY MAP AND STACK

NOTES:

NOTES:

### 9.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

Note: This section applies to the PIC16C72A only.

The analog-to-digital (A/D) converter module has five input channels.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number (refer to Application Note AN546 for use of A/D Converter). The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD) or the voltage level on the RA3/AN3/VREF pin.

The A/D converter has the feature of being able to operate while the device is in SLEEP mode. To operate in sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

Additional information on the A/D module is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

The A/D module has three registers. These registers are:

- A/D Result Register (ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

A device reset forces all registers to their reset state. This forces the A/D module to be turned off, and any conversion is aborted.

The ADCON0 register, shown in Figure 9-1, controls the operation of the A/D module. The ADCON1 register, shown in Figure 9-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference) or as digital I/O.

| R/W-0         | R/W-0                                                                                                                                                  | R/W-0                                                    | R/W-0                                        | R/W-0        | R/W-0                                | U-0 | R/W-0        |                                                                               |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------|--------------|--------------------------------------|-----|--------------|-------------------------------------------------------------------------------|--|--|--|

| ADCS1<br>bit7 | ADCS0                                                                                                                                                  | CHS2                                                     | CHS1                                         | CHS0         | GO/DONE                              | _   | ADON<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0' |  |  |  |

| bit 7-6:      | ADCS1:ADCS0: A/D Conversion Clock Select bits<br>00 = Fosc/2<br>01 = Fosc/8<br>10 = Fosc/32<br>11 = FRC (clock derived from an internal RC oscillator) |                                                          |                                              |              |                                      |     |              |                                                                               |  |  |  |

| bit 5-3:      | CHS2:CH<br>000 = cha<br>001 = cha<br>010 = cha<br>011 = cha<br>100 = cha                                                                               | annel 0, (F<br>annel 1, (F<br>annel 2, (F<br>annel 3, (F | RÃO/ANO)<br>RA1/AN1)<br>RA2/AN2)<br>RA3/AN3) | el Select bi | ts                                   |     |              |                                                                               |  |  |  |

| bit 2:        | GO/DON                                                                                                                                                 | E: A/D Co                                                | nversion                                     | Status bit   |                                      |     |              |                                                                               |  |  |  |

|               |                                                                                                                                                        | onversion<br>onversion                                   | not in pro                                   |              | this bit starts t<br>s bit is automa |     |              | ware when the A/D                                                             |  |  |  |

| bit 1:        | Unimpler                                                                                                                                               | nented: F                                                | Read as '0                                   | ı            |                                      |     |              |                                                                               |  |  |  |

| bit 0:        | <b>ADON</b> : $A_{1} = A/D c$                                                                                                                          | onverter r                                               |                                              |              | l consumes no                        |     | n ourront    |                                                                               |  |  |  |

#### **REGISTER 9-1: ADCON0 REGISTER (ADDRESS 1Fh)**

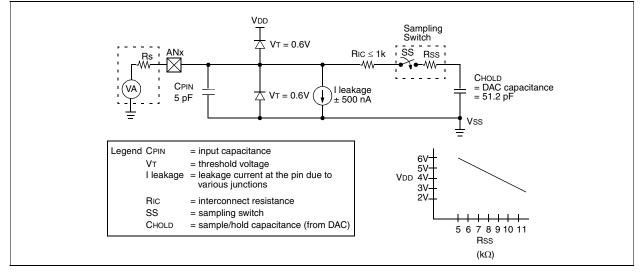

#### 9.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 9-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 10 k $\Omega$ . After the analog input channel is selected (changed), this acquisition must pass before the conversion can be started.

To calculate the minimum acquisition time, TACQ, see Equation 9-1. This equation calculates the acquisition time to within 1/2 LSb error (512 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified accuracy.

| Note: | When the conversion is started, the hold-         |

|-------|---------------------------------------------------|

|       | ing capacitor is disconnected from the input pin. |

|       | input pin.                                        |

In general;

Assuming Rs =  $10k\Omega$

Vdd =

$$3.0V$$

(Rss =  $10k\Omega$ )

TACQ  $\approx~13.0~\mu Sec$

By increasing VDD and reducing Rs and Temp., TACQ can be substantially reduced.

#### FIGURE 9-2: ANALOG INPUT MODEL

#### EQUATION 9-1: ACQUISITION TIME

- TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient

- = TAMP + TC + TCOFF TAMP =  $5\mu S$ TC = -  $(51.2pF)(1k\Omega + Rss + Rs) In(1/511)$ TCOFF = (Temp - $25^{\circ}C)(0.05\mu S/^{\circ}C)$

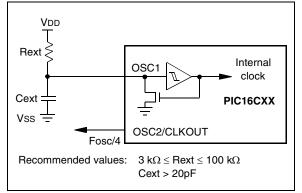

#### 10.2.3 RC OSCILLATOR

For timing insensitive applications, the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 10-4 shows how the R/C combination is connected to the PIC16CXXX.

#### FIGURE 10-4: RC OSCILLATOR MODE

### 10.3 <u>Reset</u>

The PIC16CXXX differentiates between various kinds of reset:

- Power-on Reset (POR)

- MCLR reset during normal operation

- MCLR reset during SLEEP

- WDT Reset (during normal operation)

- WDT Wake-up (during SLEEP)

- Brown-out Reset (BOR)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged by any other reset. Most other registers are reset to a "reset state" on Power-on Reset (POR), on the  $\overline{MCLR}$  and WDT Reset, on  $\overline{MCLR}$  reset during SLEEP, and on Brown-out Reset (BOR). They are not affected by a WDT Wake-up from SLEEP, which is viewed as the resumption of normal operation. The  $\overline{TO}$  and  $\overline{PD}$  bits are set or cleared depending on the reset situation, as indicated in Table 10-4. These bits are used in software to determine the nature of the reset. See Table 10-6 for a full description of reset states of all registers.

A simplified block diagram of the on-chip reset circuit is shown in Figure 10-5.

The PIC devices have a  $\overline{\text{MCLR}}$  noise filter in the  $\overline{\text{MCLR}}$  reset path. The filter will ignore small pulses. However, a valid  $\overline{\text{MCLR}}$  pulse must meet the minimum pulse width (TmcL, Specification #30).

No internal reset source (WDT, BOR, POR) will drive the  $\overline{\text{MCLR}}$  pin low.

### FIGURE 10-10: WAKE-UP FROM SLEEP THROUGH INTERRUPT

| ; a1   a2   a3   a4 ; (<br>osc1 /~//        | 21   Q2   Q3   Q4 ;<br>\/ |                       | 01 02 03 04  | a1 a2 a3 a4                   | a1 a2 a3 a4      | 01 02 03 04 |

|---------------------------------------------|---------------------------|-----------------------|--------------|-------------------------------|------------------|-------------|

| CLKOUT(4)                                   |                           | Tost(2)               | /            | /                             | //               |             |

| INTF flag<br>(INTCON<1>)                    |                           |                       |              | Interrupt Latency<br>(Note 2) | -<br> <br> <br>  |             |

| GIE bit<br>(INTCON<7>)                      | <br> <br> +<br> <br>      | Processor in<br>SLEEP |              |                               | 1<br>1<br>1<br>1 |             |

| INSTRUCTION FLOW                            | 1                         |                       |              |                               |                  | · · · ·     |

| PC <u>X PC X</u>                            | PC+1                      | PC+2                  | PC+2         | X PC + 2                      | X 0004h          | X 0005h     |

| Instruction {<br>fetched { Inst(PC) = SLEEP | Inst(PC + 1)              | ,<br>,<br>,           | Inst(PC + 2) |                               | Inst(0004h)      | Inst(0005h) |

| Instruction<br>executed Inst(PC - 1)        | SLEEP                     | 1<br>1<br>1           | Inst(PC + 1) | Dummy cycle                   | Dummy cycle      | Inst(0004h) |

**Note 1:** XT, HS or LP oscillator mode assumed.

**2:** TOST = 1024TOSC (drawing not to scale) This delay will not be there for RC osc mode.

3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

#### 10.14 Program Verification/Code Protection

If the code protection bits have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip does not recommend code pro- |

|-------|----------------------------------------|

|       | tecting windowed devices.              |

#### 10.15 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution, but are readable and writable during program/verify. It is recommended that only the 4 least significant bits of the ID location are used.

For ROM devices, these values are submitted along with the ROM code.

#### 10.16 In-Circuit Serial Programming™

PIC16CXXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three more lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

For complete details of serial programming, please refer to the In-Circuit Serial Programming (ICSP™) Guide, DS30277.

## **13.0 ELECTRICAL CHARACTERISTICS**

#### Absolute Maximum Ratings (†)

| Ambient temperature under bias                                                                              | 55°C to +125°C            |

|-------------------------------------------------------------------------------------------------------------|---------------------------|

| Storage temperature                                                                                         |                           |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)                                          |                           |

| Voltage on VDD with respect to VSS                                                                          |                           |

| Voltage on MCLR with respect to Vss (Note 2)                                                                |                           |

| Voltage on RA4 with respect to Vss                                                                          |                           |

| Total power dissipation (Note 1)                                                                            |                           |

| Maximum current out of Vss pin                                                                              |                           |

| Maximum current into VDD pin                                                                                |                           |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                | ±20 mA                    |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                              |                           |

| Maximum output current sunk by any I/O pin                                                                  | 25 mA                     |

| Maximum output current sourced by any I/O pin                                                               | 25 mA                     |

| Maximum current sunk by PORTA and PORTB (combined)                                                          | 200 mA                    |

| Maximum current sourced by PORTA and PORTB (combined)                                                       | 200 mA                    |

| Maximum current sunk by PORTC                                                                               | 200 mA                    |

| Maximum current sourced by PORTC                                                                            | 200 mA                    |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-V | ЮН) x IOH} + ∑(VOI x IOL) |

**2:** Voltage spikes below Vss at the MCLR/VPP pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR/VPP pin, rather than pulling this pin directly to Vss.

**†** NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### 13.1 DC Characteristics: PIC16C62B/72A-04 (Commercial, Industrial, Extended) PIC16C62B/72A-20 (Commercial, Industrial, Extended)

|                 |               |                                                                         | Standar     | d Opera    | ating Co                              | ondition | is (unless otherwise stated)                                                                                 |

|-----------------|---------------|-------------------------------------------------------------------------|-------------|------------|---------------------------------------|----------|--------------------------------------------------------------------------------------------------------------|

| DC CHA          |               |                                                                         | Operatir    | ng temp    | erature                               | e 0°C    | $\leq$ TA $\leq$ +70°C for commercial                                                                        |

| DC CHA          |               |                                                                         |             | -40°C      | $\leq$ TA $\leq$ +85°C for industrial |          |                                                                                                              |

|                 |               |                                                                         |             |            |                                       | -40°C    | $\leq$ TA $\leq$ +125°C for extended                                                                         |

| Param<br>No.    | Sym           | Characteristic                                                          | Min         | Тур†       | Max                                   | Units    | Conditions                                                                                                   |

| D001            | Vdd           | Supply Voltage                                                          | 4.0         | -          | 5.5                                   | V        | XT, RC and LP osc mode                                                                                       |

| D001A           |               | cappij renage                                                           | 4.5         | -          | 5.5                                   | v        | HS osc mode                                                                                                  |

|                 |               |                                                                         | VBOR*       | -          | 5.5                                   | V        | BOR enabled (Note 7)                                                                                         |

| D002*           | Vdr           | RAM Data Retention<br>Voltage (Note 1)                                  | -           | 1.5        | -                                     | V        |                                                                                                              |

| D003            | VPOR          | <b>VDD Start Voltage</b> to<br>ensure internal<br>Power-on Reset signal | -           | Vss        | -                                     | V        | See section on Power-on Reset for details                                                                    |

| D004*<br>D004A* | SVDD          | <b>VDD Rise Rate</b> to<br>ensure internal<br>Power-on Reset signal     | 0.05<br>TBD | -          | -                                     | V/ms     | PWRT enabled (PWRTE bit clear)<br>PWRT disabled (PWRTE bit set)<br>See section on Power-on Reset for details |

| D005            | VBOR          | Brown-out Reset<br>voltage trip point                                   | 3.65        | -          | 4.35                                  | V        | BODEN bit set                                                                                                |

| D010            | IDD           | Supply Current<br>(Note 2, 5)                                           | -           | 2.7        | 5                                     | mA       | XT, RC osc modes<br>Fosc = 4 MHz, VDD = 5.5V (Note 4)                                                        |

| D013            |               |                                                                         | -           | 10         | 20                                    | mA       | HS osc mode<br>Fosc = 20 MHz, VDD = 5.5V                                                                     |

| D020            | IPD           | Power-down Current                                                      | -           | 10.5       | 42                                    | μA       | VDD = 4.0V, WDT enabled,-40°C to +85°C                                                                       |

|                 |               | (Note 3, 5)                                                             | -           | 1.5        | 16                                    | μA       | VDD = $4.0V$ , WDT disabled, 0°C to $+70°C$                                                                  |

| D021            |               |                                                                         | -           | 1.5        | 19                                    | μA       | VDD = 4.0V, WDT disabled,-40°C to +85°C                                                                      |

| D021B           |               |                                                                         | -           | 2.5        | 19                                    | μA       | VDD = 4.0V, WDT disabled,-40°C to +125°C                                                                     |

| D000*           | Abaroz        | Module Differential<br>Current (Note 6)                                 |             | 6.0        | 20                                    |          |                                                                                                              |

| D022*<br>D022A* |               | Watchdog Timer<br>Brown-out Reset                                       | -           | 6.0<br>TBD | 20<br>200                             | μΑ       | WDTE BIT SET, VDD = 4.0V<br>BODEN bit set, VDD = 5.0V                                                        |

| DUZZA           | $\Delta$ IBOR | BIOWII-OUL Reset                                                        | -           | עסו        | 200                                   | μA       | DODEN DIL SEL, VDD = 5.0V                                                                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD,

$\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc mode, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: This is the voltage where the device enters the Brown-out Reset. When BOR is enabled, the device will perform a brown-out reset when VDD falls below VBOR.

#### 13.4.2 TIMING CONDITIONS

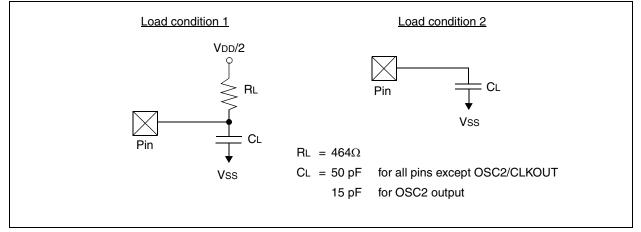

The temperature and voltages specified in Table 13-1 apply to all timing specifications unless otherwise noted. Figure 13-4 specifies the load conditions for the timing specifications.

### TABLE 13-1: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

| AC CHARACTERISTICS | Standard Operating Conditions (unless otherwise stated)                            |  |  |  |  |  |  |  |

|--------------------|------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                    | Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial        |  |  |  |  |  |  |  |

|                    | -40°C $\leq$ TA $\leq$ +85°C for industrial                                        |  |  |  |  |  |  |  |

|                    | $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for extended                             |  |  |  |  |  |  |  |

|                    | Operating voltage VDD range as described in DC spec Section 13.1 and Section 13.2. |  |  |  |  |  |  |  |

|                    | LC parts operate for commercial/industrial temp's only.                            |  |  |  |  |  |  |  |

#### FIGURE 13-4: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

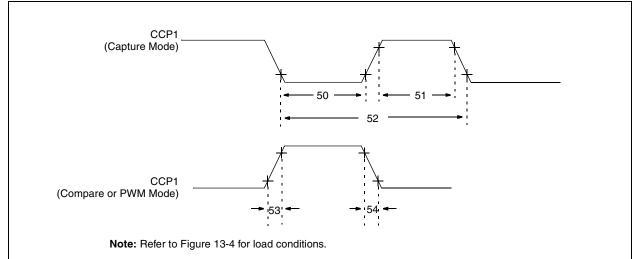

#### FIGURE 13-10: CAPTURE/COMPARE/PWM TIMINGS

#### TABLE 13-6: CAPTURE/COMPARE/PWM REQUIREMENTS

| Param<br>No. | Sym  |                         | Characteristi         | Min       | Тур†                  | Max | Units | Conditions |                                    |

|--------------|------|-------------------------|-----------------------|-----------|-----------------------|-----|-------|------------|------------------------------------|

| 50*          | TccL | CCP1 input low          | No Prescaler          |           | 0.5Tcy + 20           | —   | —     | ns         |                                    |

|              |      | time                    | With Prescaler        | PIC16CXX  | 10                    | _   | _     | ns         |                                    |

|              |      |                         |                       | PIC16LCXX | 20                    | _   | _     | ns         |                                    |

| 51*          | ТссН | cH CCP1 input high time | No Prescaler          |           | 0.5TCY + 20           | _   | _     | ns         |                                    |

|              |      |                         | With Prescaler        | PIC16CXX  | 10                    | -   | —     | ns         |                                    |

|              |      |                         |                       | PIC16LCXX | 20                    | _   | _     | ns         |                                    |

| 52*          | TccP | CCP1 input period       |                       |           | <u>3Tcy + 40</u><br>N | -   | —     | ns         | N = prescale<br>value (1,4, or 16) |

| 53*          | TccR | CCP1 output rise        | time                  | PIC16CXX  | —                     | 10  | 25    | ns         |                                    |

|              |      | PIC16                   |                       | PIC16LCXX | —                     | 25  | 45    | ns         |                                    |

| 54*          | TccF | CCP1 output fall t      | CCP1 output fall time |           | —                     | 10  | 25    | ns         |                                    |

|              |      |                         |                       | PIC16LCXX | —                     | 25  | 45    | ns         |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

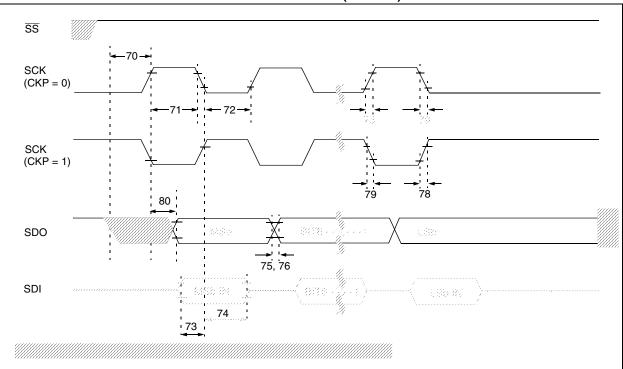

#### FIGURE 13-11: EXAMPLE SPI MASTER MODE TIMING (CKE = 0)

| Param.<br>No. | Symbol                | Characterist                              | Min         | Тур†         | Max | Units | Conditions |        |

|---------------|-----------------------|-------------------------------------------|-------------|--------------|-----|-------|------------|--------|

| 70            | TssL2scH,<br>TssL2scL | SS↓ to SCK↓ or SCK↑ input                 | Тсү         | —            | —   | ns    |            |        |

| 71            | TscH                  | SCK input high time                       | Continuous  | 1.25Tcy + 30 | —   | _     | ns         |        |

| 71A           |                       | (slave mode)                              | Single Byte | 40           |     | _     | ns         | Note 1 |

| 72            | TscL                  | SCK input low time                        | Continuous  | 1.25Tcy + 30 | _   |       | ns         |        |

| 72A           |                       | (slave mode)                              | Single Byte | 40           | _   | _     | ns         | Note 1 |

| 73            | TdiV2scH,<br>TdiV2scL | Setup time of SDI data inpu               | 100         | —            | —   | ns    |            |        |

| 73A           | Тв2в                  | Last clock edge of Byte1 to edge of Byte2 | 1.5Tcy + 40 | —            | —   | ns    | Note 1     |        |

| 74            | TscH2diL,<br>TscL2diL | Hold time of SDI data input               | to SCK edge | 100          | —   | —     | ns         |        |

| 75            | TdoR                  | SDO data output rise time                 | PIC16CXX    | _            | 10  | 25    | ns         |        |

|               |                       |                                           | PIC16LCXX   | _            | 20  | 45    | ns         |        |

| 76            | TdoF                  | SDO data output fall time                 |             | _            | 10  | 25    | ns         |        |

| 78            | TscR                  | SCK output rise time                      | PIC16CXX    | _            | 10  | 25    | ns         |        |

|               |                       | (master mode)                             | PIC16LCXX   | _            | 20  | 45    | ns         |        |

| 79            | TscF                  | SCK output fall time (maste               | er mode)    | _            | 10  | 25    | ns         |        |

| 80            | TscH2doV,             | SDO data output valid                     | PIC16CXX    | _            | _   | 50    | ns         |        |

|               | TscL2doV              | after SCK edge                            | PIC16LCXX   | _            | —   | 100   | ns         | ]      |

#### TABLE 13-7: EXAMPLE SPI MODE REQUIREMENTS (MASTER MODE, CKE = 0)

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Specification 73A is only required if specifications 71A and 72A are used.

© 1998-2013 Microchip Technology Inc.

# PIC16C62B/72A

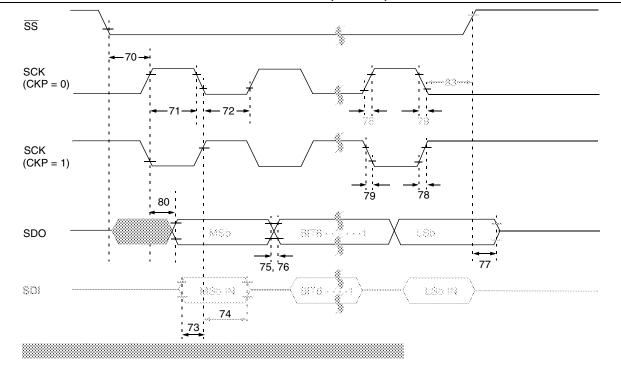

#### FIGURE 13-13: EXAMPLE SPI SLAVE MODE TIMING (CKE = 0)

### TABLE 13-9: EXAMPLE SPI MODE REQUIREMENTS (SLAVE MODE TIMING (CKE = 0)

| Param.<br>No. | Symbol                | Characterist                                                        | lic            | Min          | Тур† | Max | Units  | Conditions |

|---------------|-----------------------|---------------------------------------------------------------------|----------------|--------------|------|-----|--------|------------|

| 70            | TssL2scH,<br>TssL2scL | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ inp | Тсү            |              |      | ns  |        |            |

| 71            | TscH                  | SCK input high time                                                 | Continuous     | 1.25Tcy + 30 | —    |     | ns     |            |

| 71A           |                       | (slave mode)                                                        | Single Byte    | 40           | —    | _   | ns     | Note 1     |

| 72            | TscL                  | SCK input low time                                                  | Continuous     | 1.25Tcy + 30 | —    |     | ns     |            |

| 72A           |                       | (slave mode)                                                        | Single Byte    | 40           | —    |     | ns     | Note 1     |

| 73            | TdiV2scH,<br>TdiV2scL | Setup time of SDI data inp                                          | ut to SCK edge | 100          | —    | —   | ns     |            |

| 73A           | Тв2в                  | Last clock edge of Byte1 to<br>edge of Byte2                        | 1.5Tcy + 40    | —            | —    | ns  | Note 1 |            |

| 74            | TscH2diL,<br>TscL2diL | Hold time of SDI data inpu                                          | 100            | —            | —    | ns  |        |            |

| 75            | TdoR                  | SDO data output rise time                                           | PIC16CXX       | —            | 10   | 25  | ns     |            |

|               |                       |                                                                     | PIC16LCXX      |              | 20   | 45  | ns     |            |

| 76            | TdoF                  | SDO data output fall time                                           |                | —            | 10   | 25  | ns     |            |

| 77            | TssH2doZ              | SS↑ to SDO output hi-imp                                            | edance         | 10           | —    | 50  | ns     |            |

| 78            | TscR                  | SCK output rise time                                                | PIC16CXX       | —            | 10   | 25  | ns     |            |

|               |                       | (master mode)                                                       | PIC16LCXX      |              | 20   | 45  | ns     |            |

| 79            | TscF                  | SCK output fall time (master mode)                                  |                | —            | 10   | 25  | ns     |            |

| 80            | TscH2doV,             | SDO data output valid                                               | PIC16CXX       | —            | —    | 50  | ns     |            |

|               | TscL2doV              | after SCK edge                                                      | PIC16LCXX      |              | —    | 100 | ns     |            |

| 83            | TscH2ssH,<br>TscL2ssH | $\overline{SS}$ $\uparrow$ after SCK edge                           | •              | 1.5Tcy + 40  |      | _   | ns     |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Specification 73A is only required if specifications 71A and 72A are used.

## 14.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

The graphs and tables provided in this section are for **design guidance** and are **not tested**.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are guaranteed to operate properly only within the specified range.

The data presented in this section is a **statistical summary** of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution at 25°C. 'Max' or 'min' represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is standard deviation, over the whole temperature range.

## Graphs and Tables not available at this time.

Data is not available at this time but you may reference the *PIC16C72 Series Data Sheet* (DS39016,) DC and AC characteristic section, which contains data similar to what is expected.

## **15.0 PACKAGING INFORMATION**

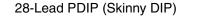

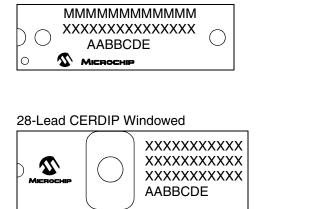

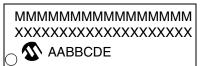

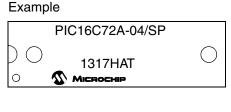

### 15.1 Package Marking Information

28-Lead SOIC

#### Example

## Example PIC16C62B-20/SO

| 28-Lead SSOP                            | Example                |

|-----------------------------------------|------------------------|

| xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx | PIC16C62B<br>20I/SS025 |

|                                         | ○                      |

| Legend: MMM       Microchip part number information         XXX       Customer specific information*         AA       Year code (last 2 digits of calendar year)         BB       Week code (week of January 1 is week '01')         C       Facility code of the plant at which wafer is manufactured         O = Outside Vendor       C = 5" Line         S = 6" Line       H = 8" Line         D       Mask revision number         E       Assembly code of the plant or country of origin in which part was assembled         Note:       In the event the full Microchip part number cannot be marked on one line, it we be carried over to the next line thus limiting the number of available character for customer specific information. |                                                      |           |                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| be carried over to the next line thus limiting the number of available character                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | XXX<br>AA<br>BB<br>C<br>D<br>E<br>Note: In the event |           | <ul> <li>Customer specific information*</li> <li>Year code (last 2 digits of calendar year)</li> <li>Week code (week of January 1 is week '01')</li> <li>Facility code of the plant at which wafer is manufactured</li> <li>O = Outside Vendor</li> <li>C = 5" Line</li> <li>S = 6" Line</li> <li>H = 8" Line</li> <li>Mask revision number</li> <li>Assembly code of the plant or country of origin in which</li> </ul> |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                      | be carrie | be carried over to the next line thus limiting the number of available character                                                                                                                                                                                                                                                                                                                                         |  |  |

Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask rev#, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

© 1998-2013 Microchip Technology Inc.

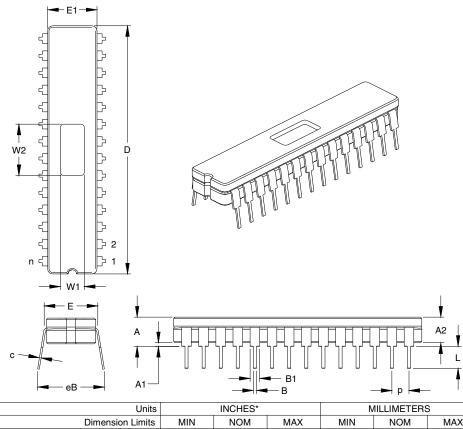

## 15.3 <u>28-Lead Ceramic Dual In-line with Window (JW) – 300 mil (CERDIP)</u>

|                            | Units     |       | INCHES |       | IV    | ILLINIL I LAG | )     |

|----------------------------|-----------|-------|--------|-------|-------|---------------|-------|

| Dimensio                   | on Limits | MIN   | NOM    | MAX   | MIN   | NOM           | MAX   |

| Number of Pins             | n         |       | 28     |       |       | 28            |       |

| Pitch                      | р         |       | .100   |       |       | 2.54          |       |

| Top to Seating Plane       | Α         | .170  | .183   | .195  | 4.32  | 4.64          | 4.95  |

| Ceramic Package Height     | A2        | .155  | .160   | .165  | 3.94  | 4.06          | 4.19  |

| Standoff                   | A1        | .015  | .023   | .030  | 0.38  | 0.57          | 0.76  |

| Shoulder to Shoulder Width | E         | .300  | .313   | .325  | 7.62  | 7.94          | 8.26  |

| Ceramic Pkg. Width         | E1        | .285  | .290   | .295  | 7.24  | 7.37          | 7.49  |

| Overall Length             | D         | 1.430 | 1.458  | 1.485 | 36.32 | 37.02         | 37.72 |

| Tip to Seating Plane       | L         | .135  | .140   | .145  | 3.43  | 3.56          | 3.68  |

| Lead Thickness             | С         | .008  | .010   | .012  | 0.20  | 0.25          | 0.30  |

| Upper Lead Width           | B1        | .050  | .058   | .065  | 1.27  | 1.46          | 1.65  |

| Lower Lead Width           | В         | .016  | .019   | .021  | 0.41  | 0.47          | 0.53  |

| Overall Row Spacing        | eB        | .345  | .385   | .425  | 8.76  | 9.78          | 10.80 |

| Window Width               | W1        | .130  | .140   | .150  | 3.30  | 3.56          | 3.81  |

| Window Length              | W2        | .290  | .300   | .310  | 7.37  | 7.62          | 7.87  |

| *0 · // D ·                |           |       |        |       |       |               |       |

\*Controlling Parameter JEDEC Equivalent: MO-058 Drawing No. C04-080

© 1998-2013 Microchip Technology Inc.

# PIC16C62B/72A

| PIR1 Register                                                  | 9, 15      |

|----------------------------------------------------------------|------------|

| ADIF Bit                                                       |            |

| CCP1IF Bit                                                     |            |

| SSPIF Bit                                                      |            |

| TMR1IF Bit                                                     |            |

| TMR2IF Bit                                                     |            |

| Pointer, FSR                                                   |            |

| PORTA                                                          |            |

| Analog Port Pins                                               |            |

| PORTA Register                                                 |            |

| RA3:RA0 and RA5 Port Pins                                      |            |

| RA4/T0CKI Pin                                                  |            |

| RA5/SS/AN4 Pin                                                 |            |

| TRISA Register                                                 |            |

| PORTB                                                          |            |

| PORTB Register                                                 |            |

| Pull-up Enable (RBPU Bit)                                      |            |

| RB0/INT Edge Select (INTEDG Bit)                               |            |

| RB0/INT Pin, External                                          |            |

| RB3:RB0 Port Pins                                              |            |

| RB7:RB4 Interrupt on Change                                    |            |

| RB7:RB4 Interrupt on Change                                    |            |

| Enable (RBIE Bit)                                              | 13, 63     |

| RB7:RB4 Interrupt on Change                                    | ,          |

| Flag (RBIF Bit)                                                | 13, 21, 63 |

| RB7:RB4 Port Pins                                              |            |

| TRISB Register                                                 | 10, 21     |

| PORTC                                                          | 6          |

| Block Diagram                                                  | 23         |

| PORTC Register                                                 | 9, 23      |

| RC0/T1OSO/T1CKI Pin                                            | 6          |

| RC1/T1OSI Pin                                                  |            |

| RC2/CCP1 Pin                                                   | 6          |

| RC3/SCK/SCL Pin                                                |            |

| RC4/SDI/SDA Pin                                                |            |

| RC5/SDO Pin                                                    | 6, 39      |

| RC6 Pin                                                        | 6          |

| RC7 Pin                                                        |            |

| TRISC Register                                                 | 10, 23     |

| Postscaler, Timer2                                             |            |

| Select (TOUTPS3:TOUTPS0 Bits)                                  |            |

| Postscaler, WDT                                                |            |

| Assignment (PSA Bit)                                           |            |

| Block Diagram                                                  |            |

| Rate Select (PS2:PS0 Bits)                                     |            |

| Switching Between Timer0 and WDT                               |            |

| Power-on Reset (POR)                                           |            |

| Oscillator Start-up Timer (OST)                                | 55, 59     |

| POR Status (POR Bit)                                           |            |

| Power Control (PCON) Register                                  |            |

| Power-down (PD Bit)                                            | 11, 57     |

| Power-on Reset Circuit, External                               |            |

| Power-up Timer (PWRT)                                          |            |

| PWRT Enable (PWRTE Bit)                                        |            |

| Time-out (TO Bit)                                              |            |

| Time-out Sequence                                              |            |

| Timing Diagram                                                 |            |

| Prescaler, Capture                                             |            |

| Prescaler, Timer0                                              |            |

| Assignment (PSA Bit)                                           |            |

| Block Diagram                                                  |            |

| Rate Select (PS2:PS0 Bits)<br>Switching Between Timer0 and WDT | 12, 25     |

|                                                                |            |

| Prescaler, Timer1<br>Select (T1CKPS1:T1CKPS0 Bits)             |            |

|                                                                |            |

| Prescaler, Timer2                       | 36     |

|-----------------------------------------|--------|

| Select (T2CKPS1:T2CKPS0 Bits)           | 31     |

| PRO MATE® II Universal Programmer       | 77     |

| Program Counter                         |        |

| PCL Register                            |        |

| PCLATH Register                         |        |

| Reset Conditions                        | 60     |

| Program Memory                          | 7      |

| Interrupt Vector                        | 7      |

| Paging                                  | 7, 17  |

| Program Memory Map                      | 7      |

| Reset Vector                            | 7      |

| Program Verification                    | 66     |

| Programming Pin (Vpp)                   | 6      |

| Programming, Device Instructions        | 67     |

| PWM (CCP Module)                        | 36     |

| Block Diagram                           | 36     |

| CCPR1H:CCPR1L Registers                 |        |

| Duty Cycle                              | 36     |

| Example Frequencies/Resolutions         | 37     |

| Output Diagram                          | 36     |

| Period                                  | 36     |

| Set-Up for PWM Operation                | 37     |

| TMR2 to PR2 Match                       | 31, 36 |

| TMR2 to PR2 Match Enable (TMR2IE Bit) . | 14     |

| TMR2 to PR2 Match Flag (TMR2IF Bit)     | 15     |

|                                         |        |

## Q

| Q-Clock |  |

|---------|--|

| R       |  |

| Register File                        | 8      |

|--------------------------------------|--------|

| Register File Map                    |        |

| Reset                                | 55, 57 |

| Block Diagram                        | 58     |

| Reset Conditions for All Registers   | 61     |

| Reset Conditions for PCON Register   | 60     |

| Reset Conditions for Program Counter | 60     |

| Reset Conditions for STATUS Register | 60     |

| Timing Diagram                       | 92     |

| Revision History                     | 111    |

## S

| SEEVAL® Evaluation and Programming System SLEEP |    |

|-------------------------------------------------|----|

| Software Simulator (MPLAB-SIM)                  |    |

| Special Features of the CPU                     | 55 |

| Special Function Registers                      | 9  |

| Speed, Operating                                | 1  |

| SPI (SSP Module)                                |    |

| Block Diagram                                   |    |

| Buffer Full Status (BF Bit)                     |    |

| Clock Edge Select (CKE Bit)                     |    |

| Clock Polarity Select (CKP Bit)                 |    |

| Data Input Sample Phase (SMP Bit)               |    |

| Mode Select (SSPM3:SSPM0 Bits)                  |    |

| Receive Overflow Indicator (SSPOV Bit)          | 47 |

| Serial Clock (RC3/SCK/SCL)                      |    |

| Serial Data In (RC4/SDI/SDA)                    |    |

| Serial Data Out (RC5/SDO)                       |    |

| Slave Select (RA5/SS/AN4)                       |    |

| Synchronous Serial Port Enable (SSPEN Bit)      |    |

|                                                 |    |