Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I²C, SPI                                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                 |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc62b-04i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-1 PIC16C62B/PIC16C72A PINOUT DESCRIPTION

| Pin Name                    | DIP<br>Pin#         | SOIC<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                                  |

|-----------------------------|---------------------|--------------|---------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN                  | 9                   | 9            | I             | ST/CMOS <sup>(3)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                        |

| OSC2/CLKOUT                 | 10                  | 10           | 0             | _                      | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/Vpp                    | 1                   | 1            | I/P           | ST                     | Master clear (reset) input or programming voltage input. This pin is an active low reset to the device.                                                                                                      |

|                             |                     |              |               |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                          |

| RA0/AN0 <sup>(4)</sup>      | 2                   | 2            | I/O           | TTL                    | RA0 can also be analog input 0                                                                                                                                                                               |

| RA1/AN1 <sup>(4)</sup>      | 3                   | 3            | I/O           | TTL                    | RA1 can also be analog input 1                                                                                                                                                                               |

| RA2/AN2 <sup>(4)</sup>      | 4                   | 4            | I/O           | TTL                    | RA2 can also be analog input 2                                                                                                                                                                               |

| RA3/AN3/VREF <sup>(4)</sup> | 5                   | 5            | I/O           | TTL                    | RA3 can also be analog input 3 or analog reference voltage                                                                                                                                                   |

| RA4/T0CKI                   | 6                   | 6            | I/O           | ST                     | RA4 can also be the clock input to the Timer0 module.<br>Output is open drain type.                                                                                                                          |

| RA5/SS/AN4 <sup>(4)</sup>   | 7                   | 7            | I/O           | TTL                    | RA5 can also be analog input 4 or the slave select for the synchronous serial port.                                                                                                                          |

|                             |                     |              |               |                        | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                                |

| RB0/INT                     | 21                  | 21           | I/O           | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                                  |

| RB1                         | 22                  | 22           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB2                         | 23                  | 23           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB3                         | 24                  | 24           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB4                         | 25                  | 25           | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                     |

| RB5                         | 26                  | 26           | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                     |

| RB6                         | 27                  | 27           | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming clock.                                                                                                                                                           |

| RB7                         | 28                  | 28           | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming data.                                                                                                                                                            |

|                             |                     |              |               |                        | PORTC is a bi-directional I/O port.                                                                                                                                                                          |

| RC0/T1OSO/T1CKI             | 11                  | 11           | I/O           | ST                     | RC0 can also be the Timer1 oscillator output or Timer1<br>clock input.                                                                                                                                       |

| RC1/T1OSI                   | 12                  | 12           | I/O           | ST                     | RC1 can also be the Timer1 oscillator input.                                                                                                                                                                 |

| RC2/CCP1                    | 13                  | 13           | I/O           | ST                     | RC2 can also be the Capture1 input/Compare1 output/<br>PWM1 output.                                                                                                                                          |

| RC3/SCK/SCL                 | 14                  | 14           | I/O           | ST                     | RC3 can also be the synchronous serial clock input/output for both SPI and I <sup>2</sup> C modes.                                                                                                           |

| RC4/SDI/SDA                 | 15                  | 15           | I/O           | ST                     | RC4 can also be the SPI Data In (SPI mode) or data I/O ( $I^2C$ mode).                                                                                                                                       |

| RC5/SDO                     | 16                  | 16           | I/O           | ST                     | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                                 |

| RC6                         | 17                  | 17           | I/O           | ST                     |                                                                                                                                                                                                              |

| RC7                         | 18                  | 18           | I/O           | ST                     |                                                                                                                                                                                                              |

| Vss                         | 8, 19               | 8, 19        | Р             | _                      | Ground reference for logic and I/O pins.                                                                                                                                                                     |

| Vdd                         | 20                  | 20           | Р             | —                      | Positive supply for logic and I/O pins.                                                                                                                                                                      |

| Legend: I = input           | O = outp<br>— = Not |              | I/O =         | input/output           | P = power or program<br>ST = Schmitt Trigger input                                                                                                                                                           |

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in serial programming mode.

This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

4: The A/D module is not available on the PIC16C62B.

#### 2.2.2.2 OPTION\_REG REGISTER

Г

The OPTION\_REG register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known as the prescaler), the External INT Interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

### REGISTER 2-2: OPTION\_REG REGISTER (ADDRESS 81h)

| R/W-1    | R/W-1                          | R/W-1                                                                                                            | R/W-1    | R/W-1        | R/W-1     | R/W-1   | R/W-1 |                  |  |  |  |  |  |

|----------|--------------------------------|------------------------------------------------------------------------------------------------------------------|----------|--------------|-----------|---------|-------|------------------|--|--|--|--|--|

| RBPU     | INTEDG                         | TOCS                                                                                                             | T0SE     | PSA          | PS2       | PS1     | PS0   | R = Readable bit |  |  |  |  |  |

| bit7     |                                |                                                                                                                  |          |              |           |         | bit0  | W = Writable bit |  |  |  |  |  |

|          | - n = Value at POR reset       |                                                                                                                  |          |              |           |         |       |                  |  |  |  |  |  |

| bit 7:   | RBPU: PORTB Pull-up Enable bit |                                                                                                                  |          |              |           |         |       |                  |  |  |  |  |  |

|          |                                | <ul> <li>1 = PORTB pull-ups are disabled</li> <li>0 = PORTB pull-ups are enabled for all PORTB inputs</li> </ul> |          |              |           |         |       |                  |  |  |  |  |  |

|          | 0 = PORTI                      | B pull-ups a                                                                                                     | are enat | oled for all | PORTBing  | outs    |       |                  |  |  |  |  |  |

| bit 6:   | INTEDG: I                      | nterrupt Ed                                                                                                      | lge Sele | ct bit       |           |         |       |                  |  |  |  |  |  |

|          | 1 = Interru                    | pt on rising                                                                                                     | edge o   | f RB0/INT    | pin       |         |       |                  |  |  |  |  |  |

|          | 0 = Interru                    | pt on falling                                                                                                    | g edge o | f RB0/INT    | - pin     |         |       |                  |  |  |  |  |  |

| bit 5:   | TOCS: TM                       | R0 Clock S                                                                                                       | ource S  | elect bit    |           |         |       |                  |  |  |  |  |  |

|          | 1 = Transit                    | ion on RA4                                                                                                       | /T0CKI   | pin          |           |         |       |                  |  |  |  |  |  |

|          |                                | al instruction                                                                                                   |          | •            | (OUT)     |         |       |                  |  |  |  |  |  |

| bit 4:   | TOSE: TMI                      |                                                                                                                  | -        | •            | ,         |         |       |                  |  |  |  |  |  |

| Dit 4.   |                                |                                                                                                                  |          |              | on RA4/T0 | CKI nin |       |                  |  |  |  |  |  |

|          |                                | •                                                                                                                |          |              | on RA4/T0 | •       |       |                  |  |  |  |  |  |

| hit 0.   |                                |                                                                                                                  | •        |              |           | o p     |       |                  |  |  |  |  |  |

| bit 3:   | PSA: Pres                      | •                                                                                                                |          |              |           |         |       |                  |  |  |  |  |  |

|          |                                | tler is assig<br>tler is assig                                                                                   |          |              | modulo    |         |       |                  |  |  |  |  |  |

|          |                                | 0                                                                                                                |          |              | module    |         |       |                  |  |  |  |  |  |

| bit 2-0: | PS2:PS0:                       | Prescaler F                                                                                                      | Rate Sel | ect bits     |           |         |       |                  |  |  |  |  |  |

|          | Bit Value                      | TMR0 Rat                                                                                                         | e WD     | Г Rate       |           |         |       |                  |  |  |  |  |  |

|          | 000                            | 1:2                                                                                                              | 1:       | 1            |           |         |       |                  |  |  |  |  |  |

|          | 001                            | 1:4                                                                                                              | 1 :      |              |           |         |       |                  |  |  |  |  |  |

|          | 010                            | 1:8                                                                                                              | 1:       |              |           |         |       |                  |  |  |  |  |  |

|          | 011                            | 1:16                                                                                                             | 1:       | -            |           |         |       |                  |  |  |  |  |  |

|          | 100                            | 1:32                                                                                                             |          | 16           |           |         |       |                  |  |  |  |  |  |

|          | 101                            | 1:64                                                                                                             |          | 32<br>64     |           |         |       |                  |  |  |  |  |  |

|          | 110                            | 1:128                                                                                                            |          | 64<br>128    |           |         |       |                  |  |  |  |  |  |

|          | 111                            | 1:256                                                                                                            |          | 120          |           |         |       |                  |  |  |  |  |  |

### 2.3 PCL and PCLATH

The program counter (PC) specifies the address of the instruction to fetch for execution. The PC is 13 bits wide. The low byte is called the PCL register and is readable and writable. The high byte is called the PCH register. This register contains the PC<12:8> bits and is not directly accessible. All updates to the PCH register go through the PCLATH register.

#### 2.3.1 STACK

The stack allows any combination of up to 8 program calls and interrupts to occur. The stack contains the return address from this branch in program execution.

Mid-range devices have an 8 level deep hardware stack. The stack space is not part of either program or data space and the stack pointer is not accessible. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RET-FIE instruction execution. PCLATH is not modified when the stack is PUSHed or POPed.

After the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

#### 2.4 Program Memory Paging

The CALL and GOTO instructions provide 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper bit of the address is provided by PCLATH<3>. The user must ensure that the page select bit is programmed to address the proper program memory page. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is popped from the stack. Therefore, manipulation of the PCLATH<3> bit is not required for the return instructions.

#### TABLE 3-1 PORTA FUNCTIONS

| Name         | Bit# | Buffer | Function                                                                                      |

|--------------|------|--------|-----------------------------------------------------------------------------------------------|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input <sup>(1)</sup>                                                   |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input <sup>(1)</sup>                                                   |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input <sup>(1)</sup>                                                   |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input <sup>(1)</sup> or VREF <sup>(1)</sup>                            |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0<br>Output is open drain type                  |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input <sup>(1)</sup> |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: The PIC16C62B does not implement the A/D module.

#### TABLE 3-2 SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name                          | Bit 7 | Bit 6 | Bit 5 | Bit 4                         | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on all other resets |

|---------|-------------------------------|-------|-------|-------|-------------------------------|-------|-------|-------|-------|-------------------------|---------------------------|

| 05h     | PORTA<br>(for PIC16C72A only) | —     | —     | RA5   | RA4                           | RA3   | RA2   | RA1   | RA0   | 0x 0000                 | 0u 0000                   |

| 05h     | PORTA<br>(for PIC16C62B only) | —     | —     | RA5   | RA4                           | RA3   | RA2   | RA1   | RA0   | xx xxxx                 | uu uuuu                   |

| 85h     | TRISA                         |       |       | PORTA | PORTA Data Direction Register |       |       |       |       | 11 1111                 | 11 1111                   |

| 9Fh     | ADCON1 <sup>(1)</sup>         |       |       |       |                               |       | PCFG2 | PCFG1 | PCFG0 | 000                     | 000                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA. Note 1: The PIC16C62B does not implement the A/D module. Maintain this register clear.

#### 5.2 <u>Timer1 Oscillator</u>

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). When the Timer1 oscillator is enabled, RC0 and RC1 pins become T1OSO and T1OSI inputs, overriding TRISC<1:0>.

The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal. Table 5-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

| TABLE 5-1 | CAPACITOR SELECTION FOR |

|-----------|-------------------------|

|           | THE TIMER1 OSCILLATOR   |

| Osc Type                                 | Freq               | C1            | C2            |  |  |  |  |  |

|------------------------------------------|--------------------|---------------|---------------|--|--|--|--|--|

| LP                                       | 32 kHz 33 pF 33 pF |               |               |  |  |  |  |  |

|                                          | 100 kHz            | 15 pF         | ्रीई वृष्ट्रे |  |  |  |  |  |

|                                          | 200 kHz            | 15 pF         | (15°pF        |  |  |  |  |  |

| These v                                  | alues are for (    | design guidar | ice only.     |  |  |  |  |  |

| Crystals Tes                             | sted:              | <u>AN</u>     |               |  |  |  |  |  |

| 32.768 kHz                               | Epson C-00         | (R32.768K-A   | $\pm$ 20 PPM  |  |  |  |  |  |

| 100 kHz                                  | Epson C 21         | 00.00 KC-P    | $\pm$ 20 PPM  |  |  |  |  |  |

| 200 kHz                                  | STD XTL 20         | 0.000 kHz     | $\pm$ 20 PPM  |  |  |  |  |  |

| of of<br>time<br>2: Sinic<br>cha<br>reso |                    |               |               |  |  |  |  |  |

### 5.3 <u>Timer1 Interrupt</u>

The TMR1 Register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow and is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled by setting TMR1 interrupt enable bit TMR1IE (PIE1<0>).

#### 5.4 <u>Resetting Timer1 using a CCP Trigger</u> <u>Output</u>

If the CCP module is configured in compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

| Note: | The special event trigger from the CCP1 |

|-------|-----------------------------------------|

|       | module will not set interrupt flag bit  |

|       | TMR1IF (PIR1<0>).                       |

Timer1 must be configured for either timer or synchronized counter mode to take advantage of this feature. If Timer1 is running in asynchronous counter mode, this reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPR1H:CCPR1L registers pair effectively becomes the period register for Timer1.

### TABLE 5-2 REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address | Name   | Bit 7   | Bit 6                                                                      | Bit 5         | Bit 4         | Bit 3         | Bit 2      | Bit 1       | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|--------|---------|----------------------------------------------------------------------------|---------------|---------------|---------------|------------|-------------|--------|-------------------------|---------------------------------|

| 0Bh,8Bh | INTCON | GIE     | PEIE                                                                       | TOIE          | INTE          | RBIE          | TOIF       | INTF        | RBIF   | 0000 000x               | 0000 000u                       |

| 0Ch     | PIR1   |         | ADIF                                                                       | -             | -             | SSPIF         | CCP1IF     | TMR2IF      | TMR1IF | -0 0000                 | -0 0000                         |

| 8Ch     | PIE1   | _       | ADIE                                                                       | -             | -             | SSPIE         | CCP1IE     | TMR2IE      | TMR1IE | -0 0000                 | -0 0000                         |

| 0Eh     | TMR1L  | Holding | g register                                                                 | r for the Lea | st Significar | t Byte of the | 16-bit TMF | R1 register |        | xxxx xxxx               | uuuu uuuu                       |

| 0Fh     | TMR1H  | Holding | Holding register for the Most Significant Byte of the 16-bit TMR1 register |               |               |               |            |             |        | xxxx xxxx               | uuuu uuuu                       |

| 10h     | T1CON  | -       | _                                                                          | T1CKPS1       | T1CKPS0       | T1OSCEN       | T1SYNC     | TMR1CS      | TMR1ON | 00 0000                 | uu uuuu                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer1 module.

#### 7.3.3 SET-UP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM on-time by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

#### TABLE 7-4 EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 5.5       |

#### TABLE 7-5 REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address | Name    | Bit 7     | Bit 6                               | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0     | Value on<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|---------|-----------|-------------------------------------|-------------|---------|---------|--------|---------|-----------|-------------------------|---------------------------------|

| 0Bh,8Bh | INTCON  | GIE       | PEIE                                | T0IE        | INTE    | RBIE    | TOIF   | INTF    | RBIF      | 0000 000x               | 0000 000u                       |

| 0Ch     | PIR1    | —         | ADIF                                | _           | —       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF    | -0 0000                 | -0 0000                         |

| 8Ch     | PIE1    | —         | ADIE                                | _           | —       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE    | -0 0000                 | -0 0000                         |

| 87h     | TRISC   | PORTC D   | ata Directio                        | on Register |         |         |        |         |           | 1111 1111               | 1111 1111                       |

| 11h     | TMR2    | Timer2 mo | odule's regis                       | ter         |         |         |        |         |           | 0000 0000               | 0000 0000                       |

| 92h     | PR2     | Timer2 mo | odule's perio                       | d register  |         |         |        |         |           | 1111 1111               | 1111 1111                       |

| 12h     | T2CON   | —         | TOUTPS3                             | TOUTPS2     | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0   | -000 0000               | -000 0000                       |

| 15h     | CCPR1L  | Capture/C | Capture/Compare/PWM register1 (LSB) |             |         |         |        |         |           | xxxx xxxx               | uuuu uuuu                       |

| 16h     | CCPR1H  | Capture/C | Capture/Compare/PWM register1 (MSB) |             |         |         |        |         | xxxx xxxx | uuuu uuuu               |                                 |

| 17h     | CCP1CON | —         | _                                   | CCP1X       | CCP1Y   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0    | 00 0000                 | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PWM and Timer2.

#### 8.3.1.2 RECEPTION

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no acknowledge ( $\overline{ACK}$ ) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set or bit SSPOV (SSPCON<6>) is set.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

#### FIGURE 8-3: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

| Receiving Address         R/W           SDA         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - </th <th>=0Receiving Data<br/>_ACK_D7XD6XD5XD4XD3XD2XD1XE<br/></th> <th></th> <th></th> | =0Receiving Data<br>_ACK_D7XD6XD5XD4XD3XD2XD1XE<br>                      |                                       |                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------|--------------------------------------|

| SSPI <u>F (PIR1&lt;3&gt;)</u><br>BF ( <u>SSPSTAT&lt;0&gt;)</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>Cleared in software</li> <li>SSPBUF register is read</li> </ul> |                                       | Bus Master<br>terminates<br>transfer |

| SSP <u>OV (SSPCON&lt;6&gt;)</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Bit SSPOV is set b                                                       | ecause the SSPBUF register is still f |                                      |

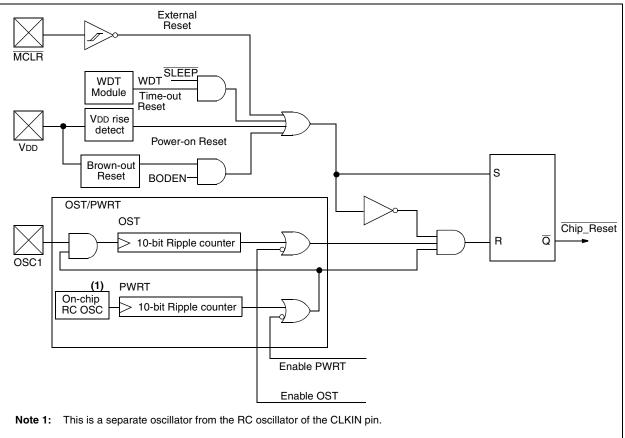

#### FIGURE 10-5: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### 10.4 Power-On Reset (POR)

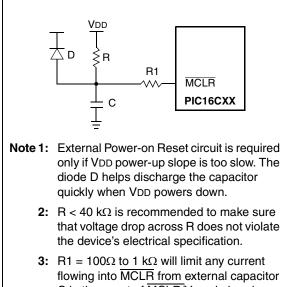

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.5V - 2.1V). To take advantage of the POR, just tie the  $\overline{\text{MCLR}}$  pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified (SVDD, parameter D004). For a slow rise time, see Figure 10-6.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met. Brown-out Reset may be used to meet the start-up conditions.

#### FIGURE 10-6: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

#### R1 = 100Ω to 1 kΩ will limit any current flowing into $\overline{MCLR}$ from external capacitor C in the event of $\overline{MCLR}/VPP$ pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

#### 10.5 Power-up Timer (PWRT)

The Power-up Timer provides a fixed nominal time-out (TPWRT, parameter #33) from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip-to-chip due to VDD, temperature and process variation. See DC parameters for details.

#### 10.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a delay of 1024 oscillator cycles (from OSC1 input) after the PWRT delay is over (TOST, parameter #32). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

Note: The OST delay may not occur when the device wakes from SLEEP.

#### 10.7 Brown-Out Reset (BOR)

The configuration bit, BODEN, can enable or disable the Brown-Out Reset circuit. If VPP falls below Vbor (parameter #35, about  $100\mu$ S), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a reset may not occur.

Once the brown-out occurs, the device will remain in brown-out reset until VDD rises above VBOR. The power-up timer then keeps the device in reset for TPWRT (parameter #33, about 72mS). If VDD should fall below VBOR during TPWRT, the brown-out reset process will restart when VDD rises above VBOR with the power-up timer reset. The power-up timer is always enabled when the brown-out reset circuit is enabled, regardless of the state of the PWRT configuration bit.

#### FIGURE 10-10: WAKE-UP FROM SLEEP THROUGH INTERRUPT

| ; a1   a2   a3   a4 ; (<br>osc1 /~//        | 21   Q2   Q3   Q4 ;<br>\/ |                       | a1 a2 a3 a4  | a1 a2 a3 a4                   | a1 a2 a3 a4      | 01 02 03 04 |

|---------------------------------------------|---------------------------|-----------------------|--------------|-------------------------------|------------------|-------------|

| CLKOUT(4)                                   |                           | Tost(2)               | /            | /                             | //               |             |

| INTF flag<br>(INTCON<1>)                    |                           |                       |              | Interrupt Latency<br>(Note 2) | -<br> <br> <br>  |             |

| GIE bit<br>(INTCON<7>)                      | <br> <br> +<br> <br>      | Processor in<br>SLEEP |              |                               | 1<br>1<br>1<br>1 |             |

| INSTRUCTION FLOW                            | 1                         |                       |              |                               |                  | · · · ·     |

| PC <u>X PC X</u>                            | PC+1                      | PC+2                  | PC+2         | X PC + 2                      | X 0004h          | X 0005h     |

| Instruction {<br>fetched { Inst(PC) = SLEEP | Inst(PC + 1)              | ,<br>,<br>,           | Inst(PC + 2) |                               | Inst(0004h)      | Inst(0005h) |

| Instruction<br>executed Inst(PC - 1)        | SLEEP                     | 1<br>1<br>1           | Inst(PC + 1) | Dummy cycle                   | Dummy cycle      | Inst(0004h) |

**Note 1:** XT, HS or LP oscillator mode assumed.

**2:** TOST = 1024TOSC (drawing not to scale) This delay will not be there for RC osc mode.

3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

#### 10.14 Program Verification/Code Protection

If the code protection bits have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip does not recommend code pro- |

|-------|----------------------------------------|

|       | tecting windowed devices.              |

#### 10.15 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution, but are readable and writable during program/verify. It is recommended that only the 4 least significant bits of the ID location are used.

For ROM devices, these values are submitted along with the ROM code.

#### 10.16 In-Circuit Serial Programming™

PIC16CXXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three more lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

For complete details of serial programming, please refer to the In-Circuit Serial Programming (ICSP™) Guide, DS30277.

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSS f,b                                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                        |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                                    |

| Description:     | If bit 'b' in register 'f' is '0', then the next instruction is executed.<br>If bit 'b' is '1', then the next instruction is discarded and a $NOP$ is executed instead, making this a 2TCY instruction. |

| CLRF             | Clear f                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CLRF f                                               |

| Operands:        | $0 \le f \le 127$                                                     |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSC f,b                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                    |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                   |

| Description:     | If bit 'b' in register 'f' is '1', then the next instruction is executed.<br>If bit 'b' in register 'f' is '0', then the next instruction is discarded, and a NOP is executed instead, making this a 2TCY instruction. |

| CLRW             | Clear W                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                          |

| Operands:        | None                                                                  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | W register is cleared. Zero bit (Z) is set.                           |

| CALL             | Call Subroutine                                                                                                                                                                                | CLRWDT           | Clear Watchdog Timer                                                                                                             |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                        | Syntax:          | [label] CLRWDT                                                                                                                   |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                             | Operands:        | None                                                                                                                             |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                               | Operation:       | $00h \rightarrow WDT$<br>0 $\rightarrow WDT$ prescaler,<br>1 $\rightarrow \overline{TO}$                                         |

| Status Affected: | None                                                                                                                                                                                           |                  | $1 \rightarrow \overline{PD}$                                                                                                    |

| Description:     | Call Subroutine. First, return address                                                                                                                                                         | Status Affected: | TO, PD                                                                                                                           |

|                  | (PC+1) is pushed onto the stack. The<br>eleven bit immediate address is loaded<br>into PC bits <10:0>. The upper bits of<br>the PC are loaded from PCLATH.<br>CALL is a two cycle instruction. | Description:     | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT. Status bits TO and PD<br>are set. |

| SUBLW            | Subtract W from Literal                                                                                                                   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SUBLW k                                                                                                                           |

| Operands:        | $0 \leq k \leq 255$                                                                                                                       |

| Operation:       | $k \text{ - } (W) \to (W)$                                                                                                                |

| Status Affected: | C, DC, Z                                                                                                                                  |

| Description:     | The W register is subtracted (2's com-<br>plement method) from the eight bit lit-<br>eral 'k'. The result is placed in the W<br>register. |

| XORLW            | Exclusive OR Literal with W                                                                                                  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                                     |

| Operands:        | $0 \leq k \leq 255$                                                                                                          |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                                |

| Status Affected: | Z                                                                                                                            |

| Description:     | The contents of the W register are<br>XOR'ed with the eight bit literal 'k'.<br>The result is placed in the W regis-<br>ter. |

| SUBWF        | Subtract W from f                                                                                                                                                                    | XORWF    |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Syntax:      | [label] SUBWF f,d                                                                                                                                                                    | Syntax:  |

| Operands:    | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                   | Operan   |

| Operation:   | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                | Operatio |

| Status       | C, DC, Z                                                                                                                                                                             | Status A |

| Affected:    |                                                                                                                                                                                      | Descrip  |

| Description: | Subtract (2's complement method) W<br>register from register 'f'. If 'd' is 0, the<br>result is stored in the W register. If 'd' is<br>1, the result is stored back in register 'f'. |          |

| XORWF            | Exclusive OR W with f                                                                                                                                                       |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                 |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                   |  |

| Status Affected: | Z                                                                                                                                                                           |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |  |

| SWAPF            | Swap Nibbles in f                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                                |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                               |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>), (f<7:4>) \rightarrow (destination<3:0>)$                                                                                        |

| Status Affected: | None                                                                                                                                                                      |

| Description:     | The upper and lower nibbles of regis-<br>ter 'f' are exchanged. If 'd' is 0, the<br>result is placed in W register. If 'd' is 1,<br>the result is placed in register 'f'. |

### 12.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB™ IDE Software

- Assemblers/Compilers/Linkers

- MPASM Assembler

- MPLAB-C17 and MPLAB-C18 C Compilers

- MPLINK/MPLIB Linker/Librarian

- Simulators

- MPLAB-SIM Software Simulator

- Emulators

- MPLAB-ICE Real-Time In-Circuit Emulator

- PICMASTER<sup>®</sup>/PICMASTER-CE In-Circuit Emulator

- ICEPIC™

- In-Circuit Debugger

- MPLAB-ICD for PIC16F877

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- Low-Cost Demonstration Boards

- SIMICE

- PICDEM-1

- PICDEM-2

- PICDEM-3

- PICDEM-17

- SEEVAL®

- KEELOQ<sup>®</sup>

#### 12.1 <u>MPLAB Integrated Development</u> <u>Environment Software</u>

- The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a Windows<sup>®</sup>-based application which contains:

- Multiple functionality

- editor

- simulator

- programmer (sold separately)

- emulator (sold separately)

- A full featured editor

- A project manager

- · Customizable tool bar and key mapping

- · A status bar

- On-line help

MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- object code

The ability to use MPLAB with Microchip's simulator, MPLAB-SIM, allows a consistent platform and the ability to easily switch from the cost-effective simulator to the full featured emulator with minimal retraining.

#### 12.2 MPASM Assembler

MPASM is a full featured universal macro assembler for all PIC MCUs. It can produce absolute code directly in the form of HEX files for device programmers, or it can generate relocatable objects for MPLINK.

MPASM has a command line interface and a Windows shell and can be used as a standalone application on a Windows 3.x or greater system. MPASM generates relocatable object files, Intel standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file which contains source lines and generated machine code, and a COD file for MPLAB debugging.

MPASM features include:

- MPASM and MPLINK are integrated into MPLAB projects.

- MPASM allows user defined macros to be created for streamlined assembly.

- MPASM allows conditional assembly for multi purpose source files.

- MPASM directives allow complete control over the assembly process.

#### 12.3 <u>MPLAB-C17 and MPLAB-C18</u> <u>C Compilers</u>

The MPLAB-C17 and MPLAB-C18 Code Development Systems are complete ANSI 'C' compilers and integrated development environments for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

#### 12.4 MPLINK/MPLIB Linker/Librarian

MPLINK is a relocatable linker for MPASM and MPLAB-C17 and MPLAB-C18. It can link relocatable objects from assembly or C source files along with precompiled libraries using directives from a linker script.

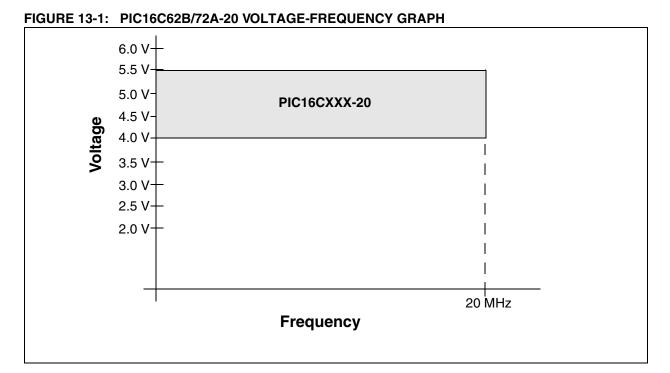

#### 13.1 DC Characteristics: PIC16C62B/72A-04 (Commercial, Industrial, Extended) PIC16C62B/72A-20 (Commercial, Industrial, Extended)

|              |               |                                                                         |         |       |                                            |            | ns (unless otherwise stated)                                   |

|--------------|---------------|-------------------------------------------------------------------------|---------|-------|--------------------------------------------|------------|----------------------------------------------------------------|

| DC CHA       | Operatir      | ng temp                                                                 | erature | e 0°C | $\leq TA \leq +70^{\circ}C$ for commercial |            |                                                                |

| DC CHA       | NACIE         |                                                                         |         |       |                                            | -40°C      | $\leq$ TA $\leq$ +85°C for industrial                          |

|              |               |                                                                         |         | -40°C | $\leq$ TA $\leq$ +125°C for extended       |            |                                                                |

| Param<br>No. | Sym           | Characteristic                                                          | Min     | Тур†  | Max                                        | Units      | Conditions                                                     |

| -            |               |                                                                         |         |       |                                            |            |                                                                |

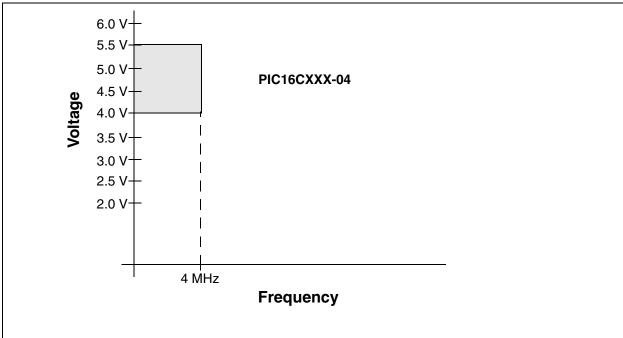

| D001         | Vdd           | Supply Voltage                                                          | 4.0     | -     | 5.5                                        | V          | XT, RC and LP osc mode                                         |

| D001A        |               |                                                                         | 4.5     | -     | 5.5                                        | V          | HS osc mode                                                    |

|              |               |                                                                         | VBOR*   | -     | 5.5                                        | V          | BOR enabled (Note 7)                                           |

| D002*        | Vdr           | RAM Data Retention <b>Voltage</b> (Note 1)                              | -       | 1.5   | -                                          | V          |                                                                |

| D003         | VPOR          | <b>VDD Start Voltage</b> to<br>ensure internal<br>Power-on Reset signal | -       | Vss   | -                                          | V          | See section on Power-on Reset for details                      |

| D004*        | SVDD          | VDD Rise Rate to                                                        | 0.05    | -     | -                                          | V/ms       |                                                                |

| D004A*       |               | ensure internal                                                         | TBD     | -     | -                                          |            | PWRT disabled (PWRTE bit set)                                  |

|              |               | Power-on Reset signal                                                   |         |       |                                            |            | See section on Power-on Reset for details                      |

| D005         | VBOR          | Brown-out Reset<br>voltage trip point                                   | 3.65    | -     | 4.35                                       | V          | BODEN bit set                                                  |

| D010         | IDD           | Supply Current                                                          | -       | 2.7   | 5                                          | mA         | XT, RC osc modes                                               |

|              |               | (Note 2, 5)                                                             |         |       |                                            |            | Fosc = 4 MHz, VDD = 5.5V (Note 4)                              |

| D013         |               |                                                                         | -       | 10    | 20                                         | mA         | HS osc mode                                                    |

| 2010         |               |                                                                         |         |       | 20                                         |            | Fosc = 20  MHz,  VDD = 5.5  V                                  |

| D020         | IPD           | Power-down Current                                                      | -       | 10.5  | 42                                         | μA         | VDD = 4.0V, WDT enabled,-40°C to +85°C                         |

|              |               | (Note 3, 5)                                                             | -       | 1.5   | 16                                         | μA         | VDD = $4.0V$ , WDT disabled, 0°C to +70°C                      |

| D021         |               |                                                                         | -       | 1.5   | 19                                         | μ <b>Α</b> | VDD = 4.0V, WDT disabled, -40°C to +85°C                       |

| D021B        |               |                                                                         | -       | 2.5   | 19                                         | μΑ         | VDD = $4.0V$ , WDT disabled, $-40^{\circ}C$ to $+125^{\circ}C$ |

|              |               | Module Differential                                                     |         |       |                                            |            |                                                                |

|              |               | Current (Note 6)                                                        |         |       |                                            |            |                                                                |

| D022*        | $\Delta IWDT$ | Watchdog Timer                                                          | -       | 6.0   | 20                                         | μA         | WDTE BIT SET, VDD = 4.0V                                       |

| D022A*       | $\Delta IBOR$ | Brown-out Reset                                                         | -       | TBD   | 200                                        | μA         | BODEN bit set, VDD = 5.0V                                      |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD,

$\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc mode, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: This is the voltage where the device enters the Brown-out Reset. When BOR is enabled, the device will perform a brown-out reset when VDD falls below VBOR.

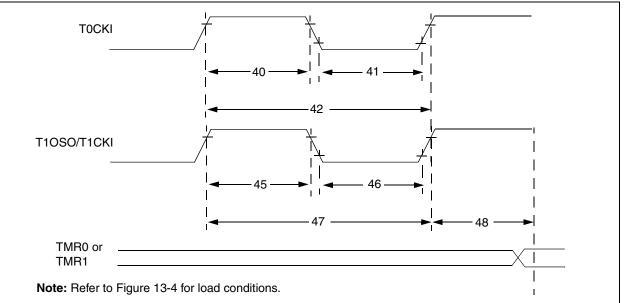

#### FIGURE 13-9: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| TABLE 13-5: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|-------------|-----------------------------------------------|

| IADEE IV V. |                                               |

| Param<br>No. | Sym       |                                                                                  | Characteristic                       |                | Min                                       | Тур† | Max   | Units | Conditions                         |  |

|--------------|-----------|----------------------------------------------------------------------------------|--------------------------------------|----------------|-------------------------------------------|------|-------|-------|------------------------------------|--|

| 40*          | Tt0H      | t0H T0CKI High Pulse Width                                                       |                                      | No Prescaler   | 0.5Tcy + 20                               | -    | -     | ns    | Must also meet                     |  |

|              |           |                                                                                  |                                      | With Prescaler | 10                                        | -    |       | ns    | parameter 42                       |  |

| 41* Tt0L     |           | T0CKI Low Pulse Width                                                            |                                      | No Prescaler   | 0.5TCY + 20                               | -    |       | ns    | Must also meet                     |  |

|              |           |                                                                                  |                                      | With Prescaler | 10                                        | -    |       | ns    | parameter 42                       |  |

| 42*          | Tt0P      |                                                                                  |                                      | No Prescaler   | Tcy + 40                                  | —    | -     | ns    |                                    |  |

|              |           |                                                                                  |                                      | With Prescaler | Greater of:<br>20 or <u>Tcy + 40</u><br>N | -    | -     | ns    | N = prescale value<br>(2, 4,, 256) |  |

| 45*          | Tt1H      | T1CKI High Time                                                                  | Synchronous, P                       | rescaler = 1   | 0.5Tcy + 20                               | —    | -     | ns    | Must also meet                     |  |

|              |           |                                                                                  | Synchronous,<br>Prescaler =<br>2,4,8 | PIC16CXX       | 15                                        | -    |       | ns    | parameter 47                       |  |

|              |           |                                                                                  |                                      | PIC16LCXX      | 25                                        | —    | _     | ns    |                                    |  |

|              |           |                                                                                  | Asynchronous                         | PIC16CXX       | 30                                        |      | _     | ns    |                                    |  |