#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, SPI                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 22                                                                           |

| Program Memory Size        | 3.5KB (2K x 14)                                                              |

| Program Memory Type        | ОТР                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 128 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc62bt-04i-ss |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

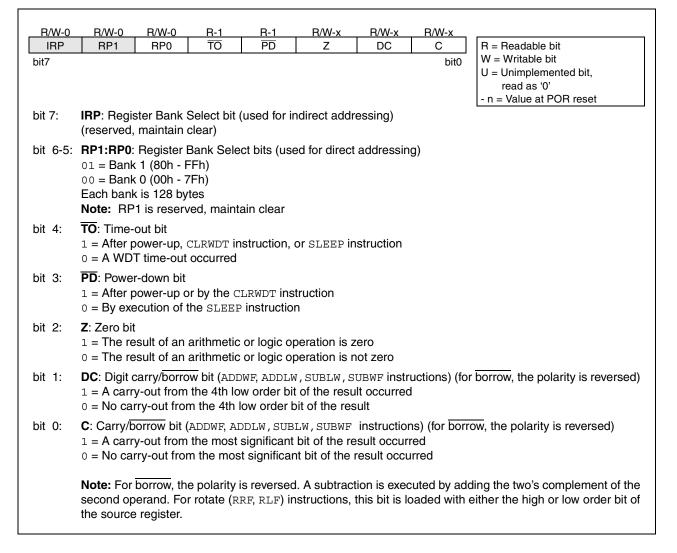

#### 2.2.2.1 STATUS REGISTER

The STATUS register, shown in Register 2-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, the write to these three bits is disabled. These bits are set or cleared according to the device logic. The TO and PD bits are not writable. The result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

- **Note 1:** The IRP and RP1 bits are reserved. Maintain these bits clear to ensure upward compatibility with future products.

- Note 2: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions.

#### REGISTER 2-1: STATUS REGISTER (ADDRESS 03h, 83h)

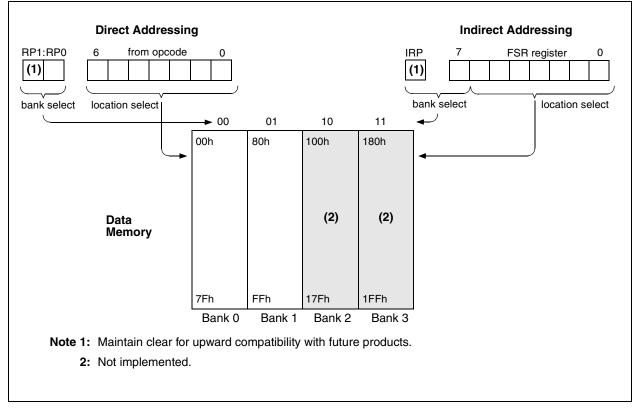

#### 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*).

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-1.

#### EXAMPLE 2-1: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

|          | movlw<br>movwf |       | ;initialize pointer<br>; to RAM |

|----------|----------------|-------|---------------------------------|

| NEXT     | clrf           | INDF  | ;clear INDF register            |

|          | incf           | FSR   | ;inc pointer                    |

|          | btfss          | FSR,4 | ;all done?                      |

|          | goto           | NEXT  | ;NO, clear next                 |

| CONTINUE |                |       |                                 |

|          | :              |       | ;YES, continue                  |

An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-3. However, IRP is not used in the PIC16C62B/72A.

#### FIGURE 2-3: DIRECT/INDIRECT ADDRESSING

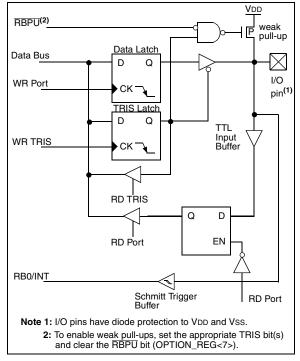

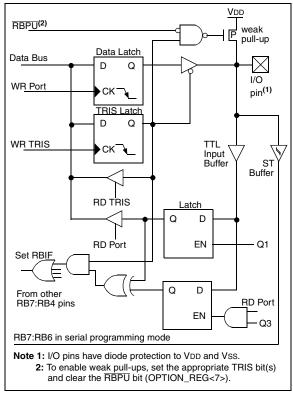

#### 3.2 PORTB and the TRISB Register

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (=1) will make the corresponding PORTB pin an input, (i.e., put the corresponding output driver in a hi-impedance mode). Clearing a TRISB bit (=0) will make the corresponding PORTB pin an output, (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit  $\overline{\text{RBPU}}$  (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

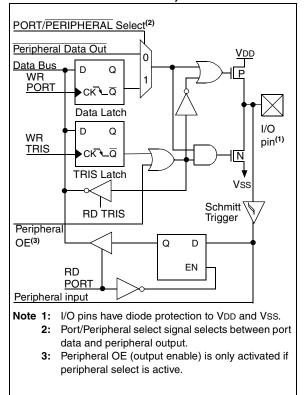

#### FIGURE 3-3: BLOCK DIAGRAM OF RB3:RB0 PINS

Four of PORTB's pins, RB7:RB4, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e. any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

RB0/INT is an external interupt pin and is configured using the INTEDG bit (OPTION\_REG<6>). RB0/INT is discussed in detail in Section 10.10.1.

## 3.3 PORTC and the TRISC Register

PORTC is an 8-bit wide bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (=1) will make the corresponding PORTC pin an input, (i.e., put the corresponding output driver in a hi-impedance mode). Clearing a TRISC bit (=0) will make the corresponding PORTC pin an output, (i.e., put the contents of the output latch on the selected pin).

PORTC is multiplexed with several peripheral functions (Table 3-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override maybe in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

#### FIGURE 3-5: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

| TABLE 8-1 | REGISTERS ASSOCIATED WITH SPI OPERATION |

|-----------|-----------------------------------------|

|           |                                         |

| Address | Name    | Bit 7                                                            | Bit 6       | Bit 5                         | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value<br>POR<br>BOF | l,   | Valu<br>all o<br>res |      |

|---------|---------|------------------------------------------------------------------|-------------|-------------------------------|-------|-------|--------|--------|--------|---------------------|------|----------------------|------|

| 0Bh,8Bh | INTCON  | GIE                                                              | PEIE        | TOIE                          | INTE  | RBIE  | T0IF   | INTF   | RBIF   | 0000 0              | 00x  | 0000                 | 000u |

| 0Ch     | PIR1    | —                                                                | ADIF        | —                             | _     | SSPIF | CCP1IF | TMR2IF | TMR1IF | -00                 | 000  | - 0                  | 0000 |

| 8Ch     | PIE1    | —                                                                | ADIE        |                               | —     | SSPIE | CCP1IE | TMR2IE | TMR1IE | -00                 | 000  | - 0                  | 0000 |

| 13h     | SSPBUF  | Synchronous Serial Port Receive Buffer/Transmit Register xxxx xx |             |                               |       |       |        |        | xxx    | uuuu                | uuuu |                      |      |

| 14h     | SSPCON  | WCOL                                                             | SSPOV       | SSPEN                         | CKP   | SSPM3 | SSPM2  | SSPM1  | SSPM0  | 0000 0              | 000  | 0000                 | 0000 |

| 94h     | SSPSTAT | SMP                                                              | CKE         | D/Ā                           | Р     | S     | R/W    | UA     | BF     | 0000 0              | 000  | 0000                 | 0000 |

| 85h     | TRISA   | _                                                                |             | PORTA Data Direction Register |       |       |        |        |        | 11 1                | 111  | 11                   | 1111 |

| 87h     | TRISC   | PORTC Data                                                       | a Direction | n Register                    |       |       |        |        |        | 1111 1              | 111  | 1111                 | 1111 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the SSP in SPI mode.

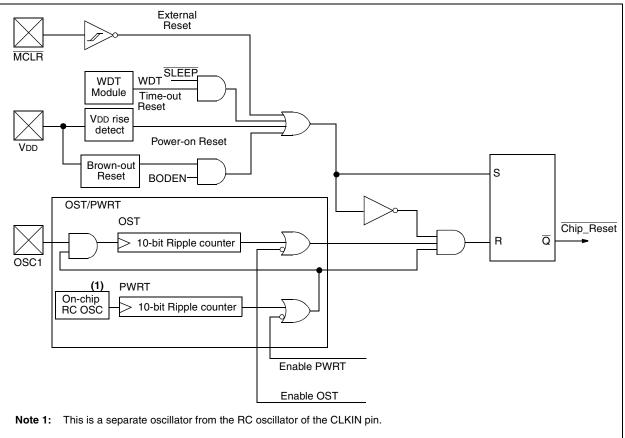

# 10.0 SPECIAL FEATURES OF THE CPU

The PIC16C62B/72A devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Mode Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- ID locations

- In-circuit serial programming<sup>™</sup> (ICSP)

These devices have a Watchdog Timer, which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The

#### FIGURE 10-1: CONFIGURATION WORD

other is the Power-up Timer (PWRT), which provides a fixed delay on power-up only and is designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

Additional information on special features is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

#### 10.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

| CP1    | CP0                                                                                                                                                                                    | CP1                                                                                                                                                                                                            | CP0  | CP1    | CP0    | _     | BODEN | CP1 | CP0 | PWRTE  | WDTE | FOSC1 | FOSC0 | Register: | CONFIG |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|--------|-------|-------|-----|-----|--------|------|-------|-------|-----------|--------|

| bit13  |                                                                                                                                                                                        | bit0 Address: 2007h                                                                                                                                                                                            |      |        |        |       |       |     |     |        |      |       |       |           |        |

|        | bit 13-8 CP1:CP0: Code Protection bits <sup>(2)</sup> 5-4: 11 = Code protection off 10 = Upper half of program memory code protected 01 = Upper 3/4th of program memory code protected |                                                                                                                                                                                                                |      |        |        |       |       |     |     |        |      |       |       |           |        |

|        |                                                                                                                                                                                        | 00 = AII                                                                                                                                                                                                       |      |        |        |       |       |     |     |        |      |       |       |           |        |

| bit 7: | I                                                                                                                                                                                      | Jnimpl                                                                                                                                                                                                         | emen | ted: R | ead as | s '1' |       |     |     |        |      |       |       |           |        |

| bit 6: |                                                                                                                                                                                        | BODEN: Brown-out Reset Enable bit <sup>(1)</sup><br>1 = BOR enabled<br>0 = BOR disabled                                                                                                                        |      |        |        |       |       |     |     |        |      |       |       |           |        |

| bit 3: |                                                                                                                                                                                        | <b>PWRTE</b> : Power-up Timer Enable bit <sup>(1)</sup><br>1 = PWRT disabled<br>0 = PWRT enabled                                                                                                               |      |        |        |       |       |     |     |        |      |       |       |           |        |

| bit 2: | :                                                                                                                                                                                      | WDTE: Watchdog Timer Enable bit<br>1 = WDT enabled<br>0 = WDT disabled                                                                                                                                         |      |        |        |       |       |     |     |        |      |       |       |           |        |

| bit 1- |                                                                                                                                                                                        | FOSC1:FOSC0: Oscillator Selection bits<br>11 = RC oscillator<br>10 = HS oscillator<br>01 = XT oscillator<br>00 = LP oscillator                                                                                 |      |        |        |       |       |     |     |        |      |       |       |           |        |

| Note   |                                                                                                                                                                                        | Enabling Brown-out Reset automatically enables Power-up Timer (PWRT), regardless of the value of bit PWRTE. All of the CP1:CP0 pairs must be given the same value to enable the code protection scheme listed. |      |        |        |       |       |     |     | PWRTE. |      |       |       |           |        |

#### FIGURE 10-5: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### 10.8 <u>Time-out Sequence</u>

When a POR reset occurs, the PWRT delay starts (if enabled). When PWRT ends, the OST counts 1024 oscillator cycles (LP, XT, HS modes only). When OST completes, the device comes out of reset. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all.

If MCLR is kept low long enough, the time-outs will expire. Bringing MCLR high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16CXXX device operating in parallel.

#### **Status Register**

Table 10-5 shows the reset conditions for the STATUS, PCON and PC registers, while Table 10-6 shows the reset conditions for all the registers.

#### 10.9 <u>Power Control/Status Register</u> (PCON)

The  $\overline{\text{BOR}}$  bit is unknown on Power-on Reset. If the Brown-out Reset circuit is used, the  $\overline{\text{BOR}}$  bit must be set by the user and checked on subsequent resets to see if it was cleared, indicating a Brown-out has occurred.

POR (Power-on Reset Status bit) is cleared on a Power-on Reset and unaffected otherwise. The user

| IRP | RP1 | RP0 | TO | PD | Z | DC | С |  |

|-----|-----|-----|----|----|---|----|---|--|

|     |     |     |    |    |   |    |   |  |

| POR BOF |

|---------|

|---------|

TABLE 10-3 TIME-OUT IN VARIOUS SITUATIONS

| Oppillator Configuration | Power              | -up      | Brown out        | Wake-up from |  |

|--------------------------|--------------------|----------|------------------|--------------|--|

| Oscillator Configuration | PWRTE = 0PWRTE = 1 |          | Brown-out        | SLEEP        |  |

| XT, HS, LP               | 72 ms + 1024Tosc   | 1024Tosc | 72 ms + 1024Tosc | 1024Tosc     |  |

| RC                       | 72 ms              |          | 72 ms            | —            |  |

#### TABLE 10-4 STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | ТО | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset                                          |

| 0   | x   | 0  | x  | Illegal, TO is set on POR                               |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

#### TABLE 10-5 RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

#### 10.13 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D and disable external clocks. Pull all I/O pins that are hi-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC, parameter D042).

#### 10.13.1 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- 1. External reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change, or some Peripheral Interrupts.

External  $\overline{\text{MCLR}}$  Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from SLEEP:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. CCP capture mode interrupt.

- Special event trigger (Timer1 in asynchronous mode using an external clock. CCP1 is in compare mode).

- 4. SSP (Start/Stop) bit detect interrupt.

- 5. SSP transmit or receive in slave mode (SPI/I<sup>2</sup>C).

- 6. USART RX or TX (synchronous slave mode).

Other peripherals cannot generate interrupts since during SLEEP, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is

regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device resumes execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, a NOP should follow the SLEEP instruction.

#### 10.13.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

<sup>© 1998-2013</sup> Microchip Technology Inc.

# 11.1 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                       |

|------------------|-------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                |

| Operands:        | $0 \leq k \leq 255$                                                                                                     |

| Operation:       | $(W) + k \to (W)$                                                                                                       |

| Status Affected: | C, DC, Z                                                                                                                |

| Description:     | The contents of the W register are<br>added to the eight bit literal 'k' and the<br>result is placed in the W register. |

| ANDWF            | AND W with f                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                             |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                   |

| Status Affected: | Z                                                                                                                                                           |

| Description:     | AND the W register with register 'f'. If<br>'d' is 0, the result is stored in the W<br>register. If 'd' is 1, the result is stored<br>back in register 'f'. |

| ADDWF            | Add W and f                                                                                                                                                                 |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                             |  |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                    |  |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result is<br>stored in the W register. If 'd' is 1, the<br>result is stored back in register 'f'. |  |  |  |  |  |  |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BCF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ANDLW            | AND Literal with W                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                            |

| Operands:        | $0 \le k \le 255$                                                                                                   |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                     |

| Status Affected: | Z                                                                                                                   |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal 'k'.<br>The result is placed in the W register. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

stand-alone mode the PRO MATE II can read, verify or program PIC devices. It can also set code-protect bits in this mode.

#### 12.11 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, lowcost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

PICSTART Plus supports all PIC devices with up to 40 pins. Larger pin count devices such as the PIC16C92X, and PIC17C76X may be supported with an adapter socket. PICSTART Plus is CE compliant.

#### 12.12 <u>SIMICE Entry-Level</u> <u>Hardware Simulator</u>

SIMICE is an entry-level hardware development system designed to operate in a PC-based environment with Microchip's simulator MPLAB-SIM. Both SIMICE and MPLAB-SIM run under Microchip Technology's MPLAB Integrated Development Environment (IDE) software. Specifically, SIMICE provides hardware simulation for Microchip's PIC12C5XX, PIC12CE5XX, and PIC16C5X families of PIC 8-bit microcontrollers. SIM-ICE works in conjunction with MPLAB-SIM to provide non-real-time I/O port emulation. SIMICE enables a developer to run simulator code for driving the target system. In addition, the target system can provide input to the simulator code. This capability allows for simple and interactive debugging without having to manually generate MPLAB-SIM stimulus files. SIMICE is a valuable debugging tool for entry-level system development.

#### 12.13 <u>PICDEM-1 Low-Cost PIC MCU</u> <u>Demonstration Board</u>

The PICDEM-1 is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The users can program the sample microcontrollers provided with the PICDEM-1 board, on a PRO MATE II or PICSTART-Plus programmer, and easily test firmware. The user can also connect the PICDEM-1 board to the MPLAB-ICE emulator and download the firmware to the emulator for testing. Additional prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push-button switches and eight LEDs connected to PORTB.

## 12.14 PICDEM-2 Low-Cost PIC16CXX Demonstration Board

The PICDEM-2 is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-2 board, on a PRO MATE II programmer or PICSTART-Plus, and easily test firmware. The MPLAB-ICE emulator may also be used with the PICDEM-2 board to test firmware. Additional prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push-button switches, a potentiometer for simulated analog input, a Serial EEPROM to demonstrate usage of the I<sup>2</sup>C bus and separate headers for connection to an LCD module and a keypad.

## 12.15 <u>PICDEM-3 Low-Cost PIC16CXXX</u> <u>Demonstration Board</u>

The PICDEM-3 is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with a LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-3 board, on a PRO MATE II programmer or PICSTART Plus with an adapter socket, and easily test firmware. The MPLAB-ICE emulator may also be used with the PICDEM-3 board to test firmware. Additional prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include an RS-232 interface, push-button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM-3 board is an LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM-3 provides an additional RS-232 interface and Windows 3.1 software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

# 12.16 PICDEM-17

The PICDEM-17 is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756, PIC17C762, and PIC17C766. All necessary hardware is included to run basic demo programs, which are supplied on a 3.5-inch disk. A programmed sample is included, and the user may erase it and program it with the other sample programs using the PRO MATE II or PICSTART Plus device programmers and easily debug

© 1998-2013 Microchip Technology Inc.

|                 |               |                                                                         | Standar     | d Opera | ating Co | ondition      | s (unless otherwise stated)                                                                                  |

|-----------------|---------------|-------------------------------------------------------------------------|-------------|---------|----------|---------------|--------------------------------------------------------------------------------------------------------------|

| DC CHA          | RACTE         | RISTICS                                                                 | Operatir    | ng temp | erature  | ∘0°C<br>-40°C | $\leq$ TA $\leq$ +70°C for commercial                                                                        |

|                 | 1             | 1                                                                       |             |         |          |               |                                                                                                              |

| Param<br>No.    | Sym           | Characteristic                                                          | Min         | Тур†    | Мах      | Units         | Conditions                                                                                                   |

| D001            | Vdd           | Supply Voltage                                                          | 2.5         | -       | 5.5      | V             | LP, XT, RC osc modes (DC - 4 MHz)                                                                            |

|                 |               |                                                                         | VBOR*       | -       | 5.5      | V             | BOR enabled (Note 7)                                                                                         |

| D002*           | Vdr           | RAM Data Retention<br>Voltage (Note 1)                                  | -           | 1.5     | -        | V             |                                                                                                              |

| D003            | VPOR          | <b>VDD Start Voltage</b> to<br>ensure internal<br>Power-on Reset signal | -           | Vss     | -        | V             | See section on Power-on Reset for details                                                                    |

| D004*<br>D004A* | SVDD          | <b>VDD Rise Rate</b> to<br>ensure internal<br>Power-on Reset signal     | 0.05<br>TBD | -<br>-  | -        | V/ms          | PWRT enabled (PWRTE bit clear)<br>PWRT disabled (PWRTE bit set)<br>See section on Power-on Reset for details |

| D005            | VBOR          | Brown-out Reset<br>voltage trip point                                   | 3.65        | -       | 4.35     | V             | BODEN bit set                                                                                                |

| D010            | IDD           | Supply Current<br>(Note 2, 5)                                           | -           | 2.0     | 3.8      | mA            | XT, RC osc modes<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                        |

| D010A           |               |                                                                         | -           | 22.5    | 48       | μA            | LP OSC MODE<br>FOSC = 32 kHz, VDD = 3.0V, WDT disabled                                                       |

| D020            | IPD           | Power-down Current                                                      | -           | 7.5     | 30       | μA            | VDD = 3.0V, WDT enabled, -40°C to +85°C                                                                      |

| D021            |               | (Note 3, 5)                                                             | -           | 0.9     | 5        | μA            | VDD = $3.0V$ , WDT disabled, $0^{\circ}C$ to $+70^{\circ}C$                                                  |

| D021A           |               |                                                                         | -           | 0.9     | 5        | μA            | VDD = 3.0V, WDT disabled, -40°C to +85°C                                                                     |

|                 |               | Module Differential<br>Current (Note 6)                                 |             |         |          |               |                                                                                                              |

| D022*           | $\Delta$ IWDT | Watchdog Timer                                                          | -           | 6.0     | 20       | μA            | WDTE BIT SET, VDD = 4.0V                                                                                     |

| D022A*          | $\Delta$ IBOR | Brown-out Reset                                                         | -           | TBD     | 200      | μA            | BODEN bit set, VDD = 5.0V                                                                                    |

#### 13.2 DC Characteristics: PIC16LC62B/72A-04 (Commercial, Industrial)

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD,

$\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- 4: For RC osc mode, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: This is the voltage where the device enters the Brown-out Reset. When BOR is enabled, the device will perform a brown-out reset when VDD falls below VBOR.

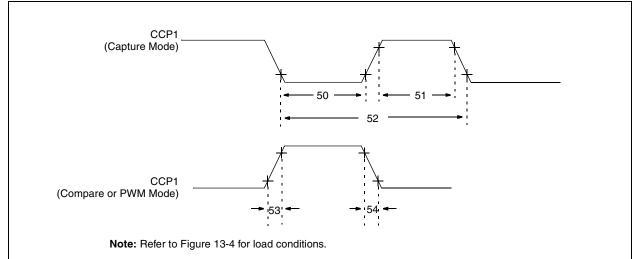

#### FIGURE 13-10: CAPTURE/COMPARE/PWM TIMINGS

#### TABLE 13-6: CAPTURE/COMPARE/PWM REQUIREMENTS

| Param<br>No. | Sym  |                    | Characteristic |           | Min                   | Тур† | Max | Units | Conditions                         |

|--------------|------|--------------------|----------------|-----------|-----------------------|------|-----|-------|------------------------------------|

| 50*          | TccL | CCP1 input low     | No Prescaler   |           | 0.5Tcy + 20           | —    | —   | ns    |                                    |

|              |      | time               | With Prescaler | PIC16CXX  | 10                    | _    | _   | ns    |                                    |

|              |      |                    |                | PIC16LCXX | 20                    | _    | _   | ns    |                                    |

| 51*          | TccH | CCP1 input high    | No Prescaler   |           | 0.5TCY + 20           | _    | _   | ns    |                                    |

|              |      | time               | With Prescaler | PIC16CXX  | 10                    | -    | —   | ns    |                                    |

|              |      |                    |                | PIC16LCXX | 20                    | _    | _   | ns    |                                    |

| 52*          | TccP | CCP1 input perior  | d              |           | <u>3Tcy + 40</u><br>N | -    | —   | ns    | N = prescale<br>value (1,4, or 16) |

| 53*          | TccR | CCP1 output rise   | time           | PIC16CXX  | —                     | 10   | 25  | ns    |                                    |

|              |      |                    |                | PIC16LCXX | —                     | 25   | 45  | ns    |                                    |

| 54*          | TccF | CCP1 output fall t | time           | PIC16CXX  | —                     | 10   | 25  | ns    |                                    |

|              |      |                    |                | PIC16LCXX | —                     | 25   | 45  | ns    |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

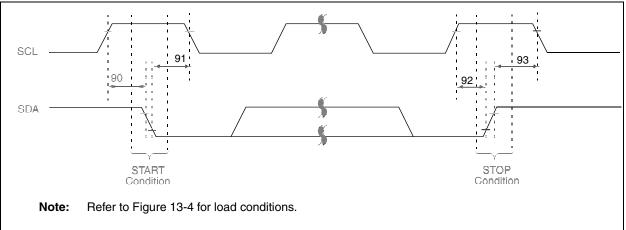

# FIGURE 13-15: I<sup>2</sup>C BUS START/STOP BITS TIMING

# TABLE 13-11: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

| Parameter<br>No. | Sym     | Charac          | teristic     | Min  | Ту<br>р | Max | Unit<br>s | Conditions                        |

|------------------|---------|-----------------|--------------|------|---------|-----|-----------|-----------------------------------|

| 90*              | TSU:STA | START condition | 100 kHz mode | 4700 |         | —   | ns        | Only relevant for repeated        |

|                  |         | Setup time      | 400 kHz mode | 600  | _       | —   |           | START condition                   |

| 91*              | THD:STA | START condition | 100 kHz mode | 4000 |         | —   | ns        | After this period the first clock |

|                  |         | Hold time       | 400 kHz mode | 600  |         | —   |           | pulse is generated                |

| 92*              | TSU:STO | STOP condition  | 100 kHz mode | 4700 |         | —   | ns        |                                   |

|                  |         | Setup time      | 400 kHz mode | 600  |         | —   |           |                                   |

| 93               | THD:STO | STOP condition  | 100 kHz mode | 4000 |         | —   | ns        |                                   |

|                  |         | Hold time       | 400 kHz mode | 600  | _       | —   |           |                                   |

These parameters are characterized but not tested.

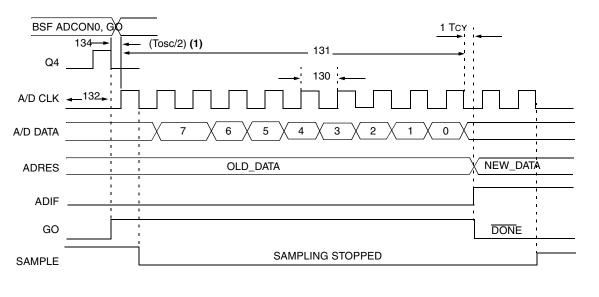

## FIGURE 13-17: A/D CONVERSION TIMING

**Note 1:** If the A/D clock source is selected as RC, a time of TCY is added before the A/D clock starts. This allows the SLEEP instruction to be executed.

| Param | Sym  | Characteristic                                    |                         | Min    | Typ†   | Max | Unit | Conditions                                                                                                                                                                                                                         |

|-------|------|---------------------------------------------------|-------------------------|--------|--------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.   |      |                                                   |                         |        |        |     | S    |                                                                                                                                                                                                                                    |

| 130   | TAD  | A/D clock period                                  | PIC16CXX                | 1.6    |        |     | μs   | Tosc based, VREF $\geq 3.0V$                                                                                                                                                                                                       |

|       |      |                                                   | PIC16LCXX               | 2.0    |        | -   | μs   | Tosc based, VREF full range                                                                                                                                                                                                        |

|       |      |                                                   | PIC16CXX                | 2.0    | 4.0    | 6.0 | μS   | A/D RC Mode                                                                                                                                                                                                                        |

|       |      |                                                   | PIC16LCXX               | 3.0    | 6.0    | 9.0 | μS   | A/D RC Mode                                                                                                                                                                                                                        |

| 131   | TCNV | Conversion time (not including S/H time) (Note 1) |                         | 11     |        | 11  | Tad  |                                                                                                                                                                                                                                    |

| 132   | TACQ | Acquisition time                                  |                         | Note 2 | 20     |     | μS   |                                                                                                                                                                                                                                    |

|       |      |                                                   |                         | 5*     | _      | _   | μs   | The minimum time is the<br>amplifier settling time. This<br>may be used if the "new" input<br>voltage has not changed by<br>more than 1 LSb (i.e., 20.0 mV<br>@ 5.12V) from the last sam-<br>pled voltage (as stated on<br>CHOLD). |

| 134   | TGO  | Q4 to A/D clock start                             |                         |        | Tosc/2 |     |      | If the A/D clock source is<br>selected as RC, a time of TCY<br>is added before the A/D clock<br>starts. This allows the SLEEP<br>instruction to be executed.                                                                       |

| 135   | Tswc | Switching from conve<br>time                      | $rt \rightarrow sample$ | 1.5    |        |     | Tad  |                                                                                                                                                                                                                                    |

#### TABLE 13-14: A/D CONVERSION REQUIREMENTS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** ADRES register may be read on the following TCY cycle.

2: See Section 9.1 for min conditions.

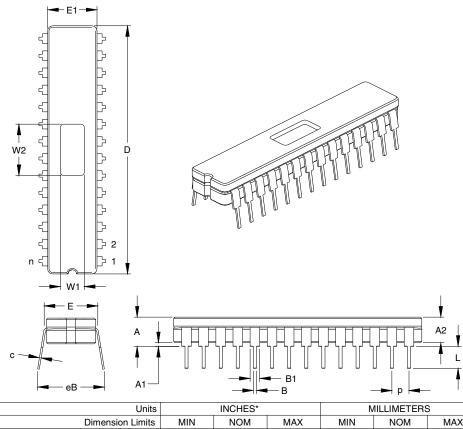

# 15.3 <u>28-Lead Ceramic Dual In-line with Window (JW) – 300 mil (CERDIP)</u>

|                            |           | INCHES |       | IVITELIIVIE I ERG |       |       |       |

|----------------------------|-----------|--------|-------|-------------------|-------|-------|-------|

| Dimensio                   | on Limits | MIN    | NOM   | MAX               | MIN   | NOM   | MAX   |

| Number of Pins             | n         |        | 28    |                   |       | 28    |       |

| Pitch                      | р         |        | .100  |                   |       | 2.54  |       |

| Top to Seating Plane       | Α         | .170   | .183  | .195              | 4.32  | 4.64  | 4.95  |

| Ceramic Package Height     | A2        | .155   | .160  | .165              | 3.94  | 4.06  | 4.19  |

| Standoff                   | A1        | .015   | .023  | .030              | 0.38  | 0.57  | 0.76  |

| Shoulder to Shoulder Width | E         | .300   | .313  | .325              | 7.62  | 7.94  | 8.26  |

| Ceramic Pkg. Width         | E1        | .285   | .290  | .295              | 7.24  | 7.37  | 7.49  |

| Overall Length             | D         | 1.430  | 1.458 | 1.485             | 36.32 | 37.02 | 37.72 |

| Tip to Seating Plane       | L         | .135   | .140  | .145              | 3.43  | 3.56  | 3.68  |

| Lead Thickness             | С         | .008   | .010  | .012              | 0.20  | 0.25  | 0.30  |

| Upper Lead Width           | B1        | .050   | .058  | .065              | 1.27  | 1.46  | 1.65  |

| Lower Lead Width           | В         | .016   | .019  | .021              | 0.41  | 0.47  | 0.53  |

| Overall Row Spacing        | eB        | .345   | .385  | .425              | 8.76  | 9.78  | 10.80 |

| Window Width               | W1        | .130   | .140  | .150              | 3.30  | 3.56  | 3.81  |

| Window Length              | W2        | .290   | .300  | .310              | 7.37  | 7.62  | 7.87  |

| *0 · · · ·                 |           |        |       |                   |       |       |       |

\*Controlling Parameter JEDEC Equivalent: MO-058 Drawing No. C04-080

© 1998-2013 Microchip Technology Inc.

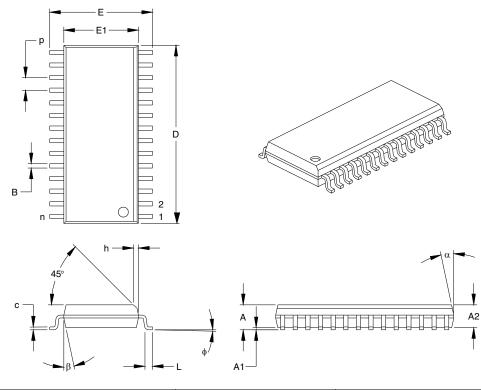

#### 28-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC) 15.4

|                          |        | INCHES* |      | MILLIMETERS |       |       |       |

|--------------------------|--------|---------|------|-------------|-------|-------|-------|

| Dimension                | Limits | MIN     | NOM  | MAX         | MIN   | NOM   | MAX   |

| Number of Pins           | n      |         | 28   |             |       | 28    |       |

| Pitch                    | р      |         | .050 |             |       | 1.27  |       |

| Overall Height           | Α      | .093    | .099 | .104        | 2.36  | 2.50  | 2.64  |

| Molded Package Thickness | A2     | .088    | .091 | .094        | 2.24  | 2.31  | 2.39  |

| Standoff                 | A1     | .004    | .008 | .012        | 0.10  | 0.20  | 0.30  |

| Overall Width            | E      | .394    | .407 | .420        | 10.01 | 10.34 | 10.67 |

| Molded Package Width     | E1     | .288    | .295 | .299        | 7.32  | 7.49  | 7.59  |

| Overall Length           | D      | .695    | .704 | .712        | 17.65 | 17.87 | 18.08 |

| Chamfer Distance         | h      | .010    | .020 | .029        | 0.25  | 0.50  | 0.74  |

| Foot Length              | L      | .016    | .033 | .050        | 0.41  | 0.84  | 1.27  |

| Foot Angle Top           | φ      | 0       | 4    | 8           | 0     | 4     | 8     |

| Lead Thickness           | С      | .009    | .011 | .013        | 0.23  | 0.28  | 0.33  |

| Lead Width               | В      | .014    | .017 | .020        | 0.36  | 0.42  | 0.51  |

| Mold Draft Angle Top     | α      | 0       | 12   | 15          | 0     | 12    | 15    |

| Mold Draft Angle Bottom  | β      | 0       | 12   | 15          | 0     | 12    | 15    |

\*Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MS-013 Drawing No. C04-052

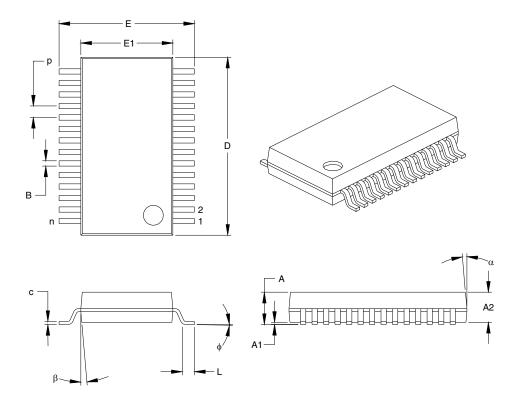

#### 28-Lead Plastic Shrink Small Outline (SS) - 209 mil, 5.30 mm (SSOP) 15.5

| Units    |                                                                                                                             |                                                                                                                                                                                                                                                                                               |                                                        | MILLIMETERS*                                           |                                                        |                                                        |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--|

| n Limits | MIN                                                                                                                         | NOM                                                                                                                                                                                                                                                                                           | MAX                                                    | MIN                                                    | NOM                                                    | MAX                                                    |  |

| n        |                                                                                                                             | 28                                                                                                                                                                                                                                                                                            |                                                        |                                                        | 28                                                     |                                                        |  |

| р        |                                                                                                                             | .026                                                                                                                                                                                                                                                                                          |                                                        |                                                        | 0.66                                                   |                                                        |  |

| A        | .068                                                                                                                        | .073                                                                                                                                                                                                                                                                                          | .078                                                   | 1.73                                                   | 1.85                                                   | 1.98                                                   |  |

| A2       | .064                                                                                                                        | .068                                                                                                                                                                                                                                                                                          | .072                                                   | 1.63                                                   | 1.73                                                   | 1.83                                                   |  |

| A1       | .002                                                                                                                        | .006                                                                                                                                                                                                                                                                                          | .010                                                   | 0.05                                                   | 0.15                                                   | 0.25                                                   |  |

| E        | .299                                                                                                                        | .309                                                                                                                                                                                                                                                                                          | .319                                                   | 7.59                                                   | 7.85                                                   | 8.10                                                   |  |

| E1       | .201                                                                                                                        | .207                                                                                                                                                                                                                                                                                          | .212                                                   | 5.11                                                   | 5.25                                                   | 5.38                                                   |  |

| D        | .396                                                                                                                        | .402                                                                                                                                                                                                                                                                                          | .407                                                   | 10.06                                                  | 10.20                                                  | 10.34                                                  |  |

| L        | .022                                                                                                                        | .030                                                                                                                                                                                                                                                                                          | .037                                                   | 0.56                                                   | 0.75                                                   | 0.94                                                   |  |

| С        | .004                                                                                                                        | .007                                                                                                                                                                                                                                                                                          | .010                                                   | 0.10                                                   | 0.18                                                   | 0.25                                                   |  |

| ¢        | 0                                                                                                                           | 4                                                                                                                                                                                                                                                                                             | 8                                                      | 0.00                                                   | 101.60                                                 | 203.20                                                 |  |

| В        | .010                                                                                                                        | .013                                                                                                                                                                                                                                                                                          | .015                                                   | 0.25                                                   | 0.32                                                   | 0.38                                                   |  |

| α        | 0                                                                                                                           | 5                                                                                                                                                                                                                                                                                             | 10                                                     | 0                                                      | 5                                                      | 10                                                     |  |

| β        | 0                                                                                                                           | 5                                                                                                                                                                                                                                                                                             | 10                                                     | 0                                                      | 5                                                      | 10                                                     |  |

|          | p           A           A2           A1           E           D           L           c           φ           B           α | n           p           A         .068           A2         .064           A1         .002           E         .299           E1         .201           D         .396           L         .022           c         .004           φ         0           B         .010           α         0 | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |  |

\*Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-150

Drawing No. C04-073

# **APPENDIX A: REVISION HISTORY**

| Version | Date | Revision Description                                                                                                                                                                                         |

|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A       | 7/98 | This is a new data sheet. However, the devices described in this data sheet are the upgrades to the devices found in the <i>PIC16C6X Data Sheet</i> , DS30234, and the <i>PIC16C7X Data Sheet</i> , DS30390. |

# APPENDIX B: CONVERSION CONSIDERATIONS

Considerations for converting from previous versions of devices to the ones listed in this data sheet are listed in Table B-1.

## TABLE B-1: CONVERSION CONSIDERATIONS

| Difference    | PIC16C62A/72                                                         | PIC16C62B/72A    |

|---------------|----------------------------------------------------------------------|------------------|

| Voltage Range | 2.5V - 6.0V                                                          | 2.5V - 5.5V      |

| SSP module    | Basic SSP (2 mode SPI)                                               | SSP (4 mode SPI) |

| CCP module    | CCP does not reset TMR1 when in special event trigger mode.          | N/A              |

| Timer1 module | Writing to TMR1L register can cause over-<br>flow in TMR1H register. | N/A              |

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support