Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc72a-04-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

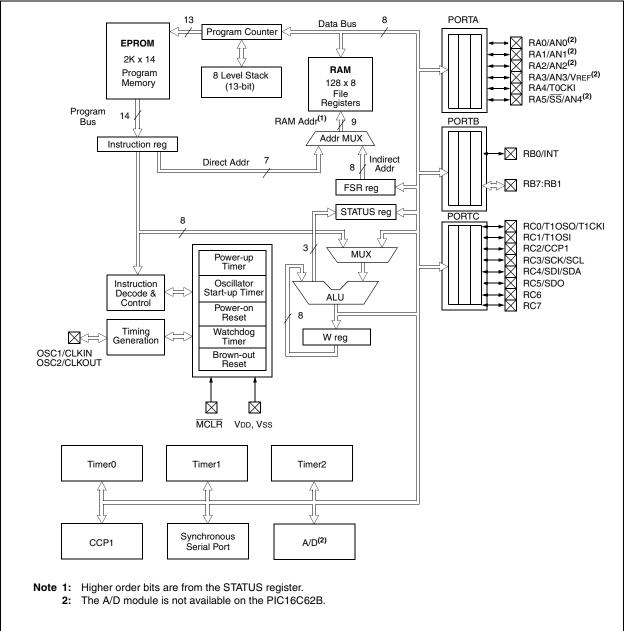

## 1.0 DEVICE OVERVIEW

This document contains device-specific information. Additional information may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

There are two devices (PIC16C62B, PIC16C72A) covered by this datasheet. The PIC16C62B does not have the A/D module implemented.

Figure 1-1 is the block diagram for both devices. The pinouts are listed in Table 1-1.

© 1998-2013 Microchip Technology Inc.

| Addr    | Name                    | Bit 7                                                            | Bit 6                              | Bit 5        | Bit 4         | Bit 3         | Bit 2           | Bit 1        | Bit 0         | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(4) |

|---------|-------------------------|------------------------------------------------------------------|------------------------------------|--------------|---------------|---------------|-----------------|--------------|---------------|--------------------------|-------------------------------------|

| Bank 1  |                         |                                                                  |                                    |              |               |               |                 |              |               |                          |                                     |

| 80h     | INDF <sup>(1)</sup>     | Addressing                                                       | this locatio                       | n uses conte | ents of FSR   | to address d  | ata memory      | (not a physi | cal register) | 0000 0000                | 0000 0000                           |

| 81h     | OPTION_REG              | RBPU                                                             | INTEDG                             | T0CS         | TOSE          | PSA           | PS2             | PS1          | PS0           | 1111 1111                | 1111 1111                           |

| 82h     | PCL <sup>(1)</sup>      | Program C                                                        | ounter's (PC                       | C) Least Sig | nificant Byte | 1             |                 |              |               | 0000 0000                | 0000 0000                           |

| 83h     | STATUS <sup>(1)</sup>   | IRP <sup>(5)</sup>                                               | RP1 <sup>(5)</sup>                 | RP0          | TO            | PD            | Z               | DC           | С             | 0001 1xxx                | 000q quuu                           |

| 84h     | FSR <sup>(1)</sup>      | Indirect dat                                                     | direct data memory address pointer |              |               |               |                 |              |               |                          | uuuu uuuu                           |

| 85h     | TRISA                   | —                                                                | —                                  |              | 11 1111       | 11 1111       |                 |              |               |                          |                                     |

| 86h     | TRISB                   | PORTB Da                                                         | ta Direction                       |              | 1111 1111     | 1111 1111     |                 |              |               |                          |                                     |

| 87h     | TRISC                   | PORTC Da                                                         | ta Direction                       |              | 1111 1111     | 1111 1111     |                 |              |               |                          |                                     |

| 88h-89h | _                       | Unimpleme                                                        | Jnimplemented                      |              |               |               |                 |              |               |                          | _                                   |

| 8Ah     | PCLATH <sup>(1,2)</sup> | —                                                                | _                                  | —            | Write Buffe   | r for the upp | er 5 bits of th | e Program (  | Counter       | 0 0000                   | 0 0000                              |

| 8Bh     | INTCON <sup>(1)</sup>   | GIE                                                              | PEIE                               | TOIE         | INTE          | RBIE          | TOIF            | INTF         | RBIF          | 0000 000x                | 0000 000u                           |

| 8Ch     | PIE1                    | —                                                                | ADIE <sup>(3)</sup>                | _            | —             | SSPIE         | CCP1IE          | TMR2IE       | TMR1IE        | -0 0000                  | -0 0000                             |

| 8Dh     | _                       | Unimpleme                                                        | ented                              |              |               |               |                 |              |               | _                        | _                                   |

| 8Eh     | PCON                    | —                                                                | _                                  | —            | —             | _             | —               | POR          | BOR           | dd                       | uu                                  |

| 8Fh-91h | _                       | Unimpleme                                                        | Jnimplemented                      |              |               |               |                 |              |               |                          | _                                   |

| 92h     | PR2                     | Timer2 Per                                                       | Timer2 Period Register             |              |               |               |                 |              |               |                          | 1111 1111                           |

| 93h     | SSPADD                  | Synchronous Serial Port (I <sup>2</sup> C mode) Address Register |                                    |              |               |               |                 |              |               | 0000 0000                | 0000 0000                           |

| 94h     | SSPSTAT                 | SMP                                                              | CKE                                | D/A          | Р             | S             | R/W             | UA           | BF            | 0000 0000                | 0000 0000                           |

| 95h-9Eh | —                       | Unimpleme                                                        | ented                              | —            | —             |               |                 |              |               |                          |                                     |

| 9Fh     | ADCON1 <sup>(3)</sup>   | _                                                                | _                                  | _            | _             | _             | PCFG2           | PCFG1        | PCFG0         | 000                      | 000                                 |

#### TABLE 2-1 SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0',

Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: A/D not implemented on the PIC16C62B, maintain as '0'.

4: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

5: The IRP and RP1 bits are reserved. Always maintain these bits clear.

**6:** On any device reset, these pins are configured as inputs.

7: This is the value that will be in the port output latch.

#### 2.2.2.2 OPTION\_REG REGISTER

Г

The OPTION\_REG register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known as the prescaler), the External INT Interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

## REGISTER 2-2: OPTION\_REG REGISTER (ADDRESS 81h)

| R/W-1    | R/W-1       | R/W-1                                             | R/W-1    | R/W-1     | R/W-1     | R/W-1   | R/W-1 |                          |  |  |  |  |  |

|----------|-------------|---------------------------------------------------|----------|-----------|-----------|---------|-------|--------------------------|--|--|--|--|--|

| RBPU     | INTEDG      | TOCS                                              | T0SE     | PSA       | PS2       | PS1     | PS0   | R = Readable bit         |  |  |  |  |  |

| bit7     |             |                                                   |          |           |           |         | bit0  | W = Writable bit         |  |  |  |  |  |

|          |             |                                                   |          |           |           |         |       | - n = Value at POR reset |  |  |  |  |  |

| bit 7:   | RBPU: PC    |                                                   |          |           |           |         |       |                          |  |  |  |  |  |

|          |             | B pull-ups a                                      |          |           |           | _       |       |                          |  |  |  |  |  |

|          | 0 = PORTI   | = PORTB pull-ups are enabled for all PORTB inputs |          |           |           |         |       |                          |  |  |  |  |  |

| bit 6:   | INTEDG: I   | ITEDG: Interrupt Edge Select bit                  |          |           |           |         |       |                          |  |  |  |  |  |

|          | 1 = Interru | pt on rising                                      | edge o   | f RB0/INT | pin       |         |       |                          |  |  |  |  |  |

|          | 0 = Interru | pt on falling                                     | g edge o | f RB0/INT | - pin     |         |       |                          |  |  |  |  |  |

| bit 5:   | TOCS: TM    | R0 Clock S                                        | ource S  | elect bit |           |         |       |                          |  |  |  |  |  |

|          | 1 = Transit | ion on RA4                                        | /T0CKI   | pin       |           |         |       |                          |  |  |  |  |  |

|          |             | = Internal instruction cycle clock (CLKOUT)       |          |           |           |         |       |                          |  |  |  |  |  |

| bit 4:   |             | <b>OSE</b> : TMR0 Source Edge Select bit          |          |           |           |         |       |                          |  |  |  |  |  |

| Dit 4.   |             |                                                   |          |           | on RA4/T0 | CKI nin |       |                          |  |  |  |  |  |

|          |             | •                                                 |          |           | on RA4/T0 | •       |       |                          |  |  |  |  |  |

| hit 0.   |             |                                                   | •        |           |           | o p     |       |                          |  |  |  |  |  |

| bit 3:   | PSA: Pres   | •                                                 |          |           |           |         |       |                          |  |  |  |  |  |

|          |             | tler is assig<br>tler is assig                    |          |           | modulo    |         |       |                          |  |  |  |  |  |

|          |             | 0                                                 |          |           | module    |         |       |                          |  |  |  |  |  |

| bit 2-0: | PS2:PS0:    | Prescaler F                                       | Rate Sel | ect bits  |           |         |       |                          |  |  |  |  |  |

|          | Bit Value   | TMR0 Rat                                          | e WD     | Γ Rate    |           |         |       |                          |  |  |  |  |  |

|          | 000         | 1:2                                               | 1:       | 1         |           |         |       |                          |  |  |  |  |  |

|          | 001         | ··· 1.7                                           |          |           |           |         |       |                          |  |  |  |  |  |

|          | 010         |                                                   |          |           |           |         |       |                          |  |  |  |  |  |

|          | 011         | 1:16                                              |          | -         |           |         |       |                          |  |  |  |  |  |

|          | 100         | 1:32                                              |          | 16        |           |         |       |                          |  |  |  |  |  |

|          | 101         | 1:64                                              |          | 32<br>64  |           |         |       |                          |  |  |  |  |  |

|          | 110         |                                                   |          |           |           |         |       |                          |  |  |  |  |  |

|          | 111         | 1:256                                             |          | 120       |           |         |       |                          |  |  |  |  |  |

## 3.0 I/O PORTS

Some I/O port pins are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

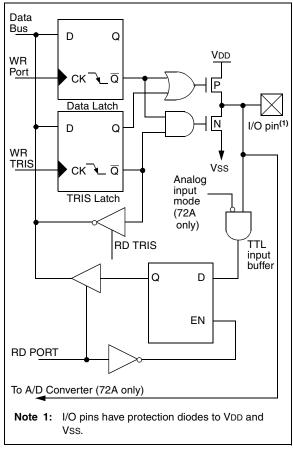

## 3.1 PORTA and the TRISA Register

PORTA is a 6-bit wide bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (=1) will make the corresponding PORTA pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISA bit (=0) will make the corresponding PORTA pin an output, (i.e., put the contents of the output latch on the selected pin).

The PORTA register reads the state of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

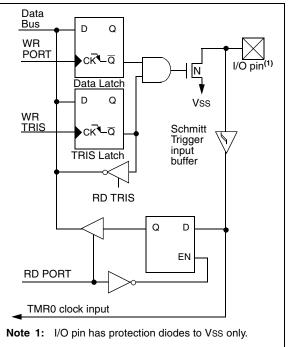

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers.

Pin RA5 is multiplexed with the SSP to become the RA5/SS pin.

On the PIC16C72A device, other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

| Note: | On a Power-on Reset, pins with analog           |  |  |  |  |  |

|-------|-------------------------------------------------|--|--|--|--|--|

|       | functions are configured as analog inputs       |  |  |  |  |  |

|       | with digital input buffers disabled . A digital |  |  |  |  |  |

|       | read of these pins will return '0'.             |  |  |  |  |  |

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### FIGURE 3-1: BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

#### FIGURE 3-2: BLOCK DIAGRAM OF RA4/T0CKI PIN

© 1998-2013 Microchip Technology Inc.

## TABLE 3-1 PORTA FUNCTIONS

| Name         | Bit# | Buffer | Function                                                                                      |

|--------------|------|--------|-----------------------------------------------------------------------------------------------|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input <sup>(1)</sup>                                                   |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input <sup>(1)</sup>                                                   |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input <sup>(1)</sup>                                                   |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input <sup>(1)</sup> or VREF <sup>(1)</sup>                            |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0<br>Output is open drain type                  |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input <sup>(1)</sup> |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: The PIC16C62B does not implement the A/D module.

## TABLE 3-2 SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name                          | Bit 7 | Bit 6 | Bit 5                         | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on all other resets |

|---------|-------------------------------|-------|-------|-------------------------------|-------|-------|-------|-------|-------|-------------------------|---------------------------|

| 05h     | PORTA<br>(for PIC16C72A only) | —     | —     | RA5                           | RA4   | RA3   | RA2   | RA1   | RA0   | 0x 0000                 | 0u 0000                   |

| 05h     | PORTA<br>(for PIC16C62B only) | —     | —     | RA5                           | RA4   | RA3   | RA2   | RA1   | RA0   | xx xxxx                 | uu uuuu                   |

| 85h     | TRISA                         |       |       | PORTA Data Direction Register |       |       |       |       |       | 11 1111                 | 11 1111                   |

| 9Fh     | ADCON1 <sup>(1)</sup>         |       |       |                               |       |       | PCFG2 | PCFG1 | PCFG0 | 000                     | 000                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA. Note 1: The PIC16C62B does not implement the A/D module. Maintain this register clear.

## TABLE 3-5 PORTC FUNCTIONS

| Name            | Bit# | Buffer<br>Type | Function                                                                    | TRISC<br>Override |

|-----------------|------|----------------|-----------------------------------------------------------------------------|-------------------|

| RC0/T1OSO/T1CKI | bit0 | ST             | Input/output port pin or Timer1 oscillator output/Timer1 clock input        | Yes               |

| RC1/T1OSI       | bit1 | ST             | Input/output port pin or Timer1 oscillator input                            | Yes               |

| RC2/CCP1        | bit2 | ST             | Input/output port pin or Capture1 input/Compare1 output/PWM1 output         | No                |

| RC3/SCK/SCL     | bit3 | ST             | RC3 can also be the synchronous serial clock for both SPI and $I^2C$ modes. | No                |

| RC4/SDI/SDA     | bit4 | ST             | RC4 can also be the SPI Data In (SPI mode) or data $I/O$ ( $I^2C$ mode).    | No                |

| RC5/SDO         | bit5 | ST             | Input/output port pin or Synchronous Serial Port data output                | No                |

| RC6             | bit6 | ST             | Input/output port pin                                                       | No                |

| RC7             | bit7 | ST             | Input/output port pin                                                       | No                |

Legend: ST = Schmitt Trigger input

## TABLE 3-6SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7   | Bit 6                        | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|---------|------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 07h     | PORTC | RC7     | RC6                          | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   | xxxx xxxx                | uuuu uuuu                 |

| 87h     | TRISC | PORTC I | ORTC Data Direction Register |       |       |       |       |       |       | 1111 1111                | 1111 1111                 |

Legend: x = unknown, u = unchanged.

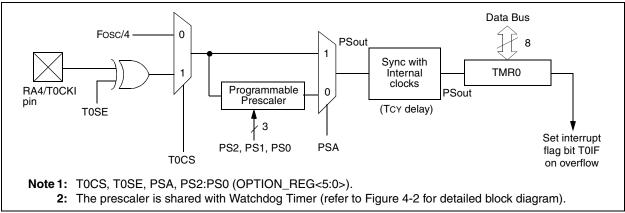

## 4.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Read and write

- INT on overflow

- 8-bit software programmable prescaler

- INT or EXT clock select

- EXT clock edge select

Figure 4-1 is a simplified block diagram of the Timer0 module.

Additional information on timer modules is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

#### 4.1 <u>Timer0 Operation</u>

Timer0 can operate as a timer or as a counter.

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed below.

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization. Additional information on external clock requirements is available in the Electrical Specifications section of this manual, and in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

#### 4.2 <u>Prescaler</u>

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 4-2). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. There is only one prescaler available which is shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The prescaler is not readable or writable.

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

Clearing bit PSA will assign the prescaler to the Timer0 module. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable.

Setting bit PSA will assign the prescaler to the Watchdog Timer (WDT). When the prescaler is assigned to the WDT, prescale values of 1:1, 1:2, ..., 1:128 are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment or ratio.

#### FIGURE 4-1: TIMER0 BLOCK DIAGRAM

### 6.1 <u>Timer2 Operation</u>

The Timer2 output is also used by the CCP module to generate the PWM "On-Time", and the PWM period with a match with PR2.

The TMR2 register is readable and writable, and is cleared on any device reset.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device reset (Power-on Reset, MCLR reset, Watchdog Timer reset or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

#### 6.2 <u>Timer2 Interrupt</u>

The Timer2 module has an 8-bit period register PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon reset.

#### 6.3 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module, which optionally uses it to generate shift clock.

## TABLE 6-1 REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Address | Name   | Bit 7                    | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|--------|--------------------------|---------|---------|---------|---------|--------|---------|---------|-------------------------|---------------------------------|

| 0Bh,8Bh | INTCON | GIE                      | PEIE    | TOIE    | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x               | 0000 000u                       |

| 0Ch     | PIR1   | _                        | ADIF    | _       | _       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | -00- 0000               | 0000 0000                       |

| 8Ch     | PIE1   | _                        | ADIE    | _       | _       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | -0 0000                 | 0000 0000                       |

| 11h     | TMR2   | Timer2 module's register |         |         |         |         |        |         |         |                         | 0000 0000                       |

| 12h     | T2CON  | _                        | TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000               | -000 0000                       |

| 92h     | PR2    | Timer2 Period Register   |         |         |         |         |        |         |         |                         | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

#### 8.3.2 MASTER OPERATION

Master operation is supported in firmware using interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared by a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is idle and both the S and P bits are clear.

In master operation, the SCL and SDA lines are manipulated in software by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt if enabled):

- START condition

- STOP condition

- Byte transfer completed

Master operation can be done with either the slave mode idle (SSPM3:SSPM0 = 1011) or with the slave active. When both master operation and slave modes are used, the software needs to differentiate the source(s) of the interrupt.

For more information on master operation, see AN554 - Software Implementation of  $I^2C$  Bus Master.

#### 8.3.3 MULTI-MASTER OPERATION

In multi-master operation, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle and both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In multi-master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost, these are:

- Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed, an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to re-transfer the data at a later time.

For more information on master operation, see AN578 - Use of the SSP Module in the of  $l^2C$  Multi-Master Environment.

| Address  | Name    | Bit 7                         | Bit 6                                                    | Bit 5                    | Bit 4    | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR |      | Value on<br>all other<br>resets |      |

|----------|---------|-------------------------------|----------------------------------------------------------|--------------------------|----------|-----------|--------|--------|--------|-------------------------|------|---------------------------------|------|

| 0Bh, 8Bh | INTCON  | GIE                           | PEIE                                                     | TOIE                     | INTE     | RBIE      | T0IF   | INTF   | RBIF   | 0000                    | 000x | 0000                            | 000u |

| 0Ch      | PIR1    | _                             | ADIF                                                     | _                        |          | SSPIF     | CCP1IF | TMR2IF | TMR1IF | - 0                     | 0000 | - 0                             | 0000 |

| 8Ch      | PIE1    | _                             | ADIE                                                     | _                        | —        | SSPIE     | CCP1IE | TMR2IE | TMR1IE | - 0                     | 0000 | - 0                             | 0000 |

| 13h      | SSPBUF  | Synchronou                    | Synchronous Serial Port Receive Buffer/Transmit Register |                          |          |           |        |        |        |                         |      | uuuu                            | uuuu |

| 93h      | SSPADD  | Synchronou                    | is Serial F                                              | Port (I <sup>2</sup> C n | node) Ad | dress Reg | jister |        |        | 0000                    | 0000 | 0000                            | 0000 |

| 14h      | SSPCON  | WCOL                          | SSPOV                                                    | SSPEN                    | CKP      | SSPM3     | SSPM2  | SSPM1  | SSPM0  | 0000                    | 0000 | 0000                            | 0000 |

| 94h      | SSPSTAT | SMP <sup>(1)</sup>            | CKE <sup>(1)</sup>                                       | D/A                      | Р        | S         | R/W    | UA     | BF     | 0000                    | 0000 | 0000                            | 0000 |

| 87h      | TRISC   | PORTC Data Direction register |                                                          |                          |          |           |        |        |        |                         | 1111 | 1111                            | 1111 |

#### TABLE 8-3REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in SPI mode.

**Note 1:** Maintain these bits clear in  $I^2C$  mode.

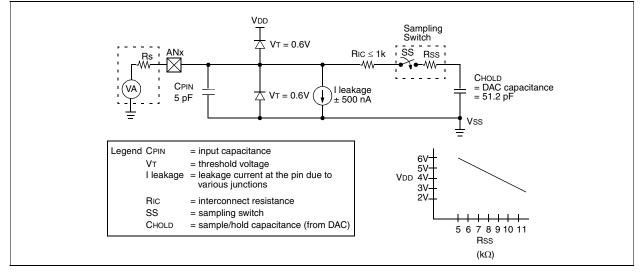

#### 9.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 9-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 10 k $\Omega$ . After the analog input channel is selected (changed), this acquisition must pass before the conversion can be started.

To calculate the minimum acquisition time, TACQ, see Equation 9-1. This equation calculates the acquisition time to within 1/2 LSb error (512 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified accuracy.

| Note: | When the conversion is started, the hold-         |  |  |  |  |  |  |  |

|-------|---------------------------------------------------|--|--|--|--|--|--|--|

|       | ing capacitor is disconnected from the input pin. |  |  |  |  |  |  |  |

|       | input pin.                                        |  |  |  |  |  |  |  |

In general;

Assuming Rs =  $10k\Omega$

Vdd =

$$3.0V$$

(Rss =  $10k\Omega$ )

TACQ  $\approx~13.0~\mu Sec$

By increasing VDD and reducing Rs and Temp., TACQ can be substantially reduced.

#### FIGURE 9-2: ANALOG INPUT MODEL

#### EQUATION 9-1: ACQUISITION TIME

- TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient

- = TAMP + TC + TCOFF TAMP =  $5\mu S$ TC = -  $(51.2pF)(1k\Omega + Rss + Rs) In(1/511)$ TCOFF =  $(Temp - 25^{\circ}C)(0.05\mu S/^{\circ}C)$

#### 9.4 <u>A/D Conversions</u>

| Note: | The GO/DONE bit should NOT be set in        |

|-------|---------------------------------------------|

|       | the same instruction that turns on the A/D. |

#### 9.5 Use of the CCP Trigger

An A/D conversion can be started by the "special event trigger" of the CCP1 module. This requires that the CCP1M3:CCP1M0 bits (CCP1CON<3:0>) be programmed as 1011 and that the A/D module be enabled (ADON bit is set). When the trigger occurs, the

TABLE 9-2 SUMMARY OF A/D REGISTERS

GO/DONE bit will be set, starting the A/D conversion, and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D acquisition period with minimal software overhead. The appropriate analog input channel must be selected and the minimum acquisition time must pass before the "special event trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), then the "special event trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

| Address | Name   | Bit 7   | Bit 6               | Bit 5   | Bit 4       | Bit 3      | Bit 2   | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all other Resets |

|---------|--------|---------|---------------------|---------|-------------|------------|---------|--------|--------|-------------------------|---------------------------|

| 0Bh,8Bh | INTCON | GIE     | PEIE                | TOIE    | INTE        | RBIE       | T0IF    | INTF   | RBIF   | 0000 000x               | 0000 000u                 |

| 0Ch     | PIR1   | _       | ADIF                | —       | _           | SSPIF      | CCP1IF  | TMR2IF | TMR1IF | -0 0000                 | -0 0000                   |

| 8Ch     | PIE1   | _       | ADIE                | —       | _           | SSPIE      | CCP1IE  | TMR2IE | TMR1IE | -0 0000                 | -0 0000                   |

| 1Eh     | ADRES  | A/D Res | A/D Result Register |         |             |            |         |        |        | xxxx xxxx               | uuuu uuuu                 |

| 1Fh     | ADCON0 | ADCS1   | ADCS0               | CHS2    | CHS1        | CHS0       | GO/DONE | —      | ADON   | 0000 00-0               | 0000 00-0                 |

| 9Fh     | ADCON1 | _       | —                   | —       | —           | —          | PCFG2   | PCFG1  | PCFG0  | 000                     | 000                       |

| 05h     | PORTA  | _       | _                   | RA5     | RA4         | RA3        | RA2     | RA1    | RA0    | 0x 0000                 | 0u 0000                   |

| 85h     | TRISA  |         | —                   | PORTA D | Data Direct | tion Regis | ter     |        |        | 11 1111                 | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D conversion.

### 10.2 Oscillator Configurations

#### 10.2.1 OSCILLATOR TYPES

The PIC16CXXX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

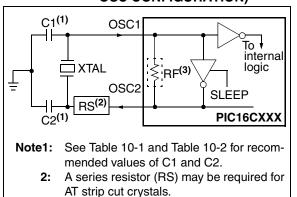

## 10.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

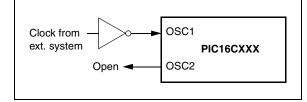

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 10-2). The PIC16CXXX oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can use an external clock source to drive the OSC1/CLKIN pin (Figure 10-3).

#### FIGURE 10-2: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

3: RF varies with the crystal chosen.

#### FIGURE 10-3: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

## TABLE 10-1 CERAMIC RESONATORS

## Ranges Tested:

| Ranges lested:                                                          |                   |                              |              |  |  |  |  |

|-------------------------------------------------------------------------|-------------------|------------------------------|--------------|--|--|--|--|

| Mode                                                                    | Freq              | 0\$C2                        |              |  |  |  |  |

| XT                                                                      | 455 kHz           | 68 - 100 pF                  | 68 - 100 pF  |  |  |  |  |

|                                                                         | 2.0 MHz           | 15 - 68 pF 🛛 🤇               | 15-68 pF     |  |  |  |  |

|                                                                         | 4.0 MHz           | 15 - 68 pF                   | ∖15, - 68 pF |  |  |  |  |

| HS                                                                      | 8.0 MHz           | 10 - 68(pF                   | 이 - 68 pF    |  |  |  |  |

|                                                                         | 16.0 MHz          | 10,-22,0F                    | 10 - 22 pF   |  |  |  |  |

| These values are for design guidance only. See notes at bottom of gage. |                   |                              |              |  |  |  |  |

| Resonator                                                               | rs Used: 🔨        |                              |              |  |  |  |  |

| 455 kHz                                                                 | Panasonie         | FO-A455K04B                  | ± 0.3%       |  |  |  |  |

| 2.0 MHz                                                                 | Murata Erie (     | CSA2.00MG                    | ± 0.5%       |  |  |  |  |

| 4.0 MHz                                                                 | Murata Erie (     | CSA4.00MG                    | $\pm 0.5\%$  |  |  |  |  |

| 8.0 MATHZ                                                               | Murata Erie (     | Murata Erie CSA8.00MT ± 0.5% |              |  |  |  |  |

| 16.0 MHz                                                                | Murata Erie (     | CSA16.00MX                   | $\pm 0.5\%$  |  |  |  |  |

| Resona                                                                  | ators did not hav | ve built-in capacito         | ors.         |  |  |  |  |

## TABLE 10-2CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq | Cap. Range<br>C1                   | Cap. Range<br>C2      |

|----------|-----------------|------------------------------------|-----------------------|

| LP       | 32 kHz          | 33 pF                              | 33 pF                 |

|          | 200 kHz         | 15 pF                              | 15 pF                 |

| XT       | 200 kHz         | 47-68 pF                           | 47-68 pF              |

|          | 1 MHz           | 15 pF <                            | ✓ 15 pF               |

|          | 4 MHz           | 15 pF 🕟                            | ∕∕15 pF               |

| HS       | 4 MHz           | 15 pt                              | ✓ 15 pF               |

|          | 8 MHz           | 15-33 pE>                          | 15-33 pF              |

|          | 20 MHz          | (15-33 pF                          | 15-33 pF              |

|          | values are      | <b>for design guida</b> r<br>page. | n <b>ce only.</b> See |

|          | Crys            | tals Used                          |                       |

| 32 kHz   | Epson C-00      | 01R32.768K-A                       | ± 20 PPM              |

| 200 kt/2 | STO XTL 2       | ± 20 PPM                           |                       |

| 1 Mhz S  | ECS ECS-1       | ± 50 PPM                           |                       |

| 4 MHz    | ECS ECS-4       | 40-20-1                            | ± 50 PPM              |

| 8 MHz    | EPSON CA        | -301 8.000M-C                      | ± 30 PPM              |

**Note 1:** Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

EPSON CA-301 20.000M-C

20 MHz

2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

± 30 PPM

- 3: Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- 4: Oscillator performance should be verified when migrating between devices (including PIC16C62A to PIC16C62B and PIC16C72 to PIC16C72A)

## PIC16C62B/72A

MPLIB is a librarian for pre-compiled code to be used with MPLINK. When a routine from a library is called from another source file, only the modules that contains that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications. MPLIB manages the creation and modification of library files.

MPLINK features include:

- MPLINK works with MPASM and MPLAB-C17 and MPLAB-C18.

- MPLINK allows all memory areas to be defined as sections to provide link-time flexibility.

MPLIB features include:

- MPLIB makes linking easier because single libraries can be included instead of many smaller files.

- MPLIB helps keep code maintainable by grouping related modules together.

- MPLIB commands allow libraries to be created and modules to be added, listed, replaced, deleted, or extracted.

## 12.5 MPLAB-SIM Software Simulator

The MPLAB-SIM Software Simulator allows code development in a PC host environment by simulating the PIC series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file or user-defined key press to any of the pins. The execution can be performed in single step, execute until break, or trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C17 and MPLAB-C18 and MPASM. The Software Simulator offers the flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

#### 12.6 <u>MPLAB-ICE High Performance</u> <u>Universal In-Circuit Emulator with</u> <u>MPLAB IDE</u>

The MPLAB-ICE Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers (MCUs). Software control of MPLAB-ICE is provided by the MPLAB Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB-ICE allows expansion to support new PIC microcontrollers.

The MPLAB-ICE Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows 3.x/95/98 environment were chosen to best make these features available to you, the end user.

MPLAB-ICE 2000 is a full-featured emulator system with enhanced trace, trigger, and data monitoring features. Both systems use the same processor modules and will operate across the full operating speed range of the PIC MCU.

### 12.7 PICMASTER/PICMASTER CE

The PICMASTER system from Microchip Technology is a full-featured, professional quality emulator system. This flexible in-circuit emulator provides a high-quality, universal platform for emulating Microchip 8-bit PIC microcontrollers (MCUs). PICMASTER systems are sold worldwide, with a CE compliant model available for European Union (EU) countries.

## 12.8 <u>ICEPIC</u>

ICEPIC is a low-cost in-circuit emulation solution for the Microchip Technology PIC16C5X, PIC16C6X, PIC16C7X, and PIC16CXXX families of 8-bit one-timeprogrammable (OTP) microcontrollers. The modular system can support different subsets of PIC16C5X or PIC16CXXX products through the use of interchangeable personality modules or daughter boards. The emulator is capable of emulating without target application circuitry being present.

#### 12.9 MPLAB-ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB-ICD, is a powerful, low-cost run-time development tool. This tool is based on the flash PIC16F877 and can be used to develop for this and other PIC microcontrollers from the PIC16CXXX family. MPLAB-ICD utilizes the In-Circuit Debugging capability built into the PIC16F87X. This feature, along with Microchip's In-Circuit Serial Programming protocol, offers cost-effective in-circuit flash programming and debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time. The MPLAB-ICD is also a programmer for the flash PIC16F87X family.

#### 12.10 PRO MATE II Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode. PRO MATE II is CE compliant.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In

## PIC16C62B/72A

and test the sample code. In addition, PICDEM-17 supports down-loading of programs to and executing out of external FLASH memory on board. The PICDEM-17 is also usable with the MPLAB-ICE or PICMASTER emulator, and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

#### 12.17 <u>SEEVAL Evaluation and Programming</u> <u>System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in trade-off analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

## 12.18 <u>KEELOQ Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

|                    |               |                                                                         | Standar                                                                                                                            | d Opera | ating Co | ondition | s (unless otherwise stated)                                                                                  |  |  |  |  |

|--------------------|---------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------|----------|----------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DC CHARACTERISTICS |               |                                                                         | Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial<br>-40^{\circ}C $\le TA \le +85^{\circ}C$ for industrial |         |          |          |                                                                                                              |  |  |  |  |

|                    | 1             | 1                                                                       | 1                                                                                                                                  | 1       |          |          |                                                                                                              |  |  |  |  |

| Param<br>No.       | Sym           | Characteristic                                                          | Min                                                                                                                                | Тур†    | Мах      | Units    | Conditions                                                                                                   |  |  |  |  |

| D001               | Vdd           | Supply Voltage                                                          | 2.5                                                                                                                                | -       | 5.5      | V        | LP, XT, RC osc modes (DC - 4 MHz)                                                                            |  |  |  |  |

|                    |               |                                                                         | VBOR*                                                                                                                              | -       | 5.5      | V        | BOR enabled (Note 7)                                                                                         |  |  |  |  |

| D002*              | Vdr           | RAM Data Retention<br>Voltage (Note 1)                                  | -                                                                                                                                  | 1.5     | -        | V        |                                                                                                              |  |  |  |  |

| D003               | VPOR          | <b>VDD Start Voltage</b> to<br>ensure internal<br>Power-on Reset signal | -                                                                                                                                  | Vss     | -        | V        | See section on Power-on Reset for details                                                                    |  |  |  |  |

| D004*<br>D004A*    | SVDD          | <b>VDD Rise Rate</b> to<br>ensure internal<br>Power-on Reset signal     | 0.05<br>TBD                                                                                                                        | -<br>-  | -        | V/ms     | PWRT enabled (PWRTE bit clear)<br>PWRT disabled (PWRTE bit set)<br>See section on Power-on Reset for details |  |  |  |  |

| D005               | VBOR          | Brown-out Reset voltage trip point                                      | 3.65                                                                                                                               | -       | 4.35     | V        | BODEN bit set                                                                                                |  |  |  |  |

| D010               | IDD           | Supply Current<br>(Note 2, 5)                                           | -                                                                                                                                  | 2.0     | 3.8      | mA       | XT, RC osc modes<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                        |  |  |  |  |

| D010A              |               |                                                                         | -                                                                                                                                  | 22.5    | 48       | μA       | LP OSC MODE<br>FOSC = 32 kHz, VDD = 3.0V, WDT disabled                                                       |  |  |  |  |

| D020               | IPD           | Power-down Current                                                      | -                                                                                                                                  | 7.5     | 30       | μA       | VDD = 3.0V, WDT enabled, -40°C to +85°C                                                                      |  |  |  |  |

| D021               |               | (Note 3, 5)                                                             | -                                                                                                                                  | 0.9     | 5        | μA       | VDD = $3.0V$ , WDT disabled, $0^{\circ}C$ to $+70^{\circ}C$                                                  |  |  |  |  |

| D021A              |               |                                                                         | -                                                                                                                                  | 0.9     | 5        | μA       | VDD = 3.0V, WDT disabled, -40°C to +85°C                                                                     |  |  |  |  |

|                    |               | Module Differential<br>Current (Note 6)                                 |                                                                                                                                    |         |          |          |                                                                                                              |  |  |  |  |

| D022*              | $\Delta$ IWDT | Watchdog Timer                                                          | -                                                                                                                                  | 6.0     | 20       | μA       | WDTE BIT SET, VDD = 4.0V                                                                                     |  |  |  |  |

| D022A*             | $\Delta$ IBOR | Brown-out Reset                                                         | -                                                                                                                                  | TBD     | 200      | μA       | BODEN bit set, VDD = 5.0V                                                                                    |  |  |  |  |

#### 13.2 DC Characteristics: PIC16LC62B/72A-04 (Commercial, Industrial)

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD,

$\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- 4: For RC osc mode, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: This is the voltage where the device enters the Brown-out Reset. When BOR is enabled, the device will perform a brown-out reset when VDD falls below VBOR.

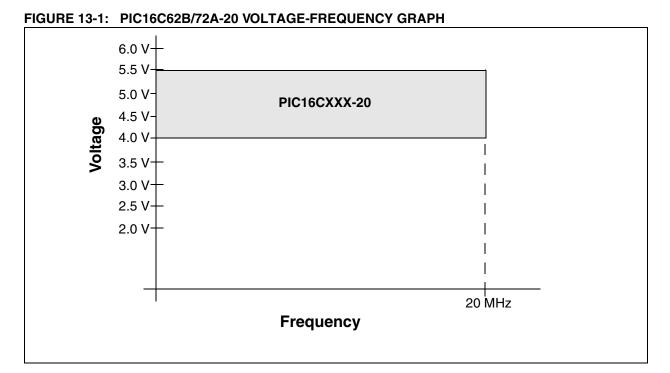

## 13.3 DC Characteristics:

#### cs: PIC16C62B/72A-04 (Commercial, Industrial, Extended) PIC16C62B/72A-20 (Commercial, Industrial, Extended) PIC16LC62B/72A-04 (Commercial, Industrial)

| DC CHA        | ARACTE | RISTICS                               | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |                 |        |                                                                                                    |  |  |

|---------------|--------|---------------------------------------|------------------------------------------------------|-----|-----------------|--------|----------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.  | Sym    |                                       |                                                      |     |                 |        |                                                                                                    |  |  |

|               |        | Input Low Voltage                     |                                                      |     |                 |        |                                                                                                    |  |  |

|               | VIL    | I/O ports                             |                                                      |     |                 |        |                                                                                                    |  |  |

| D030<br>D030A |        | with TTL buffer                       | Vss<br>Vss                                           | -   | 0.15Vdd<br>0.8V | V<br>V | For entire VDD range $4.5V \le VDD \le 5.5V$                                                       |  |  |

| D031          |        | with Schmitt Trigger buffer           | Vss                                                  | -   | 0.2Vdd          | V      |                                                                                                    |  |  |

| D032          |        | MCLR, OSC1 (in RC mode)               | Vss                                                  | -   | 0.2Vdd          | V      |                                                                                                    |  |  |

| D033          |        | OSC1 (in XT, HS and LP modes)         | Vss                                                  | -   | 0.3Vdd          | V      | Note1                                                                                              |  |  |

|               |        | Input High Voltage                    |                                                      |     |                 |        |                                                                                                    |  |  |

|               | Vін    | I/O ports                             |                                                      | -   |                 |        |                                                                                                    |  |  |

| D040          |        | with TTL buffer                       | 2.0                                                  | -   | Vdd             | V      | $4.5V \leq V\text{DD} \leq 5.5V$                                                                   |  |  |

| D040A         |        |                                       | 0.25Vd<br>D + 0.8V                                   | -   | Vdd             | V      | For entire VDD range                                                                               |  |  |

| D041          |        | with Schmitt Trigger buffer           | 0.8Vdd                                               | -   | Vdd             | v      | For entire VDD range                                                                               |  |  |

| D042          |        | MCLR                                  | 0.8Vdd                                               | -   | Vdd             | V      |                                                                                                    |  |  |

| D042A         |        | OSC1 (XT, HS and LP modes)            | 0.7Vdd                                               | -   | Vdd             | V      | Note1                                                                                              |  |  |

| D043          |        | OSC1 (in RC mode)                     | 0.9Vdd                                               | -   | Vdd             | V      |                                                                                                    |  |  |

|               |        | Input Leakage Current<br>(Notes 2, 3) |                                                      |     |                 |        |                                                                                                    |  |  |

| D060          | lı∟    | I/O ports                             | -                                                    | -   | ±1              | μA     | $\label{eq:Vss} \begin{split} &Vss \leq V PIN \leq V DD, \\ &Pin \ at \ hi\ impedance \end{split}$ |  |  |

| D061          |        | MCLR, RA4/T0CKI                       | -                                                    | -   | ±5              | μA     | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                           |  |  |

| D063          |        | OSC1                                  | -                                                    | -   | ±5              | μA     | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc modes                                                |  |  |

| D070          | IPURB  | PORTB weak pull-up current            | 50                                                   | 250 | 400             | μA     | VDD = 5V, VPIN = VSS                                                                               |  |  |

| D080          | Vol    | Output Low Voltage<br>I/O ports       | -                                                    | -   | 0.6             | v      | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                                                        |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the device be driven with external clock in RC mode.

3: Negative current is defined as current sourced by the pin.

<sup>2:</sup> The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

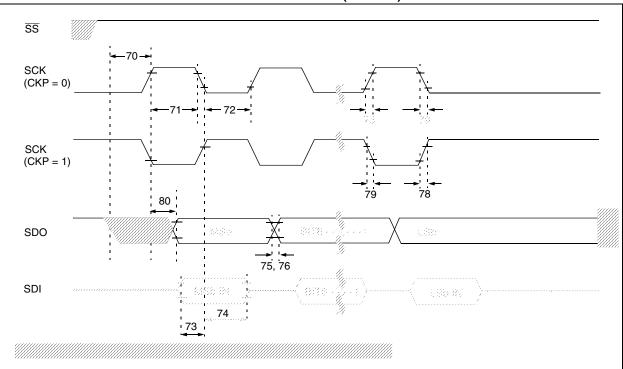

#### FIGURE 13-11: EXAMPLE SPI MASTER MODE TIMING (CKE = 0)

| Param.<br>No. | Symbol                | Characterist                                            | Min         | Тур†         | Max | Units | Conditions |        |

|---------------|-----------------------|---------------------------------------------------------|-------------|--------------|-----|-------|------------|--------|

| 70            | TssL2scH,<br>TssL2scL | SS↓ to SCK↓ or SCK↑ input                               |             | Тсү          | —   | —     | ns         |        |

| 71            | TscH                  |                                                         | Continuous  | 1.25Tcy + 30 | —   | _     | ns         |        |

| 71A           |                       |                                                         | Single Byte | 40           |     | _     | ns         | Note 1 |

| 72            | TscL                  | SCK input low time                                      | Continuous  | 1.25Tcy + 30 | _   |       | ns         |        |

| 72A           |                       | (slave mode)                                            | Single Byte | 40           | _   | _     | ns         | Note 1 |

| 73            | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge                |             | 100          | —   | —     | ns         |        |

| 73A           | Тв2в                  | Last clock edge of Byte1 to the 1st clock edge of Byte2 |             | 1.5Tcy + 40  | —   | —     | ns         | Note 1 |

| 74            | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge                 |             | 100          | —   | —     | ns         |        |

| 75            | TdoR                  | SDO data output rise time                               | PIC16CXX    | _            | 10  | 25    | ns         |        |

|               |                       |                                                         | PIC16LCXX   | _            | 20  | 45    | ns         |        |

| 76            | TdoF                  | SDO data output fall time                               |             | _            | 10  | 25    | ns         |        |

| 78            | TscR                  | SCK output rise time                                    | PIC16CXX    | _            | 10  | 25    | ns         |        |

|               | (master mode)         |                                                         | PIC16LCXX   | _            | 20  | 45    | ns         |        |

| 79            | TscF                  | SCK output fall time (maste                             | er mode)    | _            | 10  | 25    | ns         |        |

| 80            | TscH2doV,             | SDO data output valid                                   | PIC16CXX    | _            | _   | 50    | ns         |        |

|               | TscL2doV              | after SCK edge                                          | PIC16LCXX   | _            | —   | 100   | ns         | ]      |

#### TABLE 13-7: EXAMPLE SPI MODE REQUIREMENTS (MASTER MODE, CKE = 0)

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Specification 73A is only required if specifications 71A and 72A are used.

© 1998-2013 Microchip Technology Inc.

# PIC16C62B/72A

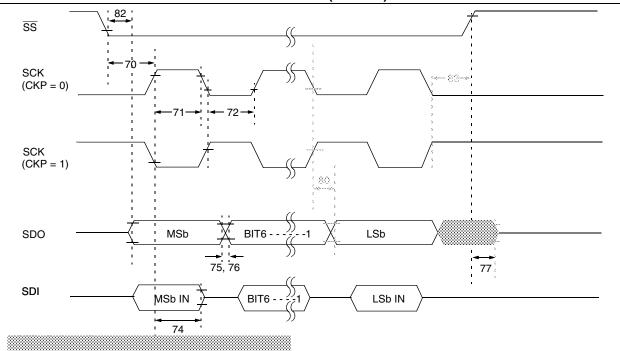

#### FIGURE 13-14: EXAMPLE SPI SLAVE MODE TIMING (CKE = 1)

#### TABLE 13-10: EXAMPLE SPI SLAVE MODE REQUIREMENTS (CKE = 1)

| Param.<br>No. | Symbol                | Characteris                                                           | Min         | Тур†         | Мах | Units | Conditions |        |

|---------------|-----------------------|-----------------------------------------------------------------------|-------------|--------------|-----|-------|------------|--------|

| 70            | TssL2scH,<br>TssL2scL | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ input |             | Тсү          | —   |       | ns         |        |

| 71            | TscH                  | SCK input high time                                                   | Continuous  | 1.25Tcy + 30 | —   | _     | ns         |        |

| 71A           |                       | (slave mode)                                                          | Single Byte | 40           | —   | _     | ns         | Note 1 |

| 72            | TscL                  | SCK input low time                                                    | Continuous  | 1.25Tcy + 30 | —   | _     | ns         |        |

| 72A           |                       | (slave mode)                                                          | Single Byte | 40           | —   |       | ns         | Note 1 |

| 73A           | Тв2в                  | Last clock edge of Byte1 to the 1st clock edge of Byte2               |             | 1.5Tcy + 40  | —   | _     | ns         | Note 1 |

| 74            | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge                               |             | 100          | —   | —     | ns         |        |

| 75            | 75 TdoR               | SDO data output rise                                                  | PIC16CXX    | —            | 10  | 25    | ns         |        |

|               | time                  |                                                                       | PIC16LCXX   |              | 20  | 45    | ns         |        |

| 76            | TdoF                  | SDO data output fall time                                             | Э           |              | 10  | 25    | ns         |        |

| 77            | TssH2doZ              | SS <sup>↑</sup> to SDO output hi-im                                   | pedance     | 10           | —   | 50    | ns         |        |

| 78            | TscR                  | SCK output rise time                                                  | PIC16CXX    |              | 10  | 25    | ns         |        |

|               |                       | (master mode)                                                         | PIC16LCXX   |              | 20  | 45    | ns         |        |

| 79            | TscF                  | SCK output fall time (ma                                              | ster mode)  |              | 10  | 25    | ns         |        |

| 80            | TscH2doV,             | SDO data output valid                                                 | PIC16CXX    |              | —   | 50    | ns         |        |

|               | TscL2doV              | after SCK edge                                                        | PIC16LCXX   |              | —   | 100   | ns         |        |

| 82            | TssL2doV              | SDO data output valid                                                 | PIC16CXX    |              | —   | 50    | ns         |        |

|               |                       | after SS↓ edge                                                        | PIC16LCXX   |              | —   | 100   | ns         |        |

| 83            | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                                                   |             | 1.5TCY + 40  | —   | —     | ns         |        |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Specification 73A is only required if specifications 71A and 72A are used.

| SSP                               |                |

|-----------------------------------|----------------|

| Enable (SSPIE Bit)                | 14             |

| Flag (SSPIF Bit)                  |                |

| RA5/SS/AN4 Pin                    | 6              |

| RC3/SCK/SCL Pin                   |                |

| RC4/SDI/SDA Pin                   |                |

| RC5/SDO Pin                       |                |

| SSPADD Register                   |                |

| SSPBUF Register                   |                |

| SSPCON Register                   |                |

| SSPSTAT Register                  | ,              |

| TMR2 Output for Clock Shift       |                |

| Write Collision Detect (WCOL Bit) |                |