Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc72a-04-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

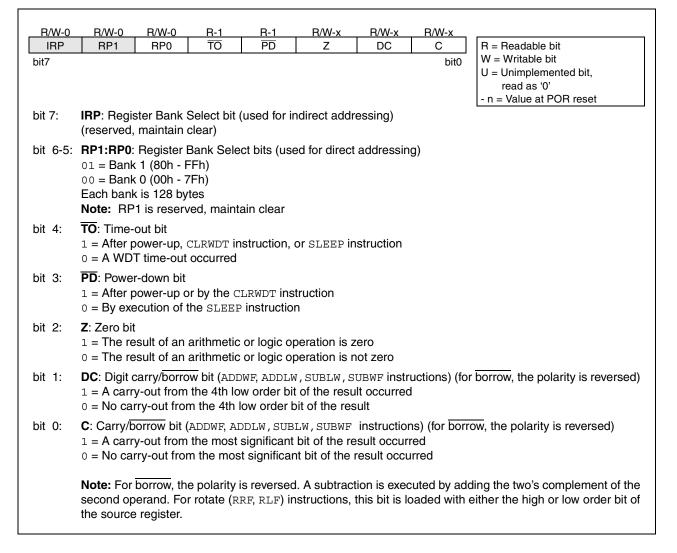

#### 2.2.2.1 STATUS REGISTER

The STATUS register, shown in Register 2-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, the write to these three bits is disabled. These bits are set or cleared according to the device logic. The TO and PD bits are not writable. The result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

- **Note 1:** The IRP and RP1 bits are reserved. Maintain these bits clear to ensure upward compatibility with future products.

- Note 2: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions.

# REGISTER 2-1: STATUS REGISTER (ADDRESS 03h, 83h)

# 2.3 PCL and PCLATH

The program counter (PC) specifies the address of the instruction to fetch for execution. The PC is 13 bits wide. The low byte is called the PCL register and is readable and writable. The high byte is called the PCH register. This register contains the PC<12:8> bits and is not directly accessible. All updates to the PCH register go through the PCLATH register.

## 2.3.1 STACK

The stack allows any combination of up to 8 program calls and interrupts to occur. The stack contains the return address from this branch in program execution.

Mid-range devices have an 8 level deep hardware stack. The stack space is not part of either program or data space and the stack pointer is not accessible. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RET-FIE instruction execution. PCLATH is not modified when the stack is PUSHed or POPed.

After the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

# 2.4 Program Memory Paging

The CALL and GOTO instructions provide 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper bit of the address is provided by PCLATH<3>. The user must ensure that the page select bit is programmed to address the proper program memory page. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is popped from the stack. Therefore, manipulation of the PCLATH<3> bit is not required for the return instructions.

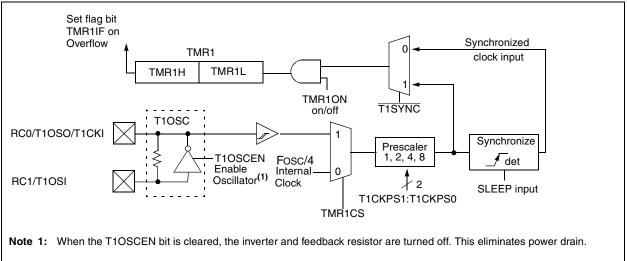

# FIGURE 5-1: TIMER1 BLOCK DIAGRAM

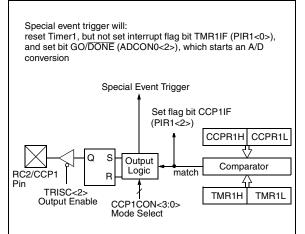

# 7.2 <u>Compare Mode</u>

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- driven High

- driven Low

- remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). The interrupt flag bit, CCP1IF, is set on all compare matches.

## FIGURE 7-2: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 7.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

| Note: | Clearing the CCP1CON register will force       |

|-------|------------------------------------------------|

|       | the RC2/CCP1 compare output latch to the       |

|       | default low level. This is not the data latch. |

#### 7.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 7.2.3 SOFTWARE INTERRUPT MODE

When a generated software interrupt is chosen, the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 7.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated, which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special trigger output of CCP1 resets the TMR1 register pair and starts an A/D conversion (if the A/D module is enabled).

# TABLE 7-3 REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

| Address | Name    | Bit 7                               | Bit 6                                                                       | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|---------|-------------------------------------|-----------------------------------------------------------------------------|---------|---------|---------|--------|--------|-----------|-------------------------|---------------------------------|

| 0Bh,8Bh | INTCON  | GIE                                 | PEIE                                                                        | TOIE    | INTE    | RBIE    | TOIF   | INTF   | RBIF      | 0000 0003               | : 0000 000u                     |

| 0Ch     | PIR1    | —                                   | ADIF                                                                        | —       | —       | SSPIF   | CCP1IF | TMR2IF | TMR1IF    | -0 0000                 | -0 0000                         |

| 8Ch     | PIE1    | —                                   | ADIE                                                                        | _       | —       | SSPIE   | CCP1IE | TMR2IE | TMR1IE    | -0 0000                 | -0 0000                         |

| 87h     | TRISC   | PORTC Da                            | PORTC Data Direction Register                                               |         |         |         |        |        |           |                         | 1111 1111                       |

| 0Eh     | TMR1L   | Holding reg                         | Holding register for the Least Significant Byte of the 16-bit TMR1 register |         |         |         |        |        |           |                         | uuuu uuuu                       |

| 0Fh     | TMR1H   | Holding reg                         | Holding register for the Most Significant Byte of the 16-bit TMR1register   |         |         |         |        |        |           | XXXX XXXX               | uuuu uuuu                       |

| 10h     | T1CON   | —                                   | _                                                                           | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR1ON    | 00 0000                 | uu uuuu                         |

| 15h     | CCPR1L  | Capture/Compare/PWM register1 (LSB) |                                                                             |         |         |         |        |        | XXXX XXXX | uuuu uuuu               |                                 |

| 16h     | CCPR1H  | Capture/Compare/PWM register1 (MSB) |                                                                             |         |         |         |        |        | XXXX XXXX | uuuu uuuu               |                                 |

| 17h     | CCP1CON | —                                   |                                                                             | CCP1X   | CCP1Y   | CCP1M3  | CCP1M2 | CCP1M1 | CCP1M0    | 00 0000                 | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by Capture and Timer1.

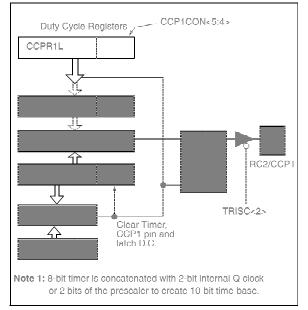

# 7.3 <u>PWM Mode</u>

In Pulse Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force  |

|-------|-------------------------------------------|

|       | the CCP1 PWM output latch to the default  |

|       | low level. This is not the PORTC I/O data |

|       | latch.                                    |

Figure 7-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step by step procedure on how to set up the CCP module for PWM operation, see Section 7.3.3.

FIGURE 7-3: SIMPLIFIED PWM BLOCK DIAGRAM

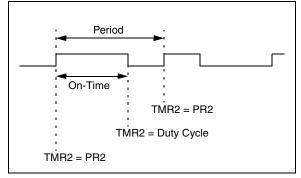

A PWM output (Figure 7-4) has a time base (period) and a time that the output stays high (on-time). The frequency of the PWM is the inverse of the period (1/period).

#### FIGURE 7-4: PWM OUTPUT

#### 7.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

| Note: | The Timer2 postscaler (see Section 6.0) is   |

|-------|----------------------------------------------|

|       | not used in the determination of the PWM     |

|       | frequency. The postscaler could be used to   |

|       | have a servo update rate at a different fre- |

|       | quency than the PWM output.                  |

#### 7.3.2 PWM ON-TIME

The PWM on-time is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. CCPR1L contains eight MSbs and CCP1CON<5:4> contains two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

CCPR1L and CCP1CON<5:4> can be written to at any time, but the on-time value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM on-time. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2 concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

Maximum PWM resolution (bits) for a given PWM frequency:

Resolution =

$$\frac{\log(\frac{Fosc}{Fpwm})}{\log(2)}$$

bits

Note: If the PWM on-time value is larger than the PWM period, the CCP1 pin will not be cleared.

For an example PWM period and on-time calculation, see the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

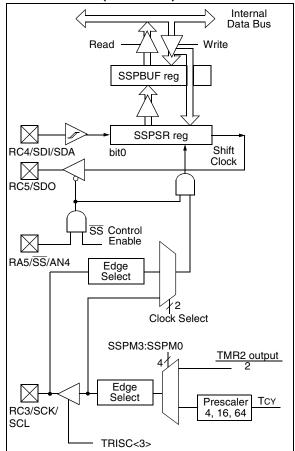

# 8.0 SYNCHRONOUS SERIAL PORT (SSP) MODULE

## 8.1 SSP Module Overview

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

For more information on SSP operation (including an I<sup>2</sup>C Overview), refer to the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023). Also, refer to Application Note AN578, *"Use of the SSP Module in the I<sup>2</sup>C Multi-Master Environment."*

# 8.2 SPI Mode

This section contains register definitions and operational characteristics of the SPI module.

Additional information on SPI operation may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

8.2.1 OPERATION OF SSP MODULE IN SPI MODE

A block diagram of the SSP Module in SPI Mode is shown in Figure 8-1.

The SPI mode allows 8-bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, three pins are used:

- Serial Data Out (SDO)RC5/SDO

- Serial Data In (SDI)RC4/SDI/SDA

- Serial Clock (SCK)RC3/SCK/SCL

Additionally, a fourth pin may be used when in a slave mode of operation:

Slave Select (SS)RA5/SS/AN4

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- Master Operation (SCK is the clock output)

- Slave Mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Clock Edge (Output data on rising/falling edge of SCK)

- Clock Rate (master operation only)

- Slave Select Mode (Slave mode only)

To enable the serial port, SSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON reg-

ister, and then set bit SSPEN. This configures the SDI, SDO, SCK and  $\overline{SS}$  pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISC register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (master operation) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set (if used)

Note: When the SPI is in Slave Mode with  $\overline{SS}$  pin control enabled, (SSPCON<3:0> = 0100) the SPI module will reset if the  $\overline{SS}$  pin is set to VDD.

**Note:** If the SPI is used in Slave Mode with CKE = '1', then the  $\overline{SS}$  pin control must be enabled.

#### FIGURE 8-1: SSP BLOCK DIAGRAM (SPI MODE)

#### 8.3.1.1 ADDRESSING

Once the SSP module has been enabled, it waits for a START condition to occur. Following the START condition, 8 bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register.

- b) The buffer full bit, BF is set.

- c) An ACK pulse is generated.

- d) SSP interrupt flag bit, SSPIF (PIR1<3>), is set (interrupt is generated if enabled) on the falling edge of the ninth SCL pulse.

In 10-bit address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal

'1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7-9 for slave-transmitter:

- 1. Receive first (high) byte of Address (bits SSPIF, BF, and bit UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of Address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of Address (bits SSPIF, BF, and UA are set).

- 5. Update the SSPADD register with the first (high) byte of Address, if match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive repeated START condition.

- 8. Receive first (high) byte of Address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

| Status Bits as Data<br>Transfer is Received |       |                    |                       | Set bit SSPIF                        |  |

|---------------------------------------------|-------|--------------------|-----------------------|--------------------------------------|--|

| BF                                          | SSPOV | $SSPSR \to SSPBUF$ | Generate ACK<br>Pulse | (SSP Interrupt occurs<br>if enabled) |  |

| 0                                           | 0     | Yes                | Yes                   | Yes                                  |  |

| 1                                           | 0     | No                 | No                    | Yes                                  |  |

| 1                                           | 1     | No                 | No                    | Yes                                  |  |

| 0                                           | 1     | Yes                | No                    | Yes                                  |  |

#### TABLE 8-2 DATA TRANSFER RECEIVED BYTE ACTIONS

Note: Shaded cells show the conditions where the user software did not properly clear the overflow condition.

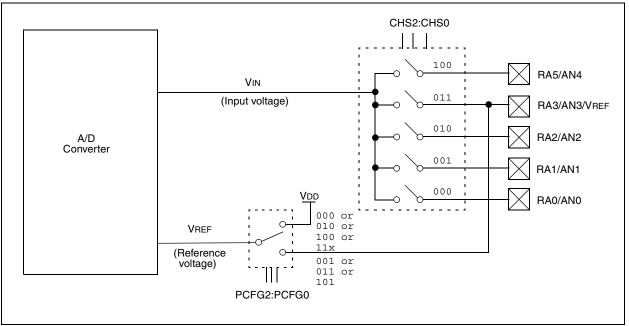

When the A/D conversion is complete, the result is loaded into the ADRES register, the GO/DONE bit, ADCON0<2>, is cleared, and the A/D interrupt flag bit, ADIF, is set. The block diagram of the A/D module is shown in Figure 9-1.

The value that is in the ADRES register is not modified for a Power-on Reset. The ADRES register will contain unknown data after a Power-on Reset.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see Section 9.1. After this acquisition time has elapsed, the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins / voltage reference / and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:

Polling for the GO/DONE bit to be cleared

- OR

- Waiting for the A/D interrupt

- 6. Read A/D Result register (ADRES), clear bit ADIF if required.

- 7. For next conversion, go to step 1 or step 2 as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2TAD is required before next acquisition starts.

#### FIGURE 9-1: A/D BLOCK DIAGRAM

## 9.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 9.5TAD per 8-bit conversion. The source of the A/D conversion clock is software selectable. The four possible options for TAD are:

- 2Tosc

- 8Tosc

- 32Tosc

- Internal RC oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu s.$

The A/D module can operate during sleep mode, but the RC oscillator must be selected as the A/D clock source prior to the SLEEP instruction.

Table 9-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

# 9.3 Configuring Analog Port Pins

The ADCON1 and TRISA registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS2:CHS0 bits and the TRIS bits.

- Note 1: When reading the port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs, will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- **Note 2:** Analog levels on any pin that is defined as a digital input (including the AN4:AN0 pins) may cause the input buffer to consume current that is out of the devices specification.

# TABLE 9-1TAD vs. DEVICE OPERATING FREQUENCIES

| AD Cloc           | k Source (TAD) | Device Frequency          |                           |                           |                         |  |  |

|-------------------|----------------|---------------------------|---------------------------|---------------------------|-------------------------|--|--|

| Operation         | ADCS1:ADCS0    | 20 MHz                    | 5 MHz                     | 1.25 MHz                  | 333.33 kHz              |  |  |

| 2Tosc             | 00             | 100 ns <sup>(2)</sup>     | 400 ns <sup>(2)</sup>     | 1.6 μs                    | 6 μs                    |  |  |

| 8Tosc             | 01             | 400 ns <sup>(2)</sup>     | 1.6 μs                    | 6.4 μs                    | 24 μs <sup>(3)</sup>    |  |  |

| 32Tosc            | 10             | 1.6 μs                    | 6.4 μs                    | 25.6 μs <sup>(3)</sup>    | 96 μs <sup>(3)</sup>    |  |  |

| RC <sup>(5)</sup> | 11             | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1)</sup> |  |  |

Legend: Shaded cells are outside of recommended range.

Note 1: The RC source has a typical TAD time of 4  $\mu$ s.

- 2: These values violate the minimum required TAD time.

- **3:** For faster conversion times, the selection of another clock source is recommended.

- 4: When device frequency is greater than 1 MHz, the RC A/D conversion clock source is recommended for sleep operation only.

- 5: For extended voltage devices (LC), please refer to Electrical Specifications section.

## 9.4 <u>A/D Conversions</u>

| Note: | The GO/DONE bit should NOT be set in        |

|-------|---------------------------------------------|

|       | the same instruction that turns on the A/D. |

#### 9.5 Use of the CCP Trigger

An A/D conversion can be started by the "special event trigger" of the CCP1 module. This requires that the CCP1M3:CCP1M0 bits (CCP1CON<3:0>) be programmed as 1011 and that the A/D module be enabled (ADON bit is set). When the trigger occurs, the

TABLE 9-2 SUMMARY OF A/D REGISTERS

GO/DONE bit will be set, starting the A/D conversion, and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D acquisition period with minimal software overhead. The appropriate analog input channel must be selected and the minimum acquisition time must pass before the "special event trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), then the "special event trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

| Address | Name   | Bit 7   | Bit 6      | Bit 5   | Bit 4                         | Bit 3 | Bit 2   | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all other Resets |

|---------|--------|---------|------------|---------|-------------------------------|-------|---------|--------|--------|-------------------------|---------------------------|

| 0Bh,8Bh | INTCON | GIE     | PEIE       | TOIE    | INTE                          | RBIE  | T0IF    | INTF   | RBIF   | 0000 000x               | 0000 000u                 |

| 0Ch     | PIR1   | _       | ADIF       | —       | _                             | SSPIF | CCP1IF  | TMR2IF | TMR1IF | -0 0000                 | -0 0000                   |

| 8Ch     | PIE1   | _       | ADIE       | —       | _                             | SSPIE | CCP1IE  | TMR2IE | TMR1IE | -0 0000                 | -0 0000                   |

| 1Eh     | ADRES  | A/D Res | ult Regist | er      |                               |       |         |        |        | xxxx xxxx               | uuuu uuuu                 |

| 1Fh     | ADCON0 | ADCS1   | ADCS0      | CHS2    | CHS1                          | CHS0  | GO/DONE | —      | ADON   | 0000 00-0               | 0000 00-0                 |

| 9Fh     | ADCON1 | _       | —          | —       | —                             | —     | PCFG2   | PCFG1  | PCFG0  | 000                     | 000                       |

| 05h     | PORTA  | _       | _          | RA5     | RA4                           | RA3   | RA2     | RA1    | RA0    | 0x 0000                 | 0u 0000                   |

| 85h     | TRISA  |         | —          | PORTA D | PORTA Data Direction Register |       |         |        |        |                         | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D conversion.

# 10.2 Oscillator Configurations

#### 10.2.1 OSCILLATOR TYPES

The PIC16CXXX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

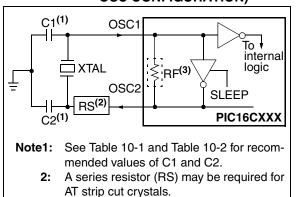

# 10.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

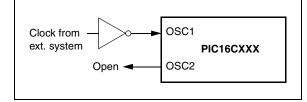

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 10-2). The PIC16CXXX oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can use an external clock source to drive the OSC1/CLKIN pin (Figure 10-3).

### FIGURE 10-2: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

3: RF varies with the crystal chosen.

#### FIGURE 10-3: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

# TABLE 10-1 CERAMIC RESONATORS

# Ranges Tested:

| Ranges lested:                               |                                      |                           |               |  |  |  |

|----------------------------------------------|--------------------------------------|---------------------------|---------------|--|--|--|

| Mode                                         | Freq                                 | OSC1                      | 0\$C2         |  |  |  |

| XT                                           | 455 kHz                              | 68 - 100 pF               | 68 - 100 pF   |  |  |  |

|                                              | 2.0 MHz                              | 15 - 68 pF 🛛 <            | 15 - 68 pF    |  |  |  |

|                                              | 4.0 MHz                              | 15 - 68 pF                | ∖15, - 68 pF  |  |  |  |

| HS                                           | 8.0 MHz                              | 10 - 68(pF                | े10 - 68 pF   |  |  |  |

|                                              | 16.0 MHz                             | 10,-22,0F                 | 10 - 22 pF    |  |  |  |

|                                              | se values are f<br>es at bottom of y | ior design guidar<br>zage | nce only. See |  |  |  |

| Resonator                                    | rs Used: 🔨                           | Par -                     |               |  |  |  |

| 455 kHz                                      | Panasonie E                          | FO-A455K04B               | ± 0.3%        |  |  |  |

| 2.0 MHz                                      | Murata Érie (                        | CSA2.00MG                 | $\pm 0.5\%$   |  |  |  |

| 4.0 MHz                                      | Murata Erie CSA4.00MG ± 0.5%         |                           |               |  |  |  |

| 8.0 MAHZ                                     | Murata Erie CSA8.00MT ± 0.5%         |                           |               |  |  |  |

| 16.0 MHz                                     | Murata Erie CSA16.00MX ± 0.5%        |                           |               |  |  |  |

| Resonators did not have built-in capacitors. |                                      |                           |               |  |  |  |

# TABLE 10-2CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq | Cap. Range<br>C1                   | Cap. Range<br>C2      |

|----------|-----------------|------------------------------------|-----------------------|

| LP       | 32 kHz          | 33 pF                              | 33 pF                 |

|          | 200 kHz         | 15 pF                              | 15 pF                 |

| XT       | 200 kHz         | 47-68 pF                           | 47-68 pF              |

|          | 1 MHz           | 15 pF 🔍                            | ↓15.pF<br>15.pF       |

|          | 4 MHz           | 15 pF 🕟                            | 15 pF                 |

| HS       | 4 MHz           | 15 pt                              | ✓ 15 pF               |

|          | 8 MHz           | 15-33 pE>                          | 15-33 pF              |

|          | 20 MHz          | (15-33 pF                          | 15-33 pF              |

|          | values are      | <b>for design guida</b> r<br>page. | n <b>ce only.</b> See |

|          | Crys            | tals Used                          |                       |

| 32 kHz   | Epson C-00      | 01R32.768K-A                       | ± 20 PPM              |

| 200 kt/2 | STO XTL 2       | ± 20 PPM                           |                       |

| 1 MHz    | ECS ECS-        | ± 50 PPM                           |                       |

| 4 MHz    | ECS ECS-4       | ± 50 PPM                           |                       |

| 8 MHz    | EPSON CA        | -301 8.000M-C                      | ± 30 PPM              |

**Note 1:** Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

EPSON CA-301 20.000M-C

20 MHz

2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

± 30 PPM

- 3: Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- 4: Oscillator performance should be verified when migrating between devices (including PIC16C62A to PIC16C62B and PIC16C72 to PIC16C72A)

# **13.0 ELECTRICAL CHARACTERISTICS**

## Absolute Maximum Ratings (†)

| Ambient temperature under bias                                                                              | 55°C to +125°C            |

|-------------------------------------------------------------------------------------------------------------|---------------------------|

| Storage temperature                                                                                         |                           |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)                                          |                           |

| Voltage on VDD with respect to VSS                                                                          |                           |

| Voltage on MCLR with respect to Vss (Note 2)                                                                |                           |

| Voltage on RA4 with respect to Vss                                                                          |                           |

| Total power dissipation (Note 1)                                                                            |                           |

| Maximum current out of Vss pin                                                                              |                           |

| Maximum current into VDD pin                                                                                |                           |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                | ±20 mA                    |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                              |                           |

| Maximum output current sunk by any I/O pin                                                                  | 25 mA                     |

| Maximum output current sourced by any I/O pin                                                               | 25 mA                     |

| Maximum current sunk by PORTA and PORTB (combined)                                                          | 200 mA                    |

| Maximum current sourced by PORTA and PORTB (combined)                                                       | 200 mA                    |

| Maximum current sunk by PORTC                                                                               | 200 mA                    |

| Maximum current sourced by PORTC                                                                            | 200 mA                    |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-V | ЮН) x IOH} + ∑(VOI x IOL) |

**2:** Voltage spikes below Vss at the MCLR/VPP pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR/VPP pin, rather than pulling this pin directly to Vss.

**†** NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### 13.1 DC Characteristics: PIC16C62B/72A-04 (Commercial, Industrial, Extended) PIC16C62B/72A-20 (Commercial, Industrial, Extended)

|              |               |                                                                         |          |         |         |            | ns (unless otherwise stated)                                   |

|--------------|---------------|-------------------------------------------------------------------------|----------|---------|---------|------------|----------------------------------------------------------------|

| DC CHA       |               | DISTICS                                                                 | Operatir | ng temp | erature | e 0°C      | $\leq TA \leq +70^{\circ}C$ for commercial                     |

| DC CHA       | NACIE         |                                                                         |          |         |         | -40°C      | $\leq$ TA $\leq$ +85°C for industrial                          |

|              |               |                                                                         |          |         |         | -40°C      | $\leq$ TA $\leq$ +125°C for extended                           |

| Param<br>No. | Sym           | Characteristic                                                          | Min      | Тур†    | Max     | Units      | Conditions                                                     |

| -            |               |                                                                         |          |         |         |            |                                                                |

| D001         | Vdd           | Supply Voltage                                                          | 4.0      | -       | 5.5     | V          | XT, RC and LP osc mode                                         |

| D001A        |               |                                                                         | 4.5      | -       | 5.5     | V          | HS osc mode                                                    |

|              |               |                                                                         | VBOR*    | -       | 5.5     | V          | BOR enabled (Note 7)                                           |

| D002*        | Vdr           | RAM Data Retention<br>Voltage (Note 1)                                  | -        | 1.5     | -       | V          |                                                                |

| D003         | VPOR          | <b>VDD Start Voltage</b> to<br>ensure internal<br>Power-on Reset signal | -        | Vss     | -       | V          | See section on Power-on Reset for details                      |

| D004*        | SVDD          | VDD Rise Rate to                                                        | 0.05     | -       | -       | V/ms       |                                                                |

| D004A*       |               | ensure internal                                                         | TBD      | -       | -       |            | PWRT disabled (PWRTE bit set)                                  |

|              |               | Power-on Reset signal                                                   |          |         |         |            | See section on Power-on Reset for details                      |

| D005         | VBOR          | Brown-out Reset<br>voltage trip point                                   | 3.65     | -       | 4.35    | V          | BODEN bit set                                                  |

| D010         | IDD           | Supply Current                                                          | -        | 2.7     | 5       | mA         | XT, RC osc modes                                               |

|              |               | (Note 2, 5)                                                             |          |         |         |            | Fosc = 4 MHz, VDD = 5.5V (Note 4)                              |

| D013         |               |                                                                         | -        | 10      | 20      | mA         | HS osc mode                                                    |

| 2010         |               |                                                                         |          |         | 20      |            | Fosc = 20  MHz,  VDD = 5.5  V                                  |

| D020         | IPD           | Power-down Current                                                      | -        | 10.5    | 42      | μA         | VDD = 4.0V, WDT enabled,-40°C to +85°C                         |

|              |               | (Note 3, 5)                                                             | -        | 1.5     | 16      | μA         | VDD = $4.0V$ , WDT disabled, 0°C to +70°C                      |

| D021         |               |                                                                         | -        | 1.5     | 19      | μ <b>Α</b> | VDD = 4.0V, WDT disabled, -40°C to +85°C                       |

| D021B        |               |                                                                         | -        | 2.5     | 19      | μΑ         | VDD = $4.0V$ , WDT disabled, $-40^{\circ}C$ to $+125^{\circ}C$ |

|              |               | Module Differential                                                     |          |         |         |            |                                                                |

|              |               | Current (Note 6)                                                        |          |         |         |            |                                                                |

| D022*        | $\Delta IWDT$ | Watchdog Timer                                                          | -        | 6.0     | 20      | μA         | WDTE BIT SET, VDD = 4.0V                                       |

| D022A*       | $\Delta IBOR$ | Brown-out Reset                                                         | -        | TBD     | 200     | μA         | BODEN bit set, VDD = 5.0V                                      |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD,

$\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc mode, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: This is the voltage where the device enters the Brown-out Reset. When BOR is enabled, the device will perform a brown-out reset when VDD falls below VBOR.

# 13.3 DC Characteristics:

## cs: PIC16C62B/72A-04 (Commercial, Industrial, Extended) PIC16C62B/72A-20 (Commercial, Industrial, Extended) PIC16LC62B/72A-04 (Commercial, Industrial)

| DC CHA        | ARACTE | RISTICS                               | Operating          | tempe<br>voltage | rature 0'<br>-40'<br>-40<br>e VDD rang | °C ≤1<br>°C ≤1<br>°C ≤1 | less otherwise stated)<br>$A \le +70^{\circ}C$ for commercial<br>$A \le +85^{\circ}C$ for industrial<br>$A \le +125^{\circ}C$ for extended<br>escribed in DC spec Section 13.1 |

|---------------|--------|---------------------------------------|--------------------|------------------|----------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.  | Sym    | Characteristic                        | Min                | Тур†             | Max                                    | Units                   | Conditions                                                                                                                                                                     |

|               |        | Input Low Voltage                     |                    |                  |                                        |                         |                                                                                                                                                                                |

|               | VIL    | I/O ports                             |                    |                  |                                        |                         |                                                                                                                                                                                |

| D030<br>D030A |        | with TTL buffer                       | Vss<br>Vss         | -                | 0.15Vdd<br>0.8V                        | V<br>V                  | For entire VDD range $4.5V \le VDD \le 5.5V$                                                                                                                                   |

| D031          |        | with Schmitt Trigger buffer           | Vss                | -                | 0.2Vdd                                 | V                       |                                                                                                                                                                                |

| D032          |        | MCLR, OSC1 (in RC mode)               | Vss                | -                | 0.2Vdd                                 | V                       |                                                                                                                                                                                |

| D033          |        | OSC1 (in XT, HS and LP modes)         | Vss                | -                | 0.3Vdd                                 | V                       | Note1                                                                                                                                                                          |

|               |        | Input High Voltage                    |                    |                  |                                        |                         |                                                                                                                                                                                |

|               | Vін    | I/O ports                             |                    | -                |                                        |                         |                                                                                                                                                                                |

| D040          |        | with TTL buffer                       | 2.0                | -                | Vdd                                    | V                       | $4.5V \leq V\text{DD} \leq 5.5V$                                                                                                                                               |

| D040A         |        |                                       | 0.25Vd<br>D + 0.8V | -                | Vdd                                    | V                       | For entire VDD range                                                                                                                                                           |

| D041          |        | with Schmitt Trigger buffer           | 0.8Vdd             | -                | Vdd                                    | v                       | For entire VDD range                                                                                                                                                           |

| D042          |        | MCLR                                  | 0.8Vdd             | -                | Vdd                                    | V                       |                                                                                                                                                                                |

| D042A         |        | OSC1 (XT, HS and LP modes)            | 0.7Vdd             | -                | Vdd                                    | V                       | Note1                                                                                                                                                                          |

| D043          |        | OSC1 (in RC mode)                     | 0.9Vdd             | -                | Vdd                                    | V                       |                                                                                                                                                                                |

|               |        | Input Leakage Current<br>(Notes 2, 3) |                    |                  |                                        |                         |                                                                                                                                                                                |

| D060          | lı∟    | I/O ports                             | -                  | -                | ±1                                     | μA                      | $\label{eq:Vss} \begin{split} &Vss \leq V PIN \leq V DD, \\ &Pin \ at \ hi\ impedance \end{split}$                                                                             |

| D061          |        | MCLR, RA4/T0CKI                       | -                  | -                | ±5                                     | μA                      | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                                                                                       |

| D063          |        | OSC1                                  | -                  | -                | ±5                                     | μA                      | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc modes                                                                                                                            |

| D070          | IPURB  | PORTB weak pull-up current            | 50                 | 250              | 400                                    | μA                      | VDD = 5V, VPIN = VSS                                                                                                                                                           |

| D080          | Vol    | Output Low Voltage<br>I/O ports       | -                  | -                | 0.6                                    | v                       | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                                                                                                                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the device be driven with external clock in RC mode.

3: Negative current is defined as current sourced by the pin.

<sup>2:</sup> The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

| Param<br>No. | Sym      | Characteristic                          |                    | Min        | Тур† | Мах         | Units | Conditions |

|--------------|----------|-----------------------------------------|--------------------|------------|------|-------------|-------|------------|

| 10*          | TosH2ckL | OSC1↑ to CLKOUT↓                        |                    | —          | 75   | 200         | ns    | Note 1     |

| 11*          | TosH2ckH | OSC1↑ to CLKOUT↑                        |                    | —          | 75   | 200         | ns    | Note 1     |

| 12*          | TckR     | CLKOUT rise time                        |                    | _          | 35   | 100         | ns    | Note 1     |

| 13*          | TckF     | CLKOUT fall time                        |                    | _          | 35   | 100         | ns    | Note 1     |

| 14*          | TckL2ioV | CLKOUT ↓ to Port out valid              |                    | —          |      | 0.5TCY + 20 | ns    | Note 1     |

| 15*          | TioV2ckH | Port in valid before CLKOU              | т↑                 | Tosc + 200 |      | _           | ns    | Note 1     |

| 16*          | TckH2iol | Port in hold after CLKOUT               | $\uparrow$         | 0          |      | _           | ns    | Note 1     |

| 17*          | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to Port of | out valid          | —          | 50   | 150         | ns    |            |

| 18*          | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to Port    | PIC16CXX           | 100        |      | _           | ns    |            |

| 18A*         |          | input invalid (I/O in hold<br>time)     | PIC16LCXX          | 200        |      | _           | ns    |            |

| 19*          | TioV2osH | Port input valid to OSC11 (             | I/O in setup time) | 0          | _    | —           | ns    |            |

| 20*          | TioR     | Port output rise time                   | PIC16CXX           | —          | 10   | 40          | ns    |            |

| 20A*         |          |                                         | PIC16LCXX          | _          |      | 80          | ns    |            |

| 21*          | TioF     | Port output fall time                   | PIC16CXX           | —          | 10   | 40          | ns    |            |

| 21A*         |          |                                         | PIC16LCXX          | _          | _    | 80          | ns    |            |

| 22††*        | Tinp     | INT pin high or low time                | ·                  | Тсү        | _    | —           | ns    |            |

| 23††*        | Trbp     | RB7:RB4 change INT high                 | or low time        | Тсү        | _    | _           | ns    |            |

| TABLE 13-3: | CLKOUT AND I/O TIMING REQUIREMENTS |

|-------------|------------------------------------|

|             |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

tt These parameters are asynchronous events not related to any internal clock edge.

**Note 1:** Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

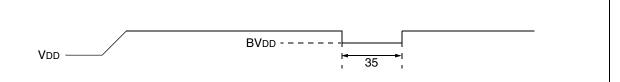

#### FIGURE 13-8: BROWN-OUT RESET TIMING

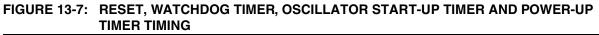

# TABLE 13-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                                   | Min | Тур†         | Max | Units | Conditions                                         |

|--------------|-------|--------------------------------------------------|-----|--------------|-----|-------|----------------------------------------------------|

| 30           | TmcL  | MCLR Pulse Width (low)                           | 2   | _            |     | μs    | VDD = 5V, -40°C to +125°C                          |

| 31*          | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler) | 7   | 18           | 33  | ms    | VDD = 5V, -40°C to +125°C                          |

| 32           | Tost  | Oscillator Start-up Timer Period                 |     | 1024<br>Tosc | —   | —     | Tosc = OSC1 period                                 |

| 33*          | Tpwrt | Power-up Timer Period                            | 28  | 72           | 132 | ms    | $VDD = 5V, -40^{\circ}C \text{ to } +125^{\circ}C$ |

| 34           | Tıoz  | I/O Hi-impedance from MCLR<br>Low or WDT reset   | _   | _            | 2.1 | μS    |                                                    |

| 35           | TBOR  | Brown-out Reset Pulse Width                      | 100 | _            | —   | μS    | $VDD \le BVDD$ (D005)                              |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

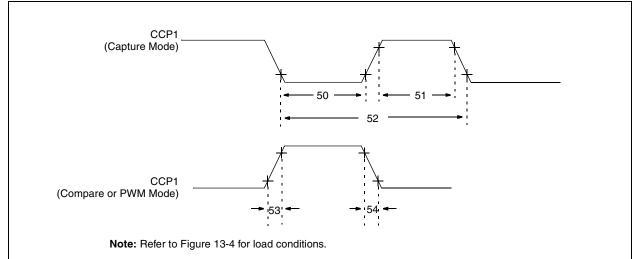

# FIGURE 13-10: CAPTURE/COMPARE/PWM TIMINGS

#### TABLE 13-6: CAPTURE/COMPARE/PWM REQUIREMENTS

| Param<br>No. | Sym  |                    | Characteristi  | С         | Min                   | Тур† | Max | Units | Conditions                         |

|--------------|------|--------------------|----------------|-----------|-----------------------|------|-----|-------|------------------------------------|

| 50*          | TccL | CCP1 input low     | No Prescaler   |           | 0.5TCY + 20           | —    | —   | ns    |                                    |

|              |      | time               | With Prescaler | PIC16CXX  | 10                    | _    | _   | ns    |                                    |

|              |      |                    |                | PIC16LCXX | 20                    | _    | _   | ns    |                                    |

| 51*          | TccH | CCP1 input high    | No Prescaler   |           | 0.5TCY + 20           | _    | _   | ns    |                                    |

|              |      | time               | With Prescaler | PIC16CXX  | 10                    | -    | —   | ns    |                                    |

|              |      |                    |                | PIC16LCXX | 20                    | _    | _   | ns    |                                    |

| 52*          | TccP | CCP1 input perior  | d              |           | <u>3Tcy + 40</u><br>N | -    | —   | ns    | N = prescale<br>value (1,4, or 16) |

| 53*          | TccR | CCP1 output rise   | time           | PIC16CXX  | —                     | 10   | 25  | ns    |                                    |

|              |      |                    |                | PIC16LCXX | —                     | 25   | 45  | ns    |                                    |

| 54*          | TccF | CCP1 output fall t | ime            | PIC16CXX  | —                     | 10   | 25  | ns    |                                    |

|              |      |                    |                | PIC16LCXX | —                     | 25   | 45  | ns    |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

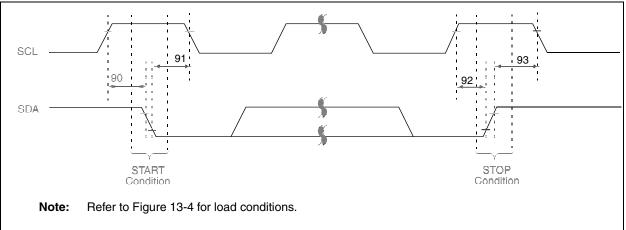

# FIGURE 13-15: I<sup>2</sup>C BUS START/STOP BITS TIMING

# TABLE 13-11: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

| Parameter<br>No. | Sym     | Charac          | teristic     | Min  | Ту<br>р | Max | Unit<br>s | Conditions                        |

|------------------|---------|-----------------|--------------|------|---------|-----|-----------|-----------------------------------|

| 90*              | TSU:STA | START condition | 100 kHz mode | 4700 |         | —   | ns        | Only relevant for repeated        |

|                  |         | Setup time      | 400 kHz mode | 600  | _       | —   |           | START condition                   |

| 91*              | THD:STA | START condition | 100 kHz mode | 4000 |         | —   | ns        | After this period the first clock |

|                  |         | Hold time       | 400 kHz mode | 600  |         | —   |           | pulse is generated                |

| 92*              | TSU:STO | STOP condition  | 100 kHz mode | 4700 |         | —   | ns        |                                   |

|                  |         | Setup time      | 400 kHz mode | 600  |         | —   |           |                                   |

| 93               | THD:STO | STOP condition  | 100 kHz mode | 4000 | —       | —   | ns        |                                   |

|                  |         | Hold time       | 400 kHz mode | 600  | _       | —   |           |                                   |

These parameters are characterized but not tested.

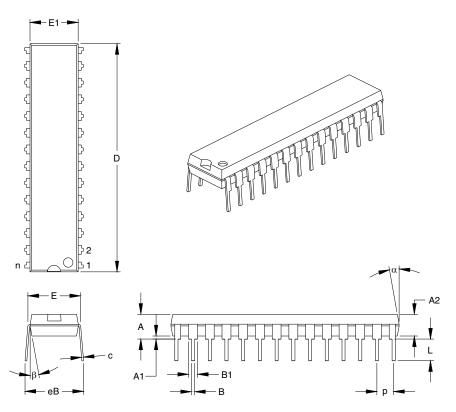

#### 28-Lead Skinny Plastic Dual In-line (SP) – 300 mil (PDIP) 15.2

|                            | Units  |       | INCHES* |       | Ν     | <b>IILLIMETERS</b> | 3     |

|----------------------------|--------|-------|---------|-------|-------|--------------------|-------|

| Dimension                  | Limits | MIN   | NOM     | MAX   | MIN   | NOM                | MAX   |

| Number of Pins             | n      |       | 28      |       |       | 28                 |       |

| Pitch                      | р      |       | .100    |       |       | 2.54               |       |

| Top to Seating Plane       | Α      | .140  | .150    | .160  | 3.56  | 3.81               | 4.06  |

| Molded Package Thickness   | A2     | .125  | .130    | .135  | 3.18  | 3.30               | 3.43  |

| Base to Seating Plane      | A1     | .015  |         |       | 0.38  |                    |       |

| Shoulder to Shoulder Width | E      | .300  | .313    | .325  | 7.62  | 7.94               | 8.26  |

| Molded Package Width       | E1     | .279  | .307    | .335  | 7.09  | 7.80               | 8.51  |

| Overall Length             | D      | 1.345 | 1.365   | 1.385 | 34.16 | 34.67              | 35.18 |

| Tip to Seating Plane       | L      | .125  | .130    | .135  | 3.18  | 3.30               | 3.43  |

| Lead Thickness             | С      | .008  | .012    | .015  | 0.20  | 0.29               | 0.38  |

| Upper Lead Width           | B1     | .040  | .053    | .065  | 1.02  | 1.33               | 1.65  |

| Lower Lead Width           | В      | .016  | .019    | .022  | 0.41  | 0.48               | 0.56  |

| Overall Row Spacing        | eB     | .320  | .350    | .430  | 8.13  | 8.89               | 10.92 |

| Mold Draft Angle Top       | α      | 5     | 10      | 15    | 5     | 10                 | 15    |

| Mold Draft Angle Bottom    | β      | 5     | 10      | 15    | 5     | 10                 | 15    |

\*Controlling Parameter

Notes: Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-095 Drawing No. C04-070

| Instruction Set |                                | 67    |

|-----------------|--------------------------------|-------|

| ADDLW .         |                                | 69    |

|                 |                                |       |

|                 |                                |       |

|                 |                                |       |

|                 |                                |       |

|                 |                                |       |

|                 |                                | ••••• |

|                 |                                |       |

|                 |                                |       |

| -               |                                |       |

| -               | -                              |       |

|                 |                                |       |

|                 |                                |       |

| -               |                                |       |

|                 |                                |       |

|                 |                                |       |

| INCFSZ          |                                | 71    |

| IORLW           |                                | 72    |

| IORWF           |                                | 72    |

| MOVF            |                                | 72    |

|                 |                                |       |

| -               |                                |       |

|                 |                                |       |

|                 |                                | -     |

|                 |                                |       |

|                 |                                |       |

|                 |                                | -     |

|                 |                                | -     |

|                 |                                |       |

|                 |                                |       |

|                 |                                |       |

|                 |                                |       |

| -               |                                |       |

| -               |                                |       |

|                 | ster                           |       |

| 0               |                                | /     |

|                 |                                | -     |

|                 |                                |       |

|                 |                                | -     |

| RBIE Bit        |                                | 13    |

| RBIF Bit        |                                | 3, 21 |

| T0IE Bit        |                                | 13    |

| T0IF Bit        |                                | 13    |

|                 | ces5                           |       |

|                 | version Complete               |       |

|                 | igram                          |       |

|                 | Complete (CCP)                 |       |

|                 | Complete (CCP)                 |       |

| Interrupt of    | on Change (RB7:RB4)            | 21    |

|                 | Pin, External                  |       |

|                 | eive/Transmit Complete2        |       |

|                 | /erflow                        |       |

|                 | PR2 Match                      |       |

|                 | PR2 Match (PWM)                |       |

|                 | ntext Saving During            |       |

| Interrupts, Ena |                                |       |

|                 | verter Enable (ADIE Bit)       | 14    |

|                 | able (CCP1IE Bit)              |       |

| Global Int      | terrupt Enable (GIE Bit)1      | 3, 62 |

|                 | on Change (RB7:RB4)            | , .=  |

| Enable (F       | RBIE Bit) 1                    |       |

|                 | al Interrupt Enable (PEIE Bit) |       |

| RB0/INT Enable (INTE Bit)13<br>SSP Enable (SSPIE Bit)14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSP Enable (SSPIE Bit)14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $TMDOO_{varflow}$ Enchlo (TOLE Dit) 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TMR0 Overflow Enable (T0IE Bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TMR1 Overflow Enable (TMR1IE Bit)14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TMR2 to PR2 Match Enable (TMR2IE Bit) 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |