Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| -                          |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Details                    |                                                                            |

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc72a-04-ss |

**NOTES:**

#### 2.2 <u>Data Memory Organization</u>

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 and RP0 are the bank select bits.

RP1<sup>(1)</sup> RP0

(STATUS<6:5>)

- $= 00 \rightarrow Bank0$

- $= 01 \rightarrow Bank1$

- = 10 → Bank2 (not implemented)

- =  $11 \rightarrow Bank3$  (not implemented)

Note 1: Maintain this bit clear to ensure upward compatibility with future products.

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some "high use" Special Function Registers from one bank may be mirrored in another bank for code reduction and guicker access.

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register FSR (Section 2.5).

FIGURE 2-2: REGISTER FILE MAP

| File                  |                            |                       | File    |  |  |  |  |  |  |  |

|-----------------------|----------------------------|-----------------------|---------|--|--|--|--|--|--|--|

| Address               | <del></del>                | <del></del>           | Address |  |  |  |  |  |  |  |

| 00h                   | INDF <sup>(1)</sup>        | INDF <sup>(1)</sup>   | 80h     |  |  |  |  |  |  |  |

| 01h                   | TMR0                       | OPTION_REG            | 81h     |  |  |  |  |  |  |  |

| 02h                   | PCL                        | PCL                   | 82h     |  |  |  |  |  |  |  |

| 03h                   | STATUS                     | STATUS                | 83h     |  |  |  |  |  |  |  |

| 04h                   | FSR                        | FSR                   | 84h     |  |  |  |  |  |  |  |

| 05h                   | PORTA                      | TRISA                 | 85h     |  |  |  |  |  |  |  |

| 06h                   | PORTB                      | TRISB                 | 86h     |  |  |  |  |  |  |  |

| 07h                   | PORTC                      | TRISC                 | 87h     |  |  |  |  |  |  |  |

| 08h                   |                            | _                     | 88h     |  |  |  |  |  |  |  |

| 09h                   | _                          | _                     | 89h     |  |  |  |  |  |  |  |

| 0Ah                   | PCLATH                     | PCLATH                | 8Ah     |  |  |  |  |  |  |  |

| 0Bh                   | INTCON                     | INTCON                | 8Bh     |  |  |  |  |  |  |  |

| 0Ch                   | PIR1                       | PIE1                  | 8Ch     |  |  |  |  |  |  |  |

| 0Dh                   | _                          | -                     | 8Dh     |  |  |  |  |  |  |  |

| 0Eh                   | TMR1L                      | PCON                  | 8Eh     |  |  |  |  |  |  |  |

| 0Fh                   | TMR1H                      | _                     | 8Fh     |  |  |  |  |  |  |  |

| 10h                   | T1CON                      | _                     | 90h     |  |  |  |  |  |  |  |

| 11h                   | TMR2                       | _                     | 91h     |  |  |  |  |  |  |  |

| 12h                   | T2CON                      | PR2                   | 92h     |  |  |  |  |  |  |  |

| 13h                   | SSPBUF                     | SSPADD                | 93h     |  |  |  |  |  |  |  |

| 14h                   | SSPCON                     | SSPSTAT               | 94h     |  |  |  |  |  |  |  |

| 15h                   | CCPR1L                     | _                     | 95h     |  |  |  |  |  |  |  |

| 16h                   | CCPR1H                     | _                     | 96h     |  |  |  |  |  |  |  |

| 17h                   | CCP1CON                    | _                     | 97h     |  |  |  |  |  |  |  |

| 18h                   | _                          | _                     | 98h     |  |  |  |  |  |  |  |

| 19h                   | _                          | _                     | 99h     |  |  |  |  |  |  |  |

| 1Ah                   | _                          | _                     | 9Ah     |  |  |  |  |  |  |  |

| 1Bh                   | _                          | _                     | 9Bh     |  |  |  |  |  |  |  |

| 1Ch                   | _                          | _                     | 9Ch     |  |  |  |  |  |  |  |

| 1Dh                   | _                          | _                     | 9Dh     |  |  |  |  |  |  |  |

| 1Eh                   | ADRES <sup>(2)</sup>       | _                     | 9Eh     |  |  |  |  |  |  |  |

| 1Fh                   | ADCON0 <sup>(2)</sup>      | ADCON1 <sup>(2)</sup> | 9Fh     |  |  |  |  |  |  |  |

| 20h                   |                            | General               | A0h     |  |  |  |  |  |  |  |

|                       |                            | Purpose               |         |  |  |  |  |  |  |  |

| General Registers BFh |                            |                       |         |  |  |  |  |  |  |  |

|                       | Purpose<br>Registers — C0h |                       |         |  |  |  |  |  |  |  |

|                       | negisters                  | _                     |         |  |  |  |  |  |  |  |

| 7Fh                   |                            | _                     | FFh     |  |  |  |  |  |  |  |

| Į.                    | Bank 0                     | Bank 1                | ļ       |  |  |  |  |  |  |  |

| Uni                   | implemented da             | ata memory loca       | tions,  |  |  |  |  |  |  |  |

| read                  | l as '0'.                  | •                     |         |  |  |  |  |  |  |  |

| Note 1: No            | ot a physical red          | aister.               |         |  |  |  |  |  |  |  |

Note 1: Not a physical register.

2: These registers are not implemented on the PIC16C62B, read as '0'.

#### 2.2.2.2 OPTION\_REG REGISTER

The OPTION\_REG register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known as the prescaler), the External INT Interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

#### REGISTER 2-2: OPTION\_REG REGISTER (ADDRESS 81h)

| R/W-1    | R/W-1                                         | R/W-1            | R/W-1       | R/W-1       | R/W-1                  | R/W-1 | R/W-1 |                                           |

|----------|-----------------------------------------------|------------------|-------------|-------------|------------------------|-------|-------|-------------------------------------------|

| RBPU     | INTEDG                                        | T0CS             | T0SE        | PSA         | PS2                    | PS1   | PS0   | R = Readable bit                          |

| bit7     |                                               |                  |             |             |                        |       | bit0  | W = Writable bit - n = Value at POR reset |

| bit 7:   | <b>RBPU</b> : PO<br>1 = PORTI<br>0 = PORTI    | 3 pull-ups       | s are disal | bled        | PORTB inp              | outs  |       | - II – Value at i Officeet                |

| bit 6:   | INTEDG: Interru<br>1 = Interru<br>0 = Interru | pt on risir      | ng edge o   | f RB0/INT   | •                      |       |       |                                           |

| bit 5:   | TOCS: TMI  1 = Transit  0 = Interna           | ion on R         | A4/T0CKI    | pin         | (OUT)                  |       |       |                                           |

| bit 4:   |                                               | ent on hi        | gh-to-low   | transition  | on RA4/T0<br>on RA4/T0 |       |       |                                           |

| bit 3:   | PSA: Pres<br>1 = Presca<br>0 = Presca         | ıler is ass      | igned to t  | he WDT      | ) module               |       |       |                                           |

| bit 2-0: | PS2:PS0:                                      | Prescale         | r Rate Sel  | lect bits   |                        |       |       |                                           |

|          | Bit Value                                     | TMR0 R           | ate WD      | ΓRate       |                        |       |       |                                           |

|          | 000                                           | 1:2<br>1:4       | 1:          |             |                        |       |       |                                           |

|          | 010                                           | 1:8              |             | : 4         |                        |       |       |                                           |

|          | 011<br>100                                    | 1:16             |             | : 8<br>: 16 |                        |       |       |                                           |

|          | 100                                           | 1 : 32<br>1 : 64 | -           | : 32        |                        |       |       |                                           |

|          | 110                                           | 1:12             |             | : 64        |                        |       |       |                                           |

|          | 111                                           | 1:25             | 6 1         | : 128       |                        |       |       |                                           |

|          |                                               |                  |             |             |                        |       |       |                                           |

#### 5.0 TIMER1 MODULE

The Timer1 module timer/counter has the following features:

- 16-bit timer/counter

- · Readable and writable

- · Internal or external clock select

- · Interrupt on overflow from FFFFh to 0000h

- · Reset from CCP module trigger

Timer1 has a control register, shown in Register 5-1. Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Figure 5-1 is a simplified block diagram of the Timer1 module.

Additional information on timer modules is available in the  $PIC^{\textcircled{\tiny{0}}}$  MCU Mid-Range Reference Manual, (DS33023).

#### 5.1 <u>Timer1 Operation</u>

Timer1 can operate in one of these modes:

- · As a timer

- · As a synchronous counter

- · As an asynchronous counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In timer mode, Timer1 increments every instruction cycle. In counter mode, it increments on every rising edge of the external clock input.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored.

Timer1 also has an internal "reset input". This reset can be generated by the CCP module as a special event trigger (Section 7.0).

#### REGISTER 5-1:T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

|          |                                           |                                                                    |                           |                                      |             | `                       | •       | •                                                                          |

|----------|-------------------------------------------|--------------------------------------------------------------------|---------------------------|--------------------------------------|-------------|-------------------------|---------|----------------------------------------------------------------------------|

| U-0      | U-0                                       | R/W-0                                                              | R/W-0                     | R/W-0                                | R/W-0       | R/W-0                   | R/W-0   |                                                                            |

| _        | _                                         | T1CKPS1                                                            | T1CKPS0                   | T10SCEN                              | T1SYNC      | TMR1CS                  | TMR10N  | R = Readable bit                                                           |

| oit7     |                                           |                                                                    |                           |                                      |             |                         | bit0    | W = Writable bit U = Unimplemented bit read as '0' - n = Value at POR rese |

| bit 7-6: | Unimple                                   | mented: F                                                          | Read as '0                | ļ                                    |             |                         |         | -                                                                          |

| bit 5-4: | 11 = 1:8<br>10 = 1:4<br>01 = 1:2          | Prescale v<br>Prescale v<br>Prescale v<br>Prescale v<br>Prescale v | /alue<br>/alue<br>/alue   | Input Cloc                           | ck Prescale | e Select bit            | S       |                                                                            |

| bit 3:   | 1 = Oscil<br>0 = Oscil                    | lator is ena<br>lator is shu                                       | abled (TRI<br>ut off      | Enable Co<br>SC<1:0> iç<br>reduce po | gnored)     |                         |         |                                                                            |

| bit 2:   | TMR1CS<br>1 = Do no<br>0 = Sync<br>TMR1CS | $\frac{S=1}{S}$ ot synchro<br>thronize ex<br>$\frac{S=0}{S}$       | nize exter<br>ternal cloo | nal clock in<br>ck input             | put         | ation Conti<br>when TMR |         |                                                                            |

| bit 1:   | 1 = Exter                                 |                                                                    | rom pin R                 | ce Select k<br>C0/T1OSC              |             | n the rising            | g edge) |                                                                            |

| bit 0:   |                                           | <b>l</b> : Timer1 (<br>bles Timer1<br>s Timer1                     |                           |                                      |             |                         |         |                                                                            |

|          |                                           |                                                                    |                           |                                      |             |                         |         |                                                                            |

**NOTES:**

#### 7.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- · driven High

- · driven Low

- · remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). The interrupt flag bit, CCP1IF, is set on all compare matches.

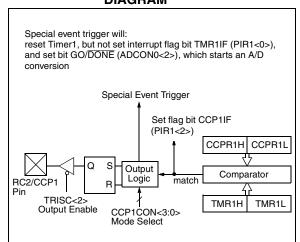

# FIGURE 7-2: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 7.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

Note: Clearing the CCP1CON register will force the RC2/CCP1 compare output latch to the default low level. This is not the data latch.

#### 7.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 7.2.3 SOFTWARE INTERRUPT MODE

When a generated software interrupt is chosen, the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 7.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated, which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special trigger output of CCP1 resets the TMR1 register pair and starts an A/D conversion (if the A/D module is enabled).

TABLE 7-3 REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

| Address | Name    | Bit 7       | Bit 6                               | Bit 5        | Bit 4       | Bit 3         | Bit 2      | Bit 1       | Bit 0     | Value on<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|---------|-------------|-------------------------------------|--------------|-------------|---------------|------------|-------------|-----------|-------------------------|---------------------------------|

| 0Bh,8Bh | INTCON  | GIE         | PEIE                                | TOIE         | INTE        | RBIE          | TOIF       | INTF        | RBIF      | 0000 000x               | 0000 000u                       |

| 0Ch     | PIR1    | _           | ADIF                                | _            | _           | SSPIF         | CCP1IF     | TMR2IF      | TMR1IF    | -0 0000                 | -0 0000                         |

| 8Ch     | PIE1    | _           | ADIE                                | _            | _           | SSPIE         | CCP1IE     | TMR2IE      | TMR1IE    | -0 0000                 | -0 0000                         |

| 87h     | TRISC   | PORTC Da    | ata Dire                            | ection Regis | ter         |               |            |             |           | 1111 1111               | 1111 1111                       |

| 0Eh     | TMR1L   | Holding reg | gister fo                           | or the Least | Significant | Byte of the   | 16-bit TMF | R1 register |           | xxxx xxxx               | uuuu uuuu                       |

| 0Fh     | TMR1H   | Holding reg | gister fo                           | or the Most  | Significant | Byte of the 1 | 16-bit TMR | 1register   |           | xxxx xxxx               | uuuu uuuu                       |

| 10h     | T1CON   | _           | _                                   | T1CKPS1      | T1CKPS0     | T10SCEN       | T1SYNC     | TMR1CS      | TMR10N    | 00 0000                 | uu uuuu                         |

| 15h     | CCPR1L  | Capture/Co  | Capture/Compare/PWM register1 (LSB) |              |             |               |            |             | xxxx xxxx | uuuu uuuu               |                                 |

| 16h     | CCPR1H  | Capture/Co  | Capture/Compare/PWM register1 (MSB) |              |             |               |            |             |           | xxxx xxxx               | uuuu uuuu                       |

| 17h     | CCP1CON | _           | _                                   | CCP1X        | CCP1Y       | CCP1M3        | CCP1M2     | CCP1M1      | CCP1M0    | 00 0000                 | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by Capture and Timer1.

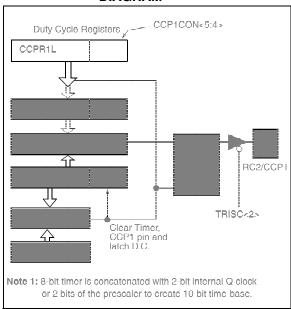

#### 7.3 PWM Mode

In Pulse Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

Note: Clearing the CCP1CON register will force the CCP1 PWM output latch to the default low level. This is not the PORTC I/O data latch

Figure 7-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step by step procedure on how to set up the CCP module for PWM operation, see Section 7.3.3.

FIGURE 7-3: SIMPLIFIED PWM BLOCK DIAGRAM

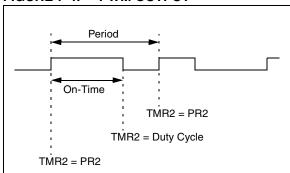

A PWM output (Figure 7-4) has a time base (period) and a time that the output stays high (on-time). The frequency of the PWM is the inverse of the period (1/period).

FIGURE 7-4: PWM OUTPUT

#### 7.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

PWM period =

$$[(PR2) + 1] \cdot 4 \cdot TOSC \cdot (TMR2 \text{ prescale value})$$

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- · TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

Note: The Timer2 postscaler (see Section 6.0) is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

#### 7.3.2 PWM ON-TIME

The PWM on-time is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. CCPR1L contains eight MSbs and CCP1CON<5:4> contains two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

CCPR1L and CCP1CON<5:4> can be written to at any time, but the on-time value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM on-time. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2 concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

Maximum PWM resolution (bits) for a given PWM frequency:

Resolution =

$$\frac{\log \left( \frac{\text{Fosc}}{\text{Fpwm}} \right)}{\log(2)}$$

bits

**Note:** If the PWM on-time value is larger than the PWM period, the CCP1 pin will not be cleared.

For an example PWM period and on-time calculation, see the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

#### REGISTER 8-2: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 SSPOV CKP SSPM1 SSPM0 WCOL **SSPEN** SSPM3 SSPM2 bit7 bit0

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as '0'

- n =Value at POR reset

bit 7: WCOL: Write Collision Detect bit

1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)

0 = No collision

bit 6: SSPOV: Receive Overflow Indicator bit

#### In SPI mode

1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is lost. Overflow can only occur in slave mode. The user must read the SSPBUF, even if only transmitting data, to avoid setting overflow. In master operation, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPBUF register.

0 = No overflow

#### In I<sup>2</sup>C mode

- 1 = A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don't care" in transmit mode. SSPOV must be cleared in software in either mode.

- 0 = No overflow

- bit 5: SSPEN: Synchronous Serial Port Enable bit

#### In SPI mode

- 1 = Enables serial port and configures SCK, SDO, and SDI as serial port pins

- 0 = Disables serial port and configures these pins as I/O port pins

#### In I<sup>2</sup>C mode

- 1 = Enables the serial port and configures the SDA and SCL pins as serial port pins

- 0 = Disables serial port and configures these pins as I/O port pins

In both modes, when enabled, these pins must be properly configured as input or output.

bit 4: CKP: Clock Polarity Select bit

#### In SPI mode

- 1 = Idle state for clock is a high level

- 0 = Idle state for clock is a low level

#### In I<sup>2</sup>C mode

SCK release control

- 1 = Enable clock

- 0 = Holds clock low (clock stretch)

- bit 3-0: SSPM3:SSPM0: Synchronous Serial Port Mode Select bits

- 0000 = SPI master operation, clock = Fosc/4

- 0001 = SPI master operation, clock = Fosc/16

- 0010 = SPI master operation, clock = Fosc/64

- 0011 = SPI master operation, clock = TMR2 output/2

- 0100 = SPI slave mode, clock = SCK pin.  $\overline{SS}$  pin control enabled.

- 0101 = SPI slave mode, clock = SCK pin.  $\overline{SS}$  pin control disabled.  $\overline{SS}$  can be used as I/O pin

- $0110 = I^2C$  slave mode, 7-bit address

- $0111 = I^2C$  slave mode, 10-bit address

- $1011 = I^2C$  firmware controlled master operation (slave idle)

- $1110 = I^2C$  slave mode, 7-bit address with start and stop bit interrupts enabled

- $1111 = I^2C$  slave mode, 10-bit address with start and stop bit interrupts enabled

# 10.0 SPECIAL FEATURES OF THE CPU

The PIC16C62B/72A devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Mode Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- · Watchdog Timer (WDT)

- SLEEP

- Code protection

- · ID locations

- In-circuit serial programming<sup>™</sup> (ICSP)

These devices have a Watchdog Timer, which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The

other is the Power-up Timer (PWRT), which provides a fixed delay on power-up only and is designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

Additional information on special features is available in the  $PIC^{\textcircled{\tiny{0}}}$  MCU Mid-Range Reference Manual, (DS33023).

#### 10.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

#### FIGURE 10-1: CONFIGURATION WORD

CP1 CP0 CP1 CP0 CP1 CP0 BODEN CP1 CP0 **PWRTE** WDTE FOSC1 FOSC0 Register: CONFIG Address: 2007h bit13 bit0 bit 13-8 CP1:CP0: Code Protection bits (2) 5-4: 11 = Code protection off 10 = Upper half of program memory code protected 01 = Upper 3/4th of program memory code protected 00 = All memory is code protected bit 7: Unimplemented: Read as '1' **BODEN**: Brown-out Reset Enable bit (1) bit 6: 1 = BOR enabled 0 = BOR disabled **PWRTE**: Power-up Timer Enable bit (1) bit 3: 1 = PWRT disabled 0 = PWRT enabled bit 2: WDTE: Watchdog Timer Enable bit 1 = WDT enabled 0 = WDT disabled bit 1-0: FOSC1:FOSC0: Oscillator Selection bits 11 = RC oscillator 10 = HS oscillator 01 = XT oscillator 00 = LP oscillator Note 1: Enabling Brown-out Reset automatically enables Power-up Timer (PWRT), regardless of the value of bit PWRTE. All of the CP1:CP0 pairs must be given the same value to enable the code protection scheme listed.

#### 10.4 Power-On Reset (POR)

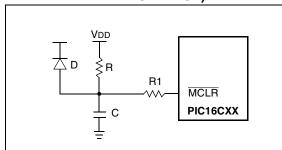

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.5V - 2.1V). To take advantage of the POR, just tie the MCLR pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified (SVDD, parameter D004). For a slow rise time, see Figure 10-6.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met. Brown-out Reset may be used to meet the start-up conditions.

FIGURE 10-6: EXTERNAL POWER-ON

RESET CIRCUIT (FOR SLOW

VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2:  $R < 40 \text{ k}\Omega$  is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- 3: R1 =  $100\Omega$  to 1 k $\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}$ /VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

#### 10.5 Power-up Timer (PWRT)

The Power-up Timer provides a fixed nominal time-out (TPWRT, parameter #33) from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip-to-chip due to VDD, temperature and process variation. See DC parameters for details.

#### 10.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a delay of 1024 oscillator cycles (from OSC1 input) after the PWRT delay is over (Tost, parameter #32). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

**Note:** The OST delay may not occur when the device wakes from SLEEP.

#### 10.7 Brown-Out Reset (BOR)

The configuration bit, BODEN, can enable or disable the Brown-Out Reset circuit. If VPP falls below Vbor (parameter #35, about  $100\mu S$ ), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a reset may not occur.

Once the brown-out occurs, the device will remain in brown-out reset until VDD rises above VBOR. The power-up timer then keeps the device in reset for TPWRT (parameter #33, about 72mS). If VDD should fall below VBOR during TPWRT, the brown-out reset process will restart when VDD rises above VBOR with the power-up timer reset. The power-up timer is always enabled when the brown-out reset circuit is enabled, regardless of the state of the  $\overline{\text{PWRT}}$  configuration bit.

#### 10.10.1 INT INTERRUPT

The external interrupt on RB0/INT pin is edge triggered: either rising, if bit INTEDG (OPTION\_REG<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 10.13 for details on SLEEP mode.

#### 10.10.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>). (Section 4.0)

#### 10.10.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>). (Section 3.2)

#### 10.11 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt, (i.e., W register and STATUS register). This will have to be implemented in software.

Example 10-1 stores and restores the W and STATUS registers. The register, W\_TEMP, must be defined in each bank and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1).

The example:

- a) Stores the W register.

- b) Stores the STATUS register in bank 0.

- c) Stores the PCLATH register.

- d) Executes the interrupt service routine code (User-generated).

- e) Restores the STATUS register (and bank select bit).

- f) Restores the W and PCLATH registers.

#### **EXAMPLE 10-1: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM**

```

MOVWF

W TEMP

;Copy W to TEMP register, could be bank one or zero

SWAPF

STATUS, W

;Swap status to be saved into W

CLRF

STATUS

; bank 0, regardless of current bank, Clears IRP, RP1, RP0

MOVWF

STATUS_TEMP

;Save status to bank zero STATUS_TEMP register

:(ISR)

SWAPF

STATUS TEMP, W

;Swap STATUS TEMP register into W

; (sets bank to original state)

MOVWF

STATUS

; Move W into STATUS register

SWAPF

W TEMP, F

;Swap W TEMP

SWAPF

W TEMP, W

;Swap W TEMP into W

```

TABLE 11-2 PIC16CXXX INSTRUCTION SET

| MSb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Mnemonic,                                                                                                                                        |        | Description                  | Cycles                |     | 14-Bit | Opcode | •    | Status   | Notes |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------|-----------------------|-----|--------|--------|------|----------|-------|--|

| ADDWF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Operands                                                                                                                                         |        |                              |                       | MSb |        |        | LSb  | Affected |       |  |

| ANDWF   f, d   AND W with f   1   00   0101   deff   feff   Z   2   2   CLRF   f   Clear W   1   00   0001   1   1   1   1   1   2   2   COMF   f, d   Complement f   1   00   0001   0000   0001   Z   COMF   f, d   Decrement f   1   00   0101   deff   feff   Z   1,2   1,2   DECF   f, d   Decrement f   1   00   0101   deff   feff   Z   1,2   DECFSZ   f, d   Decrement f, Skip if 0   1(2)   00   1011   deff   feff   Z   1,2   DECFSZ   f, d   Increment f   1   00   0101   deff   feff   Z   1,2   DECFSZ   f, d   Increment f   1   00   0101   deff   feff   Z   1,2   DECFSZ   f, d   Increment f   1   00   0100   deff   feff   Z   1,2   DECFSZ   f, d   Increment f   1   00   0100   deff   feff   Z   1,2   DECFSZ   f, d   Increment f   f   00   0100   deff   feff   Z   1,2   DECFSZ   f, d   Increment f   f   00   0100   deff   feff   Z   1,2   DECFSZ   f, d   Increment f   f   00   0100   deff   feff   Z   1,2   DECFSZ   f, d   Increment f   f   00   0100   deff   feff   Z   1,2   DECFSZ   f, d   Increment f   f   00   0100   deff   feff   Z   1,2   DECFSZ   f, d   Inclusive OR W with f   f   00   0100   deff   feff   Z   1,2   DECFSZ   f, d   Inclusive OR W with f   f   00   0100   deff   feff   Z   f,2   DECFSZ   DECFSZ   f, d   Inclusive OR W with f   f   00   0100   deff   feff   Z   f,2   DECFSZ   DECFSZ   f, d   Inclusive OR W with f   f   00   0100   deff   feff   Z   f,2   DECFSZ   f,4   DECFSZ   f,5   DECFS | BYTE-ORIE                                                                                                                                        | NTED   | FILE REGISTER OPERATIONS     |                       |     |        |        |      |          |       |  |

| CLRF         f         Clear W         1         00         0001         left         fff         Z         Z         CCRW         CLRW         1         00         0001         0001         QZ         Z         CCOMF         1         00         0010         deff         fff         Z         1,2         DECFSC         f, d         Decrement f         1         00         0011         dfff         ffff         Z         1,2         1,2         DECFSZ         f, d         Increment f         1         00         0011         dfff         ffff         Z         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2         1,2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ADDWF                                                                                                                                            | f, d   | Add W and f                  | 1                     | 00  | 0111   | dfff   | ffff | C,DC,Z   | 1,2   |  |

| CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ANDWF                                                                                                                                            | f, d   | AND W with f                 | 1                     | 00  | 0101   | dfff   | ffff | Z        | 1,2   |  |

| COMF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CLRF                                                                                                                                             | f      | Clear f                      | 1                     | 00  | 0001   | lfff   | ffff | Z        | 2     |  |

| DECF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CLRW                                                                                                                                             | -      | Clear W                      | 1                     | 00  | 0001   | 0000   | 0011 | Z        |       |  |

| DECFSZ   f, d   Increment   f, Skip if 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | COMF                                                                                                                                             | f, d   | Complement f                 | 1                     | 00  | 1001   | dfff   | ffff | Z        |       |  |

| INCF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DECF                                                                                                                                             | f, d   | Decrement f                  | 1                     | 00  | 0011   | dfff   | ffff | Z        | 1,2   |  |

| INCFSZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DECFSZ                                                                                                                                           | f, d   |                              | 1(2)                  | 00  | 1011   | dfff   | ffff |          | 1,2,3 |  |

| Inclusive OR W with f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | INCF                                                                                                                                             | f, d   | Increment f                  | 1                     | 00  | 1010   | dfff   | ffff | Z        | 1,2   |  |

| MOVF         f, d         Move W to f         1         00         1000         defff         ffff         Z         1,2           MOVWF         f         Move W to f         1         00         1000         0000         leftf         ffff         C         1,2           NOP         -         No Operation         1         00         0000         0xx0         0000         RF         Ffff         C         1,2           RRF         f, d         Rotate Right fthrough Carry         1         00         1100         dfff         ffff         C         1,2           SUBWF         f, d         Subtract W from f         1         00         1100         dfff         ffff         C         1,2           SWAPF         f, d         Swap nibbles in f         1         00         0110         dfff         ffff         Z         1,2           SWAPF         f, d         Swap nibbles in f         1         00         0110         dfff         ffff         Z         1,2           SWAPF         f, d         Sit Clear         1         0         010b         bfff         ffff         Z         1,2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | INCFSZ                                                                                                                                           | f, d   | Increment f, Skip if 0       | 1(2)                  | 00  | 1111   | dfff   | ffff |          | 1,2,3 |  |

| MOVF         f, d         Move W to f         1         00         1000         defff         fefff         Z         1,2           MOVWF         f         Move W to f         1         00         0000         leftf         fefff         C         1,2           NOP         -         No Operation         1         00         0000         0xx0         0000         RLF         ffff         C         1,2           RRF         f, d         Rotate Right f through Carry         1         00         1100         dfff         ffff         C         1,2           SUBWF         f, d         Subtract W from f         1         00         1100         dfff         ffff         C,DC,Z         1,2           SWAPF         f, d         Swap nibbles in f         1         00         0110         dfff         fffff         1,2         1,2           SWAPF         f, d         Exclusive OR W with f         1         0         010b         bfff         ffff         Z         1,2           BFF         f, b         Bit Clear f         1         0         01bb         bfff         ffff         2         1,2 <th col<="" th=""><th>IORWF</th><th>f, d</th><th>Inclusive OR W with f</th><th></th><th>00</th><th>0100</th><th>dfff</th><th>ffff</th><th>Z</th><th></th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <th>IORWF</th> <th>f, d</th> <th>Inclusive OR W with f</th> <th></th> <th>00</th> <th>0100</th> <th>dfff</th> <th>ffff</th> <th>Z</th> <th></th> | IORWF  | f, d                         | Inclusive OR W with f |     | 00     | 0100   | dfff | ffff     | Z     |  |

| MOVWF NOP         f NO Operation         Move W to f         1         00 0000 0000 0000 0000 0000 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MOVF                                                                                                                                             | f, d   | Move f                       | 1                     | 00  | 1000   | dfff   | ffff | Z        |       |  |

| RLF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MOVWF                                                                                                                                            | f      | Move W to f                  | 1                     | 00  | 0000   | lfff   | ffff |          |       |  |

| RRF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | NOP                                                                                                                                              | -      | No Operation                 | 1                     | 0.0 | 0000   | 0xx0   | 0000 |          |       |  |

| SUBWF   f, d   Subtract W from f   1   00   0010   dfff   ffff   C,DC,Z   1,2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RLF                                                                                                                                              | f, d   | Rotate Left f through Carry  | 1                     | 00  | 1101   | dfff   | ffff | С        | 1,2   |  |