Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x8b                                                                    |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc72at-04-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16C62B/72A

### 2.2.2.4 PIE1 REGISTER

This register contains the individual enable bits for the peripheral interrupts.

### REGISTER 2-4: PIE1 REGISTER (ADDRESS 8Ch)

#### R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 U-0 U-0 U-0 ADIE<sup>(1)</sup> SSPIE CCP1IE TMR2IE TMR1IE R = Readable bit W = Writable bit bit7 bit0 U = Unimplemented bit, read as '0' n = Value at POR reset Unimplemented: Read as '0' bit 7: ADIE<sup>(1)</sup>: A/D Converter Interrupt Enable bit bit 6: 1 = Enables the A/D interrupt 0 = Disables the A/D interrupt bit 5-4: Unimplemented: Read as '0' bit 3: SSPIE: Synchronous Serial Port Interrupt Enable bit 1 = Enables the SSP interrupt 0 = Disables the SSP interrupt CCP1IE: CCP1 Interrupt Enable bit bit 2: 1 = Enables the CCP1 interrupt 0 = Disables the CCP1 interrupt TMR2IE: TMR2 to PR2 Match Interrupt Enable bit bit 1: 1 = Enables the TMR2 to PR2 match interrupt 0 = Disables the TMR2 to PR2 match interrupt TMR1IE: TMR1 Overflow Interrupt Enable bit bit 0: 1 = Enables the TMR1 overflow interrupt 0 = Disables the TMR1 overflow interrupt Note 1: The PIC16C62B does not have an A/D module. This bit location is reserved on these devices. Always maintain this bit clear.

### Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

### 2.3 PCL and PCLATH

The program counter (PC) specifies the address of the instruction to fetch for execution. The PC is 13 bits wide. The low byte is called the PCL register and is readable and writable. The high byte is called the PCH register. This register contains the PC<12:8> bits and is not directly accessible. All updates to the PCH register go through the PCLATH register.

### 2.3.1 STACK

The stack allows any combination of up to 8 program calls and interrupts to occur. The stack contains the return address from this branch in program execution.

Mid-range devices have an 8 level deep hardware stack. The stack space is not part of either program or data space and the stack pointer is not accessible. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RET-FIE instruction execution. PCLATH is not modified when the stack is PUSHed or POPed.

After the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

### 2.4 Program Memory Paging

The CALL and GOTO instructions provide 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper bit of the address is provided by PCLATH<3>. The user must ensure that the page select bit is programmed to address the proper program memory page. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is popped from the stack. Therefore, manipulation of the PCLATH<3> bit is not required for the return instructions.

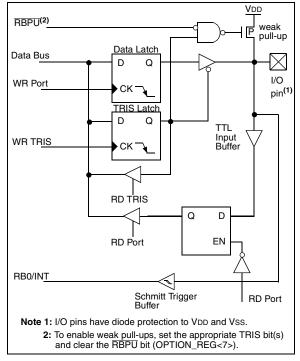

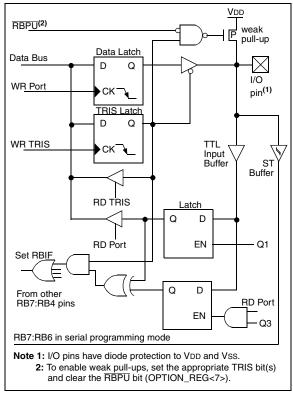

### 3.2 PORTB and the TRISB Register

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (=1) will make the corresponding PORTB pin an input, (i.e., put the corresponding output driver in a hi-impedance mode). Clearing a TRISB bit (=0) will make the corresponding PORTB pin an output, (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit  $\overline{\text{RBPU}}$  (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

### FIGURE 3-3: BLOCK DIAGRAM OF RB3:RB0 PINS

Four of PORTB's pins, RB7:RB4, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e. any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

RB0/INT is an external interupt pin and is configured using the INTEDG bit (OPTION\_REG<6>). RB0/INT is discussed in detail in Section 10.10.1.

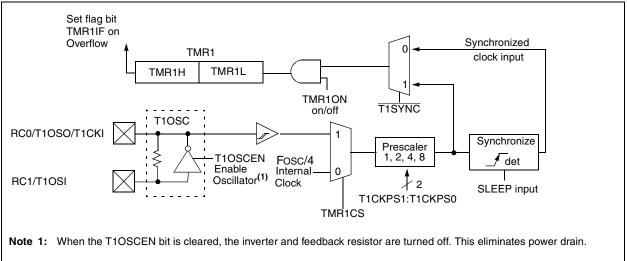

### FIGURE 5-1: TIMER1 BLOCK DIAGRAM

### 8.0 SYNCHRONOUS SERIAL PORT (SSP) MODULE

### 8.1 SSP Module Overview

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

For more information on SSP operation (including an I<sup>2</sup>C Overview), refer to the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023). Also, refer to Application Note AN578, *"Use of the SSP Module in the I<sup>2</sup>C Multi-Master Environment."*

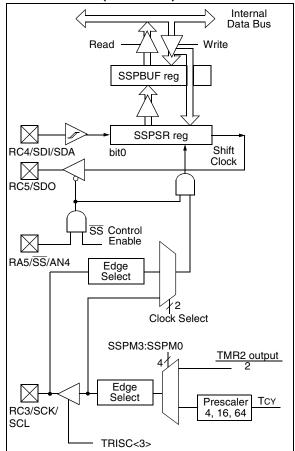

### 8.2 SPI Mode

This section contains register definitions and operational characteristics of the SPI module.

Additional information on SPI operation may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

8.2.1 OPERATION OF SSP MODULE IN SPI MODE

A block diagram of the SSP Module in SPI Mode is shown in Figure 8-1.

The SPI mode allows 8-bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, three pins are used:

- Serial Data Out (SDO)RC5/SDO

- Serial Data In (SDI)RC4/SDI/SDA

- Serial Clock (SCK)RC3/SCK/SCL

Additionally, a fourth pin may be used when in a slave mode of operation:

Slave Select (SS)RA5/SS/AN4

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- Master Operation (SCK is the clock output)

- Slave Mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Clock Edge (Output data on rising/falling edge of SCK)

- Clock Rate (master operation only)

- Slave Select Mode (Slave mode only)

To enable the serial port, SSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON reg-

ister, and then set bit SSPEN. This configures the SDI, SDO, SCK and  $\overline{SS}$  pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISC register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (master operation) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set (if used)

Note: When the SPI is in Slave Mode with  $\overline{SS}$  pin control enabled, (SSPCON<3:0> = 0100) the SPI module will reset if the  $\overline{SS}$  pin is set to VDD.

**Note:** If the SPI is used in Slave Mode with CKE = '1', then the  $\overline{SS}$  pin control must be enabled.

### FIGURE 8-1: SSP BLOCK DIAGRAM (SPI MODE)

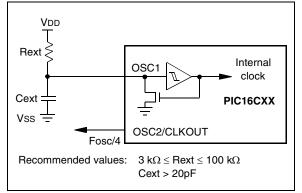

### 10.2.3 RC OSCILLATOR

For timing insensitive applications, the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 10-4 shows how the R/C combination is connected to the PIC16CXXX.

### FIGURE 10-4: RC OSCILLATOR MODE

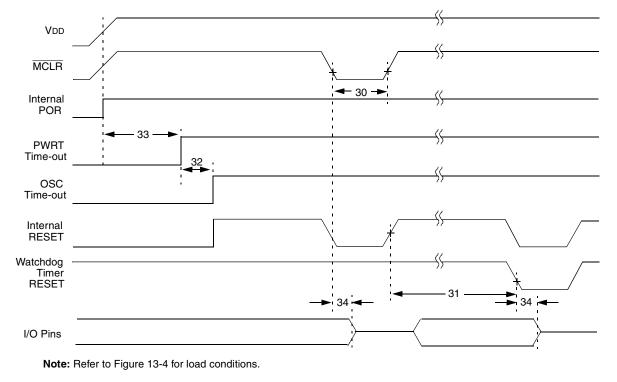

### 10.3 <u>Reset</u>

The PIC16CXXX differentiates between various kinds of reset:

- Power-on Reset (POR)

- MCLR reset during normal operation

- MCLR reset during SLEEP

- WDT Reset (during normal operation)

- WDT Wake-up (during SLEEP)

- Brown-out Reset (BOR)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged by any other reset. Most other registers are reset to a "reset state" on Power-on Reset (POR), on the  $\overline{\text{MCLR}}$  and WDT Reset, on  $\overline{\text{MCLR}}$  reset during SLEEP, and on Brown-out Reset (BOR). They are not affected by a WDT Wake-up from SLEEP, which is viewed as the resumption of normal operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared depending on the reset situation, as indicated in Table 10-4. These bits are used in software to determine the nature of the reset. See Table 10-6 for a full description of reset states of all registers.

A simplified block diagram of the on-chip reset circuit is shown in Figure 10-5.

The PIC devices have a  $\overline{\text{MCLR}}$  noise filter in the  $\overline{\text{MCLR}}$  reset path. The filter will ignore small pulses. However, a valid  $\overline{\text{MCLR}}$  pulse must meet the minimum pulse width (TmcL, Specification #30).

No internal reset source (WDT, BOR, POR) will drive the  $\overline{\text{MCLR}}$  pin low.

# PIC16C62B/72A

and test the sample code. In addition, PICDEM-17 supports down-loading of programs to and executing out of external FLASH memory on board. The PICDEM-17 is also usable with the MPLAB-ICE or PICMASTER emulator, and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

### 12.17 <u>SEEVAL Evaluation and Programming</u> <u>System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in trade-off analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

### 12.18 <u>KEELOQ Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

# PIC16C62B/72A

NOTES:

|                 |               |                                                                         | Standar                                                                   | d Opera | ating Co | ondition | s (unless otherwise stated)                                                                                  |  |  |  |

|-----------------|---------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------|---------|----------|----------|--------------------------------------------------------------------------------------------------------------|--|--|--|

| DC CHA          | RACTE         | RISTICS                                                                 | Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial |         |          |          |                                                                                                              |  |  |  |

|                 | 1             | 1                                                                       | 1                                                                         | 1       | 1        | -40°C    |                                                                                                              |  |  |  |

| Param<br>No.    | Sym           | Characteristic                                                          | Min                                                                       | Тур†    | Мах      | Units    | Conditions                                                                                                   |  |  |  |

| D001            | Vdd           | Supply Voltage                                                          | 2.5                                                                       | -       | 5.5      | V        | LP, XT, RC osc modes (DC - 4 MHz)                                                                            |  |  |  |

|                 |               |                                                                         | VBOR*                                                                     | -       | 5.5      | V        | BOR enabled (Note 7)                                                                                         |  |  |  |

| D002*           | Vdr           | RAM Data Retention<br>Voltage (Note 1)                                  | -                                                                         | 1.5     | -        | V        |                                                                                                              |  |  |  |

| D003            | VPOR          | <b>VDD Start Voltage</b> to<br>ensure internal<br>Power-on Reset signal | -                                                                         | Vss     | -        | V        | See section on Power-on Reset for details                                                                    |  |  |  |

| D004*<br>D004A* | SVDD          | <b>VDD Rise Rate</b> to<br>ensure internal<br>Power-on Reset signal     | 0.05<br>TBD                                                               | -<br>-  | -        | V/ms     | PWRT enabled (PWRTE bit clear)<br>PWRT disabled (PWRTE bit set)<br>See section on Power-on Reset for details |  |  |  |

| D005            | VBOR          | Brown-out Reset<br>voltage trip point                                   | 3.65                                                                      | -       | 4.35     | V        | BODEN bit set                                                                                                |  |  |  |

| D010            | IDD           | Supply Current<br>(Note 2, 5)                                           | -                                                                         | 2.0     | 3.8      | mA       | XT, RC osc modes<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                        |  |  |  |

| D010A           |               |                                                                         | -                                                                         | 22.5    | 48       | μA       | LP OSC MODE<br>FOSC = 32 kHz, VDD = 3.0V, WDT disabled                                                       |  |  |  |

| D020            | IPD           | Power-down Current                                                      | -                                                                         | 7.5     | 30       | μA       | VDD = 3.0V, WDT enabled, -40°C to +85°C                                                                      |  |  |  |

| D021            |               | (Note 3, 5)                                                             | -                                                                         | 0.9     | 5        | μA       | VDD = $3.0V$ , WDT disabled, $0^{\circ}C$ to $+70^{\circ}C$                                                  |  |  |  |

| D021A           |               |                                                                         | -                                                                         | 0.9     | 5        | μA       | VDD = 3.0V, WDT disabled, -40°C to +85°C                                                                     |  |  |  |

|                 |               | Module Differential<br>Current (Note 6)                                 |                                                                           |         |          |          |                                                                                                              |  |  |  |

| D022*           | $\Delta$ IWDT | Watchdog Timer                                                          | -                                                                         | 6.0     | 20       | μA       | WDTE BIT SET, VDD = 4.0V                                                                                     |  |  |  |

| D022A*          | $\Delta$ IBOR | Brown-out Reset                                                         | -                                                                         | TBD     | 200      | μA       | BODEN bit set, VDD = 5.0V                                                                                    |  |  |  |

#### 13.2 DC Characteristics: PIC16LC62B/72A-04 (Commercial, Industrial)

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD,

- $\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- 4: For RC osc mode, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: This is the voltage where the device enters the Brown-out Reset. When BOR is enabled, the device will perform a brown-out reset when VDD falls below VBOR.

## 13.3 DC Characteristics:

### cs: PIC16C62B/72A-04 (Commercial, Industrial, Extended) PIC16C62B/72A-20 (Commercial, Industrial, Extended) PIC16LC62B/72A-04 (Commercial, Industrial)

| DC CHA        | ARACTE | RISTICS                               | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C &\leq TA \leq +70^{\circ}C & \mbox{for commercial} \\ & -40^{\circ}C &\leq TA \leq +85^{\circ}C & \mbox{for industrial} \\ & -40^{\circ}C &\leq TA \leq +125^{\circ}C & \mbox{for extended} \\ \mbox{Operating voltage VDD range as described in DC spec Section 13.1} \\ & \mbox{and Section 13.2} \end{array}$ |      |                 |        |                                                                                                    |  |  |  |

|---------------|--------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------|--------|----------------------------------------------------------------------------------------------------|--|--|--|

| Param<br>No.  | Sym    | Characteristic                        | Min                                                                                                                                                                                                                                                                                                                                                                                                                                            | Тур† | Max             | Units  | Conditions                                                                                         |  |  |  |

|               |        | Input Low Voltage                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                 |        |                                                                                                    |  |  |  |

|               | VIL    | I/O ports                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                 |        |                                                                                                    |  |  |  |

| D030<br>D030A |        | with TTL buffer                       | Vss<br>Vss                                                                                                                                                                                                                                                                                                                                                                                                                                     | -    | 0.15Vdd<br>0.8V | V<br>V | For entire VDD range $4.5V \le VDD \le 5.5V$                                                       |  |  |  |

| D031          |        | with Schmitt Trigger buffer           | Vss                                                                                                                                                                                                                                                                                                                                                                                                                                            | -    | 0.2Vdd          | V      |                                                                                                    |  |  |  |

| D032          |        | MCLR, OSC1 (in RC mode)               | Vss                                                                                                                                                                                                                                                                                                                                                                                                                                            | -    | 0.2Vdd          | V      |                                                                                                    |  |  |  |

| D033          |        | OSC1 (in XT, HS and LP modes)         | Vss                                                                                                                                                                                                                                                                                                                                                                                                                                            | -    | 0.3Vdd          | V      | Note1                                                                                              |  |  |  |

|               |        | Input High Voltage                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                 |        |                                                                                                    |  |  |  |

|               | Vін    | I/O ports                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                | -    |                 |        |                                                                                                    |  |  |  |

| D040          |        | with TTL buffer                       | 2.0                                                                                                                                                                                                                                                                                                                                                                                                                                            | -    | Vdd             | V      | $4.5V \leq V\text{DD} \leq 5.5V$                                                                   |  |  |  |

| D040A         |        |                                       | 0.25Vd<br>D + 0.8V                                                                                                                                                                                                                                                                                                                                                                                                                             | -    | Vdd             | V      | For entire VDD range                                                                               |  |  |  |

| D041          |        | with Schmitt Trigger buffer           | 0.8Vdd                                                                                                                                                                                                                                                                                                                                                                                                                                         | -    | Vdd             | v      | For entire VDD range                                                                               |  |  |  |

| D042          |        | MCLR                                  | 0.8Vdd                                                                                                                                                                                                                                                                                                                                                                                                                                         | -    | Vdd             | V      |                                                                                                    |  |  |  |

| D042A         |        | OSC1 (XT, HS and LP modes)            | 0.7Vdd                                                                                                                                                                                                                                                                                                                                                                                                                                         | -    | Vdd             | V      | Note1                                                                                              |  |  |  |

| D043          |        | OSC1 (in RC mode)                     | 0.9Vdd                                                                                                                                                                                                                                                                                                                                                                                                                                         | -    | Vdd             | V      |                                                                                                    |  |  |  |

|               |        | Input Leakage Current<br>(Notes 2, 3) |                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                 |        |                                                                                                    |  |  |  |

| D060          | lı∟    | I/O ports                             | -                                                                                                                                                                                                                                                                                                                                                                                                                                              | -    | ±1              | μA     | $\label{eq:Vss} \begin{split} &Vss \leq V PIN \leq V DD, \\ &Pin \ at \ hi\ impedance \end{split}$ |  |  |  |

| D061          |        | MCLR, RA4/T0CKI                       | -                                                                                                                                                                                                                                                                                                                                                                                                                                              | -    | ±5              | μA     | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                           |  |  |  |

| D063          |        | OSC1                                  | -                                                                                                                                                                                                                                                                                                                                                                                                                                              | -    | ±5              | μA     | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc modes                                                |  |  |  |

| D070          | IPURB  | PORTB weak pull-up current            | 50                                                                                                                                                                                                                                                                                                                                                                                                                                             | 250  | 400             | μA     | VDD = 5V, VPIN = VSS                                                                               |  |  |  |

| D080          | Vol    | Output Low Voltage<br>I/O ports       | -                                                                                                                                                                                                                                                                                                                                                                                                                                              | -    | 0.6             | v      | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                                                        |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the device be driven with external clock in RC mode.

3: Negative current is defined as current sourced by the pin.

<sup>2:</sup> The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

| DC CHA       | ARACTE | RISTICS                                    | $\begin{array}{r llllllllllllllllllllllllllllllllllll$ |      |     |       |                                                                         |  |  |

|--------------|--------|--------------------------------------------|--------------------------------------------------------|------|-----|-------|-------------------------------------------------------------------------|--|--|

| Param<br>No. | Sym    | Characteristic                             | Min                                                    | Тур† | Max | Units | Conditions                                                              |  |  |

|              |        |                                            | -                                                      | -    | 0.6 | V     | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C                            |  |  |

| D083         |        | OSC2/CLKOUT<br>(RC osc mode)               | -                                                      | -    | 0.6 | V     | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                             |  |  |

|              |        |                                            | -                                                      | -    | 0.6 | V     | IOL = 1.2 mA, VDD = 4.5V,<br>-40°C to +125°C                            |  |  |

|              |        | Output High Voltage                        |                                                        |      |     |       |                                                                         |  |  |

| D090         | Vон    | I/O ports (Note 3)                         | VDD-0.7                                                | -    | -   | V     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +85°C                            |  |  |

|              |        |                                            | VDD-0.7                                                | -    | -   | V     | IOH = -2.5 mA, VDD = 4.5V,<br>-40°С to +125°С                           |  |  |

| D092         |        | OSC2/CLKOUT (RC osc<br>mode)               | Vdd-0.7                                                | -    | -   | V     | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                            |  |  |

|              |        |                                            | Vdd-0.7                                                | -    | -   | V     | IOH = -1.0 mA, VDD = 4.5V,<br>-40°C to +125°C                           |  |  |

| D150*        | Vod    | Open-Drain High Voltage                    | -                                                      | -    | 8.5 | V     | RA4 pin                                                                 |  |  |

|              |        | Capacitive Loading Specs<br>on Output Pins |                                                        |      |     |       |                                                                         |  |  |

| D100         | Cosc2  | OSC2 pin                                   | -                                                      | -    | 15  | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1. |  |  |

| D101         | Cio    | All I/O pins and OSC2 (in RC mode)         | -                                                      | -    | 50  | pF    |                                                                         |  |  |

| D102         | Cb     | SCL, SDA in I <sup>2</sup> C mode          | -                                                      | -    | 400 | pF    |                                                                         |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the device be driven with external clock in RC mode.

2: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

### 13.4 AC (Timing) Characteristics

### 13.4.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2              | ppS                                 | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|-----------------------|-------------------------------------|-----------|----------------------------------------|

| 2. TppS               |                                     | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                     |                                     |           |                                        |

| F                     | Frequency                           | Т         | Time                                   |

| Lowercas              | se letters (pp) and their meanings: |           |                                        |

| рр                    |                                     |           |                                        |

| сс                    | CCP1                                | OSC       | OSC1                                   |

| ck                    | CLKOUT                              | rd        | RD                                     |

| CS                    | CS                                  | rw        | RD or WR                               |

| di                    | SDI                                 | SC        | SCK                                    |

| do                    | SDO                                 | SS        | SS                                     |

| dt                    | Data in                             | t0        | TOCKI                                  |

| io                    | I/O port                            | t1        | T1CKI                                  |

| mc                    | MCLR                                | wr        | WR                                     |

| Uppercas              | se letters and their meanings:      |           |                                        |

| S                     |                                     |           |                                        |

| F                     | Fall                                | Р         | Period                                 |

| Н                     | High                                | R         | Rise                                   |

| I                     | Invalid (Hi-impedance)              | V         | Valid                                  |

| L                     | Low                                 | Z         | Hi-impedance                           |

| I <sup>2</sup> C only |                                     |           |                                        |

| AA                    | output access                       | High      | High                                   |

| BUF                   | Bus free                            | Low       | Low                                    |

| Tcc:st (I             | <sup>2</sup> C specifications only) |           |                                        |

| CC                    |                                     |           |                                        |

| HD                    | Hold                                | SU        | Setup                                  |

| ST                    |                                     |           |                                        |

| DAT                   | DATA input hold                     | STO       | STOP condition                         |

| STA                   | START condition                     |           |                                        |

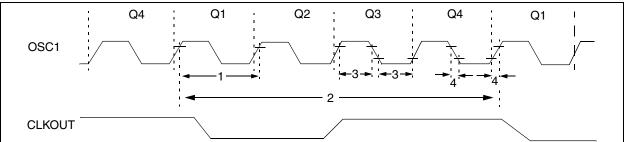

### 13.4.3 TIMING DIAGRAMS AND SPECIFICATIONS

### FIGURE 13-5: EXTERNAL CLOCK TIMING

| Param<br>No. | Sym   | Characteristic                  | Min | Тур† | Мах    | Units | Conditions          |

|--------------|-------|---------------------------------|-----|------|--------|-------|---------------------|

| 1A           | Fosc  | External CLKIN Frequency        | DC  |      | 4      | MHz   | RC and XT osc modes |

|              |       | (Note 1)                        | DC  | —    | 4      | MHz   | HS osc mode (-04)   |

|              |       |                                 | DC  | —    | 20     | MHz   | HS osc mode (-20)   |

|              |       |                                 | DC  | _    | 200    | kHz   | LP osc mode         |

|              |       | Oscillator Frequency            | DC  |      | 4      | MHz   | RC osc mode         |

|              |       | (Note 1)                        | 0.1 | —    | 4      | MHz   | XT osc mode         |

|              |       |                                 | 4   | —    | 20     | MHz   | HS osc mode         |

|              |       |                                 | 5   | _    | 200    | kHz   | LP osc mode         |

| 1            | Tosc  | External CLKIN Period           | 250 | —    | —      | ns    | RC and XT osc modes |

|              |       | (Note 1)                        | 250 | —    | —      | ns    | HS osc mode (-04)   |

|              |       |                                 | 50  | —    | —      | ns    | HS osc mode (-20)   |

|              |       |                                 | 5   | _    | —      | μS    | LP osc mode         |

|              |       | Oscillator Period               | 250 | —    | —      | ns    | RC osc mode         |

|              |       | (Note 1)                        | 250 | —    | 10,000 | ns    | XT osc mode         |

|              |       |                                 | 250 | —    | 250    | ns    | HS osc mode (-04)   |

|              |       |                                 | 50  | —    | 250    | ns    | HS osc mode (-20)   |

|              |       |                                 | 5   | _    | —      | μS    | LP osc mode         |

| 2            | Тсү   | Instruction Cycle Time (Note 1) | 200 | _    | DC     | ns    | Tcy = 4/Fosc        |

| 3*           | TosL, | External Clock in (OSC1) High   | 100 | —    | —      | ns    | XT oscillator       |

|              | TosH  | or Low Time                     | 2.5 | —    | —      | μS    | LP oscillator       |

|              |       |                                 | 15  | _    | —      | ns    | HS oscillator       |

| 4*           | TosR, | External Clock in (OSC1) Rise   | —   |      | 25     | ns    | XT oscillator       |

|              | TosF  | or Fall Time                    | —   | —    | 50     | ns    | LP oscillator       |

|              |       |                                 | _   | —    | 15     | ns    | HS oscillator       |

### TABLE 13-2: EXTERNAL CLOCK TIMING REQUIREMENTS

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin.

When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

| Param<br>No. | Sym      | Characteristic                          | Min                | Тур† | Мах | Units       | Conditions |        |

|--------------|----------|-----------------------------------------|--------------------|------|-----|-------------|------------|--------|

| 10*          | TosH2ckL | OSC1↑ to CLKOUT↓                        | —                  | 75   | 200 | ns          | Note 1     |        |

| 11*          | TosH2ckH | OSC1↑ to CLKOUT↑                        |                    | —    | 75  | 200         | ns         | Note 1 |

| 12*          | TckR     | CLKOUT rise time                        |                    | _    | 35  | 100         | ns         | Note 1 |

| 13*          | TckF     | CLKOUT fall time                        |                    | _    | 35  | 100         | ns         | Note 1 |

| 14*          | TckL2ioV | CLKOUT ↓ to Port out valid              |                    | —    |     | 0.5TCY + 20 | ns         | Note 1 |

| 15*          | TioV2ckH | Port in valid before CLKOU              | Tosc + 200         |      | _   | ns          | Note 1     |        |

| 16*          | TckH2iol | Port in hold after CLKOUT               | 0                  |      | _   | ns          | Note 1     |        |

| 17*          | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to Port of | —                  | 50   | 150 | ns          |            |        |

| 18*          | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to Port    | PIC16CXX           | 100  |     | _           | ns         |        |

| 18A*         |          | input invalid (I/O in hold<br>time)     | PIC16LCXX          | 200  |     |             | ns         |        |

| 19*          | TioV2osH | Port input valid to OSC1 <sup>↑</sup> ( | I/O in setup time) | 0    | _   | —           | ns         |        |

| 20*          | TioR     | Port output rise time                   | PIC16CXX           | —    | 10  | 40          | ns         |        |

| 20A*         |          |                                         | PIC16LCXX          | _    |     | 80          | ns         |        |

| 21*          | TioF     | Port output fall time                   | PIC16CXX           | _    | 10  | 40          | ns         |        |

| 21A*         | 1        |                                         | PIC16LCXX          | —    | —   | 80          | ns         |        |

| 22††*        | Tinp     | INT pin high or low time                | Тсү                | _    | —   | ns          |            |        |

| 23††*        | Trbp     | RB7:RB4 change INT high                 | or low time        | Тсү  | _   |             | ns         |        |

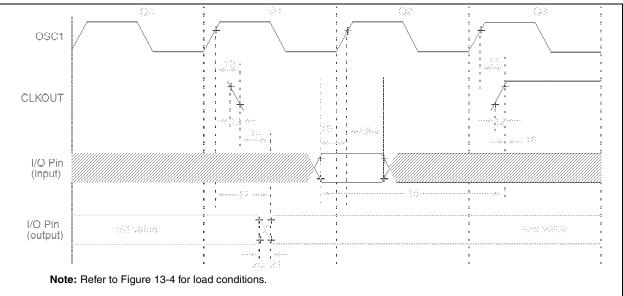

| TABLE 13-3: | CLKOUT AND I/O TIMING REQUIREMENTS |

|-------------|------------------------------------|

|             |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

tt These parameters are asynchronous events not related to any internal clock edge.

**Note 1:** Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

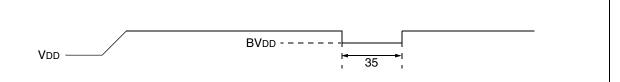

### FIGURE 13-8: BROWN-OUT RESET TIMING

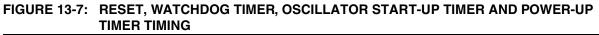

## TABLE 13-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                                   | Min | Тур†         | Max | Units | Conditions                                         |

|--------------|-------|--------------------------------------------------|-----|--------------|-----|-------|----------------------------------------------------|

| 30           | TmcL  | MCLR Pulse Width (low)                           | 2   |              | _   | μs    | VDD = 5V, -40°C to +125°C                          |

| 31*          | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler) | 7   | 18           | 33  | ms    | VDD = 5V, -40°C to +125°C                          |

| 32           | Tost  | Oscillator Start-up Timer Period                 |     | 1024<br>Tosc | —   | —     | Tosc = OSC1 period                                 |

| 33*          | Tpwrt | Power-up Timer Period                            | 28  | 72           | 132 | ms    | $VDD = 5V, -40^{\circ}C \text{ to } +125^{\circ}C$ |

| 34           | Tıoz  | I/O Hi-impedance from MCLR<br>Low or WDT reset   | _   | _            | 2.1 | μS    |                                                    |

| 35           | TBOR  | Brown-out Reset Pulse Width                      | 100 | _            | _   | μS    | $VDD \le BVDD$ (D005)                              |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

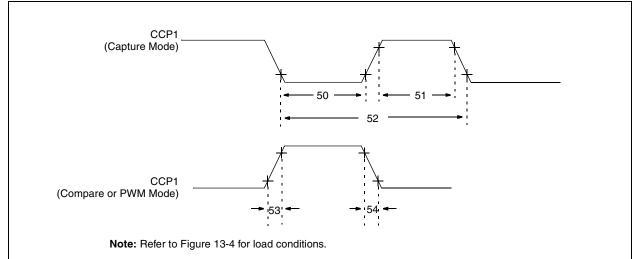

### FIGURE 13-10: CAPTURE/COMPARE/PWM TIMINGS

### TABLE 13-6: CAPTURE/COMPARE/PWM REQUIREMENTS

| Param<br>No. | Sym                              |                         | Characteristic |             | Min                   | Тур† | Max | Units | Conditions                         |

|--------------|----------------------------------|-------------------------|----------------|-------------|-----------------------|------|-----|-------|------------------------------------|

| 50*          | TccL CCP1 input low No Prescaler |                         |                | 0.5Tcy + 20 | —                     | —    | ns  |       |                                    |

|              |                                  | time                    | With Prescaler | PIC16CXX    | 10                    | _    | _   | ns    |                                    |

|              |                                  |                         |                | PIC16LCXX   | 20                    | _    | _   | ns    |                                    |

| 51*          | TccH                             | cH CCP1 input high time | No Prescaler   |             | 0.5TCY + 20           | _    | _   | ns    |                                    |

|              |                                  |                         | With Prescaler | PIC16CXX    | 10                    | -    | —   | ns    |                                    |

|              |                                  |                         |                | PIC16LCXX   | 20                    | _    | _   | ns    |                                    |

| 52*          | TccP                             | CCP1 input perior       | d              |             | <u>3Tcy + 40</u><br>N | -    | —   | ns    | N = prescale<br>value (1,4, or 16) |

| 53*          | TccR                             | CCP1 output rise time   |                | PIC16CXX    | —                     | 10   | 25  | ns    |                                    |

|              |                                  |                         |                | PIC16LCXX   | —                     | 25   | 45  | ns    |                                    |

| 54*          | TccF                             | CCP1 output fall time   |                | PIC16CXX    | —                     | 10   | 25  | ns    |                                    |

|              |                                  |                         |                | PIC16LCXX   | —                     | 25   | 45  | ns    |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

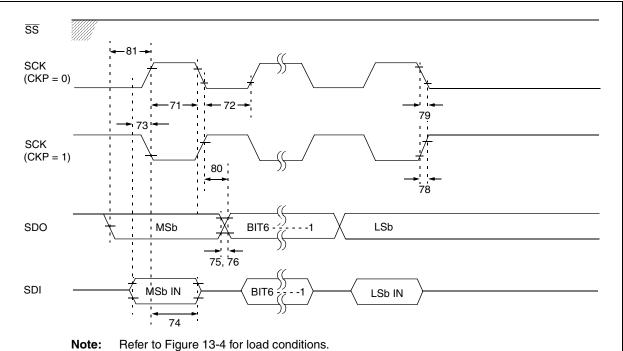

### FIGURE 13-12: EXAMPLE SPI MASTER MODE TIMING (CKE = 1)

### TABLE 13-8: EXAMPLE SPI MODE REQUIREMENTS (MASTER MODE, CKE = 1)

| Param.<br>No. | Symbol                | Characteris                               | tic         | Min          | Тур† | Мах | Units  | Conditions |

|---------------|-----------------------|-------------------------------------------|-------------|--------------|------|-----|--------|------------|

| 71            | TscH                  | SCK input high time                       | Continuous  | 1.25Tcy + 30 | -    |     | ns     |            |

| 71A           |                       | (slave mode)                              | Single Byte | 40           | —    |     | ns     | Note 1     |

| 72            | TscL                  | SCK input low time                        | Continuous  | 1.25Tcy + 30 | —    |     | ns     |            |

| 72A           |                       | (slave mode)                              | Single Byte | 40           | —    |     | ns     | Note 1     |

| 73            | TdiV2scH,<br>TdiV2scL | Setup time of SDI data in edge            | 100         | —            | _    | ns  |        |            |

| 73A           | Тв2в                  | Last clock edge of Byte1<br>edge of Byte2 | 1.5Tcy + 40 | _            | _    | ns  | Note 1 |            |

| 74            | TscH2diL,<br>TscL2diL | Hold time of SDI data inp                 | 100         | —            | _    | ns  |        |            |

| 75            | TdoR                  | SDO data output rise                      | PIC16CXX    |              | 10   | 25  | ns     |            |

|               |                       | time                                      | PIC16LCXX   |              | 20   | 45  | ns     |            |

| 76            | TdoF                  | SDO data output fall time                 |             | —            | 10   | 25  | ns     |            |

| 78            | TscR                  | SCK output rise time                      | PIC16CXX    | —            | 10   | 25  | ns     |            |

|               |                       | (master mode)                             | PIC16LCXX   |              | 20   | 45  | ns     |            |

| 79            | TscF                  | SCK output fall time (mas                 | ster mode)  |              | 10   | 25  | ns     |            |

| 80            | TscH2doV,             | SDO data output valid                     | PIC16CXX    | —            | —    | 50  | ns     |            |

|               | TscL2doV              | after SCK edge                            | PIC16LCXX   |              | —    | 100 | ns     |            |

| 81            | TdoV2scH,<br>TdoV2scL | SDO data output setup to                  | SCK edge    | Тсү          |      |     | ns     |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Specification 73A is only required if specifications 71A and 72A are used.

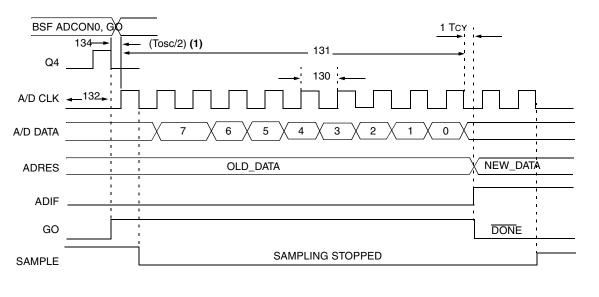

### FIGURE 13-17: A/D CONVERSION TIMING

**Note 1:** If the A/D clock source is selected as RC, a time of TCY is added before the A/D clock starts. This allows the SLEEP instruction to be executed.

| Param | Sym  | Characteristic                      |                         | Min    | Typ†   | Max | Unit | Conditions                                                                                                                                                                                                                         |

|-------|------|-------------------------------------|-------------------------|--------|--------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.   |      |                                     |                         |        |        |     | S    |                                                                                                                                                                                                                                    |

| 130   | TAD  | A/D clock period                    | PIC16CXX                | 1.6    |        |     | μs   | Tosc based, VREF $\geq 3.0V$                                                                                                                                                                                                       |

|       |      |                                     | PIC16LCXX               | 2.0    |        | -   | μs   | TOSC based, VREF full range                                                                                                                                                                                                        |

|       |      |                                     | PIC16CXX                | 2.0    | 4.0    | 6.0 | μS   | A/D RC Mode                                                                                                                                                                                                                        |

|       |      |                                     | PIC16LCXX               | 3.0    | 6.0    | 9.0 | μS   | A/D RC Mode                                                                                                                                                                                                                        |

| 131   | TCNV | Conversion time (not time) (Note 1) | 11                      |        | 11     | Tad |      |                                                                                                                                                                                                                                    |

| 132   | TACQ | Acquisition time                    |                         | Note 2 | 20     |     | μS   |                                                                                                                                                                                                                                    |

|       |      |                                     |                         | 5*     | _      | _   | μs   | The minimum time is the<br>amplifier settling time. This<br>may be used if the "new" input<br>voltage has not changed by<br>more than 1 LSb (i.e., 20.0 mV<br>@ 5.12V) from the last sam-<br>pled voltage (as stated on<br>CHOLD). |

| 134   | TGO  | Q4 to A/D clo                       | ck start                |        | Tosc/2 |     |      | If the A/D clock source is<br>selected as RC, a time of TCY<br>is added before the A/D clock<br>starts. This allows the SLEEP<br>instruction to be executed.                                                                       |

| 135   | Tswc | Switching from conve<br>time        | $rt \rightarrow sample$ | 1.5    |        |     | Tad  |                                                                                                                                                                                                                                    |

### TABLE 13-14: A/D CONVERSION REQUIREMENTS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** ADRES register may be read on the following TCY cycle.

2: See Section 9.1 for min conditions.

### **15.0 PACKAGING INFORMATION**

### 15.1 Package Marking Information

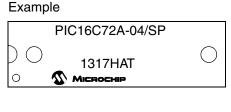

28-Lead SOIC

### Example

## Example PIC16C62B-20/SO

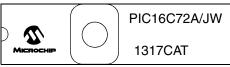

| 28-Lead SSOP                            | Example                |  |

|-----------------------------------------|------------------------|--|

| xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx | PIC16C62B<br>20I/SS025 |  |

|                                         | ○                      |  |

| ,                                                                                |                               |                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|----------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| be carried over to the next line thus limiting the number of available character | <br>XXX<br>AA<br>BB<br>C<br>D | <ul> <li>Customer specific information*</li> <li>Year code (last 2 digits of calendar year)</li> <li>Week code (week of January 1 is week '01')</li> <li>Facility code of the plant at which wafer is manufactured</li> <li>O = Outside Vendor</li> <li>C = 5" Line</li> <li>S = 6" Line</li> <li>H = 8" Line</li> <li>Mask revision number</li> <li>Assembly code of the plant or country of origin in which</li> </ul> |  |

|                                                                                  | be carrie                     | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line thus limiting the number of available characters<br>for customer specific information.                                                                                                                                                                                                             |  |

Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask rev#, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

© 1998-2013 Microchip Technology Inc.