Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XF

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | I²C, SPI                                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 22                                                                           |

| Program Memory Size        | 3.5KB (2K x 14)                                                              |

| Program Memory Type        | ОТР                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 128 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x8b                                                                     |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

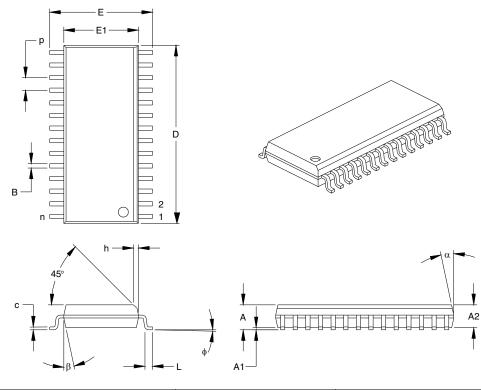

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 28-QFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc72at-04i-ml |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

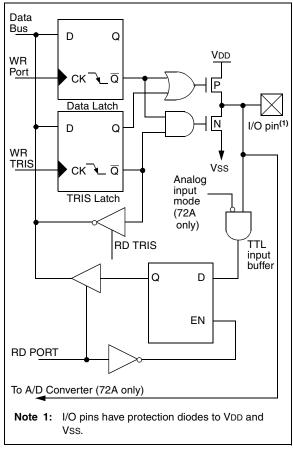

#### 3.0 I/O PORTS

Some I/O port pins are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

#### 3.1 PORTA and the TRISA Register

PORTA is a 6-bit wide bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (=1) will make the corresponding PORTA pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISA bit (=0) will make the corresponding PORTA pin an output, (i.e., put the contents of the output latch on the selected pin).

The PORTA register reads the state of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

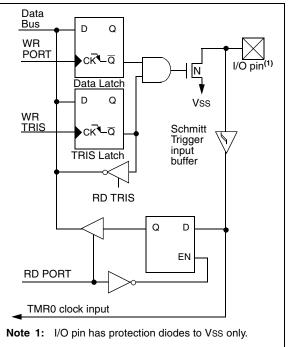

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers.

Pin RA5 is multiplexed with the SSP to become the RA5/SS pin.

On the PIC16C72A device, other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

| Note: | On a Power-on Reset, pins with analog           |

|-------|-------------------------------------------------|

|       | functions are configured as analog inputs       |

|       | with digital input buffers disabled . A digital |

|       | read of these pins will return '0'.             |

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### FIGURE 3-1: BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

#### FIGURE 3-2: BLOCK DIAGRAM OF RA4/T0CKI PIN

© 1998-2013 Microchip Technology Inc.

#### TABLE 3-5 PORTC FUNCTIONS

| Name            | Bit# | Buffer<br>Type | Function                                                                    | TRISC<br>Override |

|-----------------|------|----------------|-----------------------------------------------------------------------------|-------------------|

| RC0/T1OSO/T1CKI | bit0 | ST             | Input/output port pin or Timer1 oscillator output/Timer1 clock input        | Yes               |

| RC1/T1OSI       | bit1 | ST             | Input/output port pin or Timer1 oscillator input                            | Yes               |

| RC2/CCP1        | bit2 | ST             | Input/output port pin or Capture1 input/Compare1 output/PWM1 output         | No                |

| RC3/SCK/SCL     | bit3 | ST             | RC3 can also be the synchronous serial clock for both SPI and $I^2C$ modes. | No                |

| RC4/SDI/SDA     | bit4 | ST             | RC4 can also be the SPI Data In (SPI mode) or data $I/O$ ( $I^2C$ mode).    | No                |

| RC5/SDO         | bit5 | ST             | Input/output port pin or Synchronous Serial Port data output                | No                |

| RC6             | bit6 | ST             | Input/output port pin                                                       | No                |

| RC7             | bit7 | ST             | Input/output port pin                                                       | No                |

Legend: ST = Schmitt Trigger input

#### TABLE 3-6SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7   | Bit 6       | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|---------|-------------|------------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 07h     | PORTC | RC7     | RC6         | RC5        | RC4   | RC3   | RC2   | RC1   | RC0   | xxxx xxxx                | uuuu uuuu                 |

| 87h     | TRISC | PORTC I | Data Direct | ion Regist | er    |       |       |       |       | 1111 1111                | 1111 1111                 |

Legend: x = unknown, u = unchanged.

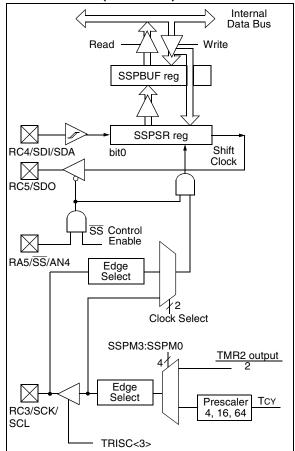

#### 8.0 SYNCHRONOUS SERIAL PORT (SSP) MODULE

#### 8.1 SSP Module Overview

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

For more information on SSP operation (including an I<sup>2</sup>C Overview), refer to the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023). Also, refer to Application Note AN578, *"Use of the SSP Module in the I<sup>2</sup>C Multi-Master Environment."*

#### 8.2 SPI Mode

This section contains register definitions and operational characteristics of the SPI module.

Additional information on SPI operation may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

8.2.1 OPERATION OF SSP MODULE IN SPI MODE

A block diagram of the SSP Module in SPI Mode is shown in Figure 8-1.

The SPI mode allows 8-bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, three pins are used:

- Serial Data Out (SDO)RC5/SDO

- Serial Data In (SDI)RC4/SDI/SDA

- Serial Clock (SCK)RC3/SCK/SCL

Additionally, a fourth pin may be used when in a slave mode of operation:

Slave Select (SS)RA5/SS/AN4

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- Master Operation (SCK is the clock output)

- Slave Mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Clock Edge (Output data on rising/falling edge of SCK)

- Clock Rate (master operation only)

- Slave Select Mode (Slave mode only)

To enable the serial port, SSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON reg-

ister, and then set bit SSPEN. This configures the SDI, SDO, SCK and  $\overline{SS}$  pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISC register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (master operation) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set (if used)

Note: When the SPI is in Slave Mode with  $\overline{SS}$  pin control enabled, (SSPCON<3:0> = 0100) the SPI module will reset if the  $\overline{SS}$  pin is set to VDD.

**Note:** If the SPI is used in Slave Mode with CKE = '1', then the  $\overline{SS}$  pin control must be enabled.

#### FIGURE 8-1: SSP BLOCK DIAGRAM (SPI MODE)

| TABLE 8-1 | REGISTERS ASSOCIATED WITH SPI OPERATION |

|-----------|-----------------------------------------|

|           |                                         |

| Address | Name    | Bit 7      | Bit 6                                                    | Bit 5   | Bit 4     | Bit 3      | Bit 2  | Bit 1  | Bit 0  | Value<br>POR<br>BOF | l,   | Valu<br>all o<br>res |      |

|---------|---------|------------|----------------------------------------------------------|---------|-----------|------------|--------|--------|--------|---------------------|------|----------------------|------|

| 0Bh,8Bh | INTCON  | GIE        | PEIE                                                     | TOIE    | INTE      | RBIE       | T0IF   | INTF   | RBIF   | 0000 0              | 00x  | 0000                 | 000u |

| 0Ch     | PIR1    | —          | ADIF                                                     | —       | _         | SSPIF      | CCP1IF | TMR2IF | TMR1IF | -00                 | 000  | - 0                  | 0000 |

| 8Ch     | PIE1    | —          | ADIE                                                     |         | —         | SSPIE      | CCP1IE | TMR2IE | TMR1IE | -00                 | 000  | - 0                  | 0000 |

| 13h     | SSPBUF  | Synchronou | Synchronous Serial Port Receive Buffer/Transmit Register |         |           |            |        |        | xxxx x | xxx                 | uuuu | uuuu                 |      |

| 14h     | SSPCON  | WCOL       | SSPOV                                                    | SSPEN   | CKP       | SSPM3      | SSPM2  | SSPM1  | SSPM0  | 0000 0              | 000  | 0000                 | 0000 |

| 94h     | SSPSTAT | SMP        | CKE                                                      | D/Ā     | Р         | S          | R/W    | UA     | BF     | 0000 0              | 000  | 0000                 | 0000 |

| 85h     | TRISA   | _          |                                                          | PORTA D | Data Dire | ction Regi | ster   |        |        | 11 1                | 111  | 11                   | 1111 |

| 87h     | TRISC   | PORTC Data | Data Direction Register 1111 1111                        |         |           |            |        | 111    | 1111   | 1111                |      |                      |      |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the SSP in SPI mode.

#### 8.3.1.2 RECEPTION

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no acknowledge ( $\overline{ACK}$ ) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set or bit SSPOV (SSPCON<6>) is set.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

#### FIGURE 8-3: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

| Receiving Address         R/W           SDA         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - </th <th>=0Receiving Data<br/>_ACK_D7XD6XD5XD4XD3XD2XD1XE<br/>9+_/1\_/2\_/3\_/4\_/5\_/6\_/7\_/8</th> <th></th> <th></th> | =0Receiving Data<br>_ACK_D7XD6XD5XD4XD3XD2XD1XE<br>9+_/1\_/2\_/3\_/4\_/5\_/6\_/7\_/8 |                                       |                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------|

| SSPI <u>F (PIR1&lt;3&gt;)</u><br>BF ( <u>SSPSTAT&lt;0&gt;)</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>Cleared in software</li> <li>SSPBUF register is read</li> </ul>             |                                       | Bus Master<br>terminates<br>transfer |

| SSP <u>OV (SSPCON&lt;6&gt;)</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Bit SSPOV is set b                                                                   | ecause the SSPBUF register is still f |                                      |

NOTES:

#### 10.13 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D and disable external clocks. Pull all I/O pins that are hi-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC, parameter D042).

#### 10.13.1 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- 1. External reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change, or some Peripheral Interrupts.

External  $\overline{\text{MCLR}}$  Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from SLEEP:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. CCP capture mode interrupt.

- Special event trigger (Timer1 in asynchronous mode using an external clock. CCP1 is in compare mode).

- 4. SSP (Start/Stop) bit detect interrupt.

- 5. SSP transmit or receive in slave mode (SPI/I<sup>2</sup>C).

- 6. USART RX or TX (synchronous slave mode).

Other peripherals cannot generate interrupts since during SLEEP, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is

regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device resumes execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, a NOP should follow the SLEEP instruction.

#### 10.13.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

<sup>© 1998-2013</sup> Microchip Technology Inc.

#### FIGURE 10-10: WAKE-UP FROM SLEEP THROUGH INTERRUPT

| ; a1   a2   a3   a4 ; (<br>osc1 /~//        | 21   Q2   Q3   Q4 ;<br>\/ |                       | 01 02 03 04  | a1 a2 a3 a4                   | a1 a2 a3 a4      | 01 02 03 04 |

|---------------------------------------------|---------------------------|-----------------------|--------------|-------------------------------|------------------|-------------|

| CLKOUT(4)                                   |                           | Tost(2)               | /            | /                             | //               |             |

| INTF flag<br>(INTCON<1>)                    |                           |                       |              | Interrupt Latency<br>(Note 2) | -<br> <br> <br>  |             |

| GIE bit<br>(INTCON<7>)                      | <br> <br> +<br> <br>      | Processor in<br>SLEEP |              |                               | 1<br>1<br>1<br>1 |             |

| INSTRUCTION FLOW                            | 1                         |                       |              |                               |                  | · · · ·     |

| PC <u>X PC X</u>                            | PC+1                      | PC+2                  | PC+2         | X PC + 2                      | X 0004h          | X 0005h     |

| Instruction {<br>fetched { Inst(PC) = SLEEP | Inst(PC + 1)              | ,<br>,<br>,           | Inst(PC + 2) |                               | Inst(0004h)      | Inst(0005h) |

| Instruction<br>executed Inst(PC - 1)        | SLEEP                     | 1<br>1<br>1           | Inst(PC + 1) | Dummy cycle                   | Dummy cycle      | Inst(0004h) |

**Note 1:** XT, HS or LP oscillator mode assumed.

**2:** TOST = 1024TOSC (drawing not to scale) This delay will not be there for RC osc mode.

3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

#### 10.14 Program Verification/Code Protection

If the code protection bits have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip does not recommend code pro- |

|-------|----------------------------------------|

|       | tecting windowed devices.              |

#### 10.15 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution, but are readable and writable during program/verify. It is recommended that only the 4 least significant bits of the ID location are used.

For ROM devices, these values are submitted along with the ROM code.

#### 10.16 In-Circuit Serial Programming™

PIC16CXXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three more lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

For complete details of serial programming, please refer to the In-Circuit Serial Programming (ICSP™) Guide, DS30277.

## 11.1 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                       |

|------------------|-------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                |

| Operands:        | $0 \leq k \leq 255$                                                                                                     |

| Operation:       | $(W) + k \to (W)$                                                                                                       |

| Status Affected: | C, DC, Z                                                                                                                |

| Description:     | The contents of the W register are<br>added to the eight bit literal 'k' and the<br>result is placed in the W register. |

| ANDWF            | AND W with f                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                             |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                   |

| Status Affected: | Z                                                                                                                                                           |

| Description:     | AND the W register with register 'f'. If<br>'d' is 0, the result is stored in the W<br>register. If 'd' is 1, the result is stored<br>back in register 'f'. |

| ADDWF            | Add W and f                                                                                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                             |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                       |

| Status Affected: | C, DC, Z                                                                                                                                                                    |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result is<br>stored in the W register. If 'd' is 1, the<br>result is stored back in register 'f'. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BCF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ANDLW            | AND Literal with W                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                            |

| Operands:        | $0 \le k \le 255$                                                                                                   |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                     |

| Status Affected: | Z                                                                                                                   |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal 'k'.<br>The result is placed in the W register. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

### 12.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB™ IDE Software

- Assemblers/Compilers/Linkers

- MPASM Assembler

- MPLAB-C17 and MPLAB-C18 C Compilers

- MPLINK/MPLIB Linker/Librarian

- Simulators

- MPLAB-SIM Software Simulator

- Emulators

- MPLAB-ICE Real-Time In-Circuit Emulator

- PICMASTER<sup>®</sup>/PICMASTER-CE In-Circuit Emulator

- ICEPIC™

- In-Circuit Debugger

- MPLAB-ICD for PIC16F877

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- Low-Cost Demonstration Boards

- SIMICE

- PICDEM-1

- PICDEM-2

- PICDEM-3

- PICDEM-17

- SEEVAL®

- KEELOQ<sup>®</sup>

#### 12.1 <u>MPLAB Integrated Development</u> <u>Environment Software</u>

- The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a Windows<sup>®</sup>-based application which contains:

- Multiple functionality

- editor

- simulator

- programmer (sold separately)

- emulator (sold separately)

- A full featured editor

- A project manager

- · Customizable tool bar and key mapping

- · A status bar

- On-line help

MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- object code

The ability to use MPLAB with Microchip's simulator, MPLAB-SIM, allows a consistent platform and the ability to easily switch from the cost-effective simulator to the full featured emulator with minimal retraining.

#### 12.2 MPASM Assembler

MPASM is a full featured universal macro assembler for all PIC MCUs. It can produce absolute code directly in the form of HEX files for device programmers, or it can generate relocatable objects for MPLINK.

MPASM has a command line interface and a Windows shell and can be used as a standalone application on a Windows 3.x or greater system. MPASM generates relocatable object files, Intel standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file which contains source lines and generated machine code, and a COD file for MPLAB debugging.

MPASM features include:

- MPASM and MPLINK are integrated into MPLAB projects.

- MPASM allows user defined macros to be created for streamlined assembly.

- MPASM allows conditional assembly for multi purpose source files.

- MPASM directives allow complete control over the assembly process.

#### 12.3 <u>MPLAB-C17 and MPLAB-C18</u> <u>C Compilers</u>

The MPLAB-C17 and MPLAB-C18 Code Development Systems are complete ANSI 'C' compilers and integrated development environments for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

#### 12.4 MPLINK/MPLIB Linker/Librarian

MPLINK is a relocatable linker for MPASM and MPLAB-C17 and MPLAB-C18. It can link relocatable objects from assembly or C source files along with precompiled libraries using directives from a linker script.

# PIC16C62B/72A

MPLIB is a librarian for pre-compiled code to be used with MPLINK. When a routine from a library is called from another source file, only the modules that contains that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications. MPLIB manages the creation and modification of library files.

MPLINK features include:

- MPLINK works with MPASM and MPLAB-C17 and MPLAB-C18.

- MPLINK allows all memory areas to be defined as sections to provide link-time flexibility.

MPLIB features include:

- MPLIB makes linking easier because single libraries can be included instead of many smaller files.

- MPLIB helps keep code maintainable by grouping related modules together.

- MPLIB commands allow libraries to be created and modules to be added, listed, replaced, deleted, or extracted.

#### 12.5 MPLAB-SIM Software Simulator

The MPLAB-SIM Software Simulator allows code development in a PC host environment by simulating the PIC series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file or user-defined key press to any of the pins. The execution can be performed in single step, execute until break, or trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C17 and MPLAB-C18 and MPASM. The Software Simulator offers the flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

#### 12.6 <u>MPLAB-ICE High Performance</u> <u>Universal In-Circuit Emulator with</u> <u>MPLAB IDE</u>

The MPLAB-ICE Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers (MCUs). Software control of MPLAB-ICE is provided by the MPLAB Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB-ICE allows expansion to support new PIC microcontrollers.

The MPLAB-ICE Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows 3.x/95/98 environment were chosen to best make these features available to you, the end user.

MPLAB-ICE 2000 is a full-featured emulator system with enhanced trace, trigger, and data monitoring features. Both systems use the same processor modules and will operate across the full operating speed range of the PIC MCU.

#### 12.7 PICMASTER/PICMASTER CE

The PICMASTER system from Microchip Technology is a full-featured, professional quality emulator system. This flexible in-circuit emulator provides a high-quality, universal platform for emulating Microchip 8-bit PIC microcontrollers (MCUs). PICMASTER systems are sold worldwide, with a CE compliant model available for European Union (EU) countries.

#### 12.8 <u>ICEPIC</u>

ICEPIC is a low-cost in-circuit emulation solution for the Microchip Technology PIC16C5X, PIC16C6X, PIC16C7X, and PIC16CXXX families of 8-bit one-timeprogrammable (OTP) microcontrollers. The modular system can support different subsets of PIC16C5X or PIC16CXXX products through the use of interchangeable personality modules or daughter boards. The emulator is capable of emulating without target application circuitry being present.

#### 12.9 MPLAB-ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB-ICD, is a powerful, low-cost run-time development tool. This tool is based on the flash PIC16F877 and can be used to develop for this and other PIC microcontrollers from the PIC16CXXX family. MPLAB-ICD utilizes the In-Circuit Debugging capability built into the PIC16F87X. This feature, along with Microchip's In-Circuit Serial Programming protocol, offers cost-effective in-circuit flash programming and debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time. The MPLAB-ICD is also a programmer for the flash PIC16F87X family.

#### 12.10 PRO MATE II Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode. PRO MATE II is CE compliant.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In

#### 13.1 DC Characteristics: PIC16C62B/72A-04 (Commercial, Industrial, Extended) PIC16C62B/72A-20 (Commercial, Industrial, Extended)

|              |               |                                                                         |          |         |         |                                                         | ns (unless otherwise stated)                                   |  |  |

|--------------|---------------|-------------------------------------------------------------------------|----------|---------|---------|---------------------------------------------------------|----------------------------------------------------------------|--|--|

| DC CHA       |               |                                                                         | Operatir | ng temp | erature | e $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial |                                                                |  |  |

| DC CHA       | NACIE         | 131103                                                                  |          |         |         | -40°C                                                   | $\leq$ TA $\leq$ +85°C for industrial                          |  |  |

|              |               |                                                                         |          |         |         | -40°C                                                   | $\leq$ TA $\leq$ +125°C for extended                           |  |  |

| Param<br>No. | Sym           | Characteristic                                                          | Min      | Тур†    | Max     | Units                                                   | Conditions                                                     |  |  |

| -            |               |                                                                         |          |         |         |                                                         |                                                                |  |  |

| D001         | Vdd           | Supply Voltage                                                          | 4.0      | -       | 5.5     | V                                                       | XT, RC and LP osc mode                                         |  |  |

| D001A        |               |                                                                         | 4.5      | -       | 5.5     | V                                                       | HS osc mode                                                    |  |  |

|              |               |                                                                         | VBOR*    | -       | 5.5     | V                                                       | BOR enabled (Note 7)                                           |  |  |

| D002*        | Vdr           | RAM Data Retention<br>Voltage (Note 1)                                  | -        | 1.5     | -       | V                                                       |                                                                |  |  |

| D003         | VPOR          | <b>VDD Start Voltage</b> to<br>ensure internal<br>Power-on Reset signal | -        | Vss     | -       | V                                                       | See section on Power-on Reset for details                      |  |  |

| D004*        | SVDD          | VDD Rise Rate to                                                        | 0.05     | -       | -       | V/ms                                                    |                                                                |  |  |

| D004A*       |               | ensure internal                                                         | TBD      | -       | -       |                                                         | PWRT disabled (PWRTE bit set)                                  |  |  |

|              |               | Power-on Reset signal                                                   |          |         |         |                                                         | See section on Power-on Reset for details                      |  |  |

| D005         | VBOR          | Brown-out Reset<br>voltage trip point                                   | 3.65     | -       | 4.35    | V                                                       | BODEN bit set                                                  |  |  |

| D010         | IDD           | Supply Current                                                          | -        | 2.7     | 5       | mA                                                      | XT, RC osc modes                                               |  |  |

|              |               | (Note 2, 5)                                                             |          |         |         |                                                         | Fosc = 4 MHz, VDD = 5.5V (Note 4)                              |  |  |

| D013         |               |                                                                         | -        | 10      | 20      | mA                                                      | HS osc mode                                                    |  |  |

| 2010         |               |                                                                         |          |         | 20      |                                                         | Fosc = 20  MHz,  VDD = 5.5  V                                  |  |  |

| D020         | IPD           | Power-down Current                                                      | -        | 10.5    | 42      | μA                                                      | VDD = 4.0V, WDT enabled,-40°C to +85°C                         |  |  |

|              |               | (Note 3, 5)                                                             | -        | 1.5     | 16      | μ <b>Α</b>                                              | VDD = $4.0V$ , WDT disabled, 0°C to $+70°C$                    |  |  |

| D021         |               |                                                                         | -        | 1.5     | 19      | μ <b>Α</b>                                              | VDD = 4.0V, WDT disabled, -40°C to +85°C                       |  |  |

| D021B        |               |                                                                         | -        | 2.5     | 19      | μΑ                                                      | VDD = $4.0V$ , WDT disabled, $-40^{\circ}C$ to $+125^{\circ}C$ |  |  |

|              |               | Module Differential                                                     |          |         |         |                                                         |                                                                |  |  |

|              |               | Current (Note 6)                                                        |          |         |         |                                                         |                                                                |  |  |

| D022*        | $\Delta IWDT$ | Watchdog Timer                                                          | -        | 6.0     | 20      | μA                                                      | WDTE BIT SET, VDD = 4.0V                                       |  |  |

| D022A*       | $\Delta IBOR$ | Brown-out Reset                                                         | -        | TBD     | 200     | μA                                                      | BODEN bit set, VDD = 5.0V                                      |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD,

$\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc mode, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: This is the voltage where the device enters the Brown-out Reset. When BOR is enabled, the device will perform a brown-out reset when VDD falls below VBOR.

|                 |               |                                                                         | Standar                                                                     | d Opera | ating Co | ondition | s (unless otherwise stated)                                                                                  |  |  |

|-----------------|---------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------|----------|----------|--------------------------------------------------------------------------------------------------------------|--|--|

| DC CHA          | RACTE         | RISTICS                                                                 | Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial |         |          |          |                                                                                                              |  |  |

|                 | 1             | 1                                                                       | $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial                     |         |          |          |                                                                                                              |  |  |

| Param<br>No.    | Sym           | Characteristic                                                          | Min                                                                         | Тур†    | Мах      | Units    | Conditions                                                                                                   |  |  |

| D001            | Vdd           | Supply Voltage                                                          | 2.5                                                                         | -       | 5.5      | V        | LP, XT, RC osc modes (DC - 4 MHz)                                                                            |  |  |

|                 |               |                                                                         | VBOR*                                                                       | -       | 5.5      | V        | BOR enabled (Note 7)                                                                                         |  |  |

| D002*           | Vdr           | RAM Data Retention<br>Voltage (Note 1)                                  | -                                                                           | 1.5     | -        | V        |                                                                                                              |  |  |

| D003            | VPOR          | <b>VDD Start Voltage</b> to<br>ensure internal<br>Power-on Reset signal | -                                                                           | Vss     | -        | V        | See section on Power-on Reset for details                                                                    |  |  |

| D004*<br>D004A* | SVDD          | <b>VDD Rise Rate</b> to<br>ensure internal<br>Power-on Reset signal     | 0.05<br>TBD                                                                 | -<br>-  | -        | V/ms     | PWRT enabled (PWRTE bit clear)<br>PWRT disabled (PWRTE bit set)<br>See section on Power-on Reset for details |  |  |

| D005            | VBOR          | Brown-out Reset<br>voltage trip point                                   | 3.65                                                                        | -       | 4.35     | V        | BODEN bit set                                                                                                |  |  |

| D010            | IDD           | Supply Current<br>(Note 2, 5)                                           | -                                                                           | 2.0     | 3.8      | mA       | XT, RC osc modes<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                        |  |  |

| D010A           |               |                                                                         | -                                                                           | 22.5    | 48       | μA       | LP OSC MODE<br>FOSC = 32 kHz, VDD = 3.0V, WDT disabled                                                       |  |  |

| D020            | IPD           | Power-down Current                                                      | -                                                                           | 7.5     | 30       | μA       | VDD = 3.0V, WDT enabled, -40°C to +85°C                                                                      |  |  |

| D021            |               | (Note 3, 5)                                                             | -                                                                           | 0.9     | 5        | μA       | VDD = $3.0V$ , WDT disabled, $0^{\circ}C$ to $+70^{\circ}C$                                                  |  |  |

| D021A           |               |                                                                         | -                                                                           | 0.9     | 5        | μA       | VDD = 3.0V, WDT disabled, -40°C to +85°C                                                                     |  |  |

|                 |               | Module Differential<br>Current (Note 6)                                 |                                                                             |         |          |          |                                                                                                              |  |  |

| D022*           | $\Delta$ IWDT | Watchdog Timer                                                          | -                                                                           | 6.0     | 20       | μA       | WDTE BIT SET, VDD = 4.0V                                                                                     |  |  |

| D022A*          | $\Delta$ IBOR | Brown-out Reset                                                         | -                                                                           | TBD     | 200      | μA       | BODEN bit set, VDD = 5.0V                                                                                    |  |  |

#### 13.2 DC Characteristics: PIC16LC62B/72A-04 (Commercial, Industrial)

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD,

$\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- 4: For RC osc mode, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: This is the voltage where the device enters the Brown-out Reset. When BOR is enabled, the device will perform a brown-out reset when VDD falls below VBOR.

### 13.3 DC Characteristics:

#### cs: PIC16C62B/72A-04 (Commercial, Industrial, Extended) PIC16C62B/72A-20 (Commercial, Industrial, Extended) PIC16LC62B/72A-04 (Commercial, Industrial)

| DC CHARACTERISTICS |       | $\begin{array}{rl} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C & \leq Ta \leq +70^{\circ}C & \mbox{for commercial} \\ & -40^{\circ}C & \leq Ta \leq +85^{\circ}C & \mbox{for industrial} \\ & -40^{\circ}C & \leq Ta \leq +125^{\circ}C & \mbox{for extended} \\ \mbox{Operating voltage VDD range as described in DC spec Section 13} \\ \mbox{and Section 13.2} \end{array}$ |                    |      |                 |        |                                                                                                    |

|--------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|-----------------|--------|----------------------------------------------------------------------------------------------------|

| Param<br>No.       | Sym   | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                 | Min                | Тур† | Max             | Units  | Conditions                                                                                         |

|                    |       | Input Low Voltage                                                                                                                                                                                                                                                                                                                                                                                                                              |                    |      |                 |        |                                                                                                    |

|                    | VIL   | I/O ports                                                                                                                                                                                                                                                                                                                                                                                                                                      |                    |      |                 |        |                                                                                                    |

| D030<br>D030A      |       | with TTL buffer                                                                                                                                                                                                                                                                                                                                                                                                                                | Vss<br>Vss         | -    | 0.15Vdd<br>0.8V | V<br>V | For entire VDD range $4.5V \le VDD \le 5.5V$                                                       |

| D031               |       | with Schmitt Trigger buffer                                                                                                                                                                                                                                                                                                                                                                                                                    | Vss                | -    | 0.2Vdd          | V      |                                                                                                    |

| D032               |       | MCLR, OSC1 (in RC mode)                                                                                                                                                                                                                                                                                                                                                                                                                        | Vss                | -    | 0.2Vdd          | V      |                                                                                                    |

| D033               |       | OSC1 (in XT, HS and LP modes)                                                                                                                                                                                                                                                                                                                                                                                                                  | Vss                | -    | 0.3Vdd          | V      | Note1                                                                                              |

|                    |       | Input High Voltage                                                                                                                                                                                                                                                                                                                                                                                                                             |                    |      |                 |        |                                                                                                    |

|                    | Vін   | I/O ports                                                                                                                                                                                                                                                                                                                                                                                                                                      |                    | -    |                 |        |                                                                                                    |

| D040               |       | with TTL buffer                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.0                | -    | Vdd             | V      | $4.5V \leq V\text{DD} \leq 5.5V$                                                                   |

| D040A              |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.25Vd<br>D + 0.8V | -    | Vdd             | V      | For entire VDD range                                                                               |

| D041               |       | with Schmitt Trigger buffer                                                                                                                                                                                                                                                                                                                                                                                                                    | 0.8Vdd             | -    | Vdd             | v      | For entire VDD range                                                                               |

| D042               |       | MCLR                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0.8Vdd             | -    | Vdd             | V      |                                                                                                    |

| D042A              |       | OSC1 (XT, HS and LP modes)                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.7Vdd             | -    | Vdd             | V      | Note1                                                                                              |

| D043               |       | OSC1 (in RC mode)                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.9Vdd             | -    | Vdd             | V      |                                                                                                    |

|                    |       | Input Leakage Current<br>(Notes 2, 3)                                                                                                                                                                                                                                                                                                                                                                                                          |                    |      |                 |        |                                                                                                    |

| D060               | lı∟   | I/O ports                                                                                                                                                                                                                                                                                                                                                                                                                                      | -                  | -    | ±1              | μA     | $\label{eq:Vss} \begin{split} &Vss \leq V PIN \leq V DD, \\ &Pin \ at \ hi\ impedance \end{split}$ |

| D061               |       | MCLR, RA4/T0CKI                                                                                                                                                                                                                                                                                                                                                                                                                                | -                  | -    | ±5              | μA     | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                           |

| D063               |       | OSC1                                                                                                                                                                                                                                                                                                                                                                                                                                           | -                  | -    | ±5              | μA     | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc modes                                                |

| D070               | IPURB | PORTB weak pull-up current                                                                                                                                                                                                                                                                                                                                                                                                                     | 50                 | 250  | 400             | μA     | VDD = 5V, VPIN = VSS                                                                               |

| D080               | Vol   | Output Low Voltage<br>I/O ports                                                                                                                                                                                                                                                                                                                                                                                                                | -                  | -    | 0.6             | v      | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                                                        |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the device be driven with external clock in RC mode.

3: Negative current is defined as current sourced by the pin.

<sup>2:</sup> The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

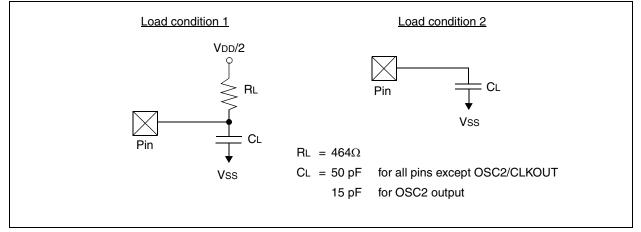

#### 13.4.2 TIMING CONDITIONS

The temperature and voltages specified in Table 13-1 apply to all timing specifications unless otherwise noted. Figure 13-4 specifies the load conditions for the timing specifications.

#### TABLE 13-1: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

| AC CHARACTERISTICS | Standard Operating Conditions (unless otherwise stated)                            |

|--------------------|------------------------------------------------------------------------------------|

|                    | Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial        |

|                    | -40°C $\leq$ TA $\leq$ +85°C for industrial                                        |

|                    | $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for extended                             |

|                    | Operating voltage VDD range as described in DC spec Section 13.1 and Section 13.2. |

|                    | LC parts operate for commercial/industrial temp's only.                            |

#### FIGURE 13-4: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

# TABLE 13-13:A/D CONVERTER CHARACTERISTICS:<br/>PIC16C72A-04 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC16C72A-20 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC16LC72A-04 (COMMERCIAL, INDUSTRIAL)

| Param<br>No. | Sym  | Characte                                   | ristic    | Min       | Тур†                   | Мах        | Units    | Conditions                                                                                                                                 |

|--------------|------|--------------------------------------------|-----------|-----------|------------------------|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| A01          | NR   | Resolution                                 |           | —         | —                      | 8-bits     | bit      | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$                                                                       |

| A02          | Eabs | Total Absolute error                       |           | —         | _                      | < ± 1      | LSB      | $\begin{array}{l} \text{VREF} = \text{VDD} = 5.12\text{V},\\ \text{VSS} \leq \text{VAIN} \leq \text{VREF} \end{array}$                     |

| A03          | EIL  | Integral linearity error                   |           | _         | —                      | < ± 1      | LSB      | $\begin{array}{l} \text{VREF} = \text{VDD} = 5.12\text{V},\\ \text{VSS} \leq \text{VAIN} \leq \text{VREF} \end{array}$                     |

| A04          | Edl  | Differential linearity er                  | ror       |           | —                      | < ± 1      | LSB      | $\begin{array}{l} \text{VREF} = \text{VDD} = 5.12\text{V},\\ \text{VSS} \leq \text{VAIN} \leq \text{VREF} \end{array}$                     |

| A05          | Efs  | Full scale error                           |           |           | _                      | < ± 1      | LSB      | $\begin{array}{l} \text{VREF} = \text{VDD} = 5.12\text{V},\\ \text{VSS} \leq \text{VAIN} \leq \text{VREF} \end{array}$                     |

| A06          | EOFF | Offset error                               |           | _         | —                      | < ± 1      | LSB      | $\begin{array}{l} \text{VREF} = \text{VDD} = 5.12\text{V},\\ \text{VSS} \leq \text{VAIN} \leq \text{VREF} \end{array}$                     |

| A10          | —    | Monotonicity                               |           | _         | guaranteed<br>(Note 3) | —          |          | $VSS \leq VAIN \leq VREF$                                                                                                                  |

| A20          | VREF | Reference voltage                          |           | 2.5V      | —                      | VDD + 0.3  | V        |                                                                                                                                            |

| A25          | VAIN | Analog input voltage                       |           | Vss - 0.3 | _                      | VREF + 0.3 | V        |                                                                                                                                            |