Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2000                       |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, SPI                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 22                                                                           |

| Program Memory Size        | 3.5KB (2K x 14)                                                              |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                |                                                                              |

| RAM Size                   | 128 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x8b                                                                     |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

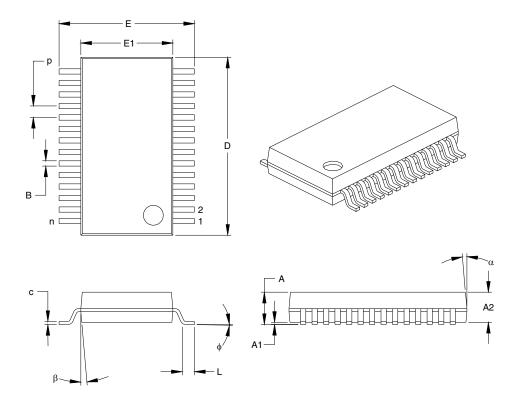

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc72at-04i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

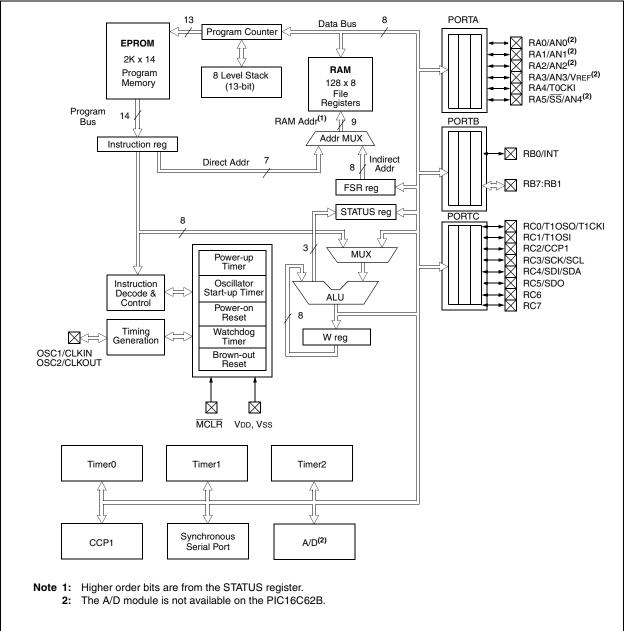

#### 1.0 DEVICE OVERVIEW

This document contains device-specific information. Additional information may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

There are two devices (PIC16C62B, PIC16C72A) covered by this datasheet. The PIC16C62B does not have the A/D module implemented.

Figure 1-1 is the block diagram for both devices. The pinouts are listed in Table 1-1.

© 1998-2013 Microchip Technology Inc.

#### TABLE 3-5 PORTC FUNCTIONS

| Name            | Bit# | Buffer<br>Type | Function                                                                    | TRISC<br>Override |

|-----------------|------|----------------|-----------------------------------------------------------------------------|-------------------|

| RC0/T1OSO/T1CKI | bit0 | ST             | Input/output port pin or Timer1 oscillator output/Timer1 clock input        | Yes               |

| RC1/T1OSI       | bit1 | ST             | Input/output port pin or Timer1 oscillator input                            | Yes               |

| RC2/CCP1        | bit2 | ST             | Input/output port pin or Capture1 input/Compare1 output/PWM1 output         | No                |

| RC3/SCK/SCL     | bit3 | ST             | RC3 can also be the synchronous serial clock for both SPI and $I^2C$ modes. | No                |

| RC4/SDI/SDA     | bit4 | ST             | RC4 can also be the SPI Data In (SPI mode) or data $I/O$ ( $I^2C$ mode).    | No                |

| RC5/SDO         | bit5 | ST             | Input/output port pin or Synchronous Serial Port data output                | No                |

| RC6             | bit6 | ST             | Input/output port pin                                                       | No                |

| RC7             | bit7 | ST             | Input/output port pin                                                       | No                |

Legend: ST = Schmitt Trigger input

#### TABLE 3-6SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7   | Bit 6       | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|---------|-------------|------------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 07h     | PORTC | RC7     | RC6         | RC5        | RC4   | RC3   | RC2   | RC1   | RC0   | xxxx xxxx                | uuuu uuuu                 |

| 87h     | TRISC | PORTC I | Data Direct | ion Regist | er    |       |       |       |       | 1111 1111                | 1111 1111                 |

Legend: x = unknown, u = unchanged.

NOTES:

#### REGISTER 8-2: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)

| R/W-0    | R/W-0                                                                                                                                                                                                                                                                   | R/W-0                                                                                                                                                           | R/W-0                                                                                                                        | R/W-0                                                                                                       | R/W-0                                                                                              | R/W-0                                                           | R/W-0                        |                                                                                                                         |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|

| WCOL     | SSPOV                                                                                                                                                                                                                                                                   | SSPEN                                                                                                                                                           | CKP                                                                                                                          | SSPM3                                                                                                       | SSPM2                                                                                              | SSPM1                                                           | SSPM0                        | R = Readable bit                                                                                                        |  |

| bit7     |                                                                                                                                                                                                                                                                         |                                                                                                                                                                 | -                                                                                                                            |                                                                                                             |                                                                                                    |                                                                 | bitO                         | W = Writable bit<br>U = Unimplemented bit, read<br>as '0'<br>- n =Value at POR reset                                    |  |

| bit 7:   | <pre>WCOL: Write Collision Detect bit 1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software) 0 = No collision</pre>                                                                                          |                                                                                                                                                                 |                                                                                                                              |                                                                                                             |                                                                                                    |                                                                 |                              |                                                                                                                         |  |

| bit 6:   | SSPOV: R                                                                                                                                                                                                                                                                | eceive Ov                                                                                                                                                       | erflow Ind                                                                                                                   | cator bit                                                                                                   |                                                                                                    |                                                                 |                              |                                                                                                                         |  |

|          | the data in<br>if only trar                                                                                                                                                                                                                                             | byte is reco<br>SSPSR is<br>smitting d<br>reception (                                                                                                           | lost. Ove<br>ata, to ave                                                                                                     | rflow can o<br>oid setting                                                                                  | nly occur i<br>overflow.                                                                           | in slave mo<br>In master                                        | ode. The use<br>operation, t | evious data. In case of overflow,<br>er must read the SSPBUF, even<br>he overflow bit is not set since<br>SUF register. |  |

|          | In $l^2$ <u>C mode</u><br>1 = A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don't care"<br>in transmit mode. SSPOV must be cleared in software in either mode.<br>0 = No overflow                                        |                                                                                                                                                                 |                                                                                                                              |                                                                                                             |                                                                                                    |                                                                 |                              |                                                                                                                         |  |

| bit 5:   | SSPEN: S                                                                                                                                                                                                                                                                | ynchronou                                                                                                                                                       | is Serial F                                                                                                                  | ort Enable                                                                                                  | bit                                                                                                |                                                                 |                              |                                                                                                                         |  |

|          | In SPI mode<br>1 = Enables serial port and configures SCK, SDO, and SDI as serial port pins<br>0 = Disables serial port and configures these pins as I/O port pins                                                                                                      |                                                                                                                                                                 |                                                                                                                              |                                                                                                             |                                                                                                    |                                                                 |                              |                                                                                                                         |  |

|          | In $I^2C$ mode<br>1 = Enables the serial port and configures the SDA and SCL pins as serial port pins<br>0 = Disables serial port and configures these pins as I/O port pins<br>In both modes, when enabled, these pins must be properly configured as input or output. |                                                                                                                                                                 |                                                                                                                              |                                                                                                             |                                                                                                    |                                                                 |                              |                                                                                                                         |  |

| bit 4:   | <b>CKP</b> : Clock Polarity Select bit<br>In SPI mode<br>1 = Idle state for clock is a high level $0 = Idle state for clock is a low level In I2C mode SCK release control 1 = Enable clock0 = Holds clock low (clock stretch)$                                         |                                                                                                                                                                 |                                                                                                                              |                                                                                                             |                                                                                                    |                                                                 |                              |                                                                                                                         |  |

| bit 3-0: | $0001 = SF$ $0010 = SF$ $0100 = SF$ $0101 = SF$ $0110 = I^{2}C$ $0111 = I^{2}C$ $1011 = I^{2}C$ $1110 = I^{2}C$                                                                                                                                                         | PI master of<br>PI master of<br>PI master of<br>PI master of<br>PI slave mo<br>C slave mo<br>C slave mo<br>C slave mo<br>C slave mo<br>C slave mo<br>C slave mo | operation,<br>operation,<br>operation,<br>ode, clock<br>ode, clock<br>de, 7-bit a<br>de, 10-bit<br>controlled<br>de, 7-bit a | clock = Fo<br>clock = Fo<br>clock = Fo<br>clock = Th<br>= SCK pin<br>address<br>address<br>ddress<br>ddress | ISC/4<br>ISC/16<br>ISC/64<br>IR2 outpu<br>I. SS pin c<br>I. SS pin c<br>peration (s<br>th start an | t/2<br>ontrol ena<br>ontrol disa<br>slave idle)<br>d stop bit i |                              |                                                                                                                         |  |

Г

#### 10.2 Oscillator Configurations

#### 10.2.1 OSCILLATOR TYPES

The PIC16CXXX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

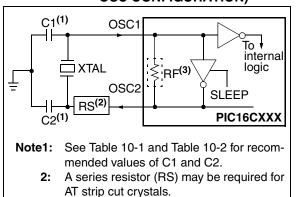

## 10.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

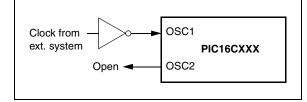

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 10-2). The PIC16CXXX oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can use an external clock source to drive the OSC1/CLKIN pin (Figure 10-3).

#### FIGURE 10-2: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

3: RF varies with the crystal chosen.

#### FIGURE 10-3: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

#### TABLE 10-1 CERAMIC RESONATORS

#### Ranges Tested:

| Ranges lested: |                                                                         |                      |              |  |  |  |

|----------------|-------------------------------------------------------------------------|----------------------|--------------|--|--|--|

| Mode           | Freq                                                                    | OSC1                 | 0\$C2        |  |  |  |

| XT             | 455 kHz                                                                 | 68 - 100 pF          | 68 - 100 pF  |  |  |  |

|                | 2.0 MHz                                                                 | 15 - 68 pF 🛛 🤇       | 15 - 68 pF   |  |  |  |

|                | 4.0 MHz                                                                 | 15 - 68 pF           | ∖15, - 68 pF |  |  |  |

| HS             | 8.0 MHz                                                                 | 10 - 68(pF           | े10 - 68 pF  |  |  |  |

|                | 16.0 MHz                                                                | 10,-22,0F            | 10 - 22 pF   |  |  |  |

|                | These values are for design guidance only. See notes at bottom of page. |                      |              |  |  |  |

| Resonator      | Resonators Used:                                                        |                      |              |  |  |  |

| 455 kHz        | Panasonie E                                                             | FO-A455K04B          | ± 0.3%       |  |  |  |

| 2.0 MHz        | Wurata Erie CSA2.00MG ± 0.5%                                            |                      |              |  |  |  |

| 4.0 MHz        | Murata Erie CSA4.00MG ± 0.5%                                            |                      |              |  |  |  |

| 8.0 MAHZ       | Murata Erie CSA8.00MT ± 0.5%                                            |                      |              |  |  |  |

| 16.0 MHz       | Murata Erie (                                                           | CSA16.00MX           | $\pm 0.5\%$  |  |  |  |

| Resona         | ators did not hav                                                       | ve built-in capacito | ors.         |  |  |  |

## TABLE 10-2CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq                                                         | Cap. Range<br>C1 | Cap. Range<br>C2 |  |  |

|----------|-------------------------------------------------------------------------|------------------|------------------|--|--|

| LP       | 32 kHz                                                                  | 33 pF            | 33 pF            |  |  |

|          | 200 kHz                                                                 | 15 pF            | 15 pF            |  |  |

| XT       | 200 kHz                                                                 | 47-68 pF         | 47-68 pF         |  |  |

|          | 1 MHz                                                                   | 15 pF 🔍          | ✓ 15 pF<br>15 pF |  |  |

|          | 4 MHz                                                                   | 15 pF 🕟          | 15 pF            |  |  |

| HS       | 4 MHz                                                                   | 15 pt            | ✓ 15 pF          |  |  |

|          | 8 MHz                                                                   | 15-33 pE>        | 15-33 pF         |  |  |

|          | 20 MHz                                                                  | (15-33 pF        | 15-33 pF         |  |  |

|          | These values are for design guidance only. See notes at bottom of page. |                  |                  |  |  |

|          | Crystals Used                                                           |                  |                  |  |  |

| 32 kHz   | Epson C-001R32.768K-A ± 20 PPM                                          |                  |                  |  |  |

| 200 kt/2 | STD XTL 200.000KHz ± 20 PPM                                             |                  |                  |  |  |

| 1 MHz    | ECS ECS-10-13-1 ± 50 PPM                                                |                  |                  |  |  |

| 4 MHz    | ECS ECS-4                                                               | 40-20-1          | ± 50 PPM         |  |  |

| 8 MHz    | EPSON CA                                                                | -301 8.000M-C    | ± 30 PPM         |  |  |

**Note 1:** Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

EPSON CA-301 20.000M-C

20 MHz

2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

± 30 PPM

- **3:** Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- 4: Oscillator performance should be verified when migrating between devices (including PIC16C62A to PIC16C62B and PIC16C72 to PIC16C72A)

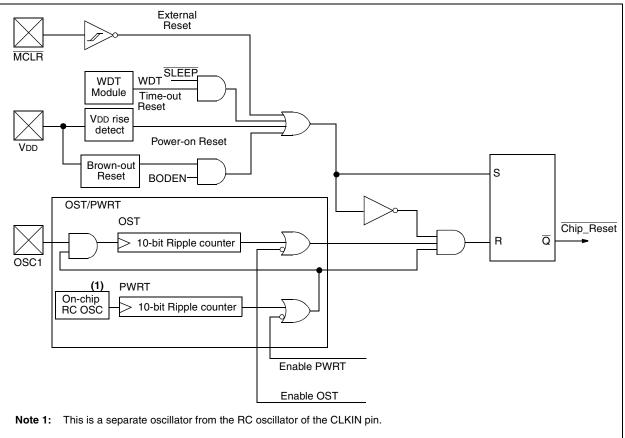

#### FIGURE 10-5: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### 10.4 Power-On Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.5V - 2.1V). To take advantage of the POR, just tie the  $\overline{\text{MCLR}}$  pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified (SVDD, parameter D004). For a slow rise time, see Figure 10-6.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met. Brown-out Reset may be used to meet the start-up conditions.

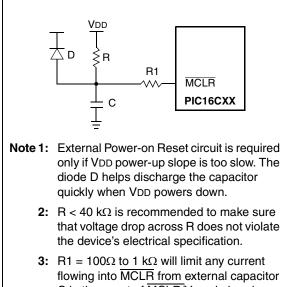

#### FIGURE 10-6: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

#### R1 = 100Ω to 1 kΩ will limit any current flowing into $\overline{MCLR}$ from external capacitor C in the event of $\overline{MCLR}/VPP$ pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

#### 10.5 Power-up Timer (PWRT)

The Power-up Timer provides a fixed nominal time-out (TPWRT, parameter #33) from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip-to-chip due to VDD, temperature and process variation. See DC parameters for details.

#### 10.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a delay of 1024 oscillator cycles (from OSC1 input) after the PWRT delay is over (TOST, parameter #32). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

Note: The OST delay may not occur when the device wakes from SLEEP.

#### 10.7 Brown-Out Reset (BOR)

The configuration bit, BODEN, can enable or disable the Brown-Out Reset circuit. If VPP falls below Vbor (parameter #35, about  $100\mu$ S), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a reset may not occur.

Once the brown-out occurs, the device will remain in brown-out reset until VDD rises above VBOR. The power-up timer then keeps the device in reset for TPWRT (parameter #33, about 72mS). If VDD should fall below VBOR during TPWRT, the brown-out reset process will restart when VDD rises above VBOR with the power-up timer reset. The power-up timer is always enabled when the brown-out reset circuit is enabled, regardless of the state of the PWRT configuration bit.

| TABLE 10-6 INITIALIZATION CONDITIONS FOR ALL REGISTERS |     |               |                                    |                          |                                 |

|--------------------------------------------------------|-----|---------------|------------------------------------|--------------------------|---------------------------------|

| Register                                               |     | cable<br>ices | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

| W                                                      | 62B | 72A           | XXXX XXXX                          | uuuu uuuu                | սսսս սսսս                       |

| INDF                                                   | 62B | 72A           | N/A                                | N/A                      | N/A                             |

| TMR0                                                   | 62B | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PCL                                                    | 62B | 72A           | 0000h                              | 0000h                    | PC + 1 <sup>(2)</sup>           |

| STATUS                                                 | 62B | 72A           | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu <b>(3)</b>            |

| FSR                                                    | 62B | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| PORTA <sup>(4)</sup>                                   | 62B | 72A           | 0x 0000                            | 0u 0000                  | uu uuuu                         |

| PORTB <sup>(5)</sup>                                   | 62B | 72A           | xxxx xxxx                          | սսսս սսսս                | սսսս սսսս                       |

| PORTC <sup>(5)</sup>                                   | 62B | 72A           | xxxx xxxx                          | սսսս սսսս                | uuuu uuuu                       |

| PCLATH                                                 | 62B | 72A           | 0 0000                             | 0 0000                   | u uuuu                          |

| INTCON                                                 | 62B | 72A           | 0000 000x                          | 0000 000u                | uuuu uuuu <b>(1)</b>            |

|                                                        | 62B | 72A           | 0000                               | 0000                     | uuuu <b>(1)</b>                 |

| PIR1                                                   | 62B | 72A           | -0 0000                            | -0 0000                  | -u uuuu <b>(1)</b>              |

| TMR1L                                                  | 62B | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| TMR1H                                                  | 62B | 72A           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| T1CON                                                  | 62B | 72A           | 00 0000                            | uu uuuu                  | uu uuuu                         |

| TMR2                                                   | 62B | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| T2CON                                                  | 62B | 72A           | -000 0000                          | -000 0000                | -uuu uuuu                       |

| SSPBUF                                                 | 62B | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| SSPCON                                                 | 62B | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| CCPR1L                                                 | 62B | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| CCPR1H                                                 | 62B | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| CCP1CON                                                | 62B | 72A           | 00 0000                            | 00 0000                  | uu uuuu                         |

| ADRES                                                  | 62B | 72A           | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| ADCON0                                                 | 62B | 72A           | 0000 00-0                          | 0000 00-0                | uuuu uu-u                       |

| OPTION_REG                                             | 62B | 72A           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISA                                                  | 62B | 72A           | 11 1111                            | 11 1111                  | uu uuuu                         |

| TRISB                                                  | 62B | 72A           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISC                                                  | 62B | 72A           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

|                                                        | 62B | 72A           | 0000                               | 0000                     | uuuu                            |

| PIE1                                                   | 62B | 72A           | -0 0000                            | -0 0000                  | -u uuuu                         |

| PCON                                                   | 62B | 72A           | 0q                                 | uq                       | uq                              |

| PR2                                                    | 62B | 72A           | 1111 1111                          | 1111 1111                | 1111 1111                       |

| SSPADD                                                 | 62B | 72A           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| SSPSTAT                                                | 62B | 72A           | 0000 0000                          | 0000 0000                | սսսս սսսս                       |

| ADCON1                                                 | 62B | 72A           | 000                                | 000                      | uuu                             |

| TABLE 10-6 | INITIALIZATION CONDITIONS FOR ALL REGISTERS |

|------------|---------------------------------------------|

|            |                                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', <math>q = value depends on condition

Note 1: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

**3:** See Table 10-5 for reset value for specific condition.

4: On any device reset, these pins are configured as inputs.

5: This is the value that will be in the port output latch.

| COMF             | Complement f                                                                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] COMF f,d                                                                                                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                           |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                |

| Status Affected: | Z                                                                                                                                                         |

| Description:     | The contents of register 'f' are comple-<br>mented. If 'd' is 0, the result is stored<br>in W. If 'd' is 1, the result is stored<br>back in register 'f'. |

| GOTO             | Unconditional Branch                                                                                                                                                                          |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                       |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                            |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                               |

| Status Affected: | None                                                                                                                                                                                          |

| Description:     | GOTO is an unconditional branch. The<br>eleven bit immediate value is loaded<br>into PC bits <10:0>. The upper bits of<br>PC are loaded from PCLATH<4:3>.<br>GOTO is a two cycle instruction. |

| DECF             | Decrement f                                                                                                                          |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECF f,d                                                                                                            |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                          |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                  |

| Status Affected: | Z                                                                                                                                    |

| Description:     | Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| INCF             | Increment f                                                                                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                       |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                     |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is 0, the result is placed<br>in the W register. If 'd' is 1, the result is<br>placed back in register 'f'. |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                      | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                          | Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                             | Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in[0,1] \end{array}$                                                                                                                                                                                                                                                            |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                  | Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                        | Status Affected: | None                                                                                                                                                                                                                                                                                                                  |

| Description:     | The contents of register 'f' are decre-<br>mented. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>placed back in register 'f'.<br>If the result is 1, the next instruction, is<br>executed. If the result is 0, then a NOP is<br>executed instead making it a $2Tcy$<br>instruction. | Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is 0, the result is placed<br>in the W register. If 'd' is 1, the result is<br>placed back in register 'f'.<br>If the result is 1, the next instruction is<br>executed. If the result is 0, a NOP is<br>executed instead making it a $2Tcy$<br>instruction. |

# PIC16C62B/72A

| IORLW            | Inclusive OR Literal with W                                                                                           |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] IORLW k                                                                                                     |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                     |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                          |  |  |  |  |  |

| Status Affected: | Z                                                                                                                     |  |  |  |  |  |

| Description:     | The contents of the W register is<br>OR'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |  |  |  |  |  |

| MOVLW            | Move Literal to W                                                                          |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                   |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                          |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                        |  |  |  |  |  |

| Status Affected: | None                                                                                       |  |  |  |  |  |

| Description:     | The eight bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |  |  |  |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                                  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] IORWF f,d                                                                                                                                                      |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                        |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                               |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                      |  |  |  |  |  |

| Description:     | Inclusive OR the W register with regis-<br>ter 'f'. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>placed back in register 'f'. |  |  |  |  |  |

| MOVWF            | Move W to f                           |

|------------------|---------------------------------------|

| Syntax:          | [label] MOVWF f                       |

| Operands:        | $0 \leq f \leq 127$                   |

| Operation:       | $(W) \rightarrow (f)$                 |

| Status Affected: | None                                  |

| Description:     | Move data from W register to register |

| MOVF             | Move f                                                                                                                                                                                                                                                                                |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                           |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                                       |

| Status Affected: | Z                                                                                                                                                                                                                                                                                     |

| Description:     | The contents of register f is moved to<br>a destination dependant upon the sta-<br>tus of d. If $d = 0$ , destination is W reg-<br>ister. If $d = 1$ , the destination is file<br>register f itself. $d = 1$ is useful to test a<br>file register since status flag Z is<br>affected. |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

### 12.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB™ IDE Software

- Assemblers/Compilers/Linkers

- MPASM Assembler

- MPLAB-C17 and MPLAB-C18 C Compilers

- MPLINK/MPLIB Linker/Librarian

- Simulators

- MPLAB-SIM Software Simulator

- Emulators

- MPLAB-ICE Real-Time In-Circuit Emulator

- PICMASTER<sup>®</sup>/PICMASTER-CE In-Circuit Emulator

- ICEPIC™

- In-Circuit Debugger

- MPLAB-ICD for PIC16F877

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- Low-Cost Demonstration Boards

- SIMICE

- PICDEM-1

- PICDEM-2

- PICDEM-3

- PICDEM-17

- SEEVAL®

- KEELOQ<sup>®</sup>

#### 12.1 <u>MPLAB Integrated Development</u> <u>Environment Software</u>

- The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a Windows<sup>®</sup>-based application which contains:

- Multiple functionality

- editor

- simulator

- programmer (sold separately)

- emulator (sold separately)

- A full featured editor

- A project manager

- · Customizable tool bar and key mapping

- · A status bar

- On-line help

MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- object code

The ability to use MPLAB with Microchip's simulator, MPLAB-SIM, allows a consistent platform and the ability to easily switch from the cost-effective simulator to the full featured emulator with minimal retraining.

#### 12.2 MPASM Assembler

MPASM is a full featured universal macro assembler for all PIC MCUs. It can produce absolute code directly in the form of HEX files for device programmers, or it can generate relocatable objects for MPLINK.

MPASM has a command line interface and a Windows shell and can be used as a standalone application on a Windows 3.x or greater system. MPASM generates relocatable object files, Intel standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file which contains source lines and generated machine code, and a COD file for MPLAB debugging.

MPASM features include:

- MPASM and MPLINK are integrated into MPLAB projects.

- MPASM allows user defined macros to be created for streamlined assembly.

- MPASM allows conditional assembly for multi purpose source files.

- MPASM directives allow complete control over the assembly process.

#### 12.3 <u>MPLAB-C17 and MPLAB-C18</u> <u>C Compilers</u>

The MPLAB-C17 and MPLAB-C18 Code Development Systems are complete ANSI 'C' compilers and integrated development environments for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

#### 12.4 MPLINK/MPLIB Linker/Librarian

MPLINK is a relocatable linker for MPASM and MPLAB-C17 and MPLAB-C18. It can link relocatable objects from assembly or C source files along with precompiled libraries using directives from a linker script.

### 13.3 DC Characteristics:

#### cs: PIC16C62B/72A-04 (Commercial, Industrial, Extended) PIC16C62B/72A-20 (Commercial, Industrial, Extended) PIC16LC62B/72A-04 (Commercial, Industrial)

| DC CHA        | RISTICS | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                    |      |                 |        |                                                                                                    |  |  |

|---------------|---------|------------------------------------------------------|--------------------|------|-----------------|--------|----------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.  | Sym     | Characteristic                                       | Min                | Тур† | Max             | Units  | Conditions                                                                                         |  |  |

|               |         | Input Low Voltage                                    |                    |      |                 |        |                                                                                                    |  |  |

|               | VIL     | I/O ports                                            |                    |      |                 |        |                                                                                                    |  |  |

| D030<br>D030A |         | with TTL buffer                                      | Vss<br>Vss         | -    | 0.15Vdd<br>0.8V | V<br>V | For entire VDD range $4.5V \le VDD \le 5.5V$                                                       |  |  |

| D031          |         | with Schmitt Trigger buffer                          | Vss                | -    | 0.2Vdd          | V      |                                                                                                    |  |  |

| D032          |         | MCLR, OSC1 (in RC mode)                              | Vss                | -    | 0.2Vdd          | V      |                                                                                                    |  |  |

| D033          |         | OSC1 (in XT, HS and LP modes)                        | Vss                | -    | 0.3Vdd          | V      | Note1                                                                                              |  |  |

|               |         | Input High Voltage                                   |                    |      |                 |        |                                                                                                    |  |  |

|               | Vін     | I/O ports                                            |                    | -    |                 |        |                                                                                                    |  |  |

| D040          |         | with TTL buffer                                      | 2.0                | -    | Vdd             | V      | $4.5V \leq V\text{DD} \leq 5.5V$                                                                   |  |  |

| D040A         |         |                                                      | 0.25Vd<br>D + 0.8V | -    | Vdd             | V      | For entire VDD range                                                                               |  |  |

| D041          |         | with Schmitt Trigger buffer                          | 0.8Vdd             | -    | Vdd             | v      | For entire VDD range                                                                               |  |  |

| D042          |         | MCLR                                                 | 0.8Vdd             | -    | Vdd             | V      |                                                                                                    |  |  |

| D042A         |         | OSC1 (XT, HS and LP modes)                           | 0.7Vdd             | -    | Vdd             | V      | Note1                                                                                              |  |  |

| D043          |         | OSC1 (in RC mode)                                    | 0.9Vdd             | -    | Vdd             | V      |                                                                                                    |  |  |

|               |         | Input Leakage Current<br>(Notes 2, 3)                |                    |      |                 |        |                                                                                                    |  |  |

| D060          | lı∟     | I/O ports                                            | -                  | -    | ±1              | μA     | $\label{eq:Vss} \begin{split} &Vss \leq V PIN \leq V DD, \\ &Pin \ at \ hi\ impedance \end{split}$ |  |  |

| D061          |         | MCLR, RA4/T0CKI                                      | -                  | -    | ±5              | μA     | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                           |  |  |

| D063          |         | OSC1                                                 | -                  | -    | ±5              | μA     | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc modes                                                |  |  |

| D070          | IPURB   | PORTB weak pull-up current                           | 50                 | 250  | 400             | μA     | VDD = 5V, VPIN = VSS                                                                               |  |  |

| D080          | Vol     | Output Low Voltage<br>I/O ports                      | -                  | -    | 0.6             | v      | IOL = 8.5  mA,  VDD = 4.5 V,<br>-40°C to +85°C                                                     |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the device be driven with external clock in RC mode.

3: Negative current is defined as current sourced by the pin.

<sup>2:</sup> The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

| DC CHA       | ARACTE | RISTICS                                    | $\begin{array}{rl} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C & \leq Ta \leq +70^{\circ}C & \mbox{for commercial} \\ & -40^{\circ}C & \leq Ta \leq +85^{\circ}C & \mbox{for industrial} \\ & -40^{\circ}C & \leq Ta \leq +125^{\circ}C & \mbox{for extended} \\ \\ \mbox{Operating voltage VDD range as described in DC spec Section 13.1} \\ \mbox{and Section 13.2} \end{array}$ |      |     |       |                                                                         |

|--------------|--------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|-------------------------------------------------------------------------|

| Param<br>No. | Sym    | Characteristic                             | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Тур† | Max | Units | Conditions                                                              |

|              |        |                                            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -    | 0.6 | V     | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C                            |

| D083         |        | OSC2/CLKOUT<br>(RC osc mode)               | -                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -    | 0.6 | V     | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                             |

|              |        |                                            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -    | 0.6 | V     | IOL = 1.2 mA, VDD = 4.5V,<br>-40°C to +125°C                            |

|              |        | Output High Voltage                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |     |       |                                                                         |

| D090         | Vон    | I/O ports (Note 3)                         | VDD-0.7                                                                                                                                                                                                                                                                                                                                                                                                                                             | -    | -   | V     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +85°C                            |

|              |        |                                            | VDD-0.7                                                                                                                                                                                                                                                                                                                                                                                                                                             | -    | -   | V     | IOH = -2.5 mA, VDD = 4.5V,<br>-40°С to +125°С                           |

| D092         |        | OSC2/CLKOUT (RC osc<br>mode)               | Vdd-0.7                                                                                                                                                                                                                                                                                                                                                                                                                                             | -    | -   | V     | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                            |

|              |        |                                            | Vdd-0.7                                                                                                                                                                                                                                                                                                                                                                                                                                             | -    | -   | V     | IOH = -1.0 mA, VDD = 4.5V,<br>-40°C to +125°C                           |

| D150*        | Vod    | Open-Drain High Voltage                    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -    | 8.5 | V     | RA4 pin                                                                 |

|              |        | Capacitive Loading Specs<br>on Output Pins |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |     |       |                                                                         |

| D100         | Cosc2  | OSC2 pin                                   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -    | 15  | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1. |

| D101         | Cio    | All I/O pins and OSC2 (in RC mode)         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -    | 50  | pF    |                                                                         |

| D102         | Cb     | SCL, SDA in I <sup>2</sup> C mode          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -    | 400 | pF    |                                                                         |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the device be driven with external clock in RC mode.

2: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

#### 13.4 AC (Timing) Characteristics

#### 13.4.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2              | ppS                                 | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|-----------------------|-------------------------------------|-----------|----------------------------------------|

| 2. TppS               |                                     | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                     |                                     |           |                                        |

| F                     | Frequency                           | Т         | Time                                   |

| Lowercas              | se letters (pp) and their meanings: |           |                                        |

| рр                    |                                     |           |                                        |

| сс                    | CCP1                                | OSC       | OSC1                                   |

| ck                    | CLKOUT                              | rd        | RD                                     |

| CS                    | CS                                  | rw        | RD or WR                               |

| di                    | SDI                                 | SC        | SCK                                    |

| do                    | SDO                                 | SS        | SS                                     |

| dt                    | Data in                             | t0        | TOCKI                                  |

| io                    | I/O port                            | t1        | T1CKI                                  |

| mc                    | MCLR                                | wr        | WR                                     |

| Uppercas              | se letters and their meanings:      |           |                                        |

| S                     |                                     |           |                                        |

| F                     | Fall                                | Р         | Period                                 |

| Н                     | High                                | R         | Rise                                   |

| I                     | Invalid (Hi-impedance)              | V         | Valid                                  |

| L                     | Low                                 | Z         | Hi-impedance                           |

| I <sup>2</sup> C only |                                     |           |                                        |

| AA                    | output access                       | High      | High                                   |

| BUF                   | Bus free                            | Low       | Low                                    |

| Tcc:st (I             | <sup>2</sup> C specifications only) |           |                                        |

| CC                    |                                     |           |                                        |

| HD                    | Hold                                | SU        | Setup                                  |

| ST                    |                                     |           |                                        |

| DAT                   | DATA input hold                     | STO       | STOP condition                         |

| STA                   | START condition                     |           |                                        |

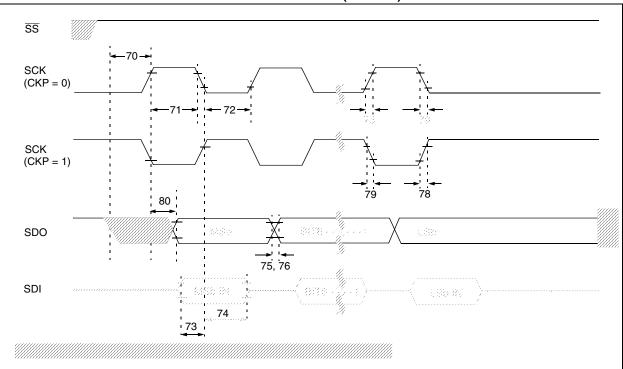

#### FIGURE 13-11: EXAMPLE SPI MASTER MODE TIMING (CKE = 0)

| Param.<br>No. | Symbol                | Characterist                              | Min         | Тур†         | Max | Units | Conditions |        |

|---------------|-----------------------|-------------------------------------------|-------------|--------------|-----|-------|------------|--------|

| 70            | TssL2scH,<br>TssL2scL | SS↓ to SCK↓ or SCK↑ input                 | Тсү         | —            | —   | ns    |            |        |

| 71            | TscH                  | SCK input high time                       | Continuous  | 1.25Tcy + 30 | —   | _     | ns         |        |

| 71A           |                       | (slave mode)                              | Single Byte | 40           |     | _     | ns         | Note 1 |

| 72            | TscL                  | SCK input low time                        | Continuous  | 1.25Tcy + 30 | —   |       | ns         |        |

| 72A           |                       | (slave mode)                              | Single Byte | 40           | _   | _     | ns         | Note 1 |

| 73            | TdiV2scH,<br>TdiV2scL | Setup time of SDI data inpu               | 100         | —            | —   | ns    |            |        |

| 73A           | Тв2в                  | Last clock edge of Byte1 to edge of Byte2 | 1.5Tcy + 40 | —            | —   | ns    | Note 1     |        |

| 74            | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge   |             | 100          | —   | —     | ns         |        |

| 75            | TdoR                  | SDO data output rise time                 | PIC16CXX    | _            | 10  | 25    | ns         |        |