Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | ARM® Cortex®-M4                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 24                                                                        |

| Program Memory Size        | 256KB (256K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 32K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.85V ~ 3.8V                                                              |

| Data Converters            | A/D 24x12b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TJ)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 32-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 32-QFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32pg1b100f256im32-c0 |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

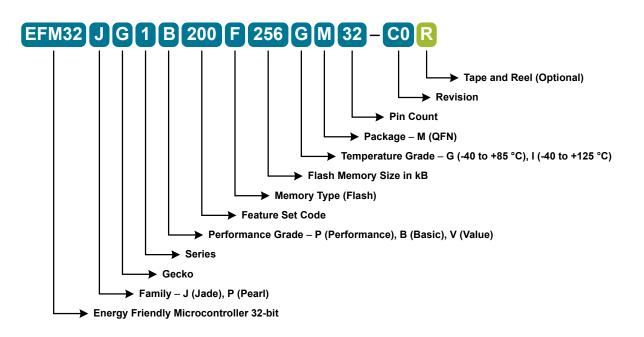

## 2. Ordering Information

| Ordering Code           | Flash<br>(kB) | RAM (kB) | DC-DC Converter | GPIO | Package | Temp<br>Range |

|-------------------------|---------------|----------|-----------------|------|---------|---------------|

| EFM32PG1B200F256GM48-C0 | 256           | 32       | Yes             | 32   | QFN48   | -40 to +85    |

| EFM32PG1B200F256IM48-C0 | 256           | 32       | Yes             | 32   | QFN48   | -40 to +125   |

| EFM32PG1B200F128GM48-C0 | 128           | 32       | Yes             | 32   | QFN48   | -40 to +85    |

| EFM32PG1B200F256GM32-C0 | 256           | 32       | Yes             | 20   | QFN32   | -40 to +85    |

| EFM32PG1B200F256IM32-C0 | 256           | 32       | Yes             | 20   | QFN32   | -40 to +125   |

| EFM32PG1B200F128GM32-C0 | 128           | 32       | Yes             | 20   | QFN32   | -40 to +85    |

| EFM32PG1B100F256GM32-C0 | 256           | 32       | No              | 24   | QFN32   | -40 to +85    |

| EFM32PG1B100F256IM32-C0 | 256           | 32       | No              | 24   | QFN32   | -40 to +125   |

| EFM32PG1B100F128GM32-C0 | 128           | 32       | No              | 24   | QFN32   | -40 to +85    |

Figure 2.1. OPN Decoder

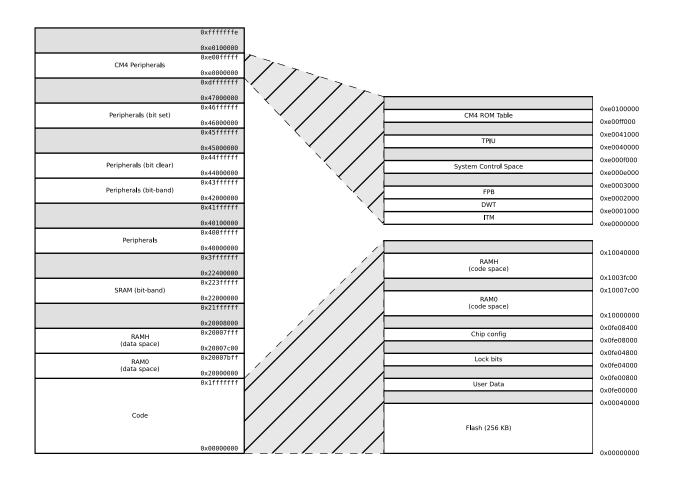

#### 3.11 Memory Map

The EFM32PG1 memory map is shown in the figures below. RAM and flash sizes are for the largest memory configuration.

Figure 3.2. EFM32PG1 Memory Map — Core Peripherals and Code Space

## 4. Electrical Specifications

#### 4.1 Electrical Characteristics

All electrical parameters in all tables are specified under the following conditions, unless stated otherwise:

- Typical values are based on T<sub>AMB</sub>=25 °C and V<sub>DD</sub>= 3.3 V, by production test and/or technology characterization.

- Minimum and maximum values represent the worst conditions across supply voltage, process variation, and operating temperature, unless stated otherwise.

Refer to Table 4.2 General Operating Conditions on page 11 for more details about operational supply and temperature limits.

#### 4.1.1 Absolute Maximum Ratings

Stresses above those listed below may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. For more information on the available quality and reliability data, see the Quality and Reliability Monitor Report at http://www.silabs.com/support/quality/pages/default.aspx.

| Parameter                                           | Symbol                | Test Condition | Min  | Тур | Max                            | Unit   |

|-----------------------------------------------------|-----------------------|----------------|------|-----|--------------------------------|--------|

| Storage temperature range                           | T <sub>STG</sub>      |                | -50  |     | 150                            | °C     |

| External main supply voltage                        | V <sub>DDMAX</sub>    |                | 0    |     | 3.8                            | V      |

| External main supply voltage ramp rate              | VDDRAMPMAX            |                | _    |     | 1                              | V / µs |

| Voltage on any 5V tolerant<br>GPIO pin <sup>1</sup> | V <sub>DIGPIN</sub>   |                | -0.3 | _   | Min of 5.25<br>and IOVDD<br>+2 | V      |

| Voltage on non-5V tolerant<br>GPIO pins             | -                     |                | -0.3 | _   | IOVDD+0.3                      | V      |

| Voltage on HFXO pins                                | V <sub>HFXOPIN</sub>  |                | -0.3 |     | 1.4                            | V      |

| Total current into VDD power lines (source)         | IVDDMAX               |                | _    | _   | 200                            | mA     |

| Total current into VSS ground lines (sink)          | I <sub>VSSMAX</sub>   |                | _    | _   | 200                            | mA     |

| Current per I/O pin (sink)                          | I <sub>IOMAX</sub>    |                | _    |     | 50                             | mA     |

| Current per I/O pin (source)                        |                       |                | _    |     | 50                             | mA     |

| Current for all I/O pins (sink)                     | I <sub>IOALLMAX</sub> |                | _    |     | 200                            | mA     |

| Current for all I/O pins<br>(source)                | -                     |                | _    | _   | 200                            | mA     |

| Voltage difference between AVDD and VREGVDD         | $\Delta V_{DD}$       |                | _    |     | 0.3                            | V      |

| Junction Temperature for -G grade devices           | Тј                    |                | -40  | _   | 105                            | °C     |

| Junction Temperature for -I grade devices           |                       |                | -40  | _   | 125                            | °C     |

| Note:                                               | 1                     | 1              | 1    | 1   | 1                              |        |

#### Table 4.1. Absolute Maximum Ratings

#### Note:

1. When a GPIO pin is routed to the analog module through the APORT, the maximum voltage = IOVDD.

### 4.1.9 Flash Memory Characteristics

| Parameter                                      | Symbol               | Test Condition            | Min   | Тур | Max | Unit   |

|------------------------------------------------|----------------------|---------------------------|-------|-----|-----|--------|

| Flash erase cycles before failure              | EC <sub>FLASH</sub>  |                           | 10000 | _   | _   | cycles |

| Flash data retention                           | RET <sub>FLASH</sub> | T <sub>AMB</sub> ≤ 85 °C  | 10    | _   | _   | years  |

|                                                |                      | T <sub>AMB</sub> ≤ 125 °C | 10    | —   | _   | years  |

| Word (32-bit) programming time                 | t <sub>W_PROG</sub>  |                           | 20    | 26  | 40  | μs     |

| Page erase time                                | t <sub>PERASE</sub>  |                           | 20    | 27  | 40  | ms     |

| Mass erase time                                | t <sub>MERASE</sub>  |                           | 20    | 27  | 40  | ms     |

| Device erase time <sup>2</sup>                 | t <sub>DERASE</sub>  | T <sub>AMB</sub> ≤ 85 °C  | —     | 60  | 74  | ms     |

|                                                |                      | T <sub>AMB</sub> ≤ 125 °C | _     | 60  | 78  | ms     |

| Page erase current <sup>3</sup>                | I <sub>ERASE</sub>   |                           | _     | —   | 3   | mA     |

| Mass or Device erase cur-<br>rent <sup>3</sup> |                      |                           | -     | —   | 5   | mA     |

| Write current <sup>3</sup>                     | I <sub>WRITE</sub>   |                           |       |     | 3   | mA     |

## Table 4.15. Flash Memory Characteristics<sup>1</sup>

Note:

1. Flash data retention information is published in the Quarterly Quality and Reliability Report.

2. Device erase is issued over the AAP interface and erases all flash, SRAM, the Lock Bit (LB) page, and the User data page Lock Word (ULW)

3. Measured at 25°C

| Parameter                                                                           | Symbol                   | Test Condition                                                                                    | Min | Тур  | Max | Unit |

|-------------------------------------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Settling time, (output settled                                                      | t <sub>IDAC_SETTLE</sub> | Range setting is changed                                                                          |     | 5    | _   | μs   |

| within 1% of steady state value)                                                    |                          | Step value is changed                                                                             | _   | 1    | _   | μs   |

| Current consumption in EM0 or EM1 <sup>2</sup>                                      | I <sub>IDAC</sub>        | Source mode, excluding output current                                                             | _   | 8.9  | 13  | μA   |

|                                                                                     |                          | Sink mode, excluding output cur-<br>rent                                                          | —   | 12   | 16  | μA   |

| Current consumption in EM2 or EM3 <sup>2</sup>                                      | -                        | Source mode, excluding output<br>current, duty cycle mode, T = 25<br>°C                           | _   | 1.04 | _   | μA   |

|                                                                                     |                          | Sink mode, excluding output cur-<br>rent, duty cycle mode, T = 25 °C                              | _   | 1.08 | _   | μA   |

|                                                                                     |                          | Source mode, excluding output<br>current, duty cycle mode, T ≥ 85<br>°C                           | _   | 8.9  | _   | μA   |

|                                                                                     |                          | Sink mode, excluding output current, duty cycle mode, $T \ge 85 \ ^{\circ}C$                      | _   | 12   | _   | μA   |

| Output voltage compliance in source mode, source current change relative to current |                          | RANGESEL1=0, output voltage =<br>min(V <sub>IOVDD</sub> , V <sub>AVDD</sub> <sup>2</sup> -100 mv) | _   | 0.04 | _   | %    |

| sourced at 0 V                                                                      |                          | RANGESEL1=1, output voltage = min(V <sub>IOVDD</sub> , V <sub>AVDD</sub> <sup>2</sup> -100 mV)    | _   | 0.02 | _   | %    |

|                                                                                     |                          | RANGESEL1=2, output voltage = min(V <sub>IOVDD</sub> , V <sub>AVDD</sub> <sup>2</sup> -150 mV)    | _   | 0.02 | _   | %    |

|                                                                                     |                          | RANGESEL1=3, output voltage =<br>min(V <sub>IOVDD</sub> , V <sub>AVDD</sub> <sup>2</sup> -250 mV) | _   | 0.02 | _   | %    |

| Output voltage compliance in sink mode, sink current                                | I <sub>COMP_SINK</sub>   | RANGESEL1=0, output voltage = 100 mV                                                              | _   | 0.18 | _   | %    |

| change relative to current sunk at IOVDD                                            |                          | RANGESEL1=1, output voltage = 100 mV                                                              | _   | 0.12 | _   | %    |

|                                                                                     |                          | RANGESEL1=2, output voltage = 150 mV                                                              | _   | 0.08 | -   | %    |

|                                                                                     |                          | RANGESEL1=3, output voltage = 250 mV                                                              | _   | 0.02 | -   | %    |

Note:

1. In IDAC\_CURPROG register

2. The IDAC is supplied by either AVDD, DVDD, or IOVDD based on the setting of ANASW in the EMU\_PWRCTRL register and PWRSEL in the IDAC\_CTRL register. Setting PWRSEL to 1 selects IOVDD. With PWRSEL cleared to 0, ANASW selects between AVDD (0) and DVDD (1).

| Parameter                               | Symbol                 | Test Condition                                             | Min | Тур  | Max  | Unit |

|-----------------------------------------|------------------------|------------------------------------------------------------|-----|------|------|------|

| Comparator delay <sup>4</sup>           | t <sub>ACMPDELAY</sub> | $BIASPROG^2 = 1$ , $FULLBIAS^2 = 0$                        | _   | 30   | _    | μs   |

|                                         |                        | $BIASPROG^{2} = 0x10, FULLBIAS^{2} = 0$                    | _   | 3.7  | _    | μs   |

|                                         |                        | BIASPROG <sup>2</sup> = 0x20, FULLBIAS <sup>2</sup><br>= 1 | _   | 35   | _    | ns   |

| Offset voltage                          | VACMPOFFSET            | BIASPROG <sup>2</sup> =0x10, FULLBIAS <sup>2</sup><br>= 1  | -35 | _    | 35   | mV   |

| Reference Voltage                       | V <sub>ACMPREF</sub>   | Internal 1.25 V reference                                  | 1   | 1.25 | 1.47 | V    |

|                                         |                        | Internal 2.5 V reference                                   | 2   | 2.5  | 2.8  | V    |

| Capacitive Sense Internal<br>Resistance | I R <sub>CSRES</sub>   | CSRESSEL <sup>5</sup> = 0                                  | _   | inf  | _    | kΩ   |

| Resistance                              |                        | CSRESSEL <sup>5</sup> = 1                                  |     | 15   | _    | kΩ   |

|                                         |                        | CSRESSEL <sup>5</sup> = 2                                  | _   | 27   | _    | kΩ   |

|                                         |                        | CSRESSEL <sup>5</sup> = 3                                  | _   | 39   | _    | kΩ   |

|                                         |                        | CSRESSEL <sup>5</sup> = 4                                  | _   | 51   | _    | kΩ   |

|                                         |                        | CSRESSEL <sup>5</sup> = 5                                  | _   | 102  | _    | kΩ   |

|                                         |                        | CSRESSEL <sup>5</sup> = 6                                  | _   | 164  | _    | kΩ   |

|                                         |                        | CSRESSEL <sup>5</sup> = 7                                  | _   | 239  | _    | kΩ   |

### Note:

1. ACMPVDD is a supply chosen by the setting in ACMPn\_CTRL\_PWRSEL and may be IOVDD, AVDD or DVDD

2. In ACMPn\_CTRL register

3. In ACMPn\_HYSTERESIS register

4.±100 mV differential drive

5. In ACMPn\_INPUTSEL register

The total ACMP current is the sum of the contributions from the ACMP and its internal voltage reference as given as:

### $I_{ACMPTOTAL} = I_{ACMP} + I_{ACMPREF}$

$\mathbf{I}_{\text{ACMPREF}}$  is zero if an external voltage reference is used.

## I2C Fast-mode (Fm)

| Parameter                                        | Symbol              | Test Condition | Min | Тур | Max | Unit |

|--------------------------------------------------|---------------------|----------------|-----|-----|-----|------|

| SCL clock frequency <sup>2</sup>                 | f <sub>SCL</sub>    |                | 0   | —   | 400 | kHz  |

| SCL clock low time                               | t <sub>LOW</sub>    |                | 1.3 | _   | _   | μs   |

| SCL clock high time                              | t <sub>HIGH</sub>   |                | 0.6 | _   | _   | μs   |

| SDA set-up time                                  | t <sub>SU,DAT</sub> |                | 100 | _   | _   | ns   |

| SDA hold time <sup>3</sup>                       | t <sub>HD,DAT</sub> |                | 100 | _   | 900 | ns   |

| Repeated START condition set-up time             | t <sub>SU,STA</sub> |                | 0.6 |     |     | μs   |

| (Repeated) START condition hold time             | t <sub>HD,STA</sub> |                | 0.6 |     |     | μs   |

| STOP condition set-up time                       | t <sub>SU,STO</sub> |                | 0.6 | _   | _   | μs   |

| Bus free time between a STOP and START condition | t <sub>BUF</sub>    |                | 1.3 | _   | _   | μs   |

## Table 4.22. I2C Fast-mode (Fm)<sup>1</sup>

#### Note:

1. For CLHR set to 1 in the I2Cn\_CTRL register

2. For the minimum HFPERCLK frequency required in Fast-mode, refer to the I2C chapter in the reference manual

3. The maximum SDA hold time (t<sub>HD,DAT</sub>) needs to be met only when the device does not stretch the low time of SCL (t<sub>LOW</sub>)

#### I2C Fast-mode Plus (Fm+)

| Parameter                                        | Symbol              | Test Condition | Min  | Тур | Max  | Unit |

|--------------------------------------------------|---------------------|----------------|------|-----|------|------|

| SCL clock frequency <sup>2</sup>                 | f <sub>SCL</sub>    |                | 0    | _   | 1000 | kHz  |

| SCL clock low time                               | t <sub>LOW</sub>    |                | 0.5  | _   |      | μs   |

| SCL clock high time                              | t <sub>HIGH</sub>   |                | 0.26 | _   | _    | μs   |

| SDA set-up time                                  | t <sub>SU,DAT</sub> |                | 50   | _   | _    | ns   |

| SDA hold time                                    | t <sub>HD,DAT</sub> |                | 100  | _   | _    | ns   |

| Repeated START condition set-up time             | t <sub>SU,STA</sub> |                | 0.26 | _   |      | μs   |

| (Repeated) START condition hold time             | t <sub>HD,STA</sub> |                | 0.26 | _   |      | μs   |

| STOP condition set-up time                       | t <sub>SU,STO</sub> |                | 0.26 | _   |      | μs   |

| Bus free time between a STOP and START condition | t <sub>BUF</sub>    |                | 0.5  | _   |      | μs   |

#### Note:

1. For CLHR set to 0 or 1 in the I2Cn\_CTRL register

2. For the minimum HFPERCLK frequency required in Fast-mode Plus, refer to the I2C chapter in the reference manual

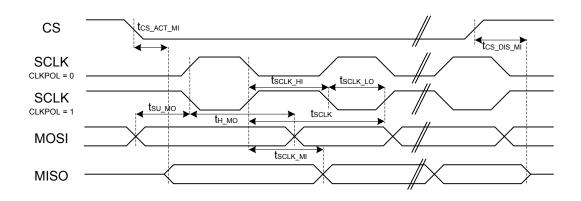

#### **SPI Slave Timing**

| Parameter                         | Symbol                 | Test Condition | Min                              | Тур | Max                               | Unit |

|-----------------------------------|------------------------|----------------|----------------------------------|-----|-----------------------------------|------|

| SCKL period <sup>1 2</sup>        | t <sub>SCLK_sl</sub>   |                | 2 *<br>t <sub>HFPERCLK</sub>     |     | -                                 | ns   |

| SCLK high period <sup>1 2</sup>   | t <sub>SCLK_hi</sub>   |                | 3 *<br>t <sub>HFPERCLK</sub>     | _   | -                                 | ns   |

| SCLK low period <sup>1 2</sup>    | t <sub>SCLK_lo</sub>   |                | 3 *<br>t <sub>HFPERCLK</sub>     |     | -                                 | ns   |

| CS active to MISO <sup>1 2</sup>  | t <sub>CS_ACT_MI</sub> |                | 4                                | —   | 50                                | ns   |

| CS disable to MISO <sup>1 2</sup> | t <sub>CS_DIS_MI</sub> |                | 4                                | _   | 50                                | ns   |

| MOSI setup time <sup>1 2</sup>    | t <sub>SU_MO</sub>     |                | 4                                | _   | _                                 | ns   |

| MOSI hold time <sup>1 2</sup>     | t <sub>H_MO</sub>      |                | 3 + 2 *<br>t <sub>HFPERCLK</sub> | _   | -                                 | ns   |

| SCLK to MISO <sup>1 2</sup>       | t <sub>SCLK_MI</sub>   |                | 16 +<br>t <sub>HFPERCLK</sub>    | _   | 66 + 2 *<br>t <sub>HFPERCLK</sub> | ns   |

### Table 4.25. SPI Slave Timing

#### Note:

1. Applies for both CLKPHA = 0 and CLKPHA = 1 (figure only shows CLKPHA = 0)

2. Measurement done with 8 pF output loading at 10% and 90% of  $V_{DD}$  (figure shows 50% of  $V_{DD}$ )

Figure 4.2. SPI Slave Timing Diagram

#### 4.2 Typical Performance Curves

Typical performance curves indicate typical characterized performance under the stated conditions.

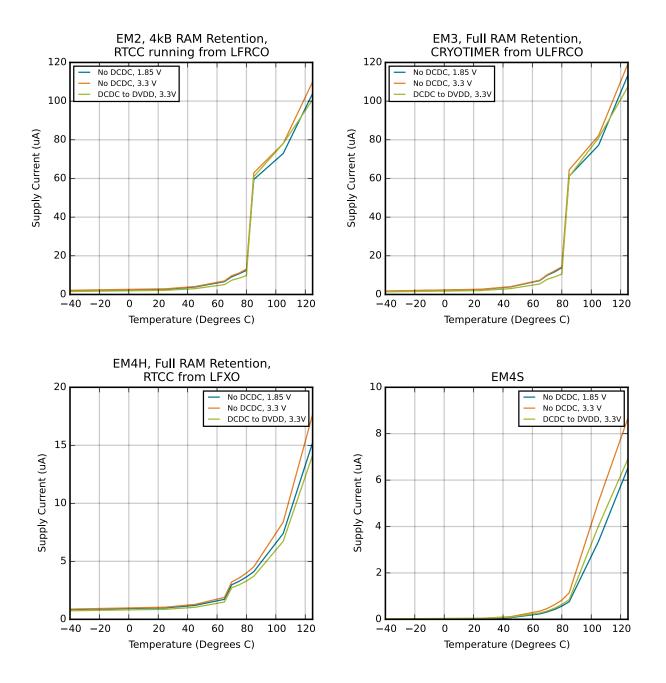

Figure 4.5. EM2, EM3, EM4H and EM4S Typical Supply Current

# 6. Pin Definitions

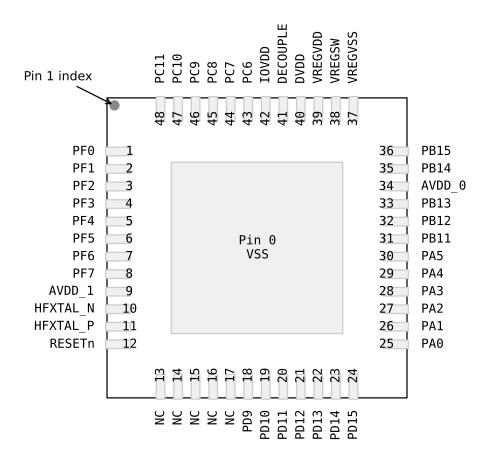

## 6.1 EFM32PG1 QFN48 with DC-DC Definition

Figure 6.1. EFM32PG1 QFN48 with DC-DC Pinout

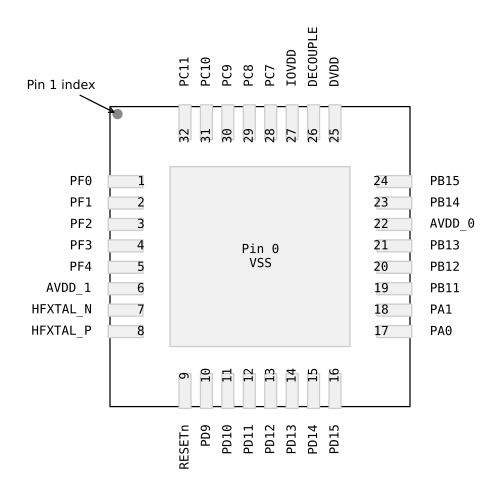

### 6.2 EFM32PG1 QFN32 without DC-DC Definition

Figure 6.2. EFM32PG1 QFN32 without DC-DC Pinout

| QFN      | 32 Pin# and Name | Name Pin Alternate Functionality / Description |                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                           |                                                                                                                       |  |

|----------|------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|

| Pin<br># | Pin Name         | Analog                                         | Timers                                                                                                                                                                                                                                                                | Communication                                                                                                                                                                                                             | Other                                                                                                                 |  |

| 30       | PC9              | BUSAY<br>BUSBX                                 | TIM0_CC0 #14<br>TIM0_CC1 #13<br>TIM0_CC2 #12<br>TIM0_CDTI0 #11<br>TIM0_CDTI1 #10<br>TIM0_CDTI2 #9<br>TIM1_CC0 #14<br>TIM1_CC1 #13<br>TIM1_CC2 #12<br>TIM1_CC3 #11 LE-<br>TIM0_OUT0 #14 LE-<br>TIM0_OUT1 #13<br>PCNT0_S0IN #14<br>PCNT0_S1IN #13                       | US0_TX #14 US0_RX<br>#13 US0_CLK #12<br>US0_CS #11 US0_CTS<br>#10 US0_RTS #9<br>US1_TX #14 US1_RX<br>#13 US1_CLK #12<br>US1_CS #11 US1_CTS<br>#10 US1_RTS #9<br>LEU0_TX #14 LEU0_RX<br>#13 I2C0_SDA #14<br>I2C0_SCL #13   | PRS_CH0 #11<br>PRS_CH9 #14<br>PRS_CH10 #3<br>PRS_CH11 #2<br>ACMP0_O #14<br>ACMP1_O #14                                |  |

| 31       | PC10             | BUSAX<br>BUSBY                                 | TIM0_CC0 #15<br>TIM0_CC1 #14<br>TIM0_CC2 #13<br>TIM0_CDTI0 #12<br>TIM0_CDTI1 #11<br>TIM0_CDT12 #10<br>TIM1_CC0 #15<br>TIM1_CC1 #14<br>TIM1_CC2 #13<br>TIM1_CC3 #12 LE-<br>TIM0_OUT0 #15 LE-<br>TIM0_OUT1 #14<br>PCNT0_S0IN #15<br>PCNT0_S1IN #14                      | US0_TX #15 US0_RX<br>#14 US0_CLK #13<br>US0_CS #12 US0_CTS<br>#11 US0_RTS #10<br>US1_TX #15 US1_RX<br>#14 US1_CLK #13<br>US1_CS #12 US1_CTS<br>#11 US1_RTS #10<br>LEU0_TX #15 LEU0_RX<br>#14 I2C0_SDA #15<br>I2C0_SCL #14 | CMU_CLK1 #3<br>PRS_CH0 #12<br>PRS_CH9 #15<br>PRS_CH10 #4<br>PRS_CH11 #3<br>ACMP0_O #15<br>ACMP1_O #15<br>GPIO_EM4WU12 |  |

| 32       | PC11             | BUSAY<br>BUSBX                                 | TIM0_CC0 #16<br>TIM0_CC1 #15<br>TIM0_CC2 #14<br>TIM0_CDTI0 #13<br>TIM0_CDTI1 #12<br>TIM0_CDTI2 #11<br>TIM1_CC0 #16<br>TIM1_CC1 #15<br>TIM1_CC2 #14<br>TIM1_CC3 #13 LE-<br>TIM0_OUT0 #16 LE-<br>TIM0_OUT0 #16 LE-<br>TIM0_OUT1 #15<br>PCNT0_S0IN #16<br>PCNT0_S1IN #15 | US0_TX #16 US0_RX<br>#15 US0_CLK #14<br>US0_CS #13 US0_CTS<br>#12 US0_RTS #11<br>US1_TX #16 US1_RX<br>#15 US1_CLK #14<br>US1_CS #13 US1_CTS<br>#12 US1_RTS #11<br>LEU0_TX #16 LEU0_RX<br>#15 I2C0_SDA #16<br>I2C0_SCL #15 | CMU_CLK0 #3<br>PRS_CH0 #13<br>PRS_CH9 #16<br>PRS_CH10 #5<br>PRS_CH11 #4<br>ACMP0_O #16<br>ACMP1_O #16<br>DBG_SWO #3   |  |

### EFM32PG1 Data Sheet Pin Definitions

| QFN      | 32 Pin# and Name |                           | Pin Alternate Funct                                                                                                                                                                                                                                                   | ionality / Description                                                                                                                                                                                                    |                                                                                                                       |

|----------|------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Pin<br># | Pin Name         | Analog                    | Timers                                                                                                                                                                                                                                                                | Communication                                                                                                                                                                                                             | Other                                                                                                                 |

| 25       | VREGVSS          | Voltage regulator VSS     |                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                           |                                                                                                                       |

| 26       | VREGSW           | DCDC regulator switching  | node                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                           |                                                                                                                       |

| 27       | VREGVDD          | Voltage regulator VDD inp | out                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                           |                                                                                                                       |

| 28       | DVDD             | Digital power supply.     |                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                           |                                                                                                                       |

| 29       | DECOUPLE         | Decouple output for on-ch | ip voltage regulator. An ext                                                                                                                                                                                                                                          | ternal decoupling capacitor                                                                                                                                                                                               | is required at this pin.                                                                                              |

| 30       | IOVDD            | Digital IO power supply.  |                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                           |                                                                                                                       |

| 31       | PC10             | BUSAX<br>BUSBY            | TIM0_CC0 #15<br>TIM0_CC1 #14<br>TIM0_CC2 #13<br>TIM0_CDTI0 #12<br>TIM0_CDTI1 #11<br>TIM0_CDTI2 #10<br>TIM1_CC0 #15<br>TIM1_CC1 #14<br>TIM1_CC2 #13<br>TIM1_CC3 #12 LE-<br>TIM0_OUT0 #15 LE-<br>TIM0_OUT0 #15 LE-<br>TIM0_OUT1 #14<br>PCNT0_S0IN #15<br>PCNT0_S1IN #14 | US0_TX #15 US0_RX<br>#14 US0_CLK #13<br>US0_CS #12 US0_CTS<br>#11 US0_RTS #10<br>US1_TX #15 US1_RX<br>#14 US1_CLK #13<br>US1_CS #12 US1_CTS<br>#11 US1_RTS #10<br>LEU0_TX #15 LEU0_RX<br>#14 I2C0_SDA #15<br>I2C0_SCL #14 | CMU_CLK1 #3<br>PRS_CH0 #12<br>PRS_CH9 #15<br>PRS_CH10 #4<br>PRS_CH11 #3<br>ACMP0_O #15<br>ACMP1_O #15<br>GPIO_EM4WU12 |

| 32       | PC11             | BUSAY<br>BUSBX            | TIM0_CC0 #16<br>TIM0_CC1 #15<br>TIM0_CC2 #14<br>TIM0_CDTI0 #13<br>TIM0_CDTI1 #12<br>TIM0_CDTI2 #11<br>TIM1_CC0 #16<br>TIM1_CC1 #15<br>TIM1_CC2 #14<br>TIM1_CC3 #13 LE-<br>TIM0_OUT0 #16 LE-<br>TIM0_OUT0 #16 LE-<br>TIM0_OUT1 #15<br>PCNT0_S0IN #16<br>PCNT0_S1IN #15 | US0_TX #16 US0_RX<br>#15 US0_CLK #14<br>US0_CS #13 US0_CTS<br>#12 US0_RTS #11<br>US1_TX #16 US1_RX<br>#15 US1_CLK #14<br>US1_CS #13 US1_CTS<br>#12 US1_RTS #11<br>LEU0_TX #16 LEU0_RX<br>#15 I2C0_SDA #16<br>I2C0_SCL #15 | CMU_CLK0 #3<br>PRS_CH0 #13<br>PRS_CH9 #16<br>PRS_CH10 #5<br>PRS_CH11 #4<br>ACMP0_O #16<br>ACMP1_O #16<br>DBG_SWO #3   |

| Alternate     |                                      |                                         |                                           |                                            |                                             |                                              |                                          |                                          |                                                                                                                                     |

|---------------|--------------------------------------|-----------------------------------------|-------------------------------------------|--------------------------------------------|---------------------------------------------|----------------------------------------------|------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Functionality | 0 - 3                                | 4 - 7                                   | 8 - 11                                    | 12 - 15                                    | 16 - 19                                     | 20 - 23                                      | 24 - 27                                  | 28 - 31                                  | Description                                                                                                                         |

| GPIO_EM4WU12  | 0: PC10                              |                                         |                                           |                                            |                                             |                                              |                                          |                                          | Pin can be used to<br>wake the system<br>up from EM4                                                                                |

| I2C0_SCL      | 0: PA1<br>1: PA2<br>2: PA3<br>3: PA4 | 4: PA5<br>5: PB11<br>6: PB12<br>7: PB13 | 8: PB14<br>9: PB15<br>10: PC6<br>11: PC7  | 12: PC8<br>13: PC9<br>14: PC10<br>15: PC11 | 16: PD9<br>17: PD10<br>18: PD11<br>19: PD12 | 20: PD13<br>21: PD14<br>22: PD15<br>23: PF0  | 24: PF1<br>25: PF2<br>26: PF3<br>27: PF4 | 28: PF5<br>29: PF6<br>30: PF7<br>31: PA0 | I2C0 Serial Clock<br>Line input / output.                                                                                           |

| I2C0_SDA      | 0: PA0<br>1: PA1<br>2: PA2<br>3: PA3 | 4: PA4<br>5: PA5<br>6: PB11<br>7: PB12  | 8: PB13<br>9: PB14<br>10: PB15<br>11: PC6 | 12: PC7<br>13: PC8<br>14: PC9<br>15: PC10  | 16: PC11<br>17: PD9<br>18: PD10<br>19: PD11 | 20: PD12<br>21: PD13<br>22: PD14<br>23: PD15 | 24: PF0<br>25: PF1<br>26: PF2<br>27: PF3 | 28: PF4<br>29: PF5<br>30: PF6<br>31: PF7 | I2C0 Serial Data in-<br>put / output.                                                                                               |

| LETIM0_OUT0   | 0: PA0<br>1: PA1<br>2: PA2<br>3: PA3 | 4: PA4<br>5: PA5<br>6: PB11<br>7: PB12  | 8: PB13<br>9: PB14<br>10: PB15<br>11: PC6 | 12: PC7<br>13: PC8<br>14: PC9<br>15: PC10  | 16: PC11<br>17: PD9<br>18: PD10<br>19: PD11 | 20: PD12<br>21: PD13<br>22: PD14<br>23: PD15 | 24: PF0<br>25: PF1<br>26: PF2<br>27: PF3 | 28: PF4<br>29: PF5<br>30: PF6<br>31: PF7 | Low Energy Timer<br>LETIM0, output<br>channel 0.                                                                                    |

| LETIM0_OUT1   | 0: PA1<br>1: PA2<br>2: PA3<br>3: PA4 | 4: PA5<br>5: PB11<br>6: PB12<br>7: PB13 | 8: PB14<br>9: PB15<br>10: PC6<br>11: PC7  | 12: PC8<br>13: PC9<br>14: PC10<br>15: PC11 | 16: PD9<br>17: PD10<br>18: PD11<br>19: PD12 | 20: PD13<br>21: PD14<br>22: PD15<br>23: PF0  | 24: PF1<br>25: PF2<br>26: PF3<br>27: PF4 | 28: PF5<br>29: PF6<br>30: PF7<br>31: PA0 | Low Energy Timer<br>LETIM0, output<br>channel 1.                                                                                    |

| LEU0_RX       | 0: PA1<br>1: PA2<br>2: PA3<br>3: PA4 | 4: PA5<br>5: PB11<br>6: PB12<br>7: PB13 | 8: PB14<br>9: PB15<br>10: PC6<br>11: PC7  | 12: PC8<br>13: PC9<br>14: PC10<br>15: PC11 | 16: PD9<br>17: PD10<br>18: PD11<br>19: PD12 | 20: PD13<br>21: PD14<br>22: PD15<br>23: PF0  | 24: PF1<br>25: PF2<br>26: PF3<br>27: PF4 | 28: PF5<br>29: PF6<br>30: PF7<br>31: PA0 | LEUART0 Receive input.                                                                                                              |

| LEU0_TX       | 0: PA0<br>1: PA1<br>2: PA2<br>3: PA3 | 4: PA4<br>5: PA5<br>6: PB11<br>7: PB12  | 8: PB13<br>9: PB14<br>10: PB15<br>11: PC6 | 12: PC7<br>13: PC8<br>14: PC9<br>15: PC10  | 16: PC11<br>17: PD9<br>18: PD10<br>19: PD11 | 20: PD12<br>21: PD13<br>22: PD14<br>23: PD15 | 24: PF0<br>25: PF1<br>26: PF2<br>27: PF3 | 28: PF4<br>29: PF5<br>30: PF6<br>31: PF7 | LEUART0 Transmit<br>output. Also used<br>as receive input in<br>half duplex commu-<br>nication.                                     |

| LFXTAL_N      | 0: PB14                              |                                         |                                           |                                            |                                             |                                              |                                          |                                          | Low Frequency<br>Crystal (typically<br>32.768 kHz) nega-<br>tive pin. Also used<br>as an optional ex-<br>ternal clock input<br>pin. |

| LFXTAL_P      | 0: PB15                              |                                         |                                           |                                            |                                             |                                              |                                          |                                          | Low Frequency<br>Crystal (typically<br>32.768 kHz) posi-<br>tive pin.                                                               |

| PCNT0_S0IN    | 0: PA0<br>1: PA1<br>2: PA2<br>3: PA3 | 4: PA4<br>5: PA5<br>6: PB11<br>7: PB12  | 8: PB13<br>9: PB14<br>10: PB15<br>11: PC6 | 12: PC7<br>13: PC8<br>14: PC9<br>15: PC10  | 16: PC11<br>17: PD9<br>18: PD10<br>19: PD11 | 20: PD12<br>21: PD13<br>22: PD14<br>23: PD15 | 24: PF0<br>25: PF1<br>26: PF2<br>27: PF3 | 28: PF4<br>29: PF5<br>30: PF6<br>31: PF7 | Pulse Counter<br>PCNT0 input num-<br>ber 0.                                                                                         |

| PCNT0_S1IN    | 0: PA1<br>1: PA2<br>2: PA3<br>3: PA4 | 4: PA5<br>5: PB11<br>6: PB12<br>7: PB13 | 8: PB14<br>9: PB15<br>10: PC6<br>11: PC7  | 12: PC8<br>13: PC9<br>14: PC10<br>15: PC11 | 16: PD9<br>17: PD10<br>18: PD11<br>19: PD12 | 20: PD13<br>21: PD14<br>22: PD15<br>23: PF0  | 24: PF1<br>25: PF2<br>26: PF3<br>27: PF4 | 28: PF5<br>29: PF6<br>30: PF7<br>31: PA0 | Pulse Counter<br>PCNT0 input num-<br>ber 1.                                                                                         |

| PRS_CH0       | 0: PF0<br>1: PF1<br>2: PF2<br>3: PF3 | 4: PF4<br>5: PF5<br>6: PF6<br>7: PF7    | 8: PC6<br>9: PC7<br>10: PC8<br>11: PC9    | 12: PC10<br>13: PC11                       |                                             |                                              |                                          |                                          | Peripheral Reflex<br>System PRS, chan-<br>nel 0.                                                                                    |

| Alternate     |                                         | LOCATION                                 |                                           |                                             |                                              |                                              |                                          |                                          |                                                                                                                                                                                    |  |  |  |  |  |

|---------------|-----------------------------------------|------------------------------------------|-------------------------------------------|---------------------------------------------|----------------------------------------------|----------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Functionality | 0 - 3                                   | 4 - 7                                    | 8 - 11                                    | 12 - 15                                     | 16 - 19                                      | 20 - 23                                      | 24 - 27                                  | 28 - 31                                  | Description                                                                                                                                                                        |  |  |  |  |  |

| US0_RX        | 0: PA1<br>1: PA2<br>2: PA3<br>3: PA4    | 4: PA5<br>5: PB11<br>6: PB12<br>7: PB13  | 8: PB14<br>9: PB15<br>10: PC6<br>11: PC7  | 12: PC8<br>13: PC9<br>14: PC10<br>15: PC11  | 16: PD9<br>17: PD10<br>18: PD11<br>19: PD12  | 20: PD13<br>21: PD14<br>22: PD15<br>23: PF0  | 24: PF1<br>25: PF2<br>26: PF3<br>27: PF4 | 28: PF5<br>29: PF6<br>30: PF7<br>31: PA0 | USART0 Asynchro-<br>nous Receive.<br>USART0 Synchro-<br>nous mode Master<br>Input / Slave Out-<br>put (MISO).                                                                      |  |  |  |  |  |

| US0_TX        | 0: PA0<br>1: PA1<br>2: PA2<br>3: PA3    | 4: PA4<br>5: PA5<br>6: PB11<br>7: PB12   | 8: PB13<br>9: PB14<br>10: PB15<br>11: PC6 | 12: PC7<br>13: PC8<br>14: PC9<br>15: PC10   | 16: PC11<br>17: PD9<br>18: PD10<br>19: PD11  | 20: PD12<br>21: PD13<br>22: PD14<br>23: PD15 | 24: PF0<br>25: PF1<br>26: PF2<br>27: PF3 | 28: PF4<br>29: PF5<br>30: PF6<br>31: PF7 | USART0 Asynchro-<br>nous Transmit. Al-<br>so used as receive<br>input in half duplex<br>communication.<br>USART0 Synchro-<br>nous mode Master<br>Output / Slave In-<br>put (MOSI). |  |  |  |  |  |

| US1_CLK       | 0: PA2<br>1: PA3<br>2: PA4<br>3: PA5    | 4: PB11<br>5: PB12<br>6: PB13<br>7: PB14 | 8: PB15<br>9: PC6<br>10: PC7<br>11: PC8   | 12: PC9<br>13: PC10<br>14: PC11<br>15: PD9  | 16: PD10<br>17: PD11<br>18: PD12<br>19: PD13 | 20: PD14<br>21: PD15<br>22: PF0<br>23: PF1   | 24: PF2<br>25: PF3<br>26: PF4<br>27: PF5 | 28: PF6<br>29: PF7<br>30: PA0<br>31: PA1 | USART1 clock in-<br>put / output.                                                                                                                                                  |  |  |  |  |  |

| US1_CS        | 0: PA3<br>1: PA4<br>2: PA5<br>3: PB11   | 4: PB12<br>5: PB13<br>6: PB14<br>7: PB15 | 8: PC6<br>9: PC7<br>10: PC8<br>11: PC9    | 12: PC10<br>13: PC11<br>14: PD9<br>15: PD10 | 16: PD11<br>17: PD12<br>18: PD13<br>19: PD14 | 20: PD15<br>21: PF0<br>22: PF1<br>23: PF2    | 24: PF3<br>25: PF4<br>26: PF5<br>27: PF6 | 28: PF7<br>29: PA0<br>30: PA1<br>31: PA2 | USART1 chip se-<br>lect input / output.                                                                                                                                            |  |  |  |  |  |

| US1_CTS       | 0: PA4<br>1: PA5<br>2: PB11<br>3: PB12  | 4: PB13<br>5: PB14<br>6: PB15<br>7: PC6  | 8: PC7<br>9: PC8<br>10: PC9<br>11: PC10   | 12: PC11<br>13: PD9<br>14: PD10<br>15: PD11 | 16: PD12<br>17: PD13<br>18: PD14<br>19: PD15 | 20: PF0<br>21: PF1<br>22: PF2<br>23: PF3     | 24: PF4<br>25: PF5<br>26: PF6<br>27: PF7 | 28: PA0<br>29: PA1<br>30: PA2<br>31: PA3 | USART1 Clear To<br>Send hardware<br>flow control input.                                                                                                                            |  |  |  |  |  |

| US1_RTS       | 0: PA5<br>1: PB11<br>2: PB12<br>3: PB13 | 4: PB14<br>5: PB15<br>6: PC6<br>7: PC7   | 8: PC8<br>9: PC9<br>10: PC10<br>11: PC11  | 12: PD9<br>13: PD10<br>14: PD11<br>15: PD12 | 16: PD13<br>17: PD14<br>18: PD15<br>19: PF0  | 20: PF1<br>21: PF2<br>22: PF3<br>23: PF4     | 24: PF5<br>25: PF6<br>26: PF7<br>27: PA0 | 28: PA1<br>29: PA2<br>30: PA3<br>31: PA4 | USART1 Request<br>To Send hardware<br>flow control output.                                                                                                                         |  |  |  |  |  |

| US1_RX        | 0: PA1<br>1: PA2<br>2: PA3<br>3: PA4    | 4: PA5<br>5: PB11<br>6: PB12<br>7: PB13  | 8: PB14<br>9: PB15<br>10: PC6<br>11: PC7  | 12: PC8<br>13: PC9<br>14: PC10<br>15: PC11  | 16: PD9<br>17: PD10<br>18: PD11<br>19: PD12  | 20: PD13<br>21: PD14<br>22: PD15<br>23: PF0  | 24: PF1<br>25: PF2<br>26: PF3<br>27: PF4 | 28: PF5<br>29: PF6<br>30: PF7<br>31: PA0 | USART1 Asynchro-<br>nous Receive.<br>USART1 Synchro-<br>nous mode Master<br>Input / Slave Out-<br>put (MISO).                                                                      |  |  |  |  |  |

| US1_TX        | 0: PA0<br>1: PA1<br>2: PA2<br>3: PA3    | 4: PA4<br>5: PA5<br>6: PB11<br>7: PB12   | 8: PB13<br>9: PB14<br>10: PB15<br>11: PC6 | 12: PC7<br>13: PC8<br>14: PC9<br>15: PC10   | 16: PC11<br>17: PD9<br>18: PD10<br>19: PD11  | 20: PD12<br>21: PD13<br>22: PD14<br>23: PD15 | 24: PF0<br>25: PF1<br>26: PF2<br>27: PF3 | 28: PF4<br>29: PF5<br>30: PF6<br>31: PF7 | USART1 Asynchro-<br>nous Transmit. Al-<br>so used as receive<br>input in half duplex<br>communication.<br>USART1 Synchro-<br>nous mode Master<br>Output / Slave In-<br>put (MOSI). |  |  |  |  |  |

| Port    | Bus   | CH31 | CH30 | CH29 | CH28 | CH27 | CH26 | CH25 | CH24 | CH23 | CH22 | CH21 | CH20 | CH19 | CH18 | CH17 | CH16 | CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | 6НЭ | CH8 | CH7  | CH6  | CH5  | CH4  | CH3  | CH2  | CH1 | CH0 |

|---------|-------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|------|------|------|------|------|------|-----|-----|

| APORT1X | BUSAX |      |      |      |      |      |      |      |      |      | PF6  |      | PF4  |      | PF2  |      | PF0  |      |      |      |      |      | PC10 |     | PC8 |      | PC6  |      |      |      |      |     |     |

| APORT1Y | BUSAY |      |      |      |      |      |      |      |      | PF7  |      | PF5  |      | PF3  |      | PF1  |      |      |      |      |      | PC11 |      | PC9 |     | PC7  |      |      |      |      |      |     |     |

| APORT2X | BUSBX |      |      |      |      |      |      |      |      | PF7  |      | PF5  |      | PF3  |      | PF1  |      |      |      |      |      | PC11 |      | 60d |     | PC7  |      |      |      |      |      |     |     |

| APORT2Y | BUSBY |      |      |      |      |      |      |      |      |      | PF6  |      | PF4  |      | PF2  |      | PF0  |      |      |      |      |      | PC10 |     | PC8 |      | PC6  |      |      |      |      |     |     |

| APORT3X | BUSCX |      | PB14 |      | PB12 |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      | PA4  |      | PA2  |     | PA0 |      | PD14 |      | PD12 |      | PD10 |     |     |

| APORT3Y | BUSCY | PB15 |      | PB13 |      | PB11 |      |      |      |      |      |      |      |      |      |      |      |      |      | PA5  |      | PA3  |      | PA1 |     | PD15 |      | PD13 |      | PD11 |      | PD9 |     |

| APORT4X | BUSDX | PB15 |      | PB13 |      | PB11 |      |      |      |      |      |      |      |      |      |      |      |      |      | PA5  |      | PA3  |      | PA1 |     | PD15 |      | PD13 |      | PD11 |      | PD9 |     |

| APORT4Y | BUSDY |      | PB14 |      | PB12 |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      | PA4  |      | PA2  |     | PA0 |      | PD14 |      | PD12 |      | PD10 |     |     |

# Table 6.9. ACMP1 Bus and Pin Mapping

## 7. QFN48 Package Specifications

### 7.1 QFN48 Package Dimensions

Figure 7.1. QFN48 Package Drawing

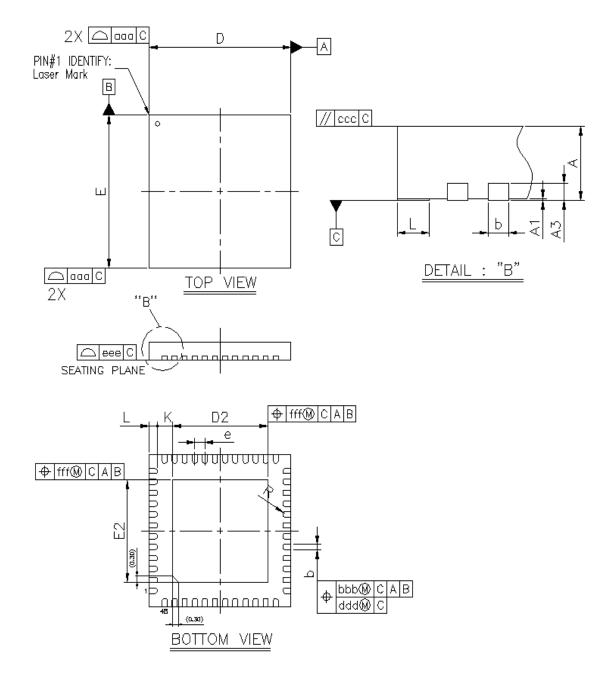

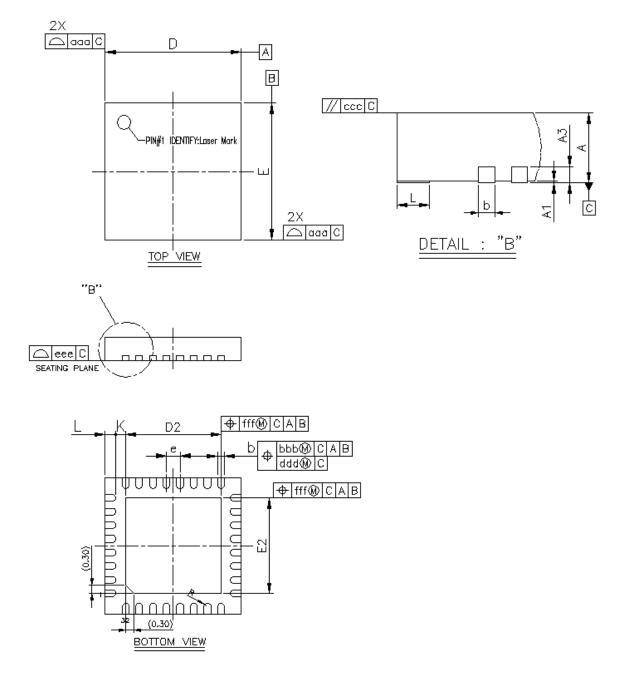

## 8. QFN32 Package Specifications

### 8.1 QFN32 Package Dimensions

Figure 8.1. QFN32 Package Drawing

### 9.7 Revision 0.1

Initial release.

### **Simplicity Studio**

One-click access to MCU and wireless tools, documentation, software, source code libraries & more. Available for Windows, Mac and Linux!

Supp

Support and Community community.silabs.com

#### Disclaimer

Silicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Labs shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs products be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga Logo®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress® and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

# http://www.silabs.com