Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | ARM® Cortex®-M4                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 20                                                                        |

| Program Memory Size        | 128KB (128K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 32K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.85V ~ 3.8V                                                              |

| Data Converters            | A/D 20x12b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 32-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 32-QFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32pg1b200f128gm32-c0 |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.6.3 Inter-Integrated Circuit Interface (I<sup>2</sup>C)

The I<sup>2</sup>C module provides an interface between the MCU and a serial I<sup>2</sup>C bus. It is capable of acting as both a master and a slave and supports multi-master buses. Standard-mode, fast-mode and fast-mode plus speeds are supported, allowing transmission rates from 10 kbit/s up to 1 Mbit/s. Slave arbitration and timeouts are also available, allowing implementation of an SMBus-compliant system. The interface provided to software by the I<sup>2</sup>C module allows precise timing control of the transmission process and highly automated transfers. Automatic recognition of slave addresses is provided in active and low energy modes.

### 3.6.4 Peripheral Reflex System (PRS)

The Peripheral Reflex System provides a communication network between different peripheral modules without software involvement. Peripheral modules producing Reflex signals are called producers. The PRS routes Reflex signals from producers to consumer peripherals which in turn perform actions in response. Edge triggers and other functionality can be applied by the PRS. The PRS allows peripheral to act autonomously without waking the MCU core, saving power.

#### 3.7 Security Features

#### 3.7.1 GPCRC (General Purpose Cyclic Redundancy Check)

The GPCRC module implements a Cyclic Redundancy Check (CRC) function. It supports both 32-bit and 16-bit polynomials. The supported 32-bit polynomial is 0x04C11DB7 (IEEE 802.3), while the 16-bit polynomial can be programmed to any value, depending on the needs of the application.

### 3.7.2 Crypto Accelerator (CRYPTO)

The Crypto Accelerator is a fast and energy-efficient autonomous hardware encryption and decryption accelerator. EFM32PG1 devices support AES encryption and decryption with 128- or 256-bit keys, ECC over both GF(P) and GF(2<sup>m</sup>), and SHA-1 and SHA-2 (SHA-224 and SHA-256).

Supported block cipher modes of operation for AES include: ECB, CTR, CBC, PCBC, CFB, OFB, GCM, CBC-MAC, GMAC and CCM.

Supported ECC NIST recommended curves include P-192, P-224, P-256, K-163, K-233, B-163 and B-233.

The CRYPTO module allows fast processing of GCM (AES), ECC and SHA with little CPU intervention. CRYPTO also provides trigger signals for DMA read and write operations.

#### 3.8 Analog

#### 3.8.1 Analog Port (APORT)

The Analog Port (APORT) is an analog interconnect matrix allowing access to many analog modules on a flexible selection of pins. Each APORT bus consists of analog switches connected to a common wire. Since many clients can operate differentially, buses are grouped by X/Y pairs.

#### 3.8.2 Analog Comparator (ACMP)

The Analog Comparator is used to compare the voltage of two analog inputs, with a digital output indicating which input voltage is higher. Inputs are selected from among internal references and external pins. The tradeoff between response time and current consumption is configurable by software. Two 6-bit reference dividers allow for a wide range of internally-programmable reference sources. The ACMP can also be used to monitor the supply voltage. An interrupt can be generated when the supply falls below or rises above the programmable threshold.

#### 3.8.3 Analog to Digital Converter (ADC)

The ADC is a Successive Approximation Register (SAR) architecture, with a resolution of up to 12 bits at up to 1 Msps. The output sample resolution is configurable and additional resolution is possible using integrated hardware for averaging over multiple samples. The ADC includes integrated voltage references and an integrated temperature sensor. Inputs are selectable from a wide range of sources, including pins configurable as either single-ended or differential.

#### 4.1.5.2 Current Consumption 3.3 V using DC-DC Converter

Unless otherwise indicated, typical conditions are: VREGVDD = AVDD = IOVDD = 3.3 V, DVDD = 1.8 V DC-DC output.  $T_{OP}$  = 25 °C. Minimum and maximum values in this table represent the worst conditions across supply voltage and process variation at  $T_{OP}$  = 25 °C. See Figure 5.2 EFM32PG1 Typical Application Circuit Using the DC-DC Converter on page 47.

| Parameter                                                  | Symbol              | Test Condition                                                   | Min | Тур  | Max | Unit   |

|------------------------------------------------------------|---------------------|------------------------------------------------------------------|-----|------|-----|--------|

| Current consumption in EM0<br>Active mode with all periph- | I <sub>ACTIVE</sub> | 38.4 MHz crystal, CPU running while loop from flash <sup>2</sup> | _   | 86   | _   | µA/MHz |

| erals disabled, DCDC in Low Noise DCM mode <sup>1</sup> .  |                     | 38 MHz HFRCO, CPU running<br>Prime from flash                    | _   | 63   | _   | µA/MHz |

|                                                            |                     | 38 MHz HFRCO, CPU running while loop from flash                  | _   | 71   | _   | µA/MHz |

|                                                            |                     | 38 MHz HFRCO, CPU running<br>CoreMark from flash                 | _   | 78   | _   | µA/MHz |

|                                                            |                     | 26 MHz HFRCO, CPU running while loop from flash                  | _   | 76   | _   | µA/MHz |

| Current consumption in EM0<br>Active mode with all periph- | -                   | 38.4 MHz crystal, CPU running while loop from flash <sup>2</sup> | _   | 96   | _   | µA/MHz |

| erals disabled, DCDC in Low Noise CCM mode <sup>3</sup> .  |                     | 38 MHz HFRCO, CPU running<br>Prime from flash                    | _   | 75   | _   | µA/MHz |

|                                                            |                     | 38 MHz HFRCO, CPU running while loop from flash                  | _   | 81   |     | µA/MHz |

|                                                            |                     | 38 MHz HFRCO, CPU running<br>CoreMark from flash                 | _   | 88   | _   | µA/MHz |

|                                                            |                     | 26 MHz HFRCO, CPU running while loop from flash                  | _   | 94   | _   | µA/MHz |

| Current consumption in EM1                                 | I <sub>EM1</sub>    | 38.4 MHz crystal <sup>2</sup>                                    | _   | 47   | _   | µA/MHz |

| Sleep mode with all peripher-<br>als disabled, DCDC in Low |                     | 38 MHz HFRCO                                                     | _   | 32   | _   | µA/MHz |

| Noise DCM mode <sup>1</sup> .                              |                     | 26 MHz HFRCO                                                     | _   | 38   | _   | µA/MHz |

| Current consumption in EM1                                 |                     | 38.4 MHz crystal <sup>2</sup>                                    | _   | 59   | _   | µA/MHz |

| Sleep mode with all peripher-<br>als disabled, DCDC in Low |                     | 38 MHz HFRCO                                                     | _   | 45   | _   | µA/MHz |

| Noise CCM mode <sup>3</sup> .                              |                     | 26 MHz HFRCO                                                     | _   | 58   | _   | µA/MHz |

| Current consumption in EM2<br>Deep Sleep mode. DCDC in     | I <sub>EM2</sub>    | Full RAM retention and RTCC running from LFXO                    | _   | 2.5  | _   | μA     |

| Low Power mode <sup>4</sup> .                              |                     | 4 kB RAM retention and RTCC running from LFRCO                   | _   | 2.2  | _   | μA     |

| Current consumption in EM3<br>Stop mode                    | I <sub>EM3</sub>    | Full RAM retention and CRYO-<br>TIMER running from ULFRCO        | _   | 2.1  | _   | μA     |

| Current consumption in EM4H Hibernate mode                 | I <sub>EM4</sub>    | 128 byte RAM retention, RTCC running from LFXO                   | _   | 0.86 | _   | μA     |

|                                                            |                     | 128 byte RAM retention, CRYO-<br>TIMER running from ULFRCO       | _   | 0.58 | _   | μA     |

|                                                            |                     | 128 byte RAM retention, no RTCC                                  | _   | 0.58 |     | μA     |

## Table 4.6. Current Consumption 3.3V with DC-DC

## EFM32PG1 Data Sheet Electrical Specifications

| Parameter                  | Symbol      | Test Condition             | Min              | Тур  | Мах | Unit |

|----------------------------|-------------|----------------------------|------------------|------|-----|------|

| Note:                      |             |                            |                  |      |     |      |

| 1. PSRR is referenced to A | VDD when AN | IASW=0 and to DVDD when AN | ASW=1 in EMU_PWR | CTRL |     |      |

| 2. In ADCn_CNTL register   |             |                            |                  |      |     |      |

| 3. In ADCn_BIASPROG reg    | gister      |                            |                  |      |     |      |

| 4. Derived from ADCCLK     |             |                            |                  |      |     |      |

|                            |             |                            |                  |      |     |      |

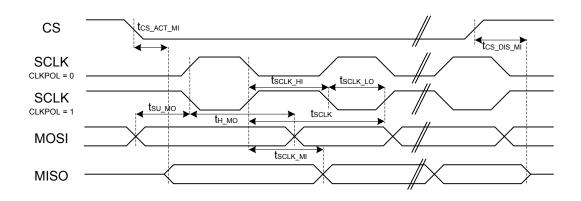

### **SPI Slave Timing**

| Parameter                         | Symbol                 | Test Condition | Min                              | Тур | Max                               | Unit |

|-----------------------------------|------------------------|----------------|----------------------------------|-----|-----------------------------------|------|

| SCKL period <sup>1 2</sup>        | t <sub>SCLK_sl</sub>   |                | 2 *<br>t <sub>HFPERCLK</sub>     |     | -                                 | ns   |

| SCLK high period <sup>1 2</sup>   | t <sub>SCLK_hi</sub>   |                | 3 *<br>t <sub>HFPERCLK</sub>     | _   | -                                 | ns   |

| SCLK low period <sup>1 2</sup>    | t <sub>SCLK_lo</sub>   |                | 3 *<br>t <sub>HFPERCLK</sub>     |     | -                                 | ns   |

| CS active to MISO <sup>1 2</sup>  | t <sub>CS_ACT_MI</sub> |                | 4                                | —   | 50                                | ns   |

| CS disable to MISO <sup>1 2</sup> | t <sub>CS_DIS_MI</sub> |                | 4                                | _   | 50                                | ns   |

| MOSI setup time <sup>1 2</sup>    | t <sub>SU_MO</sub>     |                | 4                                | _   | _                                 | ns   |

| MOSI hold time <sup>1 2</sup>     | t <sub>H_MO</sub>      |                | 3 + 2 *<br>t <sub>HFPERCLK</sub> | _   | -                                 | ns   |

| SCLK to MISO <sup>1 2</sup>       | t <sub>SCLK_MI</sub>   |                | 16 +<br>t <sub>HFPERCLK</sub>    | _   | 66 + 2 *<br>t <sub>HFPERCLK</sub> | ns   |

## Table 4.25. SPI Slave Timing

## Note:

1. Applies for both CLKPHA = 0 and CLKPHA = 1 (figure only shows CLKPHA = 0)

2. Measurement done with 8 pF output loading at 10% and 90% of  $V_{DD}$  (figure shows 50% of  $V_{DD}$ )

Figure 4.2. SPI Slave Timing Diagram

## 4.2 Typical Performance Curves

Typical performance curves indicate typical characterized performance under the stated conditions.

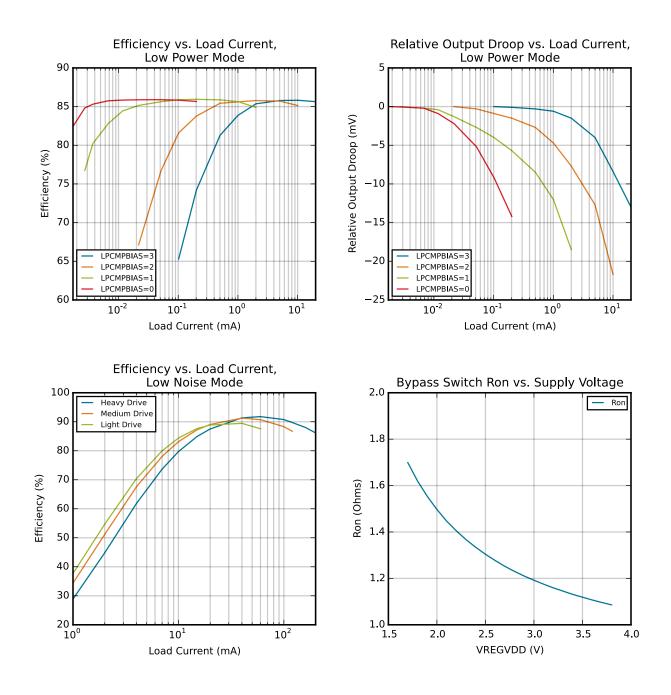

## 4.2.2 DC-DC Converter

Default test conditions: CCM mode, LDCDC = 4.7 µH, CDCDC = 1.0 µF, VDCDC\_I = 3.3 V, VDCDC\_O = 1.8 V, FDCDC\_LN = 7 MHz

Figure 4.6. DC-DC Converter Typical Performance Characteristics

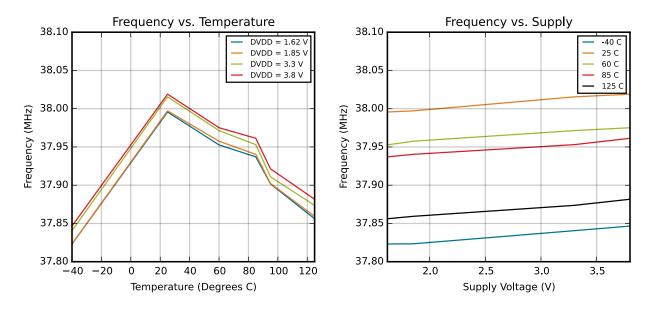

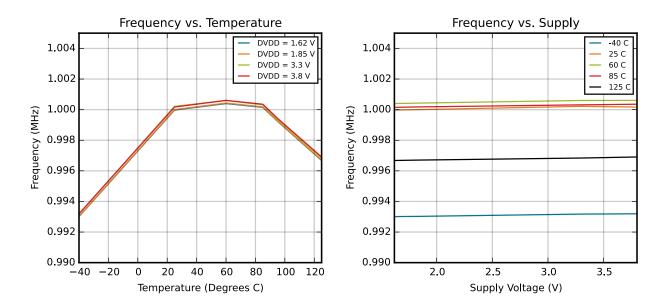

## 4.2.3 Internal Oscillators

Figure 4.8. HFRCO and AUXHFRCO Typical Performance at 38 MHz

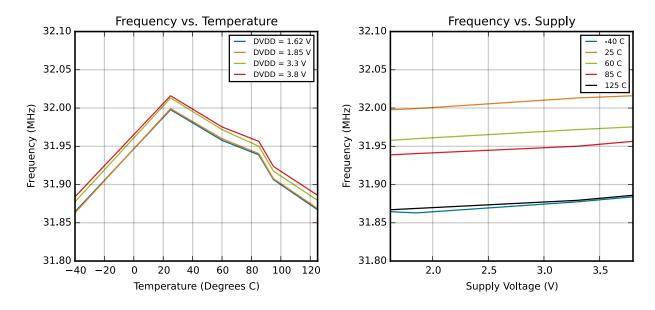

Figure 4.9. HFRCO and AUXHFRCO Typical Performance at 32 MHz

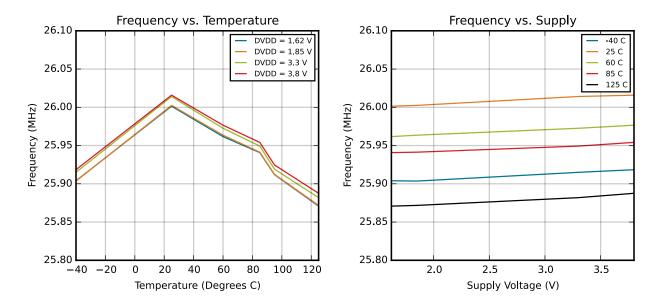

Figure 4.10. HFRCO and AUXHFRCO Typical Performance at 26 MHz

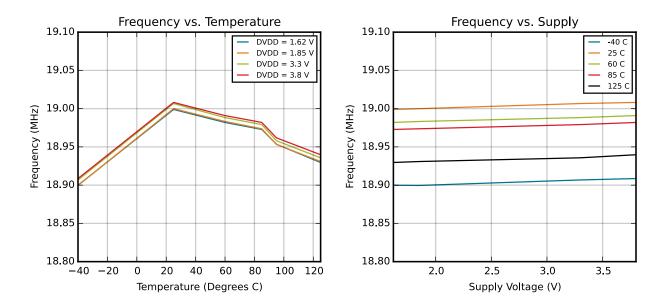

Figure 4.11. HFRCO and AUXHFRCO Typical Performance at 19 MHz

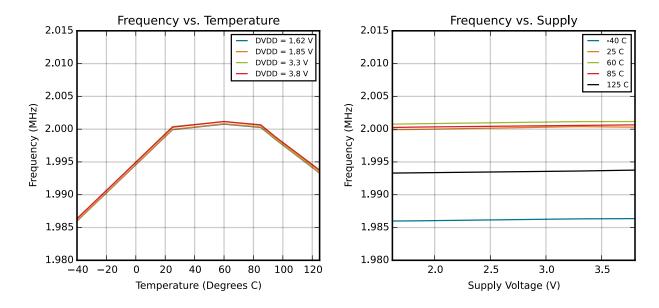

Figure 4.16. HFRCO and AUXHFRCO Typical Performance at 2 MHz

Figure 4.17. HFRCO and AUXHFRCO Typical Performance at 1 MHz

# 5. Typical Connection Diagrams

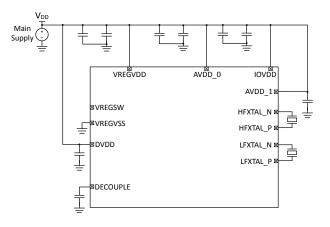

# 5.1 Power

Typical power supply connections for direct supply, without using the internal dc-dc converter, are shown in Figure 5.1 EFM32PG1 Typical Application Circuit, Direct Supply, No DC-DC Converter on page 47.

Figure 5.1. EFM32PG1 Typical Application Circuit, Direct Supply, No DC-DC Converter

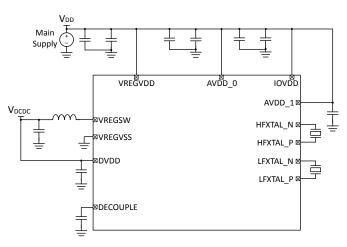

A typical application circuit using the internal dc-dc converter is shown in Figure 5.2 EFM32PG1 Typical Application Circuit Using the DC-DC Converter on page 47. The MCU operates from the dc-dc converter supply.

Figure 5.2. EFM32PG1 Typical Application Circuit Using the DC-DC Converter

## 5.2 Other Connections

Other components or connections may be required to meet the system-level requirements. Application Note AN0002: "Hardware Design Considerations" contains detailed information on these connections. Application Notes can be accessed on the Silicon Labs website (www.silabs.com/32bit-appnotes).

# 6. Pin Definitions

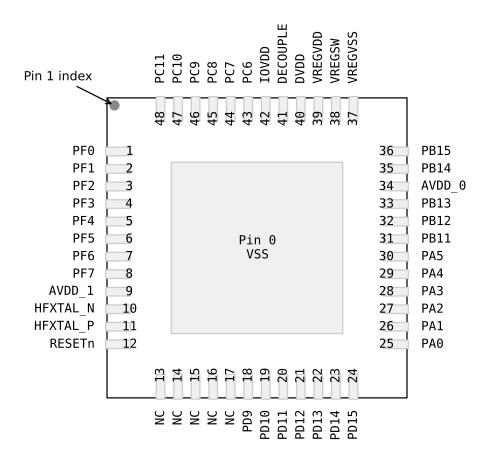

# 6.1 EFM32PG1 QFN48 with DC-DC Definition

Figure 6.1. EFM32PG1 QFN48 with DC-DC Pinout

| QFN      | 48 Pin# and Name |                | Pin Alternate Functionality / Description                                                                                                                                                                                                                |                                                                                                                                                                                                               |                                                                                           |  |  |  |  |  |  |  |  |

|----------|------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Pin<br># | Pin Name         | Analog         | Timers                                                                                                                                                                                                                                                   | Communication                                                                                                                                                                                                 | Other                                                                                     |  |  |  |  |  |  |  |  |

| 28       | PA3              | BUSCY<br>BUSDX | TIM0_CC0 #3<br>TIM0_CC1 #2<br>TIM0_CC2 #1<br>TIM0_CDTI0 #0<br>TIM0_CDTI1 #31<br>TIM0_CDTI2 #30<br>TIM1_CC0 #3<br>TIM1_CC1 #2<br>TIM1_CC2 #1<br>TIM1_CC3 #0 LE-<br>TIM0_OUT0 #3 LE-<br>TIM0_OUT0 #3 LE-<br>TIM0_OUT1 #2<br>PCNT0_S0IN #3<br>PCNT0_S1IN #2 | US0_TX #3 US0_RX #2<br>US0_CLK #1 US0_CS<br>#0 US0_CTS #31<br>US0_RTS #30 US1_TX<br>#3 US1_RX #2<br>US1_CLK #1 US1_CS<br>#0 US1_CTS #31<br>US1_RTS #30 LEU0_TX<br>#3 LEU0_RX #2<br>I2C0_SDA #3 I2C0_SCL<br>#2 | PRS_CH6 #3 PRS_CH7<br>#2 PRS_CH8 #1<br>PRS_CH9 #0 ACMP0_O<br>#3 ACMP1_O #3<br>GPIO_EM4WU8 |  |  |  |  |  |  |  |  |

| 29       | PA4              | BUSCX<br>BUSDY | TIM0_CC0 #4<br>TIM0_CC1 #3<br>TIM0_CC2 #2<br>TIM0_CDTI0 #1<br>TIM0_CDTI1 #0<br>TIM0_CDTI2 #31<br>TIM1_CC0 #4<br>TIM1_CC1 #3<br>TIM1_CC2 #2<br>TIM1_CC3 #1 LE-<br>TIM0_OUT0 #4 LE-<br>TIM0_OUT0 #4 LE-<br>TIM0_OUT1 #3<br>PCNT0_S0IN #4<br>PCNT0_S1IN #3  | US0_TX #4 US0_RX #3<br>US0_CLK #2 US0_CS<br>#1 US0_CTS #0<br>US0_RTS #31 US1_TX<br>#4 US1_RX #3<br>US1_CLK #2 US1_CS<br>#1 US1_CTS #0<br>US1_RTS #31 LEU0_TX<br>#4 LEU0_RX #3<br>I2C0_SDA #4 I2C0_SCL<br>#3   | PRS_CH6 #4 PRS_CH7<br>#3 PRS_CH8 #2<br>PRS_CH9 #1 ACMP0_O<br>#4 ACMP1_O #4                |  |  |  |  |  |  |  |  |

| 30       | PA5              | BUSCY<br>BUSDX | TIM0_CC0 #5<br>TIM0_CC1 #4<br>TIM0_CC2 #3<br>TIM0_CDTI0 #2<br>TIM0_CDTI1 #1<br>TIM0_CDT12 #0<br>TIM1_CC0 #5<br>TIM1_CC1 #4<br>TIM1_CC2 #3<br>TIM1_CC3 #2 LE-<br>TIM0_OUT0 #5 LE-<br>TIM0_OUT1 #4<br>PCNT0_S0IN #5<br>PCNT0_S1IN #4                       | US0_TX #5 US0_RX #4<br>US0_CLK #3 US0_CS<br>#2 US0_CTS #1<br>US0_RTS #0 US1_TX<br>#5 US1_RX #4<br>US1_CLK #3 US1_CS<br>#2 US1_CTS #1<br>US1_RTS #0 LEU0_TX<br>#5 LEU0_RX #4<br>I2C0_SDA #5 I2C0_SCL<br>#4     | PRS_CH6 #5 PRS_CH7<br>#4 PRS_CH8 #3<br>PRS_CH9 #2 ACMP0_O<br>#5 ACMP1_O #5                |  |  |  |  |  |  |  |  |

| 31       | PB11             | BUSCY<br>BUSDX | TIM0_CC0 #6<br>TIM0_CC1 #5<br>TIM0_CC2 #4<br>TIM0_CDTI0 #3<br>TIM0_CDTI1 #2<br>TIM0_CDTI2 #1<br>TIM1_CC0 #6<br>TIM1_CC1 #5<br>TIM1_CC2 #4<br>TIM1_CC3 #3 LE-<br>TIM0_OUT0 #6 LE-<br>TIM0_OUT0 #6 LE-<br>TIM0_OUT1 #5<br>PCNT0_S0IN #6<br>PCNT0_S1IN #5   | US0_TX #6 US0_RX #5<br>US0_CLK #4 US0_CS<br>#3 US0_CTS #2<br>US0_RTS #1 US1_TX<br>#6 US1_RX #5<br>US1_CLK #4 US1_CS<br>#3 US1_CTS #2<br>US1_RTS #1 LEU0_TX<br>#6 LEU0_RX #5<br>I2C0_SDA #6 I2C0_SCL<br>#5     | PRS_CH6 #6 PRS_CH7<br>#5 PRS_CH8 #4<br>PRS_CH9 #3 ACMP0_O<br>#6 ACMP1_O #6                |  |  |  |  |  |  |  |  |

| QFN      | 48 Pin# and Name |                | Pin Alternate Functi                                                                                                                                                                                                                                                  | onality / Description                                                                                                                                                                                                     |                                                                                                                       |

|----------|------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Pin<br># | Pin Name         | Analog         | Timers                                                                                                                                                                                                                                                                | Communication                                                                                                                                                                                                             | Other                                                                                                                 |

| 46       | PC9              | BUSAY<br>BUSBX | TIM0_CC0 #14<br>TIM0_CC1 #13<br>TIM0_CC2 #12<br>TIM0_CDTI0 #11<br>TIM0_CDTI1 #10<br>TIM0_CDTI2 #9<br>TIM1_CC0 #14<br>TIM1_CC1 #13<br>TIM1_CC2 #12<br>TIM1_CC3 #11 LE-<br>TIM0_OUT0 #14 LE-<br>TIM0_OUT1 #13<br>PCNT0_S0IN #14<br>PCNT0_S1IN #13                       | US0_TX #14 US0_RX<br>#13 US0_CLK #12<br>US0_CS #11 US0_CTS<br>#10 US0_RTS #9<br>US1_TX #14 US1_RX<br>#13 US1_CLK #12<br>US1_CS #11 US1_CTS<br>#10 US1_RTS #9<br>LEU0_TX #14 LEU0_RX<br>#13 I2C0_SDA #14<br>I2C0_SCL #13   | PRS_CH0 #11<br>PRS_CH9 #14<br>PRS_CH10 #3<br>PRS_CH11 #2<br>ACMP0_O #14<br>ACMP1_O #14                                |

| 47       | PC10             | BUSAX<br>BUSBY | TIM0_CC0 #15<br>TIM0_CC1 #14<br>TIM0_CC2 #13<br>TIM0_CDTI0 #12<br>TIM0_CDTI1 #11<br>TIM0_CDT12 #10<br>TIM1_CC0 #15<br>TIM1_CC1 #14<br>TIM1_CC2 #13<br>TIM1_CC3 #12 LE-<br>TIM0_OUT0 #15 LE-<br>TIM0_OUT1 #14<br>PCNT0_S0IN #15<br>PCNT0_S1IN #14                      | US0_TX #15 US0_RX<br>#14 US0_CLK #13<br>US0_CS #12 US0_CTS<br>#11 US0_RTS #10<br>US1_TX #15 US1_RX<br>#14 US1_CLK #13<br>US1_CS #12 US1_CTS<br>#11 US1_RTS #10<br>LEU0_TX #15 LEU0_RX<br>#14 I2C0_SDA #15<br>I2C0_SCL #14 | CMU_CLK1 #3<br>PRS_CH0 #12<br>PRS_CH9 #15<br>PRS_CH10 #4<br>PRS_CH11 #3<br>ACMP0_O #15<br>ACMP1_O #15<br>GPIO_EM4WU12 |

| 48       | PC11             | BUSAY<br>BUSBX | TIM0_CC0 #16<br>TIM0_CC1 #15<br>TIM0_CC2 #14<br>TIM0_CDTI0 #13<br>TIM0_CDTI1 #12<br>TIM0_CDTI2 #11<br>TIM1_CC0 #16<br>TIM1_CC1 #15<br>TIM1_CC2 #14<br>TIM1_CC3 #13 LE-<br>TIM0_OUT0 #16 LE-<br>TIM0_OUT0 #16 LE-<br>TIM0_OUT1 #15<br>PCNT0_S0IN #16<br>PCNT0_S1IN #15 | US0_TX #16 US0_RX<br>#15 US0_CLK #14<br>US0_CS #13 US0_CTS<br>#12 US0_RTS #11<br>US1_TX #16 US1_RX<br>#15 US1_CLK #14<br>US1_CS #13 US1_CTS<br>#12 US1_RTS #11<br>LEU0_TX #16 LEU0_RX<br>#15 I2C0_SDA #16<br>I2C0_SCL #15 | CMU_CLK0 #3<br>PRS_CH0 #13<br>PRS_CH9 #16<br>PRS_CH10 #5<br>PRS_CH11 #4<br>ACMP0_O #16<br>ACMP1_O #16<br>DBG_SWO #3   |

| QFN      | 32 Pin# and Name |                | Pin Alternate Functi                                                                                                                                                                                                                                                  | onality / Description                                                                                                                                                                                                     |                                                                                                 |

|----------|------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Pin<br># | Pin Name         | Analog         | Timers                                                                                                                                                                                                                                                                | Communication                                                                                                                                                                                                             | Other                                                                                           |

| 11       | PD10             | BUSCX<br>BUSDY | TIM0_CC0 #18<br>TIM0_CC1 #17<br>TIM0_CC2 #16<br>TIM0_CDTI0 #15<br>TIM0_CDTI1 #14<br>TIM0_CDTI2 #13<br>TIM1_CC0 #18<br>TIM1_CC1 #17<br>TIM1_CC2 #16<br>TIM1_CC3 #15 LE-<br>TIM0_OUT0 #18 LE-<br>TIM0_OUT0 #18 LE-<br>TIM0_OUT1 #17<br>PCNT0_S0IN #18<br>PCNT0_S1IN #17 | US0_TX #18 US0_RX<br>#17 US0_CLK #16<br>US0_CS #15 US0_CTS<br>#14 US0_RTS #13<br>US1_TX #18 US1_RX<br>#17 US1_CLK #16<br>US1_CS #15 US1_CTS<br>#14 US1_RTS #13<br>LEU0_TX #18 LEU0_RX<br>#17 I2C0_SDA #18<br>I2C0_SCL #17 | CMU_CLK1 #4<br>PRS_CH3 #9 PRS_CH4<br>#1 PRS_CH5 #0<br>PRS_CH6 #12<br>ACMP0_O #18<br>ACMP1_O #18 |

| 12       | PD11             | BUSCY<br>BUSDX | TIM0_CC0 #19<br>TIM0_CC1 #18<br>TIM0_CC2 #17<br>TIM0_CDTI0 #16<br>TIM0_CDTI1 #15<br>TIM0_CDT12 #14<br>TIM1_CC0 #19<br>TIM1_CC1 #18<br>TIM1_CC2 #17<br>TIM1_CC3 #16 LE-<br>TIM0_OUT0 #19 LE-<br>TIM0_OUT0 #19 LE-<br>TIM0_OUT1 #18<br>PCNT0_S0IN #19<br>PCNT0_S1IN #18 | US0_TX #19 US0_RX<br>#18 US0_CLK #17<br>US0_CS #16 US0_CTS<br>#15 US0_RTS #14<br>US1_TX #19 US1_RX<br>#18 US1_CLK #17<br>US1_CS #16 US1_CTS<br>#15 US1_RTS #14<br>LEU0_TX #19 LEU0_RX<br>#18 I2C0_SDA #19<br>I2C0_SCL #18 | PRS_CH3 #10<br>PRS_CH4 #2 PRS_CH5<br>#1 PRS_CH6 #13<br>ACMP0_O #19<br>ACMP1_O #19               |

| 13       | PD12             | BUSCX<br>BUSDY | TIM0_CC0 #20<br>TIM0_CC1 #19<br>TIM0_CC2 #18<br>TIM0_CDTI0 #17<br>TIM0_CDTI1 #16<br>TIM0_CDTI2 #15<br>TIM1_CC0 #20<br>TIM1_CC1 #19<br>TIM1_CC2 #18<br>TIM1_CC3 #17 LE-<br>TIM0_OUT0 #20 LE-<br>TIM0_OUT1 #19<br>PCNT0_S0IN #20<br>PCNT0_S1IN #19                      | US0_TX #20 US0_RX<br>#19 US0_CLK #18<br>US0_CS #17 US0_CTS<br>#16 US0_RTS #15<br>US1_TX #20 US1_RX<br>#19 US1_CLK #18<br>US1_CS #17 US1_CTS<br>#16 US1_RTS #15<br>LEU0_TX #20 LEU0_RX<br>#19 I2C0_SDA #20<br>I2C0_SCL #19 | PRS_CH3 #11<br>PRS_CH4 #3 PRS_CH5<br>#2 PRS_CH6 #14<br>ACMP0_O #20<br>ACMP1_O #20               |

| 14       | PD13             | BUSCY<br>BUSDX | TIM0_CC0 #21<br>TIM0_CC1 #20<br>TIM0_CC2 #19<br>TIM0_CDTI0 #18<br>TIM0_CDTI1 #17<br>TIM0_CDT12 #16<br>TIM1_CC0 #21<br>TIM1_CC1 #20<br>TIM1_CC2 #19<br>TIM1_CC3 #18 LE-<br>TIM0_OUT0 #21 LE-<br>TIM0_OUT0 #21 LE-<br>TIM0_OUT1 #20<br>PCNT0_S0IN #21<br>PCNT0_S1IN #20 | US0_TX #21 US0_RX<br>#20 US0_CLK #19<br>US0_CS #18 US0_CTS<br>#17 US0_RTS #16<br>US1_TX #21 US1_RX<br>#20 US1_CLK #19<br>US1_CS #18 US1_CTS<br>#17 US1_RTS #16<br>LEU0_TX #21 LEU0_RX<br>#20 I2C0_SDA #21<br>I2C0_SCL #20 | PRS_CH3 #12<br>PRS_CH4 #4 PRS_CH5<br>#3 PRS_CH6 #15<br>ACMP0_0 #21<br>ACMP1_0 #21               |

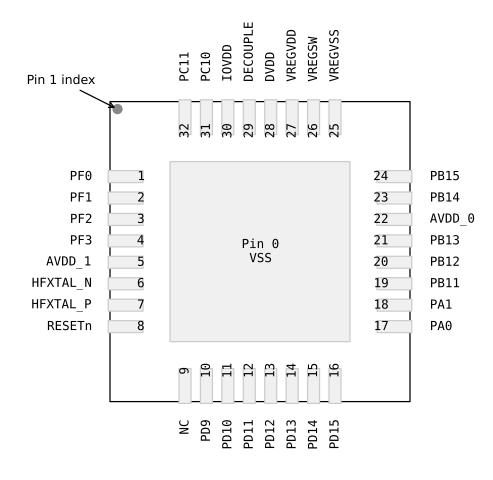

Figure 6.3. EFM32PG1 QFN32 with DC-DC Pinout

# EFM32PG1 Data Sheet Pin Definitions

| QFN      | 32 Pin# and Name |                            | Pin Alternate Functi                                                                                                                                                                                                                                        | onality / Description                                                                                                                                                                                         |                                                                                                         |

|----------|------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Pin<br># | Pin Name         | Analog                     | Timers                                                                                                                                                                                                                                                      | Communication                                                                                                                                                                                                 | Other                                                                                                   |

| 20       | PB12             | BUSCX<br>BUSDY             | TIM0_CC0 #7<br>TIM0_CC1 #6<br>TIM0_CC2 #5<br>TIM0_CDTI0 #4<br>TIM0_CDTI1 #3<br>TIM0_CDTI2 #2<br>TIM1_CC0 #7<br>TIM1_CC1 #6<br>TIM1_CC2 #5<br>TIM1_CC3 #4 LE-<br>TIM0_OUT0 #7 LE-<br>TIM0_OUT0 #7 LE-<br>TIM0_OUT1 #6<br>PCNT0_S0IN #7<br>PCNT0_S1IN #6      | US0_TX #7 US0_RX #6<br>US0_CLK #5 US0_CS<br>#4 US0_CTS #3<br>US0_RTS #2 US1_TX<br>#7 US1_RX #6<br>US1_CLK #5 US1_CS<br>#4 US1_CTS #3<br>US1_RTS #2 LEU0_TX<br>#7 LEU0_RX #6<br>I2C0_SDA #7 I2C0_SCL<br>#6     | PRS_CH6 #7 PRS_CH7<br>#6 PRS_CH8 #5<br>PRS_CH9 #4 ACMP0_O<br>#7 ACMP1_O #7                              |

| 21       | PB13             | BUSCY<br>BUSDX             | TIM0_CC0 #8<br>TIM0_CC1 #7<br>TIM0_CC2 #6<br>TIM0_CDTI0 #5<br>TIM0_CDTI1 #4<br>TIM0_CDTI2 #3<br>TIM1_CC0 #8<br>TIM1_CC1 #7<br>TIM1_CC2 #6<br>TIM1_CC3 #5 LE-<br>TIM0_OUT0 #8 LE-<br>TIM0_OUT1 #7<br>PCNT0_S0IN #8<br>PCNT0_S1IN #7                          | US0_TX #8 US0_RX #7<br>US0_CLK #6 US0_CS<br>#5 US0_CTS #4<br>US0_RTS #3 US1_TX<br>#8 US1_RX #7<br>US1_CLK #6 US1_CS<br>#5 US1_CTS #4<br>US1_RTS #3 LEU0_TX<br>#8 LEU0_RX #7<br>I2C0_SDA #8 I2C0_SCL<br>#7     | PRS_CH6 #8 PRS_CH7<br>#7 PRS_CH8 #6<br>PRS_CH9 #5 ACMP0_O<br>#8 ACMP1_O #8<br>DBG_SWO #1<br>GPIO_EM4WU9 |

| 22       | AVDD_0           | Analog power supply 0.     |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                               |                                                                                                         |

| 23       | PB14             | LFXTAL_N<br>BUSCX<br>BUSDY | TIM0_CC0 #9<br>TIM0_CC1 #8<br>TIM0_CC2 #7<br>TIM0_CDTI0 #6<br>TIM0_CDTI1 #5<br>TIM0_CDTI2 #4<br>TIM1_CC0 #9<br>TIM1_CC1 #8<br>TIM1_CC2 #7<br>TIM1_CC3 #6 LE-<br>TIM0_OUT0 #9 LE-<br>TIM0_OUT0 #9 LE-<br>TIM0_OUT1 #8<br>PCNT0_S0IN #9<br>PCNT0_S1IN #8      | US0_TX #9 US0_RX #8<br>US0_CLK #7 US0_CS<br>#6 US0_CTS #5<br>US0_RTS #4 US1_TX<br>#9 US1_RX #8<br>US1_CLK #7 US1_CS<br>#6 US1_CTS #5<br>US1_RTS #4 LEU0_TX<br>#9 LEU0_RX #8<br>I2C0_SDA #9 I2C0_SCL<br>#8     | CMU_CLK1 #1<br>PRS_CH6 #9 PRS_CH7<br>#8 PRS_CH8 #7<br>PRS_CH9 #6 ACMP0_O<br>#9 ACMP1_O #9               |

| 24       | PB15             | LFXTAL_P<br>BUSCY<br>BUSDX | TIM0_CC0 #10<br>TIM0_CC1 #9<br>TIM0_CC2 #8<br>TIM0_CDTI0 #7<br>TIM0_CDTI1 #6<br>TIM0_CDTI2 #5<br>TIM1_CC0 #10<br>TIM1_CC1 #9<br>TIM1_CC2 #8<br>TIM1_CC3 #7 LE-<br>TIM0_OUT0 #10 LE-<br>TIM0_OUT0 #10 LE-<br>TIM0_OUT1 #9<br>PCNT0_S0IN #10<br>PCNT0_S1IN #9 | US0_TX #10 US0_RX<br>#9 US0_CLK #8<br>US0_CS #7 US0_CTS<br>#6 US0_RTS #5<br>US1_TX #10 US1_RX<br>#9 US1_CLK #8<br>US1_CS #7 US1_CTS<br>#6 US1_RTS #5<br>LEU0_TX #10 LEU0_RX<br>#9 I2C0_SDA #10<br>I2C0_SCL #9 | CMU_CLK0 #1<br>PRS_CH6 #10<br>PRS_CH7 #9 PRS_CH8<br>#8 PRS_CH9 #7<br>ACMP0_O #10<br>ACMP1_O #10         |

## 6.3.1 EFM32PG1 QFN32 with DC-DC GPIO Overview

The GPIO pins are organized as 16-bit ports indicated by letters (A, B, C...), and the individual pins on each port are indicated by a number from 15 down to 0.

| Port   | Pin<br>15    | Pin<br>14    | Pin<br>13    | Pin<br>12    | Pin<br>11    | Pin<br>10    | Pin 9       | Pin 8 | Pin 7 | Pin 6 | Pin 5 | Pin 4 | Pin 3       | Pin 2       | Pin 1       | Pin 0       |

|--------|--------------|--------------|--------------|--------------|--------------|--------------|-------------|-------|-------|-------|-------|-------|-------------|-------------|-------------|-------------|

| Port A | -            | -            | -            | -            | -            | -            | -           | -     | -     | -     | -     | -     | -           | -           | PA1         | PA0         |

| Port B | PB15         | PB14         | PB13<br>(5V) | PB12<br>(5V) | PB11<br>(5V) | -            | -           | -     | -     | -     | -     | -     | -           | -           | -           | -           |

| Port C | -            | -            | -            | -            | PC11<br>(5V) | PC10<br>(5V) | -           | -     | -     | -     | -     | -     | -           | -           | -           | -           |

| Port D | PD15<br>(5V) | PD14<br>(5V) | PD13<br>(5V) | PD12<br>(5V) | PD11<br>(5V) | PD10<br>(5V) | PD9<br>(5V) | -     | -     | -     | -     | -     | -           | -           | -           | -           |

| Port F | -            | -            | -            | -            | -            | -            | -           | -     | -     | -     | -     | -     | PF3<br>(5V) | PF2<br>(5V) | PF1<br>(5V) | PF0<br>(5V) |

## Table 6.6. QFN32 with DC-DC GPIO Pinout

Note:

1. GPIO with 5V tolerance are indicated by (5V).

2. The pins PB13, PB12, PB11, PD15, PD14, and PD13 will not be 5V tolerant on all future devices. In order to preserve upgrade options with full hardware compatibility, do not use these pins with 5V domains.

| Alternate     |                                          |                                          |                                           | LOC                                          | ATION                                       |                                              |                                          |                                          |                                                         |

|---------------|------------------------------------------|------------------------------------------|-------------------------------------------|----------------------------------------------|---------------------------------------------|----------------------------------------------|------------------------------------------|------------------------------------------|---------------------------------------------------------|

| Functionality | 0 - 3                                    | 4 - 7                                    | 8 - 11                                    | 12 - 15                                      | 16 - 19                                     | 20 - 23                                      | 24 - 27                                  | 28 - 31                                  | Description                                             |

| PRS_CH1       | 0: PF1<br>1: PF2<br>2: PF3<br>3: PF4     | 4: PF5<br>5: PF6<br>6: PF7<br>7: PF0     |                                           |                                              |                                             |                                              |                                          |                                          | Peripheral Reflex<br>System PRS, chan-<br>nel 1.        |

| PRS_CH2       | 0: PF2<br>1: PF3<br>2: PF4<br>3: PF5     | 4: PF6<br>5: PF7<br>6: PF0<br>7: PF1     |                                           |                                              |                                             |                                              |                                          |                                          | Peripheral Reflex<br>System PRS, chan-<br>nel 2.        |

| PRS_CH3       | 0: PF3<br>1: PF4<br>2: PF5<br>3: PF6     | 4: PF7<br>5: PF0<br>6: PF1<br>7: PF2     | 8: PD9<br>9: PD10<br>10: PD11<br>11: PD12 | 12: PD13<br>13: PD14<br>14: PD15             |                                             |                                              |                                          |                                          | Peripheral Reflex<br>System PRS, chan-<br>nel 3.        |

| PRS_CH4       | 0: PD9<br>1: PD10<br>2: PD11<br>3: PD12  | 4: PD13<br>5: PD14<br>6: PD15            |                                           |                                              |                                             |                                              |                                          |                                          | Peripheral Reflex<br>System PRS, chan-<br>nel 4.        |

| PRS_CH5       | 0: PD10<br>1: PD11<br>2: PD12<br>3: PD13 | 4: PD14<br>5: PD15<br>6: PD9             |                                           |                                              |                                             |                                              |                                          |                                          | Peripheral Reflex<br>System PRS, chan-<br>nel 5.        |

| PRS_CH6       | 0: PA0<br>1: PA1<br>2: PA2<br>3: PA3     | 4: PA4<br>5: PA5<br>6: PB11<br>7: PB12   | 8: PB13<br>9: PB14<br>10: PB15<br>11: PD9 | 12: PD10<br>13: PD11<br>14: PD12<br>15: PD13 | 16: PD14<br>17: PD15                        |                                              |                                          |                                          | Peripheral Reflex<br>System PRS, chan-<br>nel 6.        |

| PRS_CH7       | 0: PA1<br>1: PA2<br>2: PA3<br>3: PA4     | 4: PA5<br>5: PB11<br>6: PB12<br>7: PB13  | 8: PB14<br>9: PB15<br>10: PA0             |                                              |                                             |                                              |                                          |                                          | Peripheral Reflex<br>System PRS, chan-<br>nel 7.        |

| PRS_CH8       | 0: PA2<br>1: PA3<br>2: PA4<br>3: PA5     | 4: PB11<br>5: PB12<br>6: PB13<br>7: PB14 | 8: PB15<br>9: PA0<br>10: PA1              |                                              |                                             |                                              |                                          |                                          | Peripheral Reflex<br>System PRS, chan-<br>nel 8.        |

| PRS_CH9       | 0: PA3<br>1: PA4<br>2: PA5<br>3: PB11    | 4: PB12<br>5: PB13<br>6: PB14<br>7: PB15 | 8: PA0<br>9: PA1<br>10: PA2<br>11: PC6    | 12: PC7<br>13: PC8<br>14: PC9<br>15: PC10    | 16: PC11                                    |                                              |                                          |                                          | Peripheral Reflex<br>System PRS, chan-<br>nel 9.        |

| PRS_CH10      | 0: PC6<br>1: PC7<br>2: PC8<br>3: PC9     | 4: PC10<br>5: PC11                       |                                           |                                              |                                             |                                              |                                          |                                          | Peripheral Reflex<br>System PRS, chan-<br>nel 10.       |

| PRS_CH11      | 0: PC7<br>1: PC8<br>2: PC9<br>3: PC10    | 4: PC11<br>5: PC6                        |                                           |                                              |                                             |                                              |                                          |                                          | Peripheral Reflex<br>System PRS, chan-<br>nel 11.       |

| TIM0_CC0      | 0: PA0<br>1: PA1<br>2: PA2<br>3: PA3     | 4: PA4<br>5: PA5<br>6: PB11<br>7: PB12   | 8: PB13<br>9: PB14<br>10: PB15<br>11: PC6 | 12: PC7<br>13: PC8<br>14: PC9<br>15: PC10    | 16: PC11<br>17: PD9<br>18: PD10<br>19: PD11 | 20: PD12<br>21: PD13<br>22: PD14<br>23: PD15 | 24: PF0<br>25: PF1<br>26: PF2<br>27: PF3 | 28: PF4<br>29: PF5<br>30: PF6<br>31: PF7 | Timer 0 Capture<br>Compare input /<br>output channel 0. |

| TIM0_CC1      | 0: PA1<br>1: PA2<br>2: PA3<br>3: PA4     | 4: PA5<br>5: PB11<br>6: PB12<br>7: PB13  | 8: PB14<br>9: PB15<br>10: PC6<br>11: PC7  | 12: PC8<br>13: PC9<br>14: PC10<br>15: PC11   | 16: PD9<br>17: PD10<br>18: PD11<br>19: PD12 | 20: PD13<br>21: PD14<br>22: PD15<br>23: PF0  | 24: PF1<br>25: PF2<br>26: PF3<br>27: PF4 | 28: PF5<br>29: PF6<br>30: PF7<br>31: PA0 | Timer 0 Capture<br>Compare input /<br>output channel 1. |

### 6.5 Analog Port (APORT) Client Maps

The Analog Port (APORT) is an infrastructure used to connect chip pins with on-chip analog clients such as analog comparators, ADCs, DACs, etc. The APORT consists of a set of shared buses, switches, and control logic needed to configurably implement the signal routing. A complete description of APORT functionality can be found in the Reference Manual.

Client maps for each analog circuit using the APORT are shown in the following tables. The maps are organized by bus, and show the peripheral's port connection, the shared bus, and the connection from specific bus channel numbers to GPIO pins.

In general, enumerations for the pin selection field in an analog peripheral's register can be determined by finding the desired pin connection in the table and then combining the value in the Port column (APORT\_\_), and the channel identifier (CH\_\_). For example, if pin PF7 is available on port APORT2X as CH23, the register field enumeration to connect to PF7 would be APORT2XCH23. The shared bus used by this connection is indicated in the Bus column.

| Port    | Bus   | CH31 | CH30 | CH29 | CH28 | CH27 | CH26 | CH25 | CH24 | CH23 | CH22 | CH21 | CH20 | CH19 | CH18 | CH17 | CH16 | CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | CH9 | CH8 | CH7  | CH6  | CH5  | CH4  | CH3  | CH2  | CH1 | CH0 |

|---------|-------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|------|------|------|------|------|------|-----|-----|

| APORT1X | BUSAX |      |      |      |      |      |      |      |      |      | PF6  |      | PF4  |      | PF2  |      | PF0  |      |      |      |      |      | PC10 |     | PC8 |      | 90d  |      |      |      |      |     |     |

| APORT1Y | BUSAY |      |      |      |      |      |      |      |      | PF7  |      | PF5  |      | PF3  |      | PF1  |      |      |      |      |      | PC11 |      | PC9 |     | PC7  |      |      |      |      |      |     |     |

| APORT2X | BUSBX |      |      |      |      |      |      |      |      | PF7  |      | PF5  |      | PF3  |      | PF1  |      |      |      |      |      | PC11 |      | PC9 |     | PC7  |      |      |      |      |      |     |     |

| APORT2Y | BUSBY |      |      |      |      |      |      |      |      |      | PF6  |      | PF4  |      | PF2  |      | PF0  |      |      |      |      |      | PC10 |     | PC8 |      | PC6  |      |      |      |      |     |     |

| APORT3X | BUSCX |      | PB14 |      | PB12 |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      | PA4  |      | PA2  |     | PA0 |      | PD14 |      | PD12 |      | PD10 |     |     |

| APORT3Y | BUSCY | PB15 |      | PB13 |      | PB11 |      |      |      |      |      |      |      |      |      |      |      |      |      | PA5  |      | PA3  |      | PA1 |     | PD15 |      | PD13 |      | PD11 |      | PD9 |     |

| APORT4X | BUSDX | PB15 |      | PB13 |      | PB11 |      |      |      |      |      |      |      |      |      |      |      |      |      | PA5  |      | PA3  |      | PA1 |     | PD15 |      | PD13 |      | PD11 |      | PD9 |     |

| APORT4Y | BUSDY |      | PB14 |      | PB12 |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      | PA4  |      | PA2  |     | PA0 |      | PD14 |      | PD12 |      | PD10 |     |     |

#### Table 6.8. ACMP0 Bus and Pin Mapping

| Dimension | Min      | Тур      | Мах  |  |  |  |  |  |  |

|-----------|----------|----------|------|--|--|--|--|--|--|

| A         | 0.80     | 0.85     | 0.90 |  |  |  |  |  |  |

| A1        | 0.00     | 0.02     | 0.05 |  |  |  |  |  |  |

| A3        | 0.20 REF |          |      |  |  |  |  |  |  |

| b         | 0.18     | 0.25     | 0.30 |  |  |  |  |  |  |

| D/E       | 4.90     | 5.00     | 5.10 |  |  |  |  |  |  |

| D2/E2     | 3.40     | 3.50     | 3.60 |  |  |  |  |  |  |

| E         |          | 0.50 BSC |      |  |  |  |  |  |  |

| L         | 0.30     | 0.40     | 0.50 |  |  |  |  |  |  |

| К         | 0.20     | _        | —    |  |  |  |  |  |  |

| R         | 0.09     | —        | 0.14 |  |  |  |  |  |  |

| ааа       |          | 0.15     |      |  |  |  |  |  |  |

| bbb       |          | 0.10     |      |  |  |  |  |  |  |

| ссс       |          | 0.10     |      |  |  |  |  |  |  |

| ddd       |          | 0.05     |      |  |  |  |  |  |  |

| eee       | 0.08     |          |      |  |  |  |  |  |  |

| fff       |          | 0.10     |      |  |  |  |  |  |  |

| Noto      | 1        |          |      |  |  |  |  |  |  |

## Table 8.1. QFN32 Package Dimensions

## Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to the JEDEC Solid State Outline MO-220, Variation VKKD-4.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## 9.7 Revision 0.1

Initial release.