Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M4                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                 |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                            |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.85V ~ 3.8V                                                               |

| Data Converters            | A/D 24x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 48-QFN (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32pg1b200f128gm48-c0r |

## 3.5 Counters/Timers and PWM

#### 3.5.1 Timer/Counter (TIMER)

TIMER peripherals keep track of timing, count events, generate PWM outputs and trigger timed actions in other peripherals through the PRS system. The core of each TIMER is a 16-bit counter with up to 4 compare/capture channels. Each channel is configurable in one of three modes. In capture mode, the counter state is stored in a buffer at a selected input event. In compare mode, the channel output reflects the comparison of the counter to a programmed threshold value. In PWM mode, the TIMER supports generation of pulse-width modulation (PWM) outputs of arbitrary waveforms defined by the sequence of values written to the compare registers, with optional dead-time insertion available in timer unit TIMER\_0 only.

## 3.5.2 Real Time Counter and Calendar (RTCC)

The Real Time Counter and Calendar (RTCC) is a 32-bit counter providing timekeeping in all energy modes. The RTCC includes a Binary Coded Decimal (BCD) calendar mode for easy time and date keeping. The RTCC can be clocked by any of the on-board oscillators with the exception of the AUXHFRCO, and it is capable of providing system wake-up at user defined instances. The RTCC includes 128 bytes of general purpose data retention, allowing easy and convenient data storage in all energy modes.

## 3.5.3 Low Energy Timer (LETIMER)

The unique LETIMER is a 16-bit timer that is available in energy mode EM2 Deep Sleep in addition to EM1 Sleep and EM0 Active. This allows it to be used for timing and output generation when most of the device is powered down, allowing simple tasks to be performed while the power consumption of the system is kept at an absolute minimum. The LETIMER can be used to output a variety of waveforms with minimal software intervention. The LETIMER is connected to the Real Time Counter and Calendar (RTCC), and can be configured to start counting on compare matches from the RTCC.

## 3.5.4 Ultra Low Power Wake-up Timer (CRYOTIMER)

The CRYOTIMER is a 32-bit counter that is capable of running in all energy modes. It can be clocked by either the 32.768 kHz crystal oscillator (LFXO), the 32.768 kHz RC oscillator (LFRCO), or the 1 kHz RC oscillator (ULFRCO). It can provide periodic Wakeup events and PRS signals which can be used to wake up peripherals from any energy mode. The CRYOTIMER provides a wide range of interrupt periods, facilitating flexible ultra-low energy operation.

## 3.5.5 Pulse Counter (PCNT)

The Pulse Counter (PCNT) peripheral can be used for counting pulses on a single input or to decode quadrature encoded inputs. The clock for PCNT is selectable from either an external source on pin PCTNn\_S0IN or from an internal timing reference, selectable from among any of the internal oscillators, except the AUXHFRCO. The module may operate in energy mode EM0 Active, EM1 Sleep, EM2 Deep Sleep, and EM3 Stop.

## 3.5.6 Watchdog Timer (WDOG)

The watchdog timer can act both as an independent watchdog or as a watchdog synchronous with the CPU clock. It has windowed monitoring capabilities, and can generate a reset or different interrupts depending on the failure mode of the system. The watchdog can also monitor autonomous systems driven by PRS.

# 3.6 Communications and Other Digital Peripherals

#### 3.6.1 Universal Synchronous/Asynchronous Receiver/Transmitter (USART)

The Universal Synchronous/Asynchronous Receiver/Transmitter is a flexible serial I/O module. It supports full duplex asynchronous UART communication with hardware flow control as well as RS-485, SPI, MicroWire and 3-wire. It can also interface with devices supporting:

- ISO7816 SmartCards

- IrDA

- I<sup>2</sup>S

## 3.6.2 Low Energy Universal Asynchronous Receiver/Transmitter (LEUART)

The unique LEUART<sup>TM</sup> provides two-way UART communication on a strict power budget. Only a 32.768 kHz clock is needed to allow UART communication up to 9600 baud. The LEUART includes all necessary hardware to make asynchronous serial communication possible with a minimum of software intervention and energy consumption.

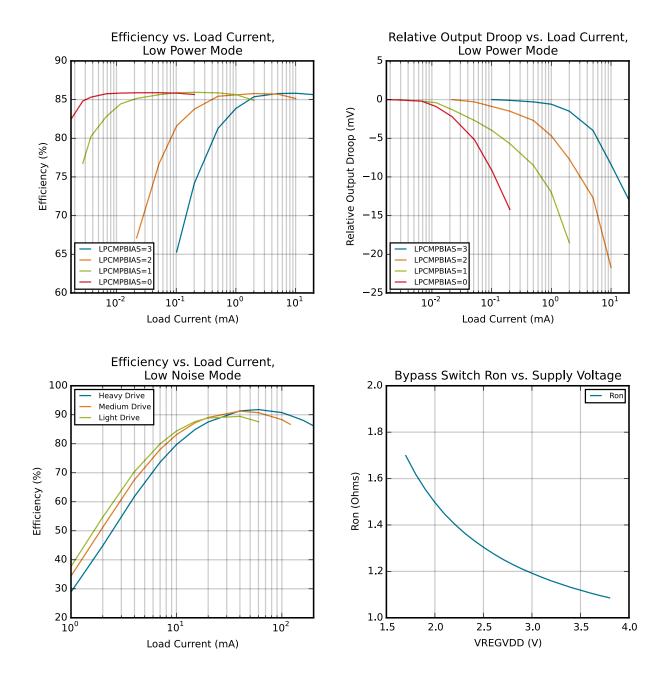

# 4.1.4 DC-DC Converter

Test conditions:  $L_{DCDC}$ =4.7  $\mu$ H (Murata LQH3NPN4R7MM0L),  $C_{DCDC}$ =1.0  $\mu$ F (Murata GRM188R71A105KA61D),  $V_{DCDC\_I}$ =3.3 V,  $V_{DCDC\_O}$ =1.8 V,  $I_{DCDC\_LOAD}$ =50 mA, Heavy Drive configuration,  $F_{DCDC\_LN}$ =7 MHz, unless otherwise indicated.

Table 4.4. DC-DC Converter

| Parameter                                           | Symbol              | Test Condition                                                                                                                           | Min  | Тур | Max                           | Unit |

|-----------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------------------------------|------|

| Input voltage range                                 | V <sub>DCDC_I</sub> | Bypass mode, I <sub>DCDC_LOAD</sub> = 50 mA                                                                                              | 1.85 | _   | V <sub>VREGVDD</sub> _        | V    |

|                                                     |                     | Low noise (LN) mode, 1.8 V output, I <sub>DCDC_LOAD</sub> = 100 mA, or Low power (LP) mode, 1.8 V output, I <sub>DCDC_LOAD</sub> = 10 mA | 2.4  | _   | V <sub>VREGVDD</sub><br>MAX   | V    |

|                                                     |                     | Low noise (LN) mode, 1.8 V output, I <sub>DCDC_LOAD</sub> = 200 mA                                                                       | 2.6  | _   | V <sub>VREGVDD</sub> _<br>MAX | V    |

| Output voltage programma-<br>ble range <sup>1</sup> | V <sub>DCDC_O</sub> |                                                                                                                                          | 1.8  | _   | V <sub>VREGVDD</sub>          | V    |

| Regulation DC Accuracy                              | ACC <sub>DC</sub>   | Low noise (LN) mode, 1.8 V target output                                                                                                 | 1.7  | _   | 1.9                           | V    |

| Regulation Window <sup>2</sup>                      | WIN <sub>REG</sub>  | Low power (LP) mode,<br>LPCMPBIAS <sup>3</sup> = 0, 1.8 V target<br>output, I <sub>DCDC_LOAD</sub> ≤ 75 µA                               | 1.63 | _   | 2.2                           | V    |

|                                                     |                     | Low power (LP) mode,<br>LPCMPBIAS <sup>3</sup> = 3, 1.8 V target<br>output, I <sub>DCDC_LOAD</sub> ≤ 10 mA                               | 1.63 | _   | 2.1                           | V    |

| Steady-state output ripple                          | V <sub>R</sub>      |                                                                                                                                          | _    | 3   | _                             | mVpp |

| Output voltage under/over-<br>shoot                 | V <sub>OV</sub>     | CCM Mode (LNFORCECCM <sup>3</sup> = 1), Load changes between 0 mA and 100 mA                                                             | _    | _   | 150                           | mV   |

|                                                     |                     | DCM Mode (LNFORCECCM <sup>3</sup> = 0), Load changes between 0 mA and 10 mA                                                              | _    | _   | 150                           | mV   |

|                                                     |                     | Overshoot during LP to LN CCM/DCM mode transitions compared to DC level in LN mode                                                       | _    | 200 | _                             | mV   |

|                                                     |                     | Undershoot during BYP/LP to LN CCM (LNFORCECCM <sup>3</sup> = 1) mode transitions compared to DC level in LN mode                        | _    | 50  | _                             | mV   |

|                                                     |                     | Undershoot during BYP/LP to LN DCM (LNFORCECCM <sup>3</sup> = 0) mode transitions compared to DC level in LN mode                        | _    | 125 | _                             | mV   |

| DC line regulation                                  | V <sub>REG</sub>    | Input changes between V <sub>VREGVDD_MAX</sub> and 2.4 V                                                                                 | _    | 0.1 | _                             | %    |

| DC load regulation                                  | I <sub>REG</sub>    | Load changes between 0 mA and 100 mA in CCM mode                                                                                         | _    | 0.1 | _                             | %    |

| Parameter                                | Symbol            | Test Condition            | Min | Тур  | Max | Unit |

|------------------------------------------|-------------------|---------------------------|-----|------|-----|------|

| Current consumption in EM4S Shutoff mode | I <sub>EM4S</sub> | no RAM retention, no RTCC | _   | 0.04 |     | μA   |

## Note:

- 1. DCDC Low Noise DCM Mode = Light Drive (PFETCNT=NFETCNT=3), F=3.0 MHz (RCOBAND=0), ANASW=DVDD

- 2. CMU\_HFXOCTRL\_LOWPOWER=1

- 3. DCDC Low Noise CCM Mode = Light Drive (PFETCNT=NFETCNT=3), F=6.4 MHz (RCOBAND=4), ANASW=DVDD

- 4. DCDC Low Power Mode = Medium Drive (PFETCNT=NFETCNT=7), LPOSCDIV=1, LPBIAS=3, LPCILIMSEL=1, ANASW=DVDD

## 4.1.5.3 Current Consumption 1.85 V without DC-DC Converter

Unless otherwise indicated, typical conditions are: VREGVDD = AVDD = DVDD = 1.85 V.  $T_{OP}$  = 25 °C. EMU\_PWRCFG\_PWRCG=NODCDC. EMU\_DCDCCTRL\_DCDCMODE=BYPASS. Minimum and maximum values in this table represent the worst conditions across supply voltage and process variation at  $T_{OP}$  = 25 °C. See Figure 5.1 EFM32PG1 Typical Application Circuit, Direct Supply, No DC-DC Converter on page 47.

Table 4.7. Current Consumption 1.85V without DC/DC

| Parameter                                                               | Symbol              | Test Condition                                                   | Min | Тур  | Max | Unit   |

|-------------------------------------------------------------------------|---------------------|------------------------------------------------------------------|-----|------|-----|--------|

| Current consumption in EM0<br>Active mode with all peripherals disabled | I <sub>ACTIVE</sub> | 38.4 MHz crystal, CPU running while loop from flash <sup>1</sup> | _   | 127  | _   | μA/MHz |

| erais disabled                                                          |                     | 38 MHz HFRCO, CPU running<br>Prime from flash                    | _   | 88   | _   | μΑ/MHz |

|                                                                         |                     | 38 MHz HFRCO, CPU running while loop from flash                  | _   | 100  | _   | µA/MHz |

|                                                                         |                     | 38 MHz HFRCO, CPU running<br>CoreMark from flash                 | _   | 112  | _   | µA/MHz |

|                                                                         |                     | 26 MHz HFRCO, CPU running while loop from flash                  | _   | 102  | _   | µA/MHz |

|                                                                         |                     | 1 MHz HFRCO, CPU running while loop from flash                   | _   | 220  | _   | µA/MHz |

| Current consumption in EM1                                              | I <sub>EM1</sub>    | 38.4 MHz crystal <sup>1</sup>                                    | _   | 61   | _   | μΑ/MHz |

| Sleep mode with all peripherals disabled                                |                     | 38 MHz HFRCO                                                     | _   | 35   | _   | µA/MHz |

|                                                                         |                     | 26 MHz HFRCO                                                     | _   | 37   | _   | μΑ/MHz |

|                                                                         |                     | 1 MHz HFRCO                                                      | _   | 154  | _   | μΑ/MHz |

| Current consumption in EM2<br>Deep Sleep mode                           | I <sub>EM2</sub>    | Full RAM retention and RTCC running from LFXO                    | _   | 3.2  | _   | μА     |

|                                                                         |                     | 4 kB RAM retention and RTCC running from LFRCO                   | _   | 2.8  | _   | μА     |

| Current consumption in EM3<br>Stop mode                                 | I <sub>EM3</sub>    | Full RAM retention and CRYO-<br>TIMER running from ULFRCO        | _   | 2.7  | _   | μА     |

| Current consumption in EM4H Hibernate mode                              | I <sub>EM4</sub>    | 128 byte RAM retention, RTCC running from LFXO                   | _   | 1    | _   | μА     |

|                                                                         |                     | 128 byte RAM retention, CRYO-<br>TIMER running from ULFRCO       | _   | 0.62 | _   | μА     |

|                                                                         |                     | 128 byte RAM retention, no RTCC                                  | _   | 0.62 | _   | μA     |

| Current consumption in EM4S Shutoff mode                                | I <sub>EM4S</sub>   | No RAM retention, no RTCC                                        | _   | 0.02 | _   | μА     |

| Note:                                                                   |                     |                                                                  |     |      |     |        |

#### Note:

1. CMU\_HFXOCTRL\_LOWPOWER=1

# 4.1.13 IDAC

Table 4.19. IDAC

| Parameter                                   | Symbol                   | Test Condition                                                                      | Min  | Тур  | Max | Unit |

|---------------------------------------------|--------------------------|-------------------------------------------------------------------------------------|------|------|-----|------|

| Number of Ranges                            | N <sub>IDAC_RANGES</sub> |                                                                                     | _    | 4    | _   | -    |

| Output Current                              | I <sub>IDAC_OUT</sub>    | RANGSEL <sup>1</sup> = RANGE0                                                       | 0.05 | _    | 1.6 | μA   |

|                                             |                          | RANGSEL <sup>1</sup> = RANGE1                                                       | 1.6  | _    | 4.7 | μA   |

|                                             |                          | RANGSEL <sup>1</sup> = RANGE2                                                       | 0.5  | _    | 16  | μA   |

|                                             |                          | RANGSEL <sup>1</sup> = RANGE3                                                       | 2    | _    | 64  | μA   |

| Linear steps within each range              | N <sub>IDAC_STEPS</sub>  |                                                                                     | _    | 32   | _   |      |

| Step size                                   | SS <sub>IDAC</sub>       | RANGSEL <sup>1</sup> = RANGE0                                                       | _    | 50   | _   | nA   |

|                                             |                          | RANGSEL <sup>1</sup> = RANGE1                                                       | _    | 100  | _   | nA   |

|                                             |                          | RANGSEL <sup>1</sup> = RANGE2                                                       | _    | 500  | _   | nA   |

|                                             |                          | RANGSEL <sup>1</sup> = RANGE3                                                       | _    | 2    | _   | μA   |

| Total Accuracy, STEPSEL <sup>1</sup> = 0x10 | ACC <sub>IDAC</sub>      | EM0 or EM1, AVDD=3.3 V, T = 25 °C                                                   | -2   | _    | 2   | %    |

|                                             |                          | EM0 or EM1                                                                          | -18  | _    | 22  | %    |

|                                             |                          | EM2 or EM3, Source mode,<br>RANGSEL <sup>1</sup> = RANGE0,<br>AVDD=3.3 V, T = 25 °C | _    | -2   | _   | %    |

|                                             |                          | EM2 or EM3, Source mode,<br>RANGSEL <sup>1</sup> = RANGE1,<br>AVDD=3.3 V, T = 25 °C | _    | -1.7 | _   | %    |

|                                             |                          | EM2 or EM3, Source mode,<br>RANGSEL <sup>1</sup> = RANGE2,<br>AVDD=3.3 V, T = 25 °C | _    | -0.8 | _   | %    |

|                                             |                          | EM2 or EM3, Source mode,<br>RANGSEL <sup>1</sup> = RANGE3,<br>AVDD=3.3 V, T = 25 °C | _    | -0.5 | _   | %    |

|                                             |                          | EM2 or EM3, Sink mode, RANG-<br>SEL <sup>1</sup> = RANGE0, AVDD=3.3 V, T<br>= 25 °C | _    | -0.7 | _   | %    |

|                                             |                          | EM2 or EM3, Sink mode, RANG-<br>SEL <sup>1</sup> = RANGE1, AVDD=3.3 V, T<br>= 25 °C | _    | -0.6 | _   | %    |

|                                             |                          | EM2 or EM3, Sink mode, RANG-<br>SEL <sup>1</sup> = RANGE2, AVDD=3.3 V, T<br>= 25 °C | _    | -0.5 | _   | %    |

|                                             |                          | EM2 or EM3, Sink mode, RANG-<br>SEL <sup>1</sup> = RANGE3, AVDD=3.3 V, T<br>= 25 °C | _    | -0.5 | _   | %    |

| Start up time                               | t <sub>IDAC_SU</sub>     | Output within 1% of steady state value                                              | _    | 5    | _   | μs   |

| Parameter                                                                           | Symbol                   | Test Condition                                                                                 | Min | Тур  | Max | Unit |

|-------------------------------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Settling time, (output settled                                                      | t <sub>IDAC_SETTLE</sub> | Range setting is changed                                                                       | _   | 5    | _   | μs   |

| within 1% of steady state value)                                                    |                          | Step value is changed                                                                          | _   | 1    | _   | μs   |

| Current consumption in EM0 or EM1 <sup>2</sup>                                      | I <sub>IDAC</sub>        | Source mode, excluding output current                                                          | _   | 8.9  | 13  | μA   |

|                                                                                     |                          | Sink mode, excluding output current                                                            | _   | 12   | 16  | μA   |

| Current consumption in EM2 or EM3 <sup>2</sup>                                      |                          | Source mode, excluding output current, duty cycle mode, T = 25 °C                              | _   | 1.04 | _   | μА   |

|                                                                                     |                          | Sink mode, excluding output current, duty cycle mode, T = 25 °C                                | _   | 1.08 | _   | μA   |

|                                                                                     |                          | Source mode, excluding output current, duty cycle mode, T ≥ 85 °C                              | _   | 8.9  | _   | μA   |

|                                                                                     |                          | Sink mode, excluding output current, duty cycle mode, T ≥ 85 °C                                | _   | 12   | _   | μA   |

| Output voltage compliance in source mode, source current change relative to current | ICOMP_SRC                | RANGESEL1=0, output voltage = min(V <sub>IOVDD</sub> , V <sub>AVDD</sub> <sup>2</sup> -100 mv) | _   | 0.04 | _   | %    |

| sourced at 0 V                                                                      |                          | RANGESEL1=1, output voltage = min(V <sub>IOVDD</sub> , V <sub>AVDD</sub> <sup>2</sup> -100 mV) | _   | 0.02 | _   | %    |

|                                                                                     |                          | RANGESEL1=2, output voltage = min(V <sub>IOVDD</sub> , V <sub>AVDD</sub> <sup>2</sup> -150 mV) | _   | 0.02 | _   | %    |

|                                                                                     |                          | RANGESEL1=3, output voltage = min(V <sub>IOVDD</sub> , V <sub>AVDD</sub> <sup>2</sup> -250 mV) | _   | 0.02 | _   | %    |

| Output voltage compliance in sink mode, sink current                                | I <sub>COMP_SINK</sub>   | RANGESEL1=0, output voltage = 100 mV                                                           | _   | 0.18 | _   | %    |

| change relative to current sunk at IOVDD                                            |                          | RANGESEL1=1, output voltage = 100 mV                                                           | _   | 0.12 | _   | %    |

|                                                                                     |                          | RANGESEL1=2, output voltage = 150 mV                                                           | _   | 0.08 | _   | %    |

|                                                                                     |                          | RANGESEL1=3, output voltage = 250 mV                                                           | _   | 0.02 | _   | %    |

## Note:

- 1. In IDAC\_CURPROG register

- 2. The IDAC is supplied by either AVDD, DVDD, or IOVDD based on the setting of ANASW in the EMU\_PWRCTRL register and PWRSEL in the IDAC\_CTRL register. Setting PWRSEL to 1 selects IOVDD. With PWRSEL cleared to 0, ANASW selects between AVDD (0) and DVDD (1).

# 4.1.14 Analog Comparator (ACMP)

Table 4.20. ACMP

| Parameter                                                           | Symbol                | Test Condition                                               | Min   | Тур | Max                    | Unit |

|---------------------------------------------------------------------|-----------------------|--------------------------------------------------------------|-------|-----|------------------------|------|

| Input voltage range                                                 | V <sub>ACMPIN</sub>   | ACMPVDD = ACMPn_CTRL_PWRSEL <sup>1</sup>                     | 0     | _   | V <sub>ACMPVDD</sub>   | V    |

| Supply Voltage                                                      | V <sub>ACMPVDD</sub>  | BIASPROG $^2 \le 0x10$ or FULL-BIAS $^2 = 0$                 | 1.85  | _   | V <sub>VREGVDD</sub> _ | V    |

|                                                                     |                       | $0x10 < BIASPROG^2 \le 0x20$ and FULLBIAS <sup>2</sup> = 1   | 2.1   | _   | V <sub>VREGVDD</sub> _ | V    |

| Active current not including                                        | I <sub>ACMP</sub>     | $BIASPROG^2 = 1$ , $FULLBIAS^2 = 0$                          | _     | 50  | _                      | nA   |

| voltage reference                                                   |                       | BIASPROG $^2$ = 0x10, FULLBIAS $^2$ = 0                      | _     | 306 | _                      | nA   |

|                                                                     |                       | BIASPROG <sup>2</sup> = 0x20, FULLBIAS <sup>2</sup> = 1      | _     | 74  | 95                     | μΑ   |

| Current consumption of internal voltage reference                   | I <sub>ACMPREF</sub>  | VLP selected as input using 2.5 V<br>Reference / 4 (0.625 V) | _     | 50  | _                      | nA   |

|                                                                     |                       | VLP selected as input using VDD                              | _     | 20  | _                      | nA   |

|                                                                     |                       | VBDIV selected as input using 1.25 V reference / 1           | _     | 4.1 | _                      | μΑ   |

|                                                                     |                       | VADIV selected as input using VDD/1                          | _     | 2.4 | _                      | μΑ   |

| Hysteresis (V <sub>CM</sub> = 1.25 V,                               | V <sub>ACMPHYST</sub> | HYSTSEL <sup>3</sup> = HYST0                                 | -1.75 | 0   | 1.75                   | mV   |

| BIASPROG <sup>2</sup> = $0x10$ , FULL-<br>BIAS <sup>2</sup> = $1$ ) |                       | HYSTSEL <sup>3</sup> = HYST1                                 | 10    | 18  | 26                     | mV   |

|                                                                     |                       | HYSTSEL <sup>3</sup> = HYST2                                 | 21    | 32  | 46                     | mV   |

|                                                                     |                       | HYSTSEL <sup>3</sup> = HYST3                                 | 27    | 44  | 63                     | mV   |

|                                                                     |                       | HYSTSEL <sup>3</sup> = HYST4                                 | 32    | 55  | 80                     | mV   |

|                                                                     |                       | HYSTSEL <sup>3</sup> = HYST5                                 | 38    | 65  | 100                    | mV   |

|                                                                     |                       | HYSTSEL <sup>3</sup> = HYST6                                 | 43    | 77  | 121                    | mV   |

|                                                                     |                       | HYSTSEL <sup>3</sup> = HYST7                                 | 47    | 86  | 148                    | mV   |

|                                                                     |                       | HYSTSEL <sup>3</sup> = HYST8                                 | -4    | 0   | 4                      | mV   |

|                                                                     |                       | HYSTSEL <sup>3</sup> = HYST9                                 | -27   | -18 | -10                    | mV   |

|                                                                     |                       | HYSTSEL <sup>3</sup> = HYST10                                | -47   | -32 | -18                    | mV   |

|                                                                     |                       | HYSTSEL <sup>3</sup> = HYST11                                | -64   | -43 | -27                    | mV   |

|                                                                     |                       | HYSTSEL <sup>3</sup> = HYST12                                | -78   | -54 | -32                    | mV   |

|                                                                     |                       | HYSTSEL <sup>3</sup> = HYST13                                | -93   | -64 | -37                    | mV   |

|                                                                     |                       | HYSTSEL <sup>3</sup> = HYST14                                | -113  | -74 | -42                    | mV   |

|                                                                     |                       | HYSTSEL <sup>3</sup> = HYST15                                | -135  | -85 | -47                    | mV   |

| Parameter                            | Symbol                  | Test Condition                                             | Min | Тур  | Max  | Unit |

|--------------------------------------|-------------------------|------------------------------------------------------------|-----|------|------|------|

| Comparator delay <sup>4</sup>        | t <sub>ACMPDELAY</sub>  | $BIASPROG^2 = 1$ , $FULLBIAS^2 = 0$                        | _   | 30   | _    | μs   |

|                                      |                         | BIASPROG <sup>2</sup> = 0x10, FULLBIAS <sup>2</sup><br>= 0 | _   | 3.7  | _    | μs   |

|                                      |                         | BIASPROG <sup>2</sup> = 0x20, FULLBIAS <sup>2</sup> = 1    | _   | 35   | _    | ns   |

| Offset voltage                       | V <sub>ACMPOFFSET</sub> | BIASPROG <sup>2</sup> =0x10, FULLBIAS <sup>2</sup> = 1     | -35 | _    | 35   | mV   |

| Reference Voltage                    | V <sub>ACMPREF</sub>    | Internal 1.25 V reference                                  | 1   | 1.25 | 1.47 | V    |

|                                      |                         | Internal 2.5 V reference                                   | 2   | 2.5  | 2.8  | V    |

| Capacitive Sense Internal Resistance | R <sub>CSRES</sub>      | CSRESSEL <sup>5</sup> = 0                                  | _   | inf  | _    | kΩ   |

| Resistance                           |                         | CSRESSEL <sup>5</sup> = 1                                  | _   | 15   | _    | kΩ   |

|                                      |                         | CSRESSEL <sup>5</sup> = 2                                  | _   | 27   | _    | kΩ   |

|                                      |                         | CSRESSEL <sup>5</sup> = 3                                  | _   | 39   | _    | kΩ   |

|                                      |                         | CSRESSEL <sup>5</sup> = 4                                  | _   | 51   | _    | kΩ   |

|                                      |                         | CSRESSEL <sup>5</sup> = 5                                  | _   | 102  | _    | kΩ   |

|                                      |                         | CSRESSEL <sup>5</sup> = 6                                  | _   | 164  | _    | kΩ   |

|                                      |                         | CSRESSEL <sup>5</sup> = 7                                  | _   | 239  | _    | kΩ   |

## Note:

- 1. ACMPVDD is a supply chosen by the setting in ACMPn\_CTRL\_PWRSEL and may be IOVDD, AVDD or DVDD

- 2. In ACMPn\_CTRL register

- 3. In ACMPn\_HYSTERESIS register

- 4. ±100 mV differential drive

- 5. In ACMPn\_INPUTSEL register

The total ACMP current is the sum of the contributions from the ACMP and its internal voltage reference as given as:

# I<sub>ACMPTOTAL</sub> = I<sub>ACMP</sub> + I<sub>ACMPREF</sub>

$I_{\mbox{\scriptsize ACMPREF}}$  is zero if an external voltage reference is used.

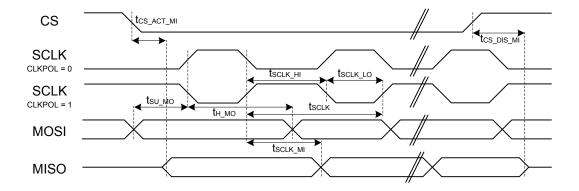

# **SPI Slave Timing**

Table 4.25. SPI Slave Timing

| Parameter                         | Symbol               | Test Condition | Min                                             | Тур | Max                                              | Unit |

|-----------------------------------|----------------------|----------------|-------------------------------------------------|-----|--------------------------------------------------|------|

| SCKL period <sup>1 2</sup>        | t <sub>SCLK_sl</sub> |                | 2 *<br>t <sub>HFPERCLK</sub>                    | _   | _                                                | ns   |

| SCLK high period <sup>1 2</sup>   | t <sub>SCLK_hi</sub> |                | 3 *<br>t <sub>HFPERCLK</sub>                    | _   | _                                                | ns   |

| SCLK low period <sup>1 2</sup>    | t <sub>SCLK_lo</sub> |                | 3 *<br>t <sub>HFPERCLK</sub>                    | _   | _                                                | ns   |

| CS active to MISO <sup>1 2</sup>  | tcs_act_mi           |                | 4                                               | _   | 50                                               | ns   |

| CS disable to MISO <sup>1 2</sup> | tcs_dis_mi           |                | 4                                               | _   | 50                                               | ns   |

| MOSI setup time <sup>1 2</sup>    | t <sub>SU_MO</sub>   |                | 4                                               | _   | _                                                | ns   |

| MOSI hold time <sup>1 2</sup>     | t <sub>H_MO</sub>    |                | 3 + 2 * the | _   | _                                                | ns   |

| SCLK to MISO <sup>1 2</sup>       | t <sub>SCLK_MI</sub> |                | 16 +<br>t <sub>HFPERCLK</sub>                   | _   | 66 + 2 * the | ns   |

## Note:

- 1. Applies for both CLKPHA = 0 and CLKPHA = 1 (figure only shows CLKPHA = 0)

- 2. Measurement done with 8 pF output loading at 10% and 90% of  $V_{DD}$  (figure shows 50% of  $V_{DD}$ )

Figure 4.2. SPI Slave Timing Diagram

# 4.2 Typical Performance Curves

Typical performance curves indicate typical characterized performance under the stated conditions.

## 4.2.2 DC-DC Converter

Default test conditions: CCM mode, LDCDC =  $4.7 \mu H$ , CDCDC =  $1.0 \mu F$ , VDCDC\_I = 3.3 V, VDCDC\_O = 1.8 V, FDCDC\_LN = 7 MHz

Figure 4.6. DC-DC Converter Typical Performance Characteristics

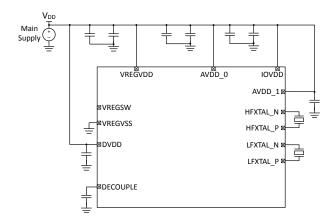

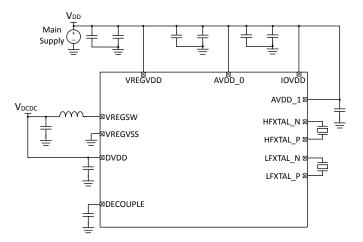

# 5. Typical Connection Diagrams

## 5.1 Power

Typical power supply connections for direct supply, without using the internal dc-dc converter, are shown in Figure 5.1 EFM32PG1 Typical Application Circuit, Direct Supply, No DC-DC Converter on page 47.

Figure 5.1. EFM32PG1 Typical Application Circuit, Direct Supply, No DC-DC Converter

A typical application circuit using the internal dc-dc converter is shown in Figure 5.2 EFM32PG1 Typical Application Circuit Using the DC-DC Converter on page 47. The MCU operates from the dc-dc converter supply.

Figure 5.2. EFM32PG1 Typical Application Circuit Using the DC-DC Converter

## 5.2 Other Connections

Other components or connections may be required to meet the system-level requirements. Application Note AN0002: "Hardware Design Considerations" contains detailed information on these connections. Application Notes can be accessed on the Silicon Labs website (www.silabs.com/32bit-appnotes).

| QFN      | 48 Pin# and Name |                             | Pin Alternate Functi                                                                                                                                                                                      | onality / Description                                                                                                                                                                                                     |                                                                                              |

|----------|------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Pin<br># | Pin Name         | Analog                      | Timers                                                                                                                                                                                                    | Communication                                                                                                                                                                                                             | Other                                                                                        |

| 24       | PD15             | BUSCY<br>BUSDX              | TIM0_CC0 #23 TIM0_CC1 #22 TIM0_CC2 #21 TIM0_CDTI0 #20 TIM0_CDTI1 #19 TIM0_CDTI2 #18 TIM1_CC0 #23 TIM1_CC1 #22 TIM1_CC2 #21 TIM1_CC3 #20 LE- TIM0_OUT0 #23 LE- TIM0_OUT1 #22 PCNT0_S0IN #23 PCNT0_S1IN #22 | US0_TX #23 US0_RX<br>#22 US0_CLK #21<br>US0_CS #20 US0_CTS<br>#19 US0_RTS #18<br>US1_TX #23 US1_RX<br>#22 US1_CLK #21<br>US1_CS #20 US1_CTS<br>#19 US1_RTS #18<br>LEU0_TX #23 LEU0_RX<br>#22 I2C0_SDA #23<br>I2C0_SCL #22 | CMU_CLK1 #5 PRS_CH3 #14 PRS_CH4 #6 PRS_CH5 #5 PRS_CH6 #17 ACMP0_O #23 ACMP1_O #23 DBG_SWO #2 |

| 25       | PA0              | ADC0_EXTN<br>BUSCX<br>BUSDY | TIM0_CC0 #0 TIM0_CC1 #31 TIM0_CC2 #30 TIM0_CDTI0 #29 TIM0_CDTI1 #28 TIM0_CDTI2 #27 TIM1_CC0 #0 TIM1_CC1 #31 TIM1_CC2 #30 TIM1_CC3 #29 LE- TIM0_OUT0 #0 LE- TIM0_OUT1 #31 PCNT0_S0IN #0 PCNT0_S1IN #31     | US0_TX #0 US0_RX<br>#31 US0_CLK #30<br>US0_CS #29 US0_CTS<br>#28 US0_RTS #27<br>US1_TX #0 US1_RX<br>#31 US1_CLK #30<br>US1_CS #29 US1_CTS<br>#28 US1_RTS #27<br>LEU0_TX #0 LEU0_RX<br>#31 I2C0_SDA #0<br>I2C0_SCL #31     | CMU_CLK1 #0 PRS_CH6 #0 PRS_CH7 #10 PRS_CH8 #9 PRS_CH9 #8 ACMP0_O #0 ACMP1_O #0               |

| 26       | PA1              | ADC0_EXTP<br>BUSCY<br>BUSDX | TIM0_CC0 #1 TIM0_CC1 #0 TIM0_CC2 #31 TIM0_CDTI0 #30 TIM0_CDTI1 #29 TIM0_CDTI2 #28 TIM1_CC0 #1 TIM1_CC1 #0 TIM1_CC2 #31 TIM1_CC3 #30 LE- TIM0_OUT0 #1 LE- TIM0_OUT1 #0 PCNT0_S0IN #1 PCNT0_S1IN #0         | US0_TX #1 US0_RX #0 US0_CLK #31 US0_CS #30 US0_CTS #29 US0_RTS #28 US1_TX #1 US1_RX #0 US1_CLK #31 US1_CS #30 US1_CTS #29 US1_RTS #28 LEU0_TX #1 LEU0_RX #0 I2C0_SDA #1 I2C0_SCL #0                                       | CMU_CLK0 #0 PRS_CH6 #1 PRS_CH7 #0 PRS_CH8 #10 PRS_CH9 #9 ACMP0_O #1 ACMP1_O #1               |

| 27       | PA2              | BUSCX<br>BUSDY              | TIM0_CC0 #2 TIM0_CC1 #1 TIM0_CC2 #0 TIM0_CDTI0 #31 TIM0_CDTI1 #30 TIM0_CDTI2 #29 TIM1_CC0 #2 TIM1_CC1 #1 TIM1_CC2 #0 TIM1_CC3 #31 LE- TIM0_OUT0 #2 LE- TIM0_OUT1 #1 PCNT0_S0IN #2 PCNT0_S1IN #1           | US0_TX #2 US0_RX #1 US0_CLK #0 US0_CS #31 US0_CTS #30 US0_RTS #29 US1_TX #2 US1_RX #1 US1_CLK #0 US1_CS #31 US1_CTS #30 US1_RTS #29 LEU0_TX #2 LEU0_RX #1 I2C0_SDA #2 I2C0_SCL #1                                         | PRS_CH6 #2 PRS_CH7<br>#1 PRS_CH8 #0<br>PRS_CH9 #10<br>ACMP0_O #2<br>ACMP1_O #2               |

| QFN      | 48 Pin# and Name |                            | Pin Alternate Functi                                                                                                                                                                                                                        | onality / Description                                                                                                                                                                           |                                                                                                         |

|----------|------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Pin<br># | Pin Name         | Analog                     | Timers                                                                                                                                                                                                                                      | Communication                                                                                                                                                                                   | Other                                                                                                   |

| 32       | PB12             | BUSCX<br>BUSDY             | TIM0_CC0 #7 TIM0_CC1 #6 TIM0_CC2 #5 TIM0_CDTI0 #4 TIM0_CDTI1 #3 TIM0_CDTI2 #2 TIM1_CC0 #7 TIM1_CC1 #6 TIM1_CC2 #5 TIM1_CC3 #4 LE- TIM0_OUT0 #7 LE- TIM0_OUT1 #6 PCNT0_S0IN #7 PCNT0_S1IN #6                                                 | US0_TX #7 US0_RX #6 US0_CLK #5 US0_CS     #4 US0_CTS #3 US0_RTS #2 US1_TX     #7 US1_RX #6 US1_CLK #5 US1_CS     #4 US1_CTS #3 US1_RTS #2 LEU0_TX     #7 LEU0_RX #6 I2C0_SDA #7 I2C0_SCL     #6 | PRS_CH6 #7 PRS_CH7<br>#6 PRS_CH8 #5<br>PRS_CH9 #4 ACMP0_O<br>#7 ACMP1_O #7                              |

| 33       | PB13             | BUSCY<br>BUSDX             | TIM0_CC0 #8 TIM0_CC1 #7 TIM0_CC2 #6 TIM0_CDTI0 #5 TIM0_CDTI1 #4 TIM0_CDTI2 #3 TIM1_CC0 #8 TIM1_CC1 #7 TIM1_CC2 #6 TIM1_CC3 #5 LE- TIM0_OUT0 #8 LE- TIM0_OUT1 #7 PCNT0_S0IN #8 PCNT0_S1IN #7                                                 | US0_TX #8 US0_RX #7 US0_CLK #6 US0_CS     #5 US0_CTS #4 US0_RTS #3 US1_TX     #8 US1_RX #7 US1_CLK #6 US1_CS     #5 US1_CTS #4 US1_RTS #3 LEU0_TX     #8 LEU0_RX #7 I2C0_SDA #8 I2C0_SCL     #7 | PRS_CH6 #8 PRS_CH7<br>#7 PRS_CH8 #6<br>PRS_CH9 #5 ACMP0_O<br>#8 ACMP1_O #8<br>DBG_SWO #1<br>GPIO_EM4WU9 |

| 34       | AVDD_0           | Analog power supply 0.     |                                                                                                                                                                                                                                             |                                                                                                                                                                                                 |                                                                                                         |

| 35       | PB14             | LFXTAL_N<br>BUSCX<br>BUSDY | TIM0_CC0 #9 TIM0_CC1 #8 TIM0_CC2 #7 TIM0_CDTI0 #6 TIM0_CDTI1 #5 TIM0_CDTI2 #4 TIM1_CC0 #9 TIM1_CC1 #8 TIM1_CC2 #7 TIM1_CC3 #6 LE- TIM0_OUT0 #9 LE- TIM0_OUT1 #8 PCNT0_S0IN #9 PCNT0_S1IN #8                                                 | US0_TX #9 US0_RX #8 US0_CLK #7 US0_CS     #6 US0_CTS #5 US0_RTS #4 US1_TX     #9 US1_RX #8 US1_CLK #7 US1_CS     #6 US1_CTS #5 US1_RTS #4 LEU0_TX     #9 LEU0_RX #8 I2C0_SDA #9 I2C0_SCL     #8 | CMU_CLK1 #1 PRS_CH6 #9 PRS_CH7 #8 PRS_CH8 #7 PRS_CH9 #6 ACMP0_O #9 ACMP1_O #9                           |

| 36       | PB15             | LFXTAL_P<br>BUSCY<br>BUSDX | TIM0_CC0 #10     TIM0_CC1 #9     TIM0_CC2 #8     TIM0_CDTI0 #7     TIM0_CDTI1 #6     TIM0_CDTI2 #5     TIM1_CC0 #10     TIM1_CC1 #9     TIM1_CC2 #8     TIM1_CC3 #7 LE- TIM0_OUT0 #10 LE- TIM0_OUT1 #9     PCNT0_S0IN #10     PCNT0_S1IN #9 | US0_TX #10 US0_RX #9 US0_CLK #8 US0_CS #7 US0_CTS #6 US0_RTS #5 US1_TX #10 US1_RX #9 US1_CLK #8 US1_CS #7 US1_CTS #6 US1_RTS #5 LEU0_TX #10 LEU0_RX #9 I2C0_SDA #10 I2C0_SCL #9                 | CMU_CLK0 #1<br>PRS_CH6 #10<br>PRS_CH7 #9 PRS_CH8<br>#8 PRS_CH9 #7<br>ACMP0_O #10<br>ACMP1_O #10         |

| QFN      | 32 Pin# and Name |                             | Pin Alternate Functi                                                                                                                                                                                      | onality / Description                                                                                                                                                                                                     |                                                                                                                 |

|----------|------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Pin<br># | Pin Name         | Analog                      | Timers                                                                                                                                                                                                    | Communication                                                                                                                                                                                                             | Other                                                                                                           |

| 15       | PD14             | BUSCX<br>BUSDY              | TIM0_CC0 #22 TIM0_CC1 #21 TIM0_CC2 #20 TIM0_CDTI0 #19 TIM0_CDTI1 #18 TIM0_CDTI2 #17 TIM1_CC0 #22 TIM1_CC1 #21 TIM1_CC2 #20 TIM1_CC3 #19 LE- TIM0_OUT0 #22 LE- TIM0_OUT1 #21 PCNT0_S0IN #22 PCNT0_S1IN #21 | US0_TX #22 US0_RX<br>#21 US0_CLK #20<br>US0_CS #19 US0_CTS<br>#18 US0_RTS #17<br>US1_TX #22 US1_RX<br>#21 US1_CLK #20<br>US1_CS #19 US1_CTS<br>#18 US1_RTS #17<br>LEU0_TX #22 LEU0_RX<br>#21 I2C0_SDA #22<br>I2C0_SCL #21 | CMU_CLK0 #5<br>PRS_CH3 #13<br>PRS_CH4 #5 PRS_CH5<br>#4 PRS_CH6 #16<br>ACMP0_O #22<br>ACMP1_O #22<br>GPIO_EM4WU4 |

| 16       | PD15             | BUSCY<br>BUSDX              | TIM0_CC0 #23 TIM0_CC1 #22 TIM0_CC2 #21 TIM0_CDTI0 #20 TIM0_CDTI1 #19 TIM0_CDTI2 #18 TIM1_CC0 #23 TIM1_CC1 #22 TIM1_CC2 #21 TIM1_CC3 #20 LE- TIM0_OUT0 #23 LE- TIM0_OUT1 #22 PCNT0_S0IN #23 PCNT0_S1IN #22 | US0_TX #23 US0_RX<br>#22 US0_CLK #21<br>US0_CS #20 US0_CTS<br>#19 US0_RTS #18<br>US1_TX #23 US1_RX<br>#22 US1_CLK #21<br>US1_CS #20 US1_CTS<br>#19 US1_RTS #18<br>LEU0_TX #23 LEU0_RX<br>#22 I2C0_SDA #23<br>I2C0_SCL #22 | CMU_CLK1 #5<br>PRS_CH3 #14<br>PRS_CH4 #6 PRS_CH5<br>#5 PRS_CH6 #17<br>ACMP0_O #23<br>ACMP1_O #23<br>DBG_SWO #2  |

| 17       | PA0              | ADC0_EXTN<br>BUSCX<br>BUSDY | TIM0_CC0 #0 TIM0_CC1 #31 TIM0_CC2 #30 TIM0_CDTI0 #29 TIM0_CDTI1 #28 TIM0_CDTI2 #27 TIM1_CC0 #0 TIM1_CC1 #31 TIM1_CC2 #30 TIM1_CC3 #29 LE- TIM0_OUT0 #0 LE- TIM0_OUT1 #31 PCNT0_S0IN #0 PCNT0_S1IN #31     | US0_TX #0 US0_RX<br>#31 US0_CLK #30<br>US0_CS #29 US0_CTS<br>#28 US0_RTS #27<br>US1_TX #0 US1_RX<br>#31 US1_CLK #30<br>US1_CS #29 US1_CTS<br>#28 US1_RTS #27<br>LEU0_TX #0 LEU0_RX<br>#31 I2C0_SDA #0<br>I2C0_SCL #31     | CMU_CLK1 #0 PRS_CH6 #0 PRS_CH7 #10 PRS_CH8 #9 PRS_CH9 #8 ACMP0_O #0 ACMP1_O #0                                  |

| 18       | PA1              | ADC0_EXTP<br>BUSCY<br>BUSDX | TIM0_CC0 #1 TIM0_CC1 #0 TIM0_CC2 #31 TIM0_CDTI0 #30 TIM0_CDTI1 #29 TIM0_CDTI2 #28 TIM1_CC0 #1 TIM1_CC1 #0 TIM1_CC2 #31 TIM1_CC3 #30 LE- TIM0_OUT0 #1 LE- TIM0_OUT1 #0 PCNT0_S0IN #1 PCNT0_S1IN #0         | US0_TX #1 US0_RX #0 US0_CLK #31 US0_CS #30 US0_CTS #29 US0_RTS #28 US1_TX #1 US1_RX #0 US1_CLK #31 US1_CS #30 US1_CTS #29 US1_RTS #28 LEU0_TX #1 LEU0_RX #0 I2C0_SDA #1 I2C0_SCL #0                                       | CMU_CLK0 #0 PRS_CH6 #1 PRS_CH7 #0 PRS_CH8 #10 PRS_CH9 #9 ACMP0_O #1 ACMP1_O #1                                  |

| QFN      | 32 Pin# and Name | Pin Alternate Functionality / Description |                                                                                                                                                                                                           |                                                                                                                                                                                                                           |                                                                                                  |  |  |  |  |  |

|----------|------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin<br># | Pin Name         | Analog                                    | Timers                                                                                                                                                                                                    | Communication                                                                                                                                                                                                             | Other                                                                                            |  |  |  |  |  |

| 30       | PC9              | BUSAY<br>BUSBX                            | TIM0_CC0 #14 TIM0_CC1 #13 TIM0_CC2 #12 TIM0_CDTI0 #11 TIM0_CDTI1 #10 TIM0_CDTI2 #9 TIM1_CC0 #14 TIM1_CC1 #13 TIM1_CC2 #12 TIM1_CC3 #11 LE- TIM0_OUT0 #14 LE- TIM0_OUT1 #13 PCNT0_S0IN #14 PCNT0_S1IN #13  | US0_TX #14 US0_RX<br>#13 US0_CLK #12<br>US0_CS #11 US0_CTS<br>#10 US0_RTS #9<br>US1_TX #14 US1_RX<br>#13 US1_CLK #12<br>US1_CS #11 US1_CTS<br>#10 US1_RTS #9<br>LEU0_TX #14 LEU0_RX<br>#13 I2C0_SDA #14<br>I2C0_SCL #13   | PRS_CH0 #11 PRS_CH9 #14 PRS_CH10 #3 PRS_CH11 #2 ACMP0_O #14 ACMP1_O #14                          |  |  |  |  |  |

| 31       | PC10             | BUSAX<br>BUSBY                            | TIM0_CC0 #15 TIM0_CC1 #14 TIM0_CC2 #13 TIM0_CDTI0 #12 TIM0_CDTI1 #11 TIM0_CDTI2 #10 TIM1_CC0 #15 TIM1_CC1 #14 TIM1_CC2 #13 TIM1_CC3 #12 LE- TIM0_OUT0 #15 LE- TIM0_OUT1 #14 PCNT0_S0IN #15 PCNT0_S1IN #14 | US0_TX #15 US0_RX<br>#14 US0_CLK #13<br>US0_CS #12 US0_CTS<br>#11 US0_RTS #10<br>US1_TX #15 US1_RX<br>#14 US1_CLK #13<br>US1_CS #12 US1_CTS<br>#11 US1_RTS #10<br>LEU0_TX #15 LEU0_RX<br>#14 I2C0_SDA #15<br>I2C0_SCL #14 | CMU_CLK1 #3 PRS_CH0 #12 PRS_CH9 #15 PRS_CH10 #4 PRS_CH11 #3 ACMP0_O #15 ACMP1_O #15 GPIO_EM4WU12 |  |  |  |  |  |

| 32       | PC11             | BUSAY<br>BUSBX                            | TIM0_CC0 #16 TIM0_CC1 #15 TIM0_CC2 #14 TIM0_CDTI0 #13 TIM0_CDTI1 #12 TIM0_CDTI2 #11 TIM1_CC0 #16 TIM1_CC1 #15 TIM1_CC2 #14 TIM1_CC3 #13 LE- TIM0_OUT0 #16 LE- TIM0_OUT1 #15 PCNT0_S0IN #16 PCNT0_S1IN #15 | US0_TX #16 US0_RX<br>#15 US0_CLK #14<br>US0_CS #13 US0_CTS<br>#12 US0_RTS #11<br>US1_TX #16 US1_RX<br>#15 US1_CLK #14<br>US1_CS #13 US1_CTS<br>#12 US1_RTS #11<br>LEU0_TX #16 LEU0_RX<br>#15 I2C0_SDA #16<br>I2C0_SCL #15 | CMU_CLK0 #3 PRS_CH0 #13 PRS_CH9 #16 PRS_CH10 #5 PRS_CH11 #4 ACMP0_O #16 ACMP1_O #16 DBG_SWO #3   |  |  |  |  |  |

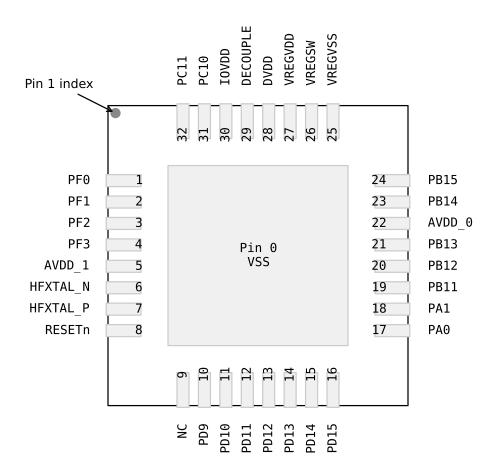

## 6.3 EFM32PG1 QFN32 with DC-DC Definition

Figure 6.3. EFM32PG1 QFN32 with DC-DC Pinout

## 6.3.1 EFM32PG1 QFN32 with DC-DC GPIO Overview

The GPIO pins are organized as 16-bit ports indicated by letters (A, B, C...), and the individual pins on each port are indicated by a number from 15 down to 0.

Table 6.6. QFN32 with DC-DC GPIO Pinout

| Port   | Pin<br>15    | Pin<br>14    | Pin<br>13    | Pin<br>12    | Pin<br>11    | Pin<br>10    | Pin 9       | Pin 8 | Pin 7 | Pin 6 | Pin 5 | Pin 4 | Pin 3       | Pin 2       | Pin 1       | Pin 0       |

|--------|--------------|--------------|--------------|--------------|--------------|--------------|-------------|-------|-------|-------|-------|-------|-------------|-------------|-------------|-------------|

| Port A | -            | -            | -            | -            | -            | -            | -           | -     | -     | -     | -     | -     | -           | -           | PA1         | PA0         |

| Port B | PB15         | PB14         | PB13<br>(5V) | PB12<br>(5V) | PB11<br>(5V) | -            | -           | -     | -     | -     | -     | -     | -           | -           | -           | -           |

| Port C | -            | -            | -            | -            | PC11<br>(5V) | PC10<br>(5V) | -           | -     | -     | -     | -     | -     | -           | -           | -           | -           |

| Port D | PD15<br>(5V) | PD14<br>(5V) | PD13<br>(5V) | PD12<br>(5V) | PD11<br>(5V) | PD10<br>(5V) | PD9<br>(5V) | -     | -     | -     | -     | -     | -           | -           | -           | -           |

| Port F | _            | -            | -            | -            | -            | -            | _           | -     | -     | -     | -     | -     | PF3<br>(5V) | PF2<br>(5V) | PF1<br>(5V) | PF0<br>(5V) |

## Note:

- 1. GPIO with 5V tolerance are indicated by (5V).

- 2. The pins PB13, PB12, PB11, PD15, PD14, and PD13 will not be 5V tolerant on all future devices. In order to preserve upgrade options with full hardware compatibility, do not use these pins with 5V domains.

| Alternate     | LOCATION                                 |                                          |                                           |                                              |                                             |                                              |                                          |                                          |                                                         |  |

|---------------|------------------------------------------|------------------------------------------|-------------------------------------------|----------------------------------------------|---------------------------------------------|----------------------------------------------|------------------------------------------|------------------------------------------|---------------------------------------------------------|--|

| Functionality | 0 - 3                                    | 4 - 7                                    | 8 - 11                                    | 12 - 15                                      | 16 - 19                                     | 20 - 23                                      | 24 - 27                                  | 28 - 31                                  | Description                                             |  |

| PRS_CH1       | 0: PF1<br>1: PF2<br>2: PF3<br>3: PF4     | 4: PF5<br>5: PF6<br>6: PF7<br>7: PF0     |                                           |                                              |                                             |                                              |                                          |                                          | Peripheral Reflex<br>System PRS, chan-<br>nel 1.        |  |

| PRS_CH2       | 0: PF2<br>1: PF3<br>2: PF4<br>3: PF5     | 4: PF6<br>5: PF7<br>6: PF0<br>7: PF1     |                                           |                                              |                                             |                                              |                                          |                                          | Peripheral Reflex<br>System PRS, chan-<br>nel 2.        |  |

| PRS_CH3       | 0: PF3<br>1: PF4<br>2: PF5<br>3: PF6     | 4: PF7<br>5: PF0<br>6: PF1<br>7: PF2     | 8: PD9<br>9: PD10<br>10: PD11<br>11: PD12 | 12: PD13<br>13: PD14<br>14: PD15             |                                             |                                              |                                          |                                          | Peripheral Reflex<br>System PRS, chan-<br>nel 3.        |  |

| PRS_CH4       | 0: PD9<br>1: PD10<br>2: PD11<br>3: PD12  | 4: PD13<br>5: PD14<br>6: PD15            |                                           |                                              |                                             |                                              |                                          |                                          | Peripheral Reflex<br>System PRS, chan-<br>nel 4.        |  |

| PRS_CH5       | 0: PD10<br>1: PD11<br>2: PD12<br>3: PD13 | 4: PD14<br>5: PD15<br>6: PD9             |                                           |                                              |                                             |                                              |                                          |                                          | Peripheral Reflex<br>System PRS, chan-<br>nel 5.        |  |

| PRS_CH6       | 0: PA0<br>1: PA1<br>2: PA2<br>3: PA3     | 4: PA4<br>5: PA5<br>6: PB11<br>7: PB12   | 8: PB13<br>9: PB14<br>10: PB15<br>11: PD9 | 12: PD10<br>13: PD11<br>14: PD12<br>15: PD13 | 16: PD14<br>17: PD15                        |                                              |                                          |                                          | Peripheral Reflex<br>System PRS, chan-<br>nel 6.        |  |

| PRS_CH7       | 0: PA1<br>1: PA2<br>2: PA3<br>3: PA4     | 4: PA5<br>5: PB11<br>6: PB12<br>7: PB13  | 8: PB14<br>9: PB15<br>10: PA0             |                                              |                                             |                                              |                                          |                                          | Peripheral Reflex<br>System PRS, chan-<br>nel 7.        |  |

| PRS_CH8       | 0: PA2<br>1: PA3<br>2: PA4<br>3: PA5     | 4: PB11<br>5: PB12<br>6: PB13<br>7: PB14 | 8: PB15<br>9: PA0<br>10: PA1              |                                              |                                             |                                              |                                          |                                          | Peripheral Reflex<br>System PRS, chan-<br>nel 8.        |  |

| PRS_CH9       | 0: PA3<br>1: PA4<br>2: PA5<br>3: PB11    | 4: PB12<br>5: PB13<br>6: PB14<br>7: PB15 | 8: PA0<br>9: PA1<br>10: PA2<br>11: PC6    | 12: PC7<br>13: PC8<br>14: PC9<br>15: PC10    | 16: PC11                                    |                                              |                                          |                                          | Peripheral Reflex<br>System PRS, chan-<br>nel 9.        |  |

| PRS_CH10      | 0: PC6<br>1: PC7<br>2: PC8<br>3: PC9     | 4: PC10<br>5: PC11                       |                                           |                                              |                                             |                                              |                                          |                                          | Peripheral Reflex<br>System PRS, chan-<br>nel 10.       |  |

| PRS_CH11      | 0: PC7<br>1: PC8<br>2: PC9<br>3: PC10    | 4: PC11<br>5: PC6                        |                                           |                                              |                                             |                                              |                                          |                                          | Peripheral Reflex<br>System PRS, chan-<br>nel 11.       |  |

| TIM0_CC0      | 0: PA0<br>1: PA1<br>2: PA2<br>3: PA3     | 4: PA4<br>5: PA5<br>6: PB11<br>7: PB12   | 8: PB13<br>9: PB14<br>10: PB15<br>11: PC6 | 12: PC7<br>13: PC8<br>14: PC9<br>15: PC10    | 16: PC11<br>17: PD9<br>18: PD10<br>19: PD11 | 20: PD12<br>21: PD13<br>22: PD14<br>23: PD15 | 24: PF0<br>25: PF1<br>26: PF2<br>27: PF3 | 28: PF4<br>29: PF5<br>30: PF6<br>31: PF7 | Timer 0 Capture<br>Compare input /<br>output channel 0. |  |

| TIM0_CC1      | 0: PA1<br>1: PA2<br>2: PA3<br>3: PA4     | 4: PA5<br>5: PB11<br>6: PB12<br>7: PB13  | 8: PB14<br>9: PB15<br>10: PC6<br>11: PC7  | 12: PC8<br>13: PC9<br>14: PC10<br>15: PC11   | 16: PD9<br>17: PD10<br>18: PD11<br>19: PD12 | 20: PD13<br>21: PD14<br>22: PD15<br>23: PF0  | 24: PF1<br>25: PF2<br>26: PF3<br>27: PF4 | 28: PF5<br>29: PF6<br>30: PF7<br>31: PA0 | Timer 0 Capture<br>Compare input /<br>output channel 1. |  |

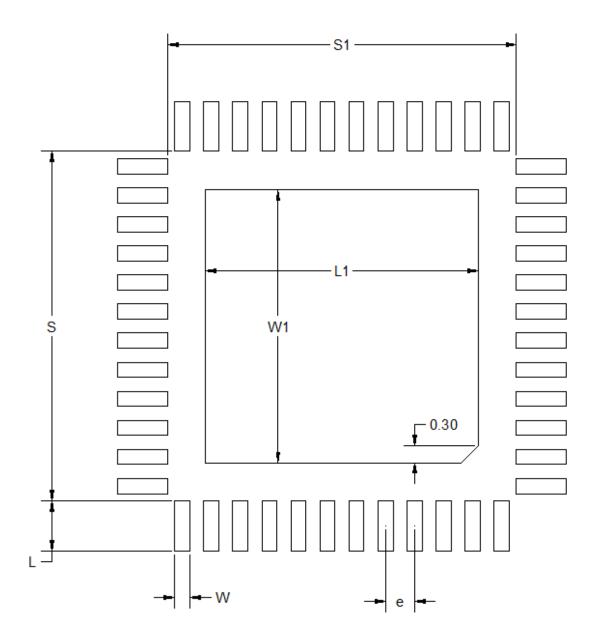

# 7.2 QFN48 PCB Land Pattern

Figure 7.2. QFN48 PCB Land Pattern Drawing

# 9.7 Revision 0.1

Initial release.