Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | HC08                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | SCI, SPI                                                              |

| Peripherals                | LVD, POR, PWM                                                         |

| Number of I/O              | 36                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | · ·                                                                   |

| RAM Size                   | 512 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 8x8b                                                              |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 44-QFP                                                                |

| Supplier Device Package    | 44-QFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908gt16cfbe |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History (Sheet 2 of 2)**

| Date               | Revision<br>Level                       | Description                                                                                                                                                                                                                                       | Page<br>Number(s)               |

|--------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|                    |                                         | Chapter 15 System Integration Module (SIM) — Clarified SIM features and functionality                                                                                                                                                             | 179, 182,<br>183, 184           |

|                    |                                         | 15.7.2 SIM Reset Status Register — Clarified SRSR operation                                                                                                                                                                                       | 194                             |

|                    |                                         | Table 19-1. Monitor Mode Signal Requirements and Options — Reworked                                                                                                                                                                               | 247                             |

|                    |                                         | 19.2.1 Functional Description — Corrected Break description                                                                                                                                                                                       | 237, 240                        |

|                    | 3.0                                     | 19.3 Monitor Module (MON) — Reworked                                                                                                                                                                                                              | 243                             |

| September,<br>2004 | (Continued<br>from<br>previous<br>page) | Chapter 20 Electrical Specifications — Revised/added tables:<br>20.5 5.0-V DC Electrical Characteristics<br>20.6 3.0-V DC Electrical Characteristics<br>20.7 Supply Current Characteristics<br>20.8 5-V Control Timing<br>20.9 3-V Control Timing | 257<br>258<br>259<br>260<br>260 |

|                    |                                         | 20.20 Memory Characteristics — Updated memory table                                                                                                                                                                                               | 273                             |

|                    |                                         | Chapter 20 Electrical Specifications — Added figures:<br>Figure 20-1. RST and IRQ Timing<br>Figure 20-2. RST and IRQ Timing                                                                                                                       | 260<br>260                      |

| March,<br>2006     | 4.0                                     | Appendix A MC68HC08GT16 — Introduces the MC68HC08GT16, the ROM part equivalent to the MC68HC908GT16.                                                                                                                                              | 281                             |

|                    |                                         | 4.2 Functional Description — In the description of the COP Rate Select Bit corrected the values for COP timeout period                                                                                                                            | 57                              |

|                    |                                         | Figure 5-1. COP Block Diagram — Replaced BUSCLKX4 with COPCLK                                                                                                                                                                                     | 61                              |

| April,             |                                         | 14.9.1 ESCI Arbiter Control Register — Replaced one half with one quarter in definition for ACLK = 0                                                                                                                                              | 176                             |

| 2007               | 5.0                                     | 14.9.3 Bit Time Measurement — Replaced one half with one quarter in definition for ACLK = $0$                                                                                                                                                     | 177                             |

|                    |                                         | Revised the following diagrams:<br>Figure 19-10. Forced Monitor Mode (Low)<br>Figure 19-11. Forced Monitor Mode (High)<br>Figure 19-12. Standard Monitor Mode                                                                                     | 245<br>245<br>246               |

**Table of Contents**

Chapter 3 Analog-to-Digital Converter (ADC)

| 3.1   | Introduction                                         | 49 |

|-------|------------------------------------------------------|----|

| 3.2   | Features                                             | 49 |

| 3.3   | Functional Description                               | 49 |

| 3.3.1 | ADC Port I/O Pins                                    | 49 |

| 3.3.2 | ADC Port I/O Pins                                    |    |

| 3.3.3 | Voltage Conversion                                   |    |

| 3.3.4 |                                                      |    |

| 3.3.5 |                                                      |    |

| 3.3.6 | Accuracy and Precision                               |    |

| 3.4   | Interrupts                                           | 52 |

| 3.5   | Low-Power Modes                                      |    |

| 3.5.1 | Wait Mode                                            |    |

| 3.5.2 | Stop Mode                                            | 53 |

| 3.6   | I/O Signals                                          | 53 |

| 3.6.1 | ADC Analog Power Pin (V <sub>DDA</sub> )             |    |

| 3.6.2 | ADC Analog Ground Pin (V <sub>SSA</sub> )            |    |

| 3.6.3 | ADC Voltage Reference High Pin (V <sub>REFH</sub> ). |    |

| 3.6.4 | ADC Voltage Reference Low Pin (V <sub>REFL</sub> )   |    |

| 3.6.5 | ADC Voltage In (V <sub>ADIN</sub> )                  |    |

| 3.7   | I/O Registers                                        |    |

| 3.7.1 | ADC Status and Control Register                      |    |

| 3.7.2 | ADC Data Register.                                   |    |

| 3.7.3 | ADC Clock Register                                   | 56 |

### Chapter 4 Configuration Register (CONFIG)

| 4.1 | Introduction           | 57 |

|-----|------------------------|----|

| 4.2 | Functional Description | 57 |

## Chapter 5

## Computer Operating Properly (COP) Module

| 5.1   |                         | 61 |

|-------|-------------------------|----|

| 5.2   | Functional Description  | 61 |

| 5.3   | I/O Signals             |    |

| 5.3.1 |                         |    |

| 5.3.2 | STOP Instruction        |    |

| 5.3.3 | COPCTL Write            |    |

| 5.3.4 | Power-On Reset.         |    |

| 5.3.5 | Internal Reset.         |    |

| 5.3.6 | Reset Vector Fetch      |    |

| 5.3.7 | COPD (COP Disable).     | 63 |

| 5.3.8 | COPRS (COP Rate Select) | 63 |

| 5.4   | COP Control Register    | 63 |

| 5.5   | Interrupts              | 63 |

Input/Output (I/O) Section

| \$FE0C                               | LVI STATUS REGISTER (LVISR)                                                                    |

|--------------------------------------|------------------------------------------------------------------------------------------------|

| \$FE0D<br>↓<br>\$FE0F                | UNIMPLEMENTED<br>3 BYTES                                                                       |

| \$FE10<br>↓<br>\$FE1F                | UNIMPLEMENTED<br>16 BYTES<br>RESERVED FOR COMPATIBILITY WITH MONITOR CODE<br>FOR A-FAMILY PART |

| \$FE20<br>↓<br>\$FF4F                | MONITOR ROM<br>304 BYTES                                                                       |

| \$FF50<br>↓<br>\$FF7D                | UNIMPLEMENTED<br>46 BYTES                                                                      |

| \$FF7E                               | FLASH BLOCK PROTECT REGISTER (FLBPR)                                                           |

| \$FF7F                               | UNIMPLEMENTED 1 BYTE                                                                           |

| \$FF80                               | ICG USER TRIM REGISTER 5V (ICGTR5)                                                             |

| \$FF81                               | ICG USER TRIM REGISTER 3V (ICGTR3)                                                             |

| \$FF82<br>↓<br>\$FFDB                | UNIMPLEMENTED<br>90 BYTES                                                                      |

| \$FFDC<br>↓<br>\$FFFF <sup>(2)</sup> | FLASH VECTORS<br>36 BYTES                                                                      |

2. \$FFF6-\$FFFD reserved for eight security bytes

Figure 2-1. Memory Map (Continued)

#### Memory

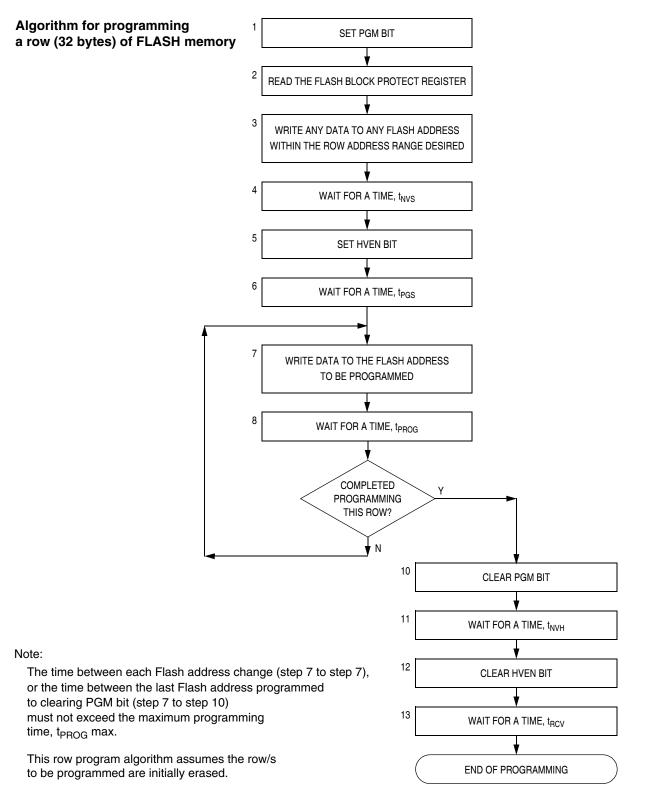

Figure 2-4. Flash Programming Flowchart

### 3.5.2 Stop Mode

The ADC module is inactive after the execution of a STOP instruction. Any pending conversion is aborted. ADC conversions resume when the MCU exits stop mode after an external interrupt. Allow one conversion cycle to stabilize the analog circuitry.

## 3.6 I/O Signals

The ADC module has eight pins shared with port B, PTB7/AD7–PTB0/AD0.

### 3.6.1 ADC Analog Power Pin (V<sub>DDA</sub>)

The ADC analog portion uses  $V_{DDA}$  as its power pin. Connect the  $V_{DDA}$  pin to the same voltage potential as  $V_{DD}$ . External filtering may be necessary to ensure clean  $V_{DDA}$  for good results.

NOTE

For maximum noise immunity, route V<sub>DDA</sub> carefully and place bypass capacitors as close as possible to the package.

### 3.6.2 ADC Analog Ground Pin (V<sub>SSA</sub>)

The ADC analog portion uses  $V_{SSA}$  as its ground pin. Connect the  $V_{SSA}$  pin to the same voltage potential as  $V_{SS}$ .

NOTE

Route V<sub>SSA</sub> cleanly to avoid any offset errors.

### 3.6.3 ADC Voltage Reference High Pin (V<sub>REFH</sub>)

The ADC analog portion uses  $V_{REFH}$  as its upper voltage reference pin. The  $V_{REFH}$  pin must be connected to the same voltage potential as  $V_{DDA}$ . External filtering is often necessary to ensure a clean  $V_{REFH}$  for good results. Any noise present on this pin will be reflected and possibly magnified in A/D conversion values.

### NOTE

For maximum noise immunity, route  $V_{REFH}$  carefully and place bypass capacitors as close as possible to the package. Routing  $V_{REFH}$  close and parallel to  $V_{REFL}$  may improve common mode noise rejection.

### 3.6.4 ADC Voltage Reference Low Pin (V<sub>REFL</sub>)

The ADC analog portion uses  $V_{REFL}$  as its lower voltage reference pin. The  $V_{REFL}$  pin must be connected to the same voltage potential as  $V_{SSA}$ . External filtering is often necessary to ensure a clean  $V_{REFL}$  for good results. Any noise present on this pin will be reflected and possibly magnified in A/D conversion values.

### NOTE

For maximum noise immunity, route  $V_{REFL}$  carefully and, if not connected to  $V_{SS}$ , place bypass capacitors as close as possible to the package. Routing  $V_{REFH}$  close and parallel to  $V_{REFL}$  may improve common mode noise rejection.

**Central Processor Unit (CPU)**

## 6.7 Instruction Set Summary

Table 6-1 provides a summary of the M68HC08 instruction set.

| Source                                                                                                   | Operation                                               | Description                                                           |   |   | Effe<br>on C |   |   |           | Address<br>Mode                                                                                          | Opcode                                           | Operand                                            | les                   |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------|---|---|--------------|---|---|-----------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------|-----------------------|

| Form                                                                                                     |                                                         |                                                                       | ۷ | н | I            | Ν | z | С         | Add                                                                                                      | odo                                              | Ope                                                | Cycles                |

| ADC #opr<br>ADC opr<br>ADC opr<br>ADC opr,X<br>ADC opr,X<br>ADC ,X<br>ADC ,X<br>ADC opr,SP<br>ADC opr,SP | Add with Carry                                          | A ← (A) + (M) + (C)                                                   | ţ | ţ | _            | ţ | ţ | ţ         | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                                      | A9<br>B9<br>C9<br>D9<br>E9<br>F9<br>9EE9<br>9ED9 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff          | 2 3 4 4 3 2 4 5       |

| ADD #opr<br>ADD opr<br>ADD opr,<br>ADD opr,X<br>ADD opr,X<br>ADD opr,SP<br>ADD opr,SP                    | Add without Carry                                       | A ← (A) + (M)                                                         | ţ | Ţ | _            | ţ | ţ | ţ         | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                                      | AB<br>BB<br>CB<br>DB<br>EB<br>FB<br>9EEB<br>9EDB |                                                    | 23443245              |

| AIS #opr                                                                                                 | Add Immediate Value (Signed) to SP                      | $SP \leftarrow (SP) + (16 \ \ensuremath{M})$                          | - | - | -            | - | - | -         | IMM                                                                                                      | A7                                               | ii                                                 | 2                     |

| AIX #opr                                                                                                 | Add Immediate Value (Signed) to H:X                     | $H:X \leftarrow (H:X) + (16 \mathrel{\scriptstyle{\triangleleft}} M)$ | - | - | -            | - | - | -         | IMM                                                                                                      | AF                                               | ii                                                 | 2                     |

| AND #opr<br>AND opr<br>AND opr,X<br>AND opr,X<br>AND opr,X<br>AND,X<br>AND opr,SP<br>AND opr,SP          | Logical AND                                             | A ← (A) & (M)                                                         | 0 | _ | _            | ţ | ţ | _         | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                                      | A4<br>B4<br>C4<br>D4<br>E4<br>F4<br>9EE4<br>9ED4 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff    | 23443245              |

| ASL opr<br>ASLA<br>ASLX<br>ASL opr,X<br>ASL ,X<br>ASL ,X                                                 | Arithmetic Shift Left<br>(Same as LSL)                  |                                                                       | ţ | _ | _            | ţ | ţ | ţ         | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                                    | 38<br>48<br>58<br>68<br>78<br>9E68               | dd<br>ff<br>ff                                     | 4<br>1<br>4<br>3<br>5 |

| ASR opr<br>ASRA<br>ASRX<br>ASR opr,X<br>ASR opr,X<br>ASR opr,SP                                          | Arithmetic Shift Right                                  |                                                                       | ţ | _ | _            | ţ | ţ | ţ         | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                                    | 37<br>47<br>57<br>67<br>77<br>9E67               | dd<br>ff<br>ff                                     | 4<br>1<br>4<br>3<br>5 |

| BCC rel                                                                                                  | Branch if Carry Bit Clear                               | $PC \leftarrow (PC) + 2 + rel ? (C) = 0$                              | - | - | -            | - | - | -         | REL                                                                                                      | 24                                               | rr                                                 | 3                     |

| BCLR n, opr                                                                                              | Clear Bit n in M                                        | Mn ← 0                                                                | _ | _ | _            | _ | _ | _         | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 11<br>13<br>15<br>17<br>19<br>1B<br>1D<br>1F     | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd | 4 4 4 4 4 4 4 4       |

| BCS rel                                                                                                  | Branch if Carry Bit Set (Same as BLO)                   | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) = 1$                     | - | - | -            | - | - | -         | REL                                                                                                      | 25                                               | rr                                                 | 3                     |

| BEQ rel                                                                                                  | Branch if Equal                                         | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (Z) = 1$                     | - | - | -            | - | - | -         | REL                                                                                                      | 27                                               | rr                                                 | 3                     |

| BGE opr                                                                                                  | Branch if Greater Than or Equal To<br>(Signed Operands) | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (N \oplus V) = 0$            | - | - | _            | - | - | -         | REL                                                                                                      | 90                                               | rr                                                 | 3                     |

| BGT <i>opr</i>                                                                                           | Branch if Greater Than (Signed<br>Operands)             | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (Z) \mid (N \oplus V) = 0$   | - | - | _            | - | - | -         | REL                                                                                                      | 92                                               | rr                                                 | 3                     |

| BHCC rel                                                                                                 | Branch if Half Carry Bit Clear                          | $PC \leftarrow (PC) + 2 + rel? (H) = 0$                               | - | - | _            | - | - | <u> -</u> | REL                                                                                                      | 28                                               | rr                                                 | 3                     |

| BHCS rel                                                                                                 | Branch if Half Carry Bit Set                            | $PC \leftarrow (PC) + 2 + rel? (H) = 1$                               | - | - | -            | - | - | -         | REL                                                                                                      | 29                                               | rr                                                 | 3                     |

| BHI rel                                                                                                  | Branch if Higher                                        | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) \mid (Z) = 0$            | - | - | -            | - | - | -         | REL                                                                                                      | 22                                               | rr                                                 | 3                     |

### Table 6-1. Instruction Set Summary (Sheet 1 of 6)

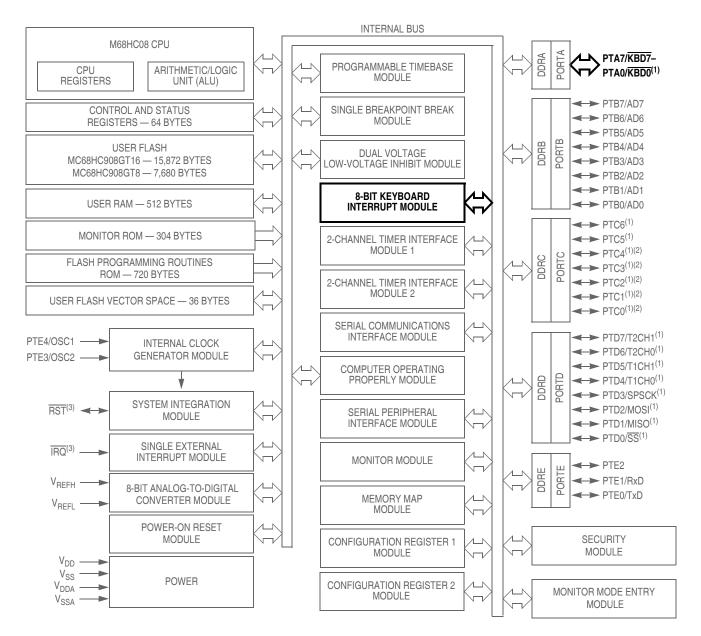

#### Internal Clock Generator (ICG) Module)

1. Ports are software configurable with pullup device if input port.

2. Higher current drive port pins

3. Pin contains integrated pullup device

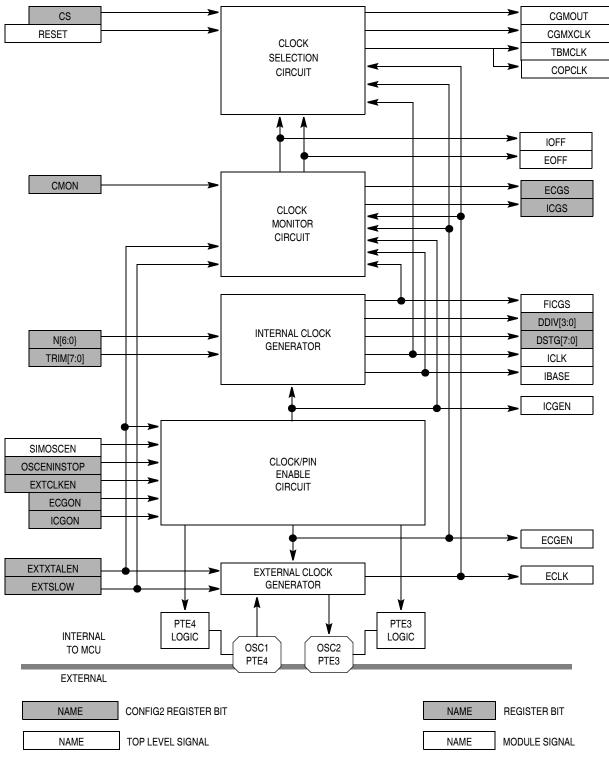

### Figure 7-1. Block Diagram Highlighting ICG Module and Pins

**Functional Description**

Figure 7-2. ICG Module Block Diagram

#### Internal Clock Generator (ICG) Module)

clock period tolerance plus 10 percent) must be added. This adjustment can be reduced with trimming. Table 7-3 shows some typical values for settling time.

| τ <sub>1</sub> | τ <b>2</b>     | Ν  | <sup>τ</sup> 15 | τ <b>5</b> | <sup>⊤</sup> tot |

|----------------|----------------|----|-----------------|------------|------------------|

| 1/ (6.45 MHz)  | 1/ (25.8 MHz)  | 84 | 430 μs          | 535 μs     | 850 μs           |

| 1/ (25.8 MHz)  | 1/ (6.45 MHz)  | 21 | 107 μs          | 212 μs     | 525 μs           |

| 1/ (25.8 MHz)  | 1/ (307.2 kHz) | 1  | 141 μs          | 246 μs     | 560 μs           |

| 1/ (307.2 kHz) | 1/ (25.8 MHz)  | 84 | 11.9 ms         | 12.0 ms    | 12.3 ms          |

Table 7-3. Typical Settling Time Examples

## 7.4.7 Trimming Frequency on the Internal Clock Generator

The unadjusted frequency of the low-frequency base clock (IBASE), when the comparators in the frequency comparator indicate zero error, will vary as much as  $\pm 25$  percent due to process, temperature, and voltage dependencies. These dependencies are in the voltage and current references, the offset of the comparators, and the internal capacitor.

The method of changing the unadjusted operating point is by changing the size of the capacitor. This capacitor is designed with 639 equally sized units. Of that number, 384 of these units are always connected. The remaining 255 units are put in by adjusting the ICG trim factor (TRIM). The default value for TRIM is \$80, or 128 units, making the default capacitor size 512. Each unit added or removed will adjust the output frequency by about  $\pm 0.195$  percent of the unadjusted frequency (adding to TRIM will decrease frequency). Therefore, the frequency of IBASE can be changed to  $\pm 25$  percent of its unadjusted value, which is enough to cancel the process variability mentioned before.

The best way to trim the internal clock is to use the timer to measure the width of an input pulse on an input capture pin (this pulse must be supplied by the application and should be as long or wide as possible). Considering the prescale value of the timer and the theoretical (zero error) frequency of the bus (307.2 kHz \*N/4), the error can be calculated. This error, expressed as a percentage, can be divided by 0.195 percent and the resultant factor added or subtracted from TRIM. This process should be repeated to eliminate any residual error.

## 7.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power- consumption standby modes.

## 7.5.1 Wait Mode

The ICG remains active in wait mode. If enabled, the ICG interrupt to the CPU can bring the MCU out of wait mode.

In some applications, low power-consumption is desired in wait mode and a high-frequency clock is not needed. In these applications, reduce power consumption by either selecting a low-frequency external clock and turn the internal clock generator off or reduce the bus frequency by minimizing the ICG multiplier factor (N) before executing the WAIT instruction.

Internal Clock Generator (ICG) Module)

## 7.6.3 Slow External Clock (EXTSLOW)

Slow external clock (EXTSLOW), when set, will decrease the drive strength of the oscillator amplifier, enabling low-frequency crystal operation (30 kHz–100 kHz) if properly enabled with the external clock enable (EXTCLKEN) and external crystal enable (EXTXTALEN) bits. When clear, EXTSLOW enables high-frequency crystal operation (1 MHz to 8 MHz).

EXTSLOW, when set, also configures the clock monitor to expect an external clock source that is slower than the low-frequency base clock (60 Hz to 307.2 kHz). When EXTSLOW is clear, the clock monitor will expect an external clock faster than the low-frequency base clock (307.2 kHz to 32 MHz).

The default state for this option is clear.

## 7.6.4 Oscillator Enable In Stop (OSCENINSTOP)

Oscillator enable in stop (OSCENINSTOP), when set, will enable the ICG to continue to generate clocks (either CGMXCLK, CGMOUT, COPCLK, or TBMCLK) in stop mode. This function is used to keep the timebase and COP running while the rest of the microcontroller stops. The clock monitor and autoswitching functions remain operative.

When OSCENINSTOP is clear, all clock generation will cease and CGMXCLK, CGMOUT, COPCLK, and TBMCLK will be forced low during stop mode. The clock monitor and autoswitching functions become inoperative.

The default state for this option is clear.

## 7.7 Input/Output (I/O) Registers

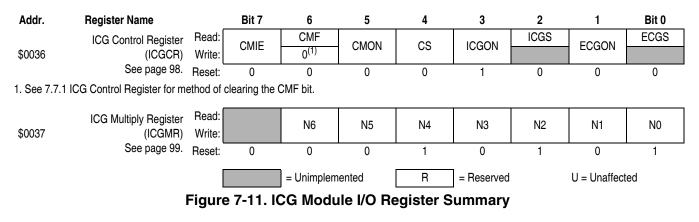

The ICG contains five registers, summarized in Figure 7-11. These registers are:

- 1. ICG control register (ICGCR)

- 2. ICG multiplier register (ICGMR)

- 3. ICG trim register (ICGTR)

- 4. ICG DCO divider control register (ICGDVR)

- 5. ICG DCO stage control register (ICGDSR)

Several of the bits in these registers have interaction where the state of one bit may force another bit to a particular state or prevent another bit from being set or cleared. A summary of this interaction is shown in Table 7-4.

#### Keyboard Interrupt Module (KBI)

1. Ports are software configurable with pullup device if input port.

2. Higher current drive port pins

3. Pin contains integrated pullup device

### Figure 9-1. Block Diagram Highlighting KBI Block and Pins

#### Low-Power Modes (MODES)

### 11.3.2 Stop Mode

The break module is inactive in stop mode. A break interrupt causes exit from stop mode and sets the SBSW bit in the break status register. The STOP instruction does not affect break module register states.

## 11.4 Central Processor Unit (CPU)

### 11.4.1 Wait Mode

The WAIT instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling interrupts. After exit from wait mode by interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

### 11.4.2 Stop Mode

The STOP instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling external interrupts. After exit from stop mode by external interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

After exiting stop mode, the CPU clock begins running after the oscillator stabilization delay.

## 11.5 Internal Clock Generator Module (ICG)

### 11.5.1 Wait Mode

The internal clock generator (ICG) module remains active in wait mode. If enabled, the ICG interrupt to the CPU can bring the MCU out of wait mode.

In some applications, low power-consumption is desired in wait mode and a high-frequency clock is not needed. In these applications, reduce power consumption by either selecting a low-frequency external clock and turn the internal clock generator off or reduce the bus frequency by minimizing the ICG multiplier factor (N) before executing the WAIT instruction.

### 11.5.2 Stop Mode

The value of the oscillator enable in stop (OSCENINSTOP) bit in the CONFIG2 register determines the behavior of the ICG in stop mode. If OSCENINSTOP is low, the ICG is disabled in stop and, upon execution of the STOP instruction, all ICG activity will cease and the output clocks (CGMXCLK, CGMOUT, COPCLK, and TBMCLK) will be held low. Power consumption will be minimal.

If OSCENINSTOP is high, the ICG is enabled in stop and activity will continue. This is useful if the timebase module (TBM) is required to bring the MCU out of stop mode. ICG interrupts will not bring the MCU out of stop mode in this case.

During stop mode, if OSCENINSTOP is low, several functions in the ICG are affected. The stable bits (ECGS and ICGS) are cleared, which will enable the external clock stabilization divider upon recovery. The clock monitor is disabled (CMON = 0) which will also clear the clock monitor interrupt enable (CMIE) and clock monitor flag (CMF) bits. The CS, ICGON, ECGON, N, TRIM, DDIV, and DSTG bits are unaffected.

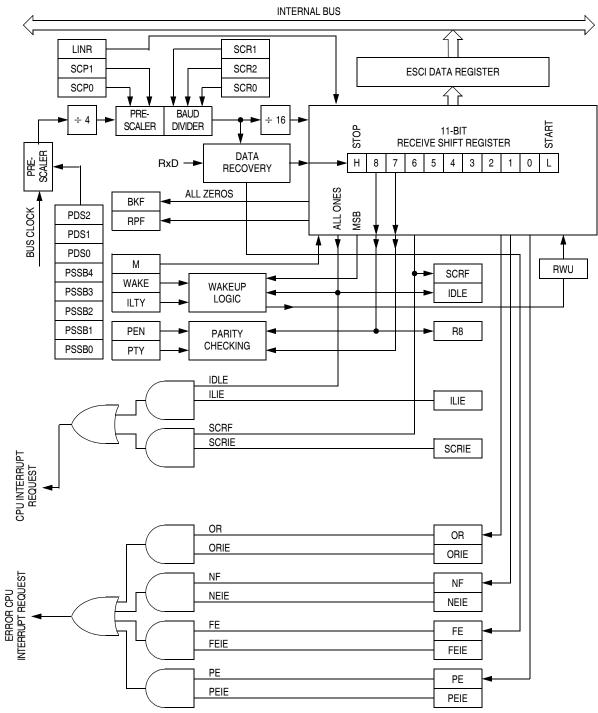

Enhanced Serial Communications Interface (ESCI) Module

#### Enhanced Serial Communications Interface (ESCI) Module

| RT8, RT9, and RT10 Samples | Data Bit Determination | Noise Flag |

|----------------------------|------------------------|------------|

| 000                        | 0                      | 0          |

| 001                        | 0                      | 1          |

| 010                        | 0                      | 1          |

| 011                        | 1                      | 1          |

| 100                        | 0                      | 1          |

| 101                        | 1                      | 1          |

| 110                        | 1                      | 1          |

| 111                        | 1                      | 0          |

### Table 14-3. Data Bit Recovery

NOTE

The RT8, RT9, and RT10 samples do not affect start bit verification. If any or all of the RT8, RT9, and RT10 start bit samples are 1s following a successful start bit verification, the noise flag (NF) is set and the receiver assumes that the bit is a start bit.

To verify a stop bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 14-4 summarizes the results of the stop bit samples.

| RT8, RT9, and RT10 Samples | Framing Error Flag | Noise Flag |

|----------------------------|--------------------|------------|

| 000                        | 1                  | 0          |

| 001                        | 1                  | 1          |

| 010                        | 1                  | 1          |

| 011                        | 0                  | 1          |

| 100                        | 1                  | 1          |

| 101                        | 0                  | 1          |

| 110                        | 0                  | 1          |

| 111                        | 0                  | 0          |

### Table 14-4. Stop Bit Recovery

### 14.4.3.4 Framing Errors

If the data recovery logic does not detect a 1 where the stop bit should be in an incoming character, it sets the framing error bit, FE, in SCS1. A break character also sets the FE bit because a break character has no stop bit. The FE bit is set at the same time that the SCRF bit is set.

### 14.4.3.5 Baud Rate Tolerance

A transmitting device may be operating at a baud rate below or above the receiver baud rate. Accumulated bit time misalignment can cause one of the three stop bit data samples to fall outside the actual stop bit. Then a noise error occurs. If more than one of the samples is outside the stop bit, a framing error occurs. In most applications, the baud rate tolerance is much more than the degree of misalignment that is likely to occur.

As the receiver samples an incoming character, it resynchronizes the RT clock on any valid falling edge within the character. Resynchronization within characters corrects misalignments between transmitter bit times and receiver bit times.

Enhanced Serial Communications Interface (ESCI) Module

## 14.9 ESCI Arbiter

The ESCI module comprises an arbiter module designed to support software for communication tasks as bus arbitration, baud rate recovery and break time detection. The arbiter module consists of an 9-bit counter with 1-bit overflow and control logic. The CPU can control operation mode via the ESCI arbiter control register (SCIACTL).

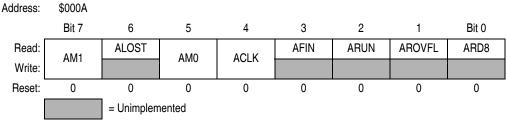

## 14.9.1 ESCI Arbiter Control Register

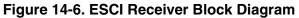

Figure 14-19. ESCI Arbiter Control Register (SCIACTL)

### AM1 and AM0 — Arbiter Mode Select Bits

These read/write bits select the mode of the arbiter module as shown in Table 14-12. Reset clears AM1 and AM0.

| AM[1:0] | ESCI Arbiter Mode     |

|---------|-----------------------|

| 0 0     | Idle / counter reset  |

| 0 1     | Bit time measurement  |

| 1 0     | Bus arbitration       |

| 1 1     | Reserved / do not use |

### Table 14-12. ESCI Arbiter Selectable Modes

### ALOST — Arbitration Lost Flag

This read-only bit indicates loss of arbitration. Clear ALOST by writing a 0 to AM1. Reset clears ALOST.

### ACLK — Arbiter Counter Clock Select Bit

This read/write bit selects the arbiter counter clock source. Reset clears ACLK.

- 1 = Arbiter counter is clocked with one half of the ESCI input clock generated by the ESCI prescaler

- 0 = Arbiter counter is clocked with one quarter of the bus clock

### AFIN— Arbiter Bit Time Measurement Finish Flag

This read-only bit indicates bit time measurement has finished. Clear AFIN by writing any value to SCIACTL. Reset clears AFIN.

- 1 = Bit time measurement has finished

- 0 = Bit time measurement not yet finished

### **ARUN**— Arbiter Counter Running Flag

This read-only bit indicates the arbiter counter is running. Reset clears ARUN.

1 = Arbiter counter running

0 = Arbiter counter stopped

#### System Integration Module (SIM)

### 15.2.2 Clock Startup from POR or LVI Reset

When the power-on reset module or the low-voltage inhibit module generates a reset, the clocks to the CPU and peripherals are inactive and held in an inactive phase until after the 4096 CGMXCLK cycle POR timeout has completed. The RST pin is driven low by the SIM during this entire period. The IBUS clocks start upon completion of the timeout.

### 15.2.3 Clocks in Stop Mode and Wait Mode

Upon exit from stop mode by an interrupt, break, or reset, the SIM allows CGMXCLK to clock the SIM counter. The CPU and peripheral clocks do not become active until after the stop delay timeout. This timeout is selectable as 4096 or 32 CGMXCLK cycles. See 15.6.2 Stop Mode.

In wait mode, the CPU clocks are inactive. The SIM also produces two sets of clocks for other modules. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

## 15.3 Reset and System Initialization

The MCU has these reset sources:

- Power-on reset module (POR)

- External reset pin (RST)

- Computer operating properly module (COP)

- Low-voltage inhibit module (LVI)

- Illegal opcode

- Illegal address

- Forced monitor mode entry reset (MODRST)

All of these resets produce the vector \$FFFE:\$FFFF (\$FEFE:\$FEFF in monitor mode) and assert the internal reset signal (IRST). IRST causes all registers to be returned to their default values and all modules to be returned to their reset states.

An internal reset clears the SIM counter (see 15.4 SIM Counter), but an external reset does not. Each of the resets sets a corresponding bit in the SIM reset status register (SRSR). See 15.7 SIM Registers.

### 15.3.1 External Pin Reset

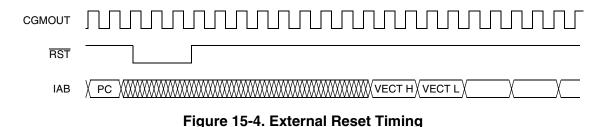

The  $\overline{\text{RST}}$  pin circuit includes an internal pullup device. Pulling the asynchronous  $\overline{\text{RST}}$  pin low halts all processing. The PIN bit of the SIM reset status register (SRSR) is set as long as  $\overline{\text{RST}}$  is held low for a minimum of 67 CGMXCLK cycles, assuming that neither the POR nor the LVI was the source of the reset. See Table 15-2 for details. Figure 15-4 shows the relative timing.

MC68HC908GT16 • MC68HC908GT8 • MC68HC08GT16 Data Sheet, Rev. 5.0

# Chapter 16 Serial Peripheral Interface (SPI) Module

## 16.1 Introduction

This section describes the serial peripheral interface (SPI) module, which allows full-duplex, synchronous, serial communications with peripheral devices.

The text that follows describes the SPI. The SPI I/O pin names are  $\overline{SS}$  (slave select), SPSCK (SPI serial clock), MOSI (master out slave in), and MISO (master in/slave out). The SPI shares four I/O pins with four parallel I/O ports.

## 16.2 Features

Features of the SPI module include:

- Full-duplex operation

- Master and slave modes

- Double-buffered operation with separate transmit and receive registers

- Four master mode frequencies (maximum = bus frequency ÷ 2)

- Maximum slave mode frequency = bus frequency

- Serial clock with programmable polarity and phase

- Two separately enabled interrupts:

- SPRF (SPI receiver full)

- SPTE (SPI transmitter empty)

- Mode fault error flag with CPU interrupt capability

- Overflow error flag with CPU interrupt capability

- Programmable wired-OR mode

- I/O (input/output) port bit(s) software configurable with pullup device(s) if configured as input port bit(s)

## **16.3 Functional Description**

The SPI module allows full-duplex, synchronous, serial communication between the MCU and peripheral devices, including other MCUs. Software can poll the SPI status flags or SPI operation can be interrupt driven.

If a port bit is configured for input, then an internal pullup device may be enabled for that port bit.

The following paragraphs describe the operation of the SPI module. Refer to Figure 16-2 for a summary of the SPI I/O registers.

#### Monitor Module (MON)

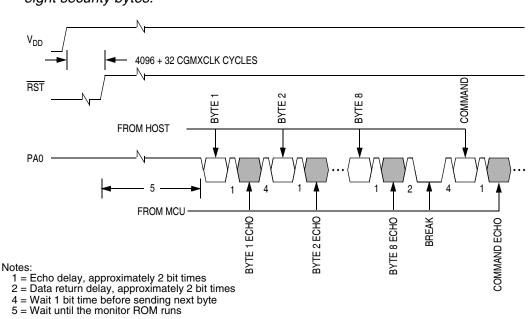

Upon power-on reset, if the received bytes of the security code do not match the data at locations \$FFF6-\$FFFD, the host fails to bypass the security feature. The MCU remains in monitor mode, but reading a Flash location returns an invalid value and trying to execute code from Flash causes an illegal address reset. After receiving the eight security bytes from the host, the MCU transmits a break character, signifying that it is ready to receive a command.

#### NOTE

The MCU does not transmit a break character until after the host sends the eight security bytes.

### Figure 19-18. Monitor Mode Entry Timing

To determine whether the security code entered is correct, check to see if bit 6 of RAM address \$40 is set. If it is, then the correct security code has been entered and Flash can be accessed.

If the security sequence fails, the device should be reset by a power-on reset and brought up in monitor mode to attempt another entry. After failing the security sequence, the Flash module can also be mass erased by executing an erase routine that was downloaded into internal RAM. The mass erase operation clears the security code locations so that all eight security bytes become \$FF (blank).

### A.8.1 5.0-V DC Electrical Characteristics

| Characteristic <sup>(1)</sup>                                                                   | Symbol                              | Min                   | Typ <sup>(2)</sup> | Мах                   | Unit |

|-------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------|--------------------|-----------------------|------|

| Output high voltage                                                                             |                                     |                       |                    |                       |      |

| $(I_{Load} = -2.0 \text{ mA})$ all I/O pins                                                     | V <sub>OH</sub>                     | V <sub>DD</sub> – 0.8 |                    | _                     | V    |

| (I <sub>Load</sub> = -10.0 mA) all I/O pins                                                     | V <sub>OH</sub>                     | V <sub>DD</sub> – 1.5 |                    |                       | V    |

| $(I_{Load} = -20.0 \text{ mA})$ pins PTC0–PTC4 only                                             | V <sub>OH</sub>                     | V <sub>DD</sub> – 1.5 |                    | —                     | V    |

| Maximum combined I <sub>OH</sub> for port C, port E,<br>port PTD0–PTD3                          | I <sub>OH1</sub>                    |                       | —                  | 50                    | mA   |

| Maximum combined I <sub>OH</sub> for port PTD4–PTD7,<br>port A, port B                          | I <sub>OH2</sub>                    | —                     | —                  | 50                    | mA   |

| Maximum total I <sub>OH</sub> for all port pins                                                 | I <sub>ОНТ</sub>                    | —                     | —                  | 100                   | mA   |

| Output low voltage                                                                              |                                     |                       |                    |                       |      |

| (I <sub>Load</sub> = 1.6 mÅ) all I/O pins                                                       | V <sub>OL</sub>                     | —                     | _                  | 0.4                   | V    |

| (I <sub>Load</sub> = 10 mA) all I/O pins                                                        | V <sub>OL</sub>                     | —                     |                    | 1.5                   | V    |

| $(I_{Load} = 20 \text{mA})$ pins PTC0–PTC4 only                                                 | V <sub>OL</sub>                     | —                     | —                  | 1.5                   | V    |

| Maximum combined I <sub>OL</sub> for port C, port E,<br>port PTD0–PTD3                          | I <sub>OL1</sub>                    | —                     | —                  | 50                    | mA   |

| Maximum combined I <sub>OL</sub> for port PTD4–PTD7,<br>port A, port B                          | I <sub>OL2</sub>                    | —                     | —                  | 50                    | mA   |

| Maximum total I <sub>OL</sub> for all port pins                                                 | I <sub>OLT</sub>                    | —                     | —                  | 100                   | mA   |

| Input high voltage<br>All ports, IRQ, RST, OSC1                                                 | V <sub>IH</sub>                     | $0.7 	imes V_{DD}$    | _                  | V <sub>DD</sub>       | V    |

| Input low voltage<br>All ports, IRQ, RST, OSC1                                                  | V <sub>IL</sub>                     | V <sub>SS</sub>       | _                  | $0.2 \times V_{DD}$   | V    |

| DC injection current, all ports <sup>(3)</sup>                                                  | I <sub>INJ</sub>                    | - 2.0                 | —                  | + 2.0                 | mA   |

| Total DC current injection (sum of all I/O) <sup>(3)</sup>                                      | I <sub>INJTOT</sub>                 | - 25                  | —                  | +25                   | mA   |

| I/O ports Hi-Z leakage current <sup>(4)</sup>                                                   | IIL                                 |                       | —                  | ±10                   | μA   |

| Input current                                                                                   | l <sub>In</sub>                     | —                     | —                  | ±1                    | μA   |

| Pullup resistors (as input only)<br>Ports PTA7/KBD7–PTA0/KBD0, PTC6–PTC0,<br>PTD7/T2CH1–PTD0/SS | R <sub>PU</sub>                     | 20                    | 30                 | 65                    | kΩ   |

| Capacitance<br>Ports (as input or output)                                                       | C <sub>Out</sub><br>C <sub>In</sub> |                       |                    | 12<br>8               | pF   |

| Monitor mode entry voltage                                                                      | V <sub>TST</sub>                    | V <sub>DD</sub> + 2.5 | _                  | V <sub>DD</sub> + 4.0 | V    |

| Low-voltage inhibit, trip falling voltage                                                       | V <sub>TRIPF</sub>                  | 3.90                  | 4.25               | 4.50                  | V    |

| Low-voltage inhibit, trip rising voltage                                                        | V <sub>TRIPR</sub>                  | 4.00                  | 4.35               | 4.60                  | V    |

| Low-voltage inhibit reset/recover hysteresis<br>( $V_{TRIPF} + V_{HYS} = V_{TRIPR}$ )           | V <sub>HYS</sub>                    | _                     | 100                | _                     | mV   |

| POR rearm voltage <sup>(5)</sup>                                                                | V <sub>POR</sub>                    | 0                     | —                  | 100                   | mV   |

| POR reset voltage <sup>(6)</sup>                                                                | V <sub>PORRST</sub>                 | 0                     | 700                | —                     | mV   |

| POR rise time ramp rate <sup>(7)</sup>                                                          | R <sub>POR</sub>                    | 0.035                 | —                  | _                     | V/ms |

1.  $V_{DD}$  = 5.0 Vdc ± 10%,  $V_{SS}$  = 0 Vdc,  $T_A = T_A$  (min) to  $T_A$  (max), unless otherwise noted 2. Typical values reflect average measurements at midpoint of voltage range, 25°C only.

3. Some disturbance of the ADC accuracy is possible during any injection event and is dependent on board layout and power supply decoupling. This parameter is guaranteed by characterization.

4. Pullups and pulldowns are disabled. Port B leakage is specified in 20.16 ADC Characteristics.

Maximum is highest voltage that POR is guaranteed.

Maximum is highest voltage that POR is possible.

7. If minimum  $V_{DD}$  is not reached before the internal POR reset is released,  $\overline{RST}$  must be driven low externally until minimum  $V_{DD}$  is reached.

MC68HC08GT16

## A.9 ADC Characteristics

| Characteristic <sup>(1)</sup>                                   | Symbol            | Min                          | Max                          | Unit                    | Comments                                                                                            |

|-----------------------------------------------------------------|-------------------|------------------------------|------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------|

| Supply voltage                                                  | V <sub>DDA</sub>  | 2.7<br>(V <sub>DD</sub> min) | 5.5<br>(V <sub>DD</sub> max) | V                       | V <sub>DDA</sub> should be tied to the<br>same potential as V <sub>DD</sub> via<br>separate traces. |

| Input voltages                                                  | V <sub>ADIN</sub> | 0                            | V <sub>DDA</sub>             | V                       |                                                                                                     |

| Resolution                                                      | B <sub>AD</sub>   | 8                            | 8                            | Bits                    |                                                                                                     |

| Absolute accuracy<br>$(V_{REFL} = V_{SSA}, V_{REFH} = V_{DDA})$ | A <sub>AD</sub>   | _                            | ± 1.5                        | LSB                     | Includes quantization                                                                               |

| ADC internal clock                                              | f <sub>ADIC</sub> | 0.5                          | 1.048                        | MHz                     | t <sub>AIC</sub> = 1/f <sub>ADIC</sub> , tested only<br>at 1 MHz                                    |

| Conversion range                                                | R <sub>AD</sub>   | V <sub>REFL</sub>            | V <sub>REFH</sub>            | V                       | $V_{SSA} \le V_{ADIN} \le V_{DDA}$                                                                  |

| Power-up time                                                   | t <sub>ADPU</sub> | 16                           |                              | t <sub>AIC</sub> cycles |                                                                                                     |

| ADC voltage reference high                                      | V <sub>REFH</sub> | V <sub>SSA</sub> – 0.1       | V <sub>DDA</sub> + 0.1       | V                       | $V_{REFL} \leq V_{REFH}$                                                                            |

| ADC voltage reference low                                       | V <sub>REFL</sub> | V <sub>SSA</sub> – 0.1       | V <sub>DDA</sub> + 0.1       | V                       | $V_{REFL} \le V_{REFH}$                                                                             |

| Conversion time                                                 | t <sub>ADC</sub>  | 16                           | 17                           | t <sub>AIC</sub> cycles |                                                                                                     |

| Sample time <sup>(2)</sup>                                      | t <sub>ADS</sub>  | 5                            | —                            | t <sub>AIC</sub> cycles |                                                                                                     |

| Zero input reading <sup>(3)</sup>                               | Z <sub>ADI</sub>  | 00                           | 01                           | Hex                     | $V_{IN} = V_{REFL}$                                                                                 |

| Full-scale reading <sup>(3)</sup>                               | F <sub>ADI</sub>  | FE                           | FF                           | Hex                     | V <sub>IN</sub> = V <sub>REFH</sub>                                                                 |

| Input capacitance                                               | C <sub>ADI</sub>  | —                            | 8                            | pF                      | Not tested                                                                                          |

| Input leakage <sup>(4)</sup><br>Port B                          | _                 | —                            | ± 1                          | μA                      |                                                                                                     |

1.  $V_{DD} = 5.0 \text{ Vdc} \pm 10\%$ ,  $V_{SS} = 0 \text{ Vdc}$ ,  $V_{DDA} = 5.0 \text{ Vdc} \pm 10\%$ ,  $V_{SSA} = 0 \text{ Vdc}$ ,  $V_{REFH} = 5.0 \text{ Vdc} \pm 10\%$ ,  $V_{REFL} = 0$ 2. Source impedances greater than 10 k $\Omega$  adversely affect internal RC charging time during input sampling. 3. Zero-input/full-scale reading requires sufficient decoupling measures for accurate conversions.

4. The external system error caused by input leakage current is approximately equal to the product of R source and input current.