Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | SCI, SPI                                                               |

| Peripherals                | LVD, POR, PWM                                                          |

| Number of I/O              | 36                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 512 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 8x8b                                                               |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 44-QFP                                                                 |

| Supplier Device Package    | 44-QFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908gt16cfber |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Chapter 2 Memory

## 2.1 Introduction

The CPU08 can address 64 Kbytes of memory space. The memory map, shown in Figure 2-1, includes:

- User Flash memory:

- MC68HC908GT16 15,872 bytes

- MC68HC908GT8 7,680 bytes

- 512 bytes of random-access memory (RAM)

- 720 bytes of Flash programming routines read-only memory (ROM)

- 36 bytes of user-defined vectors

- 304 bytes of monitor ROM

# 2.2 Unimplemented Memory Locations

Accessing an unimplemented location can cause an illegal address reset. In the memory map (Figure 2-1) and in register figures in this document, unimplemented locations are shaded.

# 2.3 Reserved Memory Locations

Accessing a reserved location can have unpredictable effects on MCU operation. In the Figure 2-1 and in register figures in this document, reserved locations are marked with the word Reserved or with the letter R.

# 2.4 Input/Output (I/O) Section

Most of the control, status, and data registers are in the zero page area of \$0000–\$003F. Additional I/O registers have these addresses:

- \$FE00; SIM break status register, SBSR

- \$FE01; SIM reset status register, SRSR

- \$FE02; reserved, SUBAR

- \$FE03; SIM break flag control register, SBFCR

- \$FE04; interrupt status register 1, INT1

- \$FE05; interrupt status register 2, INT2

- \$FE06; interrupt status register 3, INT3

- \$FE07; reserved

- \$FE08; Flash control register, FLCR

- \$FE09; break address register high, BRKH

- \$FE0A; break address register low, BRKL

- \$FE0B; break status and control register, BRKSCR

MC68HC908GT16 • MC68HC908GT8 • MC68HC08GT16 Data Sheet, Rev. 5.0

## Memory

| Addr.  | Register Name                                    |                 | Bit 7 | 6       | 5       | 4        | 3                      | 2     | 1         | Bit 0   |

|--------|--------------------------------------------------|-----------------|-------|---------|---------|----------|------------------------|-------|-----------|---------|

|        | Keyboard Status                                  | Read:           | 0     | 0       | 0       | 0        | KEYF                   | 0     | IMASKK    | MODEK   |

| \$001A | and Control Register<br>(INTKBSCR)               | Write:          |       |         |         |          |                        | ACKK  | IIVIASKK  | IVIODEK |

|        | See page 111.                                    | Reset:          | 0     | 0       | 0       | 0        | 0                      | 0     | 0         | 0       |

| \$001B | Keyboard Interrupt Enable<br>Register (INTKBIER) | Read:<br>Write: | KBIE7 | KBIE6   | KBIE5   | KBIE4    | KBIE3                  | KBIE2 | KBIE1     | KBIE0   |

|        | See page 112.                                    | Reset:          | 0     | 0       | 0       | 0        | 0                      | 0     | 0         | 0       |

|        | Timebase Module Control                          | Read:           | TBIF  | TBR2    | TBR1    | TBR0     | 0                      | TBIE  | TBON      | R       |

|        | Register (TBCR)                                  | Write:          |       | I DN2   | IDITI   | IBITO    | TACK                   | IDIE  | IDON      | 1 1     |

|        | See page 218.                                    | Reset:          | 0     | 0       | 0       | 0        | 0                      | 0     | 0         | 0       |

|        | IRQ Status and Control                           | Read:           | 0     | 0       | 0       | 0        | IRQF1                  | 0     | IMA CIZ 1 | MODE1   |

| \$001D | Register (INTSCR)                                | Write:          |       |         |         |          |                        | ACK1  | IMASK1    | MODE1   |

|        | See page 104.                                    | Reset:          | 0     | 0       | 0       | 0        | 0                      | 0     | 0         | 0       |

|        | Configuration Register 2                         | Read:           | R     | 0       | EXT-    | EXT-SLOW | EXT-                   | 0     | OSCENIN-  | R       |

| \$001E | (CONFIG2) <sup>†</sup>                           | Write:          | n     |         | XTALEN  | EXT-SLOW | CLKEN                  |       | STOP      | Π       |

|        | See page 58.                                     | Reset:          | 0     | 0       | 0       | 0        | 0                      | 0     | 0         | 0       |

| \$001F | Configuration Register 1 (CONFIG1) <sup>†</sup>  | Read:<br>Write: | COPRS | LVISTOP | LVIRSTD | LVIPWRD  | LVI5OR3 <sup>(1)</sup> | SSREC | STOP      | COPD    |

|        | See page 58.                                     | Reset:          | 0     | 0       | 0       | 0        | 0                      | 0     | 0         | 0       |

<sup>1.</sup> One-time writable register after each reset, except LVI5OR3 bit. LVI5OR3 bit is only reset via POR (power-on reset).

|               |                                                  | -               |        |            |       |             |        |              |       |        |

|---------------|--------------------------------------------------|-----------------|--------|------------|-------|-------------|--------|--------------|-------|--------|

|               | Timer 1 Status and Control                       | Read:           | TOF    | TOIE       | TSTOP | 0           | 0      | PS2          | PS1   | PS0    |

| \$0020        | Register (T1SC)                                  | Write:          | 0      | TOIL       | 10101 | TRST        |        | 1 02         | 5     | 1 00   |

|               | See page 231.                                    | Reset:          | 0      | 0          | 1     | 0           | 0      | 0            | 0     | 0      |

|               | Timer 1 Counter                                  | Read:           | Bit 15 | 14         | 13    | 12          | 11     | 10           | 9     | Bit 8  |

| \$0021        | Register High (T1CNTH)                           | Write:          |        |            |       |             |        |              |       |        |

|               | See page 232.                                    | Reset:          | 0      | 0          | 0     | 0           | 0      | 0            | 0     | 0      |

|               | Timer 1 Counter                                  | Read:           | Bit 7  | 6          | 5     | 4           | 3      | 2            | 1     | Bit 0  |

| \$0022        | Register Low (T1CNTL)                            | Write:          |        |            |       |             |        |              |       |        |

| See page 232. | Reset:                                           | 0               | 0      | 0          | 0     | 0           | 0      | 0            | 0     |        |

| \$0023        | Timer 1 Counter Modulo<br>Register High (T1MODH) | Read:<br>Write: | Bit 15 | 14         | 13    | 12          | 11     | 10           | 9     | Bit 8  |

|               | See page 233.                                    | Reset:          | 1      | 1          | 1     | 1           | 1      | 1            | 1     | 1      |

| \$0024        | Timer 1 Counter Modulo<br>Register Low (T1MODL)  | Read:<br>Write: | Bit 7  | 6          | 5     | 4           | 3      | 2            | 1     | Bit 0  |

|               | See page 233.                                    | Reset:          | 1      | 1          | 1     | 1           | 1      | 1            | 1     | 1      |

|               | Timer 1 Channel 0 Status and                     | Read:           | CH0F   | CHOIE      | MCOD  | MCOA        | EL COD | El COA       | TO\/0 | CHOMAY |

|               | Control Register (T1SC0)                         | Write:          | 0      | CH0IE      | MS0B  | MS0A        | ELS0B  | ELS0A        | TOV0  | CH0MAX |

|               | See page 233.                                    | Reset:          | 0      | 0          | 0     | 0           | 0      | 0            | 0     | 0      |

|               |                                                  |                 |        | = Unimplem | ented | R = Reserve | d      | U = Unaffect | ed    |        |

Figure 2-2. Control, Status, and Data Registers (Sheet 3 of 7)

MC68HC908GT16 • MC68HC908GT8 • MC68HC08GT16 Data Sheet, Rev. 5.0

## Memory

| Addr.  | Register Name                               |                 | Bit 7     | 6          | 5      | 4           | 3              | 2            | 1     | Bit 0  |

|--------|---------------------------------------------|-----------------|-----------|------------|--------|-------------|----------------|--------------|-------|--------|

|        | Timer 2 Channel 1 Status and                | Read:           | CH1F      | CHILE      | 0      | MC1A        | ELC4D          | ELC1A        | TOVA  | CHIMAY |

| \$0033 | • ,                                         | Write:          | 0         | CH1IE      |        | MS1A        | ELS1B          | ELS1A        | TOV1  | CH1MAX |

|        | See page 234.                               | Reset:          | 0         | 0          | 0      | 0           | 0              | 0            | 0     | 0      |

| \$0034 | Timer 2 Channel 1<br>Register High (T2CH1H) | Read:<br>Write: | Bit 15    | 14         | 13     | 12          | 11             | 10           | 9     | Bit 8  |

|        | See page 236.                               | Reset:          |           |            |        | Indetermina | te after reset |              |       |        |

| \$0035 | Timer 2 Channel 1<br>Register Low (T2CH1L)  | Read:<br>Write: | Bit 7     | 6          | 5      | 4           | 3              | 2            | 1     | Bit 0  |

|        | See page 236.                               | Reset:          |           |            |        | Indetermina | te after reset |              |       |        |

| \$0036 | ICG Control Register<br>(ICGCR)             | Read:<br>Write: | CMIE      | CMF<br>0   | CMON   | CS          | ICGON          | ICGS         | ECGON | ECGS   |

| ,,,,,, | See page 98.                                | Reset:          | 0         | 0          | 0      | 0           | 1              | 0            | 0     | 0      |

| \$0037 | ICG Multiplier Register<br>(ICGMR)          | Read:<br>Write: |           | N6         | N5     | N4          | N3             | N2           | N1    | N0     |

|        | See page 99.                                | Reset:          | 0         | 0          | 0      | 1           | 0              | 1            | 0     | 1      |

| \$0038 | ICG Trim Register<br>(ICGTR)                | Read:<br>Write: | TRIM7     | TRIM6      | TRIM5  | TRIM4       | TRIM3          | TRIM2        | TRIM1 | TRIM0  |

|        | See page 100.                               | Reset:          | 1         | 0          | 0      | 0           | 0              | 0            | 0     | 0      |

| \$0039 | ICG Divider Control<br>Register (ICGDVR)    | Read:<br>Write: |           |            |        |             | DDIV3          | DDIV2        | DDIV1 | DDIV0  |

|        | See page 100.                               | Reset:          | 0         | 0          | 0      | 0           | U              | U            | U     | U      |

|        | ICG DCO Stage Control                       | Read:           | DSTG7     | DSTG6      | DSTG5  | DSTG4       | DSTG3          | DSTG2        | DSTG1 | DSTG0  |

| \$003A | Register (ICGDSR)                           | Write:          | R         | R          | R      | R           | R              | R            | R     | R      |

|        | See page 100.                               | Reset:          |           |            |        | Unaffecte   | d by reset     |              |       |        |

| \$003B | Reserved                                    | Read:<br>Write: | R         | R          | R      | R           | R              | R            | R     | R      |

|        |                                             | Reset:          |           |            |        | Indetermina | te after reset |              |       |        |

| \$003C | ADC Status and Control<br>Register (ADSCR)  | Read:<br>Write: | COCO<br>R | AIEN       | ADCO   | ADCH4       | ADCH3          | ADCH2        | ADCH1 | ADCH0  |

|        | See page 54.                                | Reset:          | 0         | 0          | 0      | 1           | 1              | 1            | 1     | 1      |

|        | ADC Data Register                           | Read:           | AD7       | AD6        | AD5    | AD4         | AD3            | AD2          | AD1   | AD0    |

| \$003D | (ADR)                                       | Write:          |           |            |        |             |                |              |       |        |

|        | See page 55.                                | Reset:          | 0         | 0          | 0      | 0           | 0              | 0            | 0     | 0      |

| \$003E | ADC Clock Register (ADCLK)                  | Read:<br>Write: | ADIV2     | ADIV1      | ADIV0  | ADICLK      | 0              | 0            | 0     | 0      |

|        | See page 56.                                | Reset:          | 0         | 0          | 0      | 0           | 0              | 0            | 0     | 0      |

|        |                                             | Read:           |           |            |        |             |                |              |       |        |

| \$003F | Unimplemented                               | Write:          |           |            |        |             |                |              |       |        |

|        |                                             | Reset:          |           |            |        |             |                |              |       |        |

|        |                                             |                 |           | = Unimplem | nented | R = Reserve | ed             | U = Unaffect | ed    |        |

Figure 2-2. Control, Status, and Data Registers (Sheet 5 of 7)

MC68HC908GT16 • MC68HC908GT8 • MC68HC08GT16 Data Sheet, Rev. 5.0

#### Internal Clock Generator (ICG) Module)

## 7.3.1 Clock Enable Circuit

The clock enable circuit is used to enable the internal clock (ICLK) or external clock (ECLK) and the port logic which is shared with the oscillator pins (OSC1 and OSC2). The clock enable circuit generates an ICG stop (ICGSTOP) signal which stops all clocks (ICLK, ECLK, and the low-frequency base clock, IBASE). ICGSTOP is set and the ICG is disabled in stop mode if the oscillator enable stop bit (OSCENINSTOP) in the CONFIG2 register is clear. The ICG clocks will be enabled in stop mode if OSCENINSTOP is high.

The internal clock enable signal (ICGEN) turns on the internal clock generator which generates ICLK. ICGEN is set (active) whenever the ICGON bit is set and the ICGSTOP signal is clear. When ICGEN is clear, ICLK and IBASE are both low.

The external clock enable signal (ECGEN) turns on the external clock generator which generates ECLK. ECGEN is set (active) whenever the ECGON bit is set and the ICGSTOP signal is clear. ECGON cannot be set unless the external clock enable (EXTCLKEN) bit in the CONFIG2 register is set. when ECGEN is clear, ECLK is low.

The port E4 enable signal (PE4EN) turns on the port E4 logic. Since port E4 is on the same pin as OSC1, this signal is only active (set) when the external clock function is not desired. Therefore, PE4EN is clear when ECGON is set. PE4EN is not gated with ICGSTOP, which means that if the ECGON bit is set, the port E4 logic will remain disabled in stop mode.

The port E3 enable signal (PE3EN) turns on the port E3 logic. Since port E3 is on the same pin as OSC2, this signal is only active (set) when 2-pin oscillator function is not desired. Therefore, PE3EN is clear when ECGON and the external crystal enable (EXTXTALEN) bit in the CONFIG2 register are both set. PE3EN is not gated with ICGSTOP, which means that if ECGON and EXTXTALEN are set, the port E3 logic will remain disabled in stop mode.

## 7.3.2 Internal Clock Generator

The internal clock generator, shown in Figure 7-3, creates a low frequency base clock (IBASE), which operates at a nominal frequency ( $f_{NOM}$ ) of 307.2 kHz  $\pm$  25 percent, and an internal clock (ICLK) which is an integer multiple of IBASE. This multiple is the ICG multiplier factor (N), which is programmed in the ICG multiplier register (ICGMR). The internal clock generator is turned off and the output clocks (IBASE and ICLK) are held low when the internal clock generator enable signal (ICGEN) is clear.

The internal clock generator contains:

- A digitally controlled oscillator

- A modulo N divider

- A frequency comparator, which contains voltage and current references, a frequency to voltage converter, and comparators

- A digital loop filter

Settling time depends primarily on how many corrections it takes to change the clock period and the period of each correction. Since the corrections require four periods of the low-frequency base clock  $(4^*\tau_{\text{IBASE}})$ , and since ICLK is N (the ICG multiply factor for the desired frequency) times faster than IBASE, each correction takes  $4^*N^*\tau_{\text{ICL K}}$ . The period of ICLK, however, will vary as the corrections occur.

## 7.4.6.1 Settling to Within 15 Percent

When the error is greater than 15 percent, the filter takes eight corrections to double or halve the clock period. Due to how the DCO increases or decreases the clock period, the total period of these eight corrections is approximately 11 times the period of the fastest correction. (If the corrections were perfectly linear, the total period would be 11.5 times the minimum period; however, the ring must be slightly nonlinear.) Therefore, the total time it takes to double or halve the clock period is 44\*N\*tici KFAST.

If the clock period needs more than doubled or halved, the same relationship applies, only for each time the clock period needs doubled, the total number of cycles doubles. That is, when transitioning from fast to slow, going from the initial speed to half speed takes  $44*N*\tau_{ICLKFAST}$ ; from half speed to quarter speed takes  $88*N*\tau_{ICLKFAST}$ ; going from quarter speed to eighth speed takes  $176*N*\tau_{ICLKFAST}$ ; and so on. This series can be expressed as  $(2^X-1)*44*N*\tau_{ICLKFAST}$ , where x is the number of times the speed needs doubled or halved. Since  $2^X$  happens to be equal to  $\tau_{ICLKSLOW}/\tau_{ICLKFAST}$ , the equation reduces to  $44*N*(\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_{ICLKSLOW}-\tau_$

Note that increasing speed takes much longer than decreasing speed since N is higher. This can be expressed in terms of the initial clock period ( $\tau_1$ ) minus the final clock period ( $\tau_2$ ) as such:

$$\tau_{15} = abs[44N(\tau_1 - \tau_2)]$$

## 7.4.6.2 Settling to Within 5 Percent

Once the clock period is within 15 percent of the desired clock period, the filter starts making smaller adjustments. When between 15 percent and 5 percent error, each correction will adjust the clock period between 1.61 percent and 2.94 percent. In this mode, a maximum of eight corrections will be required to get to less than 5 percent error. Since the clock period is relatively close to desired, each correction takes approximately the same period of time, or  $4^*\tau_{IBASE}$ . At this point, the internal clock stable bit (ICGS) will be set and the clock frequency is usable, although the error will be as high as 5 percent. The total time to this point is:

$$\tau_5 = abs[44N(\tau_1 - \tau_2)] + 32\tau_{IBASE}$$

### 7.4.6.3 Total Settling Time

Once the clock period is within 5 percent of the desired clock period, the filter starts making minimum adjustments. In this mode, each correction will adjust the frequency between 0.202 percent and 0.368 percent. A maximum of 24 corrections will be required to get to the minimum error. Each correction takes approximately the same period of time, or  $4^*\tau_{\text{IBASE}}$ . Added to the corrections for 15 percent to 5 percent, this makes 32 corrections (128\* $\tau_{\text{IBASE}}$ ) to get from 15 percent to the minimum error. The total time to the minimum error is:

$$\tau_{tot} = abs[44N(\tau_1 - \tau_2)] + 128\tau_{IBASE}$$

The equations for  $\tau_{15}$ ,  $\tau_{5}$ , and  $\tau_{tot}$  are dependent on the actual initial and final clock periods  $\tau_{1}$  and  $\tau_{2}$ , not the nominal. This means the variability in the ICLK frequency due to process, temperature, and voltage must be considered. Additionally, other process factors and noise can affect the actual tolerances of the points at which the filter changes modes. This means a worst case adjustment of up to 35 percent (ICLK

MC68HC908GT16 • MC68HC908GT8 • MC68HC08GT16 Data Sheet, Rev. 5.0

## 9.5.2 Stop Mode

The keyboard module remains active in stop mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of stop mode.

# 9.6 Keyboard Module During Break Interrupts

The system integration module (SIM) controls whether the keyboard interrupt latch can be cleared during the break state. The BCFE bit in the SIM break flag control register (SBFCR) enables software to clear status bits during the break state.

To allow software to clear the keyboard interrupt latch during a break interrupt, write a 1 to the BCFE bit. If a latch is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect the latch during the break state, write a 0 to the BCFE bit. With BCFE at 0 (its default state), writing to the keyboard acknowledge bit (ACKK) in the keyboard status and control register during the break state has no effect. See 9.7.1 Keyboard Status and Control Register.

# 9.7 I/O Registers

These registers control and monitor operation of the keyboard module:

- Keyboard status and control register (INTKBSCR)

- Keyboard interrupt enable register (INTKBIER)

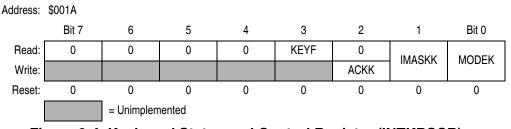

## 9.7.1 Keyboard Status and Control Register

The keyboard status and control register:

- Flags keyboard interrupt requests

- Acknowledges keyboard interrupt requests

- Masks keyboard interrupt requests

- Controls keyboard interrupt triggering sensitivity

Figure 9-4. Keyboard Status and Control Register (INTKBSCR)

#### Bits 7-4 — Not used

These read-only bits always read as 0s.

## **KEYF** — Keyboard Flag Bit

This read-only bit is set when a keyboard interrupt is pending. Reset clears the KEYF bit.

- 1 = Keyboard interrupt pending

- 0 = No keyboard interrupt pending

MC68HC908GT16 • MC68HC908GT8 • MC68HC08GT16 Data Sheet, Rev. 5.0 Freescale Semiconductor 111

# **Chapter 11 Low-Power Modes (MODES)**

## 11.1 Introduction

The microcontroller (MCU) may enter two low-power modes: wait mode and stop mode. They are common to all HC08 MCUs and are entered through instruction execution. This section describes how each module acts in the low-power modes.

#### 11.1.1 Wait Mode

The WAIT instruction puts the MCU in a low-power standby mode in which the central processor unit (CPU) clock is disabled but the bus clock continues to run. Power consumption can be further reduced by disabling the LVI module and/or the timebase module through bits in the CONFIG1 register. (See Chapter 4 Configuration Register (CONFIG).)

## 11.1.2 Stop Mode

Stop mode is entered when a STOP instruction is executed. The CPU clock is disabled and the bus clock is disabled if the OSCENINSTOP bit in the CONFIG2 register is at a 0. (See Chapter 4 Configuration Register (CONFIG).)

# 11.2 Analog-to-Digital Converter (ADC)

#### 11.2.1 Wait Mode

The analog-to-digital converter (ADC) continues normal operation during wait mode. Any enabled CPU interrupt request from the ADC can bring the MCU out of wait mode. If the ADC is not required to bring the MCU out of wait mode, power down the ADC by setting ADCH4—ADCH0 bits in the ADC status and control register before executing the WAIT instruction.

## 11.2.2 Stop Mode

The ADC module is inactive after the execution of a STOP instruction. Any pending conversion is aborted. ADC conversions resume when the MCU exits stop mode after an external interrupt. Allow one conversion cycle to stabilize the analog circuitry.

# 11.3 Break Module (BRK)

#### 11.3.1 Wait Mode

If enabled, the break (BRK) module is active in wait mode. In the break routine, the user can subtract one from the return address on the stack if the SBSW bit in the break status register is set.

MC68HC908GT16 • MC68HC908GT8 • MC68HC08GT16 Data Sheet, Rev. 5.0

#### **Low-Power Modes (MODES)**

## 11.3.2 **Stop Mode**

The break module is inactive in stop mode. A break interrupt causes exit from stop mode and sets the SBSW bit in the break status register. The STOP instruction does not affect break module register states.

# 11.4 Central Processor Unit (CPU)

## 11.4.1 Wait Mode

The WAIT instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling interrupts. After exit from wait mode by interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

## **11.4.2 Stop Mode**

The STOP instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling external interrupts. After exit from stop mode by external interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

After exiting stop mode, the CPU clock begins running after the oscillator stabilization delay.

# 11.5 Internal Clock Generator Module (ICG)

## 11.5.1 Wait Mode

The internal clock generator (ICG) module remains active in wait mode. If enabled, the ICG interrupt to the CPU can bring the MCU out of wait mode.

In some applications, low power-consumption is desired in wait mode and a high-frequency clock is not needed. In these applications, reduce power consumption by either selecting a low-frequency external clock and turn the internal clock generator off or reduce the bus frequency by minimizing the ICG multiplier factor (N) before executing the WAIT instruction.

## 11.5.2 Stop Mode

The value of the oscillator enable in stop (OSCENINSTOP) bit in the CONFIG2 register determines the behavior of the ICG in stop mode. If OSCENINSTOP is low, the ICG is disabled in stop and, upon execution of the STOP instruction, all ICG activity will cease and the output clocks (CGMXCLK, CGMOUT, COPCLK, and TBMCLK) will be held low. Power consumption will be minimal.

If OSCENINSTOP is high, the ICG is enabled in stop and activity will continue. This is useful if the timebase module (TBM) is required to bring the MCU out of stop mode. ICG interrupts will not bring the MCU out of stop mode in this case.

During stop mode, if OSCENINSTOP is low, several functions in the ICG are affected. The stable bits (ECGS and ICGS) are cleared, which will enable the external clock stabilization divider upon recovery. The clock monitor is disabled (CMON = 0) which will also clear the clock monitor interrupt enable (CMIE) and clock monitor flag (CMF) bits. The CS, ICGON, ECGON, N, TRIM, DDIV, and DSTG bits are unaffected.

MC68HC908GT16 • MC68HC908GT8 • MC68HC08GT16 Data Sheet, Rev. 5.0

## Input/Output (I/O) Ports (PORTS)

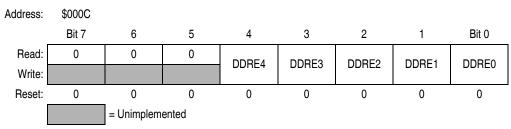

Figure 12-18. Data Direction Register E (DDRE)

## DDRE4-DDRE0 — Data Direction Register E Bits

These read/write bits control port E data direction. Reset clears DDRE4–DDRE0, configuring all port E pins as inputs.

- 1 = Corresponding port E pin configured as output

- 0 = Corresponding port E pin configured as input

#### NOTE

Avoid glitches on port E pins by writing to the port E data register before changing data direction register E bits from 0 to 1.

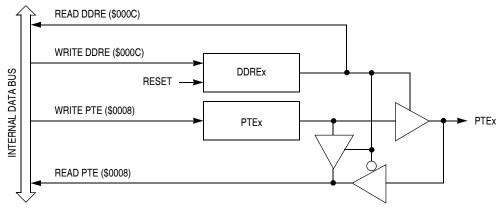

Figure 12-19 shows the port E I/O logic.

Figure 12-19. Port E I/O Circuit

When bit DDREx is a 1, reading address \$0008 reads the PTEx data latch. When bit DDREx is a 0, reading address \$0008 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit. Table 12-6 summarizes the operation of the port E pins.

| Table 12-6. Port E Pin Function | Table | 12-6 | Port F | Pin | Functions |

|---------------------------------|-------|------|--------|-----|-----------|

|---------------------------------|-------|------|--------|-----|-----------|

| DDRE | PTE              | I/O Pin                    | Accesses to DDRE | Access    | ses to PTE               |

|------|------------------|----------------------------|------------------|-----------|--------------------------|

| Bit  | Bit              | Mode                       | Read/Write       | Read      | Write                    |

| 0    | X <sup>(1)</sup> | Input, Hi-Z <sup>(2)</sup> | DDRE4-DDRE0      | Pin       | PTE4-PTE0 <sup>(3)</sup> |

| 1    | Х                | Output                     | DDRE4-DDRE0      | PTE4-PTE0 | PTE4-PTE0                |

- 1. X = Don't care

- 2. Hi-Z = High impedance

- 3. Writing affects data register, but does not affect input.

MC68HC908GT16 • MC68HC908GT8 • MC68HC08GT16 Data Sheet, Rev. 5.0

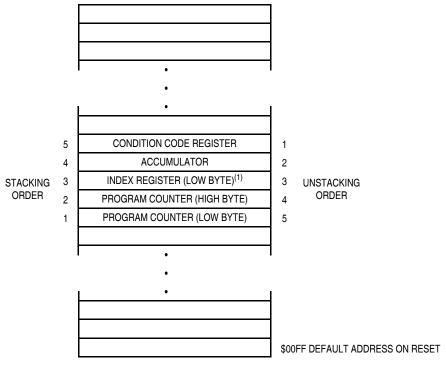

1. High byte of index register is not stacked.

Figure 13-4. Interrupt Stacking Order

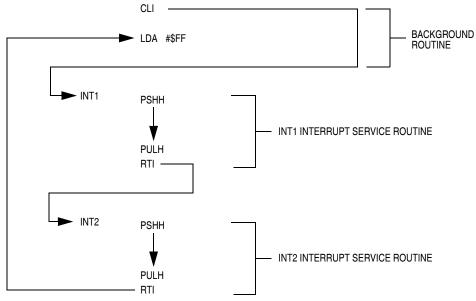

After every instruction, the CPU checks all pending interrupts if the I bit is not set. If more than one interrupt is pending when an instruction is done, the highest priority interrupt is serviced first. In the example shown in Figure 13-5, if an interrupt is pending upon exit from the interrupt service routine, the pending interrupt is serviced before the LDA instruction is executed.

Figure 13-5. Interrupt Recognition Example

MC68HC908GT16 • MC68HC908GT8 • MC68HC08GT16 Data Sheet, Rev. 5.0

**Resets and Interrupts**

MC68HC908GT16 • MC68HC908GT8 • MC68HC08GT16 Data Sheet, Rev. 5.0

#### **Enhanced Serial Communications Interface (ESCI) Module**

**Table 14-3. Data Bit Recovery**

| RT8, RT9, and RT10 Samples | Data Bit Determination | Noise Flag |

|----------------------------|------------------------|------------|

| 000                        | 0                      | 0          |

| 001                        | 0                      | 1          |

| 010                        | 0                      | 1          |

| 011                        | 1                      | 1          |

| 100                        | 0                      | 1          |

| 101                        | 1                      | 1          |

| 110                        | 1                      | 1          |

| 111                        | 1                      | 0          |

#### NOTE

The RT8, RT9, and RT10 samples do not affect start bit verification. If any or all of the RT8, RT9, and RT10 start bit samples are 1s following a successful start bit verification, the noise flag (NF) is set and the receiver assumes that the bit is a start bit.

To verify a stop bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 14-4 summarizes the results of the stop bit samples.

**Table 14-4. Stop Bit Recovery**

| RT8, RT9, and RT10 Samples | Framing Error Flag | Noise Flag |

|----------------------------|--------------------|------------|

| 000                        | 1                  | 0          |

| 001                        | 1                  | 1          |

| 010                        | 1                  | 1          |

| 011                        | 0                  | 1          |

| 100                        | 1                  | 1          |

| 101                        | 0                  | 1          |

| 110                        | 0                  | 1          |

| 111                        | 0                  | 0          |

## 14.4.3.4 Framing Errors

If the data recovery logic does not detect a 1 where the stop bit should be in an incoming character, it sets the framing error bit, FE, in SCS1. A break character also sets the FE bit because a break character has no stop bit. The FE bit is set at the same time that the SCRF bit is set.

#### 14.4.3.5 Baud Rate Tolerance

A transmitting device may be operating at a baud rate below or above the receiver baud rate. Accumulated bit time misalignment can cause one of the three stop bit data samples to fall outside the actual stop bit. Then a noise error occurs. If more than one of the samples is outside the stop bit, a framing error occurs. In most applications, the baud rate tolerance is much more than the degree of misalignment that is likely to occur.

As the receiver samples an incoming character, it resynchronizes the RT clock on any valid falling edge within the character. Resynchronization within characters corrects misalignments between transmitter bit times and receiver bit times.

MC68HC908GT16 • MC68HC908GT8 • MC68HC08GT16 Data Sheet, Rev. 5.0

#### **Enhanced Serial Communications Interface (ESCI) Module**

For an 8-bit character, data sampling of the stop bit takes the receiver 9 bit times  $\times$  16 RT cycles + 10 RT cycles = 154 RT cycles.

With the misaligned character shown in Figure 14-9, the receiver counts 154 RT cycles at the point when the count of the transmitting device is 10 bit times  $\times$  16 RT cycles = 160 RT cycles.

The maximum percent difference between the receiver count and the transmitter count of a fast 8-bit character with no errors is

$$\left| \frac{154 - 160}{154} \right| \times 100 = 3.90\%.$$

For a 9-bit character, data sampling of the stop bit takes the receiver 10 bit times  $\times$  16 RT cycles + 10 RT cycles = 170 RT cycles.

With the misaligned character shown in Figure 14-9, the receiver counts 170 RT cycles at the point when the count of the transmitting device is 11 bit times  $\times$  16 RT cycles = 176 RT cycles.

The maximum percent difference between the receiver count and the transmitter count of a fast 9-bit character with no errors is:

$$\left| \frac{170 - 176}{170} \right| \times 100 = 3.53\%.$$

## 14.4.3.6 Receiver Wakeup

So that the MCU can ignore transmissions intended only for other receivers in multiple-receiver systems, the receiver can be put into a standby state. Setting the receiver wakeup bit, RWU, in SCC2 puts the receiver into a standby state during which receiver interrupts are disabled.

Depending on the state of the WAKE bit in SCC1, either of two conditions on the RxD pin can bring the receiver out of the standby state:

- 1. Address mark An address mark is a 1 in the MSB position of a received character. When the WAKE bit is set, an address mark wakes the receiver from the standby state by clearing the RWU bit. The address mark also sets the ESCI receiver full bit, SCRF. Software can then compare the character containing the address mark to the user-defined address of the receiver. If they are the same, the receiver remains awake and processes the characters that follow. If they are not the same, software can set the RWU bit and put the receiver back into the standby state.

- Idle input line condition When the WAKE bit is clear, an idle character on the RxD pin wakes the

receiver from the standby state by clearing the RWU bit. The idle character that wakes the receiver

does not set the receiver idle bit, IDLE, or the ESCI receiver full bit, SCRF. The idle line type bit,

ILTY, determines whether the receiver begins counting 1s as idle character bits after the start bit

or after the stop bit.

## NOTE

With the WAKE bit clear, setting the RWU bit after the RxD pin has been idle will cause the receiver to wake up.

a valid character that sets the SCRF bit before an idle condition can set the IDLE bit. Also, after the IDLE bit has been cleared, a valid character must again set the SCRF bit before an idle condition can set the IDLE bit. Reset clears the IDLE bit.

- 1 = Receiver input idle

- 0 = Receiver input active (or idle since the IDLE bit was cleared)

#### OR — Receiver Overrun Bit

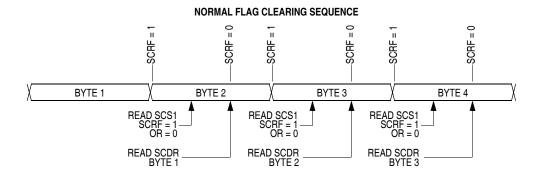

This clearable, read-only bit is set when software fails to read the SCDR before the receive shift register receives the next character. The OR bit generates an ESCI error CPU interrupt request if the ORIE bit in SCC3 is also set. The data in the shift register is lost, but the data already in the SCDR is not affected. Clear the OR bit by reading SCS1 with OR set and then reading the SCDR. Reset clears the OR bit.

- 1 = Receive shift register full and SCRF = 1

- 0 = No receiver overrun

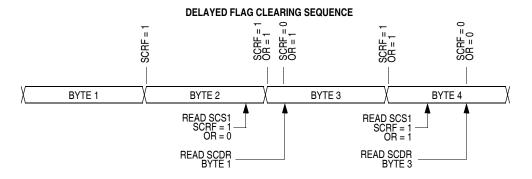

Software latency may allow an overrun to occur between reads of SCS1 and SCDR in the flag-clearing sequence. Figure 14-14 shows the normal flag-clearing sequence and an example of an overrun caused by a delayed flag-clearing sequence. The delayed read of SCDR does not clear the OR bit because OR was not set when SCS1 was read. Byte 2 caused the overrun and is lost. The next flag-clearing sequence reads byte 3 in the SCDR instead of byte 2.

In applications that are subject to software latency or in which it is important to know which byte is lost due to an overrun, the flag-clearing routine can check the OR bit in a second read of SCS1 after reading the data register.

Figure 14-14. Flag Clearing Sequence

MC68HC908GT16 • MC68HC908GT8 • MC68HC08GT16 Data Sheet, Rev. 5.0

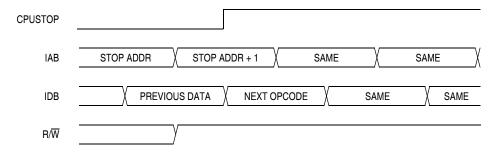

Note: Previous data can be operand data or the STOP opcode, depending on the last instruction.

Figure 15-18. Stop Mode Entry Timing

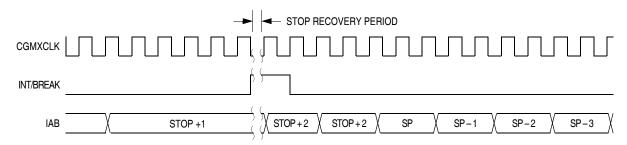

Figure 15-19. Stop Mode Recovery from Interrupt

# 15.7 SIM Registers

The SIM has three memory-mapped registers. Table 15-4 shows the mapping of these registers.

Address

Register

Access Mode

\$FE00

SBSR

User

\$FE01

SRSR

User

\$FE03

SBFCR

User

Table 15-4. SIM Registers

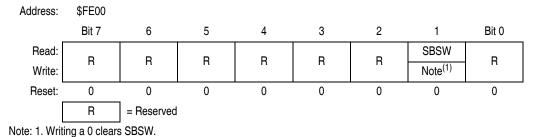

# 15.7.1 SIM Break Status Register

The SIM break status register (SBSR) contains a flag to indicate that a break caused an exit from wait mode. This register is only used in emulation mode.

Figure 15-20. SIM Break Status Register (SBSR)

MC68HC908GT16 • MC68HC908GT8 • MC68HC08GT16 Data Sheet, Rev. 5.0

Serial Peripheral Interface (SPI) Module

## SPR1 and SPR0 — SPI Baud Rate Select Bits

In master mode, these read/write bits select one of four baud rates as shown in Table 16-3. SPR1 and SPR0 have no effect in slave mode. Reset clears SPR1 and SPR0.

**Table 16-3. SPI Master Baud Rate Selection**

| SPR1 and SPR0 | Baud Rate Divisor (BD) |

|---------------|------------------------|

| 00            | 2                      |

| 01            | 8                      |

| 10            | 32                     |

| 11            | 128                    |

Use this formula to calculate the SPI baud rate:

Baud rate =

$$\frac{BUSCLK}{BD}$$

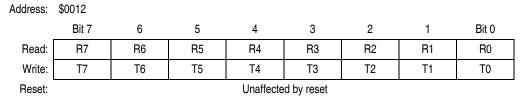

## 16.12.3 SPI Data Register

The SPI data register consists of the read-only receive data register and the write-only transmit data register. Writing to the SPI data register writes data into the transmit data register. Reading the SPI data register reads data from the receive data register. The transmit data and receive data registers are separate registers that can contain different values. See Figure 16-2.

Figure 16-16. SPI Data Register (SPDR)

## R7-R0/T7-T0 — Receive/Transmit Data Bits

## NOTE

Do not use read-modify-write instructions on the SPI data register since the register read is not the same as the register written.

| Addr.  | Register Name                                                             |                              | Bit 7                        | 6                            | 5                            | 4                            | 3              | 2     | 1     | Bit 0    |      |       |       |      |        |

|--------|---------------------------------------------------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|----------------|-------|-------|----------|------|-------|-------|------|--------|

|        | Timer 2 Counter                                                           | Read:                        | Bit 15                       | 14                           | 13                           | 12                           | 11             | 10    | 9     | Bit 8    |      |       |       |      |        |

| \$002C | Register High (T2CNTH)                                                    | Write:                       |                              |                              |                              |                              |                |       |       |          |      |       |       |      |        |

|        | See page 232.                                                             | Reset:                       | 0                            | 0                            | 0                            | 0                            | 0              | 0     | 0     | 0        |      |       |       |      |        |

|        | Timer 2 Counter                                                           | Read:                        | Bit 7                        | 6                            | 5                            | 4                            | 3              | 2     | 1     | Bit 0    |      |       |       |      |        |

| \$002D | Register Low (T2CNTL)                                                     | Write:                       |                              |                              |                              |                              |                |       |       |          |      |       |       |      |        |

|        | See page 232.                                                             | Reset:                       | 0                            | 0                            | 0                            | 0                            | 0              | 0     | 0     | 0        |      |       |       |      |        |

| \$002E | Timer 2 Counter Modulo<br>Register High (T2MODH)                          | Read:<br>Write:              | Bit 15                       | 14                           | 13                           | 12                           | 11             | 10    | 9     | Bit 8    |      |       |       |      |        |

|        | See page 233.                                                             | Reset:                       | 1                            | 1                            | 1                            | 1                            | 1              | 1     | 1     | 1        |      |       |       |      |        |

| \$002F | Timer 2 Counter Modulo<br>\$002F Register Low (T2MODL)                    | Read:<br>Write:              | Bit 7                        | 6                            | 5                            | 4                            | 3              | 2     | 1     | Bit 0    |      |       |       |      |        |

|        | See page 233.                                                             | Reset:                       | 1                            | 1                            | 1                            | 1                            | 1              | 1     | 1     | 1        |      |       |       |      |        |

|        | Timer 2 Channel 0 Status and<br>Control Register (T2SC0)<br>See page 233. | Timer 2 Channel 0 Status and | Read:          | CH0F  | CH0IE | MS0B     | MS0A | ELS0B | ELS0A | TOV0 | CH0MAX |

| \$0030 |                                                                           | Write:                       | 0                            | CHOIL                        | IVISOB                       | IVISUA                       | LLSUB          | LLOUA | 1000  | CHOWAX   |      |       |       |      |        |

|        |                                                                           | Reset:                       | 0                            | 0                            | 0                            | 0                            | 0              | 0     | 0     | 0        |      |       |       |      |        |

| \$0031 | Timer 2 Channel 0<br>Register High (T2CH0H)                               | Read:<br>Write:              | Bit 15                       | 14                           | 13                           | 12                           | 11             | 10    | 9     | Bit 8    |      |       |       |      |        |

|        | See page 236.                                                             | Reset:                       | Indeterminate after reset    |                              |                              |                              |                |       |       |          |      |       |       |      |        |

| \$0032 | Timer 2 Channel 0<br>Register Low (T2CH0L)                                | Read:<br>Write:              | Bit 7                        | 6                            | 5                            | 4                            | 3              | 2     | 1     | Bit 0    |      |       |       |      |        |

|        | See page 236.                                                             | Reset:                       |                              |                              |                              | Indeterminat                 | te after reset |       |       |          |      |       |       |      |        |

|        | Timer 2 Channel 1 Status and                                              | Read:                        | CH1F                         | CH1IE                        | 0                            | MS1A                         | ELS1B          | ELS1A | TOV1  | CH1MAX   |      |       |       |      |        |

| \$0033 | Control Register (T2SC1)                                                  | Write:                       | 0                            | OTTIL                        |                              | WOTA                         | LLOID          | LLOTA | 1011  | OTTIWIZZ |      |       |       |      |        |

|        | See page 234.                                                             | Reset:                       | 0                            | 0                            | 0                            | 0                            | 0              | 0     | 0     | 0        |      |       |       |      |        |

| \$0034 | Timer 2 Channel 1<br>Register High (T2CH1H)                               | Read:<br>Write:              | Bit 15                       | 14                           | 13                           | 12                           | 11             | 10    | 9     | Bit 8    |      |       |       |      |        |

|        | See page 236.                                                             | Reset:                       |                              |                              | ı                            | Indeterminat                 | te after reset |       |       |          |      |       |       |      |        |

| \$0035 | Timer 2 Channel 1<br>Register Low (T2CH1L)                                | Read:<br>Write:              | Bit 7                        | 6                            | 5                            | 4                            | 3              | 2     | 1     | Bit 0    |      |       |       |      |        |

|        | See page 236.                                                             | Reset:                       |                              |                              |                              | Indeterminat                 | te after reset |       |       |          |      |       |       |      |        |

|        |                                                                           |                              |                              | = Unimplem                   | ented                        |                              |                |       |       |          |      |       |       |      |        |

Figure 18-3. TIM I/O Register Summary (Sheet 2 of 2)

## 18.4.1 TIM Counter Prescaler

The TIM clock source can be one of the seven prescaler outputs. The prescaler generates seven clock rates from the internal bus clock. The prescaler select bits, PS[2:0], in the TIM status and control register select the TIM clock source.

## 18.4.2 Input Capture

With the input capture function, the TIM can capture the time at which an external event occurs. When an active edge occurs on the pin of an input capture channel, the TIM latches the contents of the TIM counter

MC68HC908GT16 • MC68HC908GT8 • MC68HC08GT16 Data Sheet, Rev. 5.0

## 18.4.4 Pulse Width Modulation (PWM)

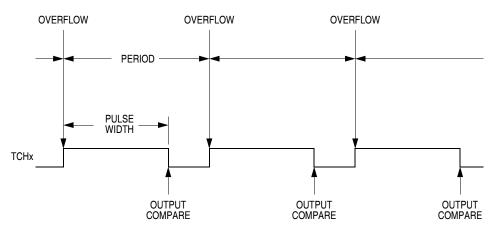

By using the toggle-on-overflow feature with an output compare channel, the TIM can generate a PWM signal. The value in the TIM counter modulo registers determines the period of the PWM signal. The channel pin toggles when the counter reaches the value in the TIM counter modulo registers. The time between overflows is the period of the PWM signal.

As Figure 18-4 shows, the output compare value in the TIM channel registers determines the pulse width of the PWM signal. The time between overflow and output compare is the pulse width. Program the TIM to clear the channel pin on output compare if the state of the PWM pulse is logic 1. Program the TIM to set the pin if the state of the PWM pulse is logic 0.

The value in the TIM counter modulo registers and the selected prescaler output determines the frequency of the PWM output. The frequency of an 8-bit PWM signal is variable in 256 increments. Writing \$00FF (255) to the TIM counter modulo registers produces a PWM period of 256 times the internal bus clock period if the prescaler select value is \$000. See 18.9.1 TIM Status and Control Register.

The value in the TIM channel registers determines the pulse width of the PWM output. The pulse width of an 8-bit PWM signal is variable in 256 increments. Writing \$0080 (128) to the TIM channel registers produces a duty cycle of 128/256 or 50%.

Figure 18-4. PWM Period and Pulse Width

## 18.4.4.1 Unbuffered PWM Signal Generation

Any output compare channel can generate unbuffered PWM pulses as described in 18.4.4 Pulse Width Modulation (PWM). The pulses are unbuffered because changing the pulse width requires writing the new pulse width value over the old value currently in the TIM channel registers.

An unsynchronized write to the TIM channel registers to change a pulse width value could cause incorrect operation for up to two PWM periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that PWM period. Also, using a TIM overflow interrupt routine to write a new, smaller pulse width value may cause the compare to be missed. The TIM may pass the new value before it is written.

Use the following methods to synchronize unbuffered changes in the PWM pulse width on channel x:

• When changing to a shorter pulse width, enable channel x output compare interrupts and write the new value in the output compare interrupt routine. The output compare interrupt occurs at the end of the current pulse. The interrupt routine has until the end of the PWM period to write the new value.

MC68HC908GT16 • MC68HC908GT8 • MC68HC08GT16 Data Sheet, Rev. 5.0

#### **Development Support**

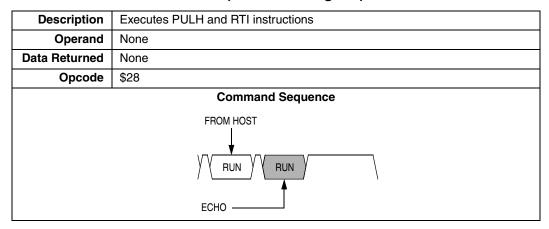

Table 19-7. RUN (Run User Program) Command

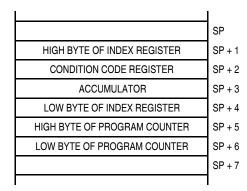

The MCU executes the SWI and PSHH instructions when it enters monitor mode. The RUN command tells the MCU to execute the PULH and RTI instructions. Before sending the RUN command, the host can modify the stacked CPU registers to prepare to run the host program. The READSP command returns the incremented stack pointer value, SP + 1. The high and low bytes of the program counter are at addresses SP + 5 and SP + 6.

Figure 19-17. Stack Pointer at Monitor Mode Entry

## 19.3.2 Security

A security feature discourages unauthorized reading of Flash locations while in monitor mode. The host can bypass the security feature at monitor mode entry by sending eight security bytes that match the bytes at locations \$FFF6\_\$FFFD. Locations \$FFF6\_\$FFFD contain user-defined data.

#### NOTE

Do not leave locations \$FFF6-\$FFFD blank. For security reasons, program locations \$FFF6-\$FFFD even if they are not used for vectors.

During monitor mode entry, the MCU waits after the power-on reset for the host to send the eight security bytes on pin PTA0. If the received bytes match those at locations \$FFF6—\$FFFD, the host bypasses the security feature and can read all Flash locations and execute code from Flash. Security remains bypassed until a power-on reset occurs. If the reset was not a power-on reset, security remains bypassed and security code entry is not required. See Figure 19-18.

MC68HC908GT16 • MC68HC908GT8 • MC68HC08GT16 Data Sheet, Rev. 5.0

## **Electrical Specifications**

## 20.16 ADC Characteristics

| Characteristic <sup>(1)</sup>          | Symbol            | Min                          | Max                          | Unit                    | Comments                                                                                      |

|----------------------------------------|-------------------|------------------------------|------------------------------|-------------------------|-----------------------------------------------------------------------------------------------|

| Supply voltage                         | V <sub>DDA</sub>  | 2.7<br>(V <sub>DD</sub> min) | 5.5<br>(V <sub>DD</sub> max) | V                       | V <sub>DDA</sub> should be tied to the same potential as V <sub>DD</sub> via separate traces. |

| Input voltages                         | V <sub>ADIN</sub> | 0                            | $V_{DDA}$                    | V                       |                                                                                               |

| Resolution                             | B <sub>AD</sub>   | 8                            | 8                            | Bits                    |                                                                                               |

| Absolute accuracy                      | A <sub>AD</sub>   | _                            | ± 1                          | LSB                     | Includes quantization                                                                         |

| ADC internal clock                     | f <sub>ADIC</sub> | 0.5                          | 1.048                        | MHz                     | t <sub>AIC</sub> = 1/f <sub>ADIC</sub> , tested only<br>at 1 MHz                              |

| Conversion range                       | R <sub>AD</sub>   | V <sub>REFL</sub>            | V <sub>REFH</sub>            | V                       | $V_{SSA} \le V_{ADIN} \le V_{DDA}$                                                            |

| Power-up time                          | t <sub>ADPU</sub> | 16                           |                              | t <sub>AIC</sub> cycles |                                                                                               |

| ADC voltage reference high             | V <sub>REFH</sub> | V <sub>SSA</sub> – 0.1       | V <sub>DDA</sub> + 0.1       | V                       | $V_{REFL} \leq V_{REFH}$                                                                      |

| ADC voltage reference low              | $V_{REFL}$        | V <sub>SSA</sub> – 0.1       | V <sub>DDA</sub> + 0.1       | V                       | $V_{REFL} \leq V_{REFH}$                                                                      |

| Conversion time                        | t <sub>ADC</sub>  | 16                           | 17                           | t <sub>AIC</sub> cycles |                                                                                               |

| Sample time <sup>(2)</sup>             | t <sub>ADS</sub>  | 5                            | _                            | t <sub>AIC</sub> cycles |                                                                                               |

| Zero input reading <sup>(3)</sup>      | Z <sub>ADI</sub>  | 00                           | 01                           | Hex                     | V <sub>IN</sub> = V <sub>REFL</sub>                                                           |

| Full-scale reading <sup>(3)</sup>      | F <sub>ADI</sub>  | FE                           | FF                           | Hex                     | V <sub>IN</sub> = V <sub>REFH</sub>                                                           |

| Input capacitance                      | C <sub>ADI</sub>  | _                            | 8                            | pF                      | Not tested                                                                                    |

| Input leakage <sup>(4)</sup><br>Port B | _                 | _                            | ± 1                          | μΑ                      |                                                                                               |

$<sup>1.\</sup> V_{DD} = 5.0\ Vdc \pm 10\%,\ V_{SS} = 0\ Vdc,\ V_{DDA} = 5.0\ Vdc \pm 10\%,\ V_{SSA} = 0\ Vdc,\ V_{REFH} = 5.0\ Vdc \pm 10\%,\ V_{REFL} = 0$

<sup>2.</sup> Source impedances greater than 10 k $\Omega$  adversely affect internal RC charging time during input sampling.

<sup>3.</sup> Zero-input/full-scale reading requires sufficient decoupling measures for accurate conversions.

<sup>4.</sup> The external system error caused by input leakage current is approximately equal to the product of R source and input current.