Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                        |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | XCore                                                         |

| Core Size                  | 32-Bit 12-Core                                                |

| Speed                      | 2000MIPS                                                      |

| Connectivity               | USB                                                           |

| Peripherals                | -                                                             |

| Number of I/O              | 81                                                            |

| Program Memory Size        | -                                                             |

| Program Memory Type        | ROMIess                                                       |

| EEPROM Size                | -                                                             |

| RAM Size                   | 512K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 0.95V ~ 3.6V                                                  |

| Data Converters            | -                                                             |

| Oscillator Type            | External                                                      |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 128-TQFP Exposed Pad                                          |

| Supplier Device Package    | 128-TQFP (14x14)                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xu212-512-tq128-c20 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

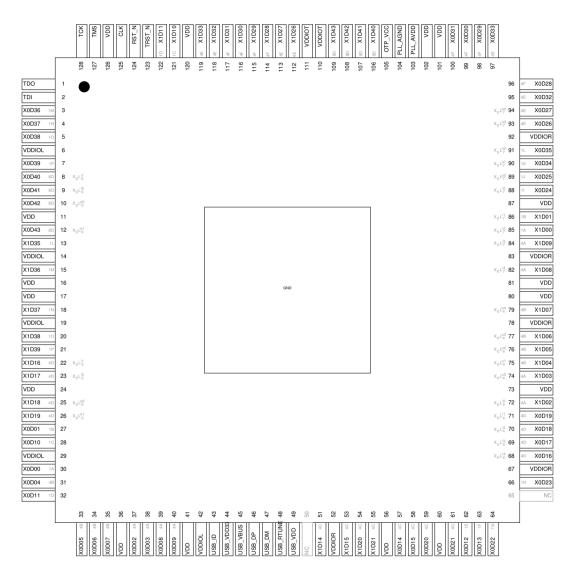

# 3 Pin Configuration

### 6 Product Overview

The XU212-512-TQ128 is a powerful device that consists of two xCORE Tiles, each comprising a flexible logical processing cores with tightly integrated I/O and on-chip memory.

#### 6.1 Logical cores

Each tile has 6 active logical cores, which issue instructions down a shared fivestage pipeline. Instructions from the active cores are issued round-robin. If up to five logical cores are active, each core is allocated a fifth of the processing cycles. If more than five logical cores are active, each core is allocated at least 1/n cycles (for *n* cores). Figure 3 shows the guaranteed core performance depending on the number of cores used.

Figure 3: Logical core performance

| jure 3: | Speed | MIPS      | Frequency | Mi  | inimum | n MIPS | per cor | e (for <i>n</i> | l core | s) |  |

|---------|-------|-----------|-----------|-----|--------|--------|---------|-----------------|--------|----|--|

| al core | grade |           |           | 1   | 2      | 3      | 4       | 5               | 6      |    |  |

| mance   | 10    | 1000 MIPS | 500 MHz   | 100 | 100    | 100    | 100     | 100             | 83     |    |  |

There is no way that the performance of a logical core can be reduced below these predicted levels (unless *priority threads* are used: in this case the guaranteed minimum performance is computed based on the number of priority threads as defined in the architecture manual). Because cores may be delayed on I/O, however, their unused processing cycles can be taken by other cores. This means that for more than five logical cores, the performance of each core is often higher than the predicted minimum but cannot be guaranteed.

The logical cores are triggered by events instead of interrupts and run to completion. A logical core can be paused to wait for an event.

### 6.2 xTIME scheduler

The xTIME scheduler handles the events generated by xCORE Tile resources, such as channel ends, timers and I/O pins. It ensures that all events are serviced and synchronized, without the need for an RTOS. Events that occur at the I/O pins are handled by the Hardware-Response ports and fed directly to the appropriate xCORE Tile. An xCORE Tile can also choose to wait for a specified time to elapse, or for data to become available on a channel.

Tasks do not need to be prioritised as each of them runs on their own logical xCORE. It is possible to share a set of low priority tasks on a single core using cooperative multitasking.

#### 6.3 Hardware Response Ports

Hardware Response ports connect an xCORE tile to one or more physical pins and as such define the interface between hardware attached to the XU212-512-TQ128, and the software running on it. A combination of 1 bit, 4 bit, 8 bit, 16 bit and 32 bit

11

If the USB PHY is used, then either a 24 MHz or 12 MHz oscillator must be used.

If a different tile frequency is required (eg, 500 MHz), then the PLL must be reprogrammed after boot to provide the required tile frequency. The XMOS tools perform this operation by default. Further details on configuring the clock can be found in the xCORE-200 Clock Frequency Control document.

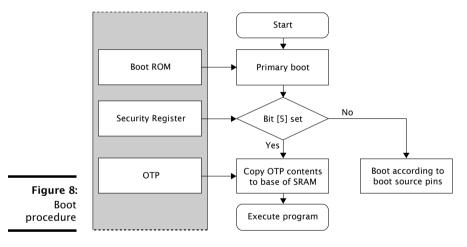

### 8 Boot Procedure

The device is kept in reset by driving RST\_N low. When in reset, all GPIO pins have a pull-down enabled. When the device is taken out of reset by releasing RST\_N the processor starts its internal reset process. After 15-150  $\mu$ s (depending on the input clock) the processor boots.

The xCORE Tile boot procedure is illustrated in Figure 8. If bit 5 of the security register (*see* §9.1) is set, the device boots from OTP. To get a high value, a 3K3 pull-up resistor should be strapped onto the pin. To assure a low value, a pull-down resistor is required if other external devices are connected to this port.

|            | X0D06 | X0D05 | X0D04 | Tile 0 boot   | Tile 1 boot   | Enabled links |

|------------|-------|-------|-------|---------------|---------------|---------------|

|            | 0     | 0     | 0     | QSPI master   | Channel end 0 | None          |

|            | 0     | 0     | 1     | SPI master    | Channel end 0 | None          |

| Figure 9:  | 0     | 1     | 0     | SPI slave     | Channel end 0 | None          |

| oot source | 0     | 1     | 1     | SPI slave     | SPI slave     | None          |

| pins       | 1     | 0     | 0     | Channel end 0 | Channel end 0 | XL0 (2w)      |

The boot image has the following format:

- ► A 32-bit program size *s* in words.

- Program consisting of  $s \times 4$  bytes.

Boot

### 9 Memory

#### 9.1 OTP

Each xCORE Tile integrates 8 KB one-time programmable (OTP) memory along with a security register that configures system wide security features. The OTP holds data in four sectors each containing 512 rows of 32 bits which can be used to implement secure bootloaders and store encryption keys. Data for the security register is loaded from the OTP on power up. All additional data in OTP is copied from the OTP to SRAM and executed first on the processor.

The OTP memory is programmed using three special I/O ports: the OTP address port is a 16-bit port with resource ID 0x100200, the OTP data is written via a 32-bit port with resource ID 0x200100, and the OTP control is on a 16-bit port with ID 0x100300. Programming is performed through libotp and xburn.

#### 9.2 SRAM

Each xCORE Tile integrates a single 256KBSRAM bank for both instructions and data. All internal memory is 32 bits wide, and instructions are either 16-bit or 32-bit. Byte (8-bit), half-word (16-bit) or word (32-bit) accesses are supported and are executed within one tile clock cycle. There is no dedicated external memory interface, although data memory can be expanded through appropriate use of the ports.

### 10 USB PHY

The USB PHY provides High-Speed and Full-Speed, device, host, and on-the-go functionality. The PHY is configured through a set of peripheral registers (Appendix F), and data is communicated through ports on the digital node. A library, XUD, is provided to implement *USB-device* functionality.

The USB PHY is connected to the ports on Tile 0 and Tile 1 as shown in Figure 14. When the USB PHY is enabled on Tile 0, the ports shown can on Tile 0 only be used with the USB PHY. When the USB PHY is enabled on Tile 1, then the ports shown can on Tile 1 only be used with the USB PHY. All other IO pins and ports are unaffected. The USB PHY should not be enabled on both tiles. Two clock blocks can be used to clock the USB ports. One clock block for the TXDATA path, and one clock block for the RXDATA path. Details on how to connect those ports are documented in an application note on USB for xCORE-200.

An external resistor of 43.2 ohm (1% tolerance) should connect USB\_RTUNE to ground, as close as possible to the device.

#### 10.1 USB VBUS

USB\_VBUS need not be connected if the device is wholly powered by USB, and the device is used to implement a *USB-device*.

The JTAG usercode register can be read by using the USERCODE instruction. Its contents are specified in Figure 18. The OTP User ID field is read from bits [22:31] of the security register on xCORE Tile 0, *see* §9.1 (all zero on unprogrammed devices).

Figure 18: USERCODE return value

| 10.        | Bit | 31 |   |   |      |      |    |   |   |   |   |     |     | ι | Jser | code | Reg | jiste | r |   |   |       |      |       |      |   |   |   |   |   | В | it0 |

|------------|-----|----|---|---|------|------|----|---|---|---|---|-----|-----|---|------|------|-----|-------|---|---|---|-------|------|-------|------|---|---|---|---|---|---|-----|

| 18:        |     |    |   | 0 | TP U | lser | ID |   |   |   |   | Unu | sed |   |      |      |     |       |   |   |   | Silic | on l | Revis | sion |   |   |   |   |   |   |     |

| DDE<br>lue | 0   | 0  | 0 | 0 | 0    | 0    | 0  | 0 | 0 | 0 | 0 | 0   | 0   | 0 | 1    | 0    | 1   | 0     | 0 | 0 | 0 | 0     | 0    | 0     | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

| lue        |     | (  | ) |   |      | (    | )  |   |   |   | ) |     |     | Ĩ | 2    |      |     | 8     | 3 |   |   | (     | )    |       |      | ( | ) |   |   | C | ) |     |

# 12 Board Integration

The device has the following power supply pins:

- ▶ VDD pins for the xCORE Tile, including a USB\_VDD pin that powers the USB PHY

- VDDIO pins for the I/O lines. Separate I/O supplies are provided for the left, top, and right side of the package; different I/O voltages may be supplied on those. The signal description (Section 4) specifies which I/O is powered from which power-supply

- ▶ PLL\_AVDD pins for the PLL

- ▶ OTP\_VCC pins for the OTP

- ► A USB\_VDD33 pin for the analogue supply to the USB-PHY

Several pins of each type are provided to minimize the effect of inductance within the package, all of which must be connected. The power supplies must be brought up monotonically and input voltages must not exceed specification at any time.

The VDD supply must ramp from 0V to its final value within  $10 \, \text{ms}$  to ensure correct startup.

The VDDIO and OTP\_VCC supply must ramp to its final value before VDD reaches 0.4 V.

The PLL\_AVDD supply should be separated from the other noisier supplies on the board. The PLL requires a very clean power supply, and a low pass filter (for example, a  $4.7 \Omega$  resistor and 100 nF multi-layer ceramic capacitor) is recommended on this pin.

The following ground pins are provided:

- PLL\_AGND for PLL\_AVDD

- ▶ GND for all other supplies

All ground pins must be connected directly to the board ground.

The VDD and VDDIO supplies should be decoupled close to the chip by several 100 nF low inductance multi-layer ceramic capacitors between the supplies and GND

(for example, 100nF 0402 for each supply pin). The ground side of the decoupling capacitors should have as short a path back to the GND pins as possible. A bulk decoupling capacitor of at least 10 uF should be placed on each of these supplies.

RST\_N is an active-low asynchronous-assertion global reset signal. Following a reset, the PLL re-establishes lock after which the device boots up according to the boot mode (see §8). RST\_N and must be asserted low during and after power up for 100 ns.

#### 12.1 USB connections

USB\_VBUS should be connected to the VBUS pin of the USB connector. A 2.2 uF capacitor to ground is required on the VBUS pin. A ferrite bead may be used to reduce HF noise.

For self-powered systems, a bleeder resistor may be required to stop VBUS from floating when no USB cable is attached.

USB DP and USB DN should be connected to the USB connector. USB ID does not need to be connected.

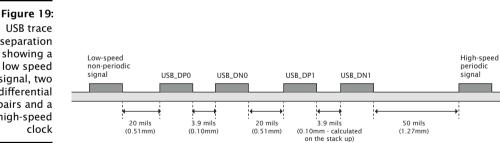

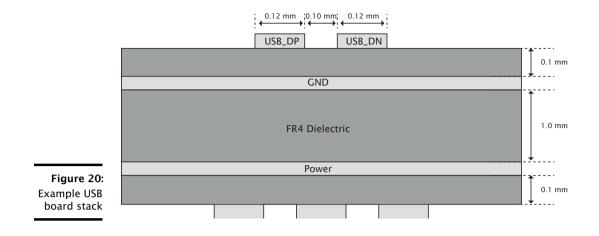

### 12.2 USB signal routing and placement

The USB\_DP and USB\_DN lines are the positive and negative data polarities of a high speed USB signal respectively. Their high-speed differential nature implies that they must be coupled and properly isolated. The board design must ensure that the board traces for USB DP and USB DN are tightly matched. In addition, according to the USB 2.0 specification, the USB\_DP and USB\_DN differential impedance must be **90** Ω.

#### 12.2.1 General routing and placement guidelines

The following guidelines will help to avoid signal guality and EMI problems on high speed USB designs. They relate to a four-layer (Signal, GND, Power, Signal) PCB.

For best results, most of the routing should be done on the top layer (assuming the USB connector and XS2-U12A-512-TQ128 are on the top layer) closest to GND.

USB trace separation showing a low speed signal, two differential pairs and a high-speed

Reference planes should be below the transmission lines in order to maintain control of the trace impedance.

We recommend that the high-speed clock and high-speed USB differential pairs are routed first before any other routing. When routing high speed USB signals, the following guidelines should be followed:

- ▶ High speed differential pairs should be routed together.

- ▶ High-speed USB signal pair traces should be trace-length matched. Maximum trace-length mismatch should be no greater than 4mm.

- ▶ Ensure that high speed signals (clocks, USB differential pairs) are routed as far away from off-board connectors as possible.

- ▶ High-speed clock and periodic signal traces that run parallel should be at least 1.27mm away from USB\_DP/USB\_DN (see Figure 19).

- Low-speed and non-periodic signal traces that run parallel should be at least 0.5mm away from USB\_DP/USB\_DN (see Figure 19).

- ▶ Route high speed USB signals on the top of the PCB wherever possible.

- Route high speed USB traces over continuous power planes, with no breaks. If a trade-off must be made, changing signal layers is preferable to crossing plane splits.

- Follow the  $20 \times h$  rule; keep traces  $20 \times h$  (the height above the power plane) away from the edge of the power plane.

- ▶ Use a minimum of vias in high speed USB traces.

- Avoid corners in the trace. Where necessary, rather than turning through a 90 degree angle, use two 45 degree turns or an arc.

### 13.5 Power Consumption

| Symbol     | Parameter              | MIN | TYP  | MAX | UNITS   | Notes      |

|------------|------------------------|-----|------|-----|---------|------------|

| I(DDCQ)    | Quiescent VDD current  |     | 45   |     | mA      | A, B, C    |

| PD         | Tile power dissipation |     | 325  |     | µW/MIPS | A, D, E, F |

| IDD        | Active VDD current     |     | 570  | 700 | mA      | A, G       |

| I(ADDPLL)  | PLL_AVDD current       |     | 5    | 7   | mA      | Н          |

| I(VDD33)   | VDD33 current          |     | 26.7 |     | mA      | I          |

| I(USB_VDD) | USB_VDD current        |     | 8.27 |     | mA      | J          |

Figure 26: xCORE Tile currents

A Use for budgetary purposes only.

- B Assumes typical tile and I/O voltages with no switching activity.

- C Includes PLL current.

- D Assumes typical tile and I/O voltages with nominal switching activity.

- E Assumes 1 MHz = 1 MIPS.

- F PD(TYP) value is the usage power consumption under typical operating conditions.

- G Measurement conditions: VDD = 1.0 V, VDDIO = 3.3 V, 25 °C, 500 MHz, average device resource usage.

- H PLL\_AVDD = 1.0 V

- I HS mode transmitting while driving all 0's data (constant JKJK on DP/DM). Loading of 10 pF. Transfers do not include any interpacket delay.

- J HS receive mode; no traffic.

The tile power consumption of the device is highly application dependent and should be used for budgetary purposes only.

More detailed power analysis can be found in the XS1-U Power Consumption document,

| 1 | 3.6 | Clock |

|---|-----|-------|

|   |     |       |

Figure 27: Clock

| Symbol | Parameter                 | MIN  | TYP | MAX | UNITS | Notes |

|--------|---------------------------|------|-----|-----|-------|-------|

| f      | Frequency                 | 9    | 24  | 25  | MHz   |       |

| SR     | Slew rate                 | 0.10 |     |     | V/ns  |       |

| TJ(LT) | Long term jitter (pk-pk)  |      |     | 2   | %     | А     |

| f(MAX) | Processor clock frequency |      |     | 500 | MHz   | В     |

A Percentage of CLK period.

B Assumes typical tile and I/O voltages with nominal activity.

Further details can be found in the XS1-U Clock Frequency Control document,

-XM()S

|                             | Symbol       | Parameter                                                           | MIN | TYP | MAX | UNITS | Notes |

|-----------------------------|--------------|---------------------------------------------------------------------|-----|-----|-----|-------|-------|

| <b></b>                     | T(XOVALID)   | Input data valid window                                             | 8   |     |     | ns    |       |

| Figure 28:                  | T(XOINVALID) | Output data invalid window                                          | 9   |     |     | ns    |       |

| I/O AC char-<br>acteristics | T(XIFMAX)    | Rate at which data can be sampled with respect to an external clock |     |     | 60  | MHz   |       |

#### 13.7 xCORE Tile I/O AC Characteristics

The input valid window parameter relates to the capability of the device to capture data input to the chip with respect to an external clock source. It is calculated as the sum of the input setup time and input hold time with respect to the external clock as measured at the pins. The output invalid window specifies the time for which an output is invalid with respect to the external clock. Note that these parameters are specified as a window rather than absolute numbers since the device provides functionality to delay the incoming clock with respect to the incoming data.

Information on interfacing to high-speed synchronous interfaces can be found in the XS1 Port I/O Timing document, X5821.

#### 13.8 xConnect Link Performance

|            | Symbol     | Parameter                      | MIN | TYP | MAX | UNITS  | Notes |

|------------|------------|--------------------------------|-----|-----|-----|--------|-------|

|            | B(2blinkP) | 2b link bandwidth (packetized) |     |     | 87  | MBit/s | A, B  |

| Figure 29: | B(5blinkP) | 5b link bandwidth (packetized) |     |     | 217 | MBit/s | A, B  |

| Link       | B(2blinkS) | 2b link bandwidth (streaming)  |     |     | 100 | MBit/s | В     |

| erformance | B(5blinkS) | 5b link bandwidth (streaming)  |     |     | 250 | MBit/s | В     |

perform

A Assumes 32-byte packet in 3-byte header mode. Actual performance depends on size of the header and payload.

B 7.5 ns symbol time.

The asynchronous nature of links means that the relative phasing of CLK clocks is not important in a multi-clock system, providing each meets the required stability criteria.

| 1 | 3.9 | ITAG | Timing |

|---|-----|------|--------|

|   | 5.5 | 1170 | 1 mmg  |

|    | Symbol   | Parameter                     | MIN | TYP | MAX | UNITS | Notes |

|----|----------|-------------------------------|-----|-----|-----|-------|-------|

|    | f(TCK_D) | TCK frequency (debug)         |     |     | 18  | MHz   |       |

|    | f(TCK_B) | TCK frequency (boundary scan) |     |     | 10  | MHz   |       |

| -  | T(SETUP) | TDO to TCK setup time         | 5   |     |     | ns    | А     |

| ): | T(HOLD)  | TDO to TCK hold time          | 5   |     |     | ns    | А     |

| 9  | T(DELAY) | TCK to output delay           |     |     | 15  | ns    | В     |

Figure 30 JTAG timing

A Timing applies to TMS and TDI inputs.

B Timing applies to TDO output from negative edge of TCK.

All JTAG operations are synchronous to TCK apart from the global asynchronous reset TRST\_N.

-XM()S-

A write message comprises the following:

| control-token | 24-bit response        | 8-bit           | 8-bit | data | control-token |

|---------------|------------------------|-----------------|-------|------|---------------|

| 36            | channel-end identifier | register number | size  |      | 1             |

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

A read message comprises the following:

| control-token | 24-bit response        | 8-bit           | 8-bit | control-token |

|---------------|------------------------|-----------------|-------|---------------|

| 37            | channel-end identifier | register number | size  | 1             |

The response to the read message comprises either control token 3, data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

| Bits  | Perm | Init | Description                                                                                                                                                                                                                           |

|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                                                                                                                                                                              |

| 25:18 | RW   | 0    | RGMII TX data delay value (in PLL output cycle increments)                                                                                                                                                                            |

| 17:9  | RW   | 0    | RGMII TX clock divider value. TX clk rises when counter (clocked<br>by PLL output) reaches this value and falls when counter reaches<br>(value»1). Value programmed into this field should be actual<br>divide value required minus 1 |

| 8     | RW   | 0    | Enable RGMII interface periph ports                                                                                                                                                                                                   |

| 7:6   | RO   | -    | Reserved                                                                                                                                                                                                                              |

| 5     | RW   | 0    | Select the dynamic mode (1) for the clock divider when the clock divider is enabled. In dynamic mode the clock divider is only activated when all active threads are paused. In static mode the clock divider is always enabled.      |

| 4     | RW   | 0    | Enable the clock divider. This divides the output of the PLL to facilitate one of the low power modes.                                                                                                                                |

| 3     | RO   | -    | Reserved                                                                                                                                                                                                                              |

| 2     | RW   |      | Select between UTMI (1) and ULPI (0) mode.                                                                                                                                                                                            |

| 1     | RW   |      | Enable the ULPI Hardware support module                                                                                                                                                                                               |

| 0     | RO   | -    | Reserved                                                                                                                                                                                                                              |

0x02: xCORE Tile control

### B.4 xCORE Tile boot status: 0x03

This read-only register describes the boot status of the xCORE tile.

-XMOS"-

|         | Bits  | Perm | Init | Description                                               |

|---------|-------|------|------|-----------------------------------------------------------|

|         | 31:24 | RO   | -    | Reserved                                                  |

|         | 23:16 | RO   |      | Processor number.                                         |

|         | 15:9  | RO   | -    | Reserved                                                  |

|         | 8     | RO   |      | Overwrite BOOT_MODE.                                      |

|         | 7:6   | RO   | -    | Reserved                                                  |

|         | 5     | RO   |      | Indicates if core1 has been powered off                   |

|         | 4     | RO   |      | Cause the ROM to not poll the OTP for correct read levels |

| -       | 3     | RO   |      | Boot ROM boots from RAM                                   |

| ).<br>2 | 2     | RO   |      | Boot ROM boots from JTAG                                  |

| 5       | 1:0   | RO   |      | The boot PLL mode pin value.                              |

0x03: xCORE Tile boot status

### **B.5** Security configuration: 0x05

| Bits  | Perm | Init | Description                                                 |

|-------|------|------|-------------------------------------------------------------|

| 31    | RW   |      | Disables write permission on this register                  |

| 30:15 | RO   | -    | Reserved                                                    |

| 14    | RW   |      | Disable access to XCore's global debug                      |

| 13    | RO   | -    | Reserved                                                    |

| 12    | RW   |      | lock all OTP sectors                                        |

| 11:8  | RW   |      | lock bit for each OTP sector                                |

| 7     | RW   |      | Enable OTP reduanacy                                        |

| 6     | RO   | -    | Reserved                                                    |

| 5     | RW   |      | Override boot mode and read boot image from OTP             |

| 4     | RW   |      | Disable JTAG access to the PLL/BOOT configuration registers |

| 3:1   | RO   | -    | Reserved                                                    |

| 0     | RW   |      | Disable access to XCore's JTAG debug TAP                    |

Copy of the security register as read from OTP.

0x05: Security configuration

## B.6 Ring Oscillator Control: 0x06

There are four free-running oscillators that clock four counters. The oscillators can be started and stopped using this register. The counters should only be read when the ring oscillator has been stopped for at least 10 core clock cycles (this can be achieved by inserting two nop instructions between the SETPS and GETPS). The counter values can be read using four subsequent registers. The ring oscillators are asynchronous to the xCORE tile clock and can be used as a source of random bits.

**0x06:** Ring Oscillator Control

| Bits | Perm | Init | Description                        |

|------|------|------|------------------------------------|

| 31:2 | RO   | -    | Reserved                           |

| 1    | RW   | 0    | Core ring oscillator enable.       |

| 0    | RW   | 0    | Peripheral ring oscillator enable. |

### B.7 Ring Oscillator Value: 0x07

This register contains the current count of the xCORE Tile Cell ring oscillator. This value is not reset on a system reset.

-XMOS-

#### B.18 Debug interrupt data: 0x16

On a data watchpoint, this register contains the effective address of the memory operation that triggered the debugger. On a resource watchpoint, it countains the resource identifier.

**0x16:** Debug interrupt data

| 1 <b>6:</b><br>ug | Bits | Perm | Init | Description |

|-------------------|------|------|------|-------------|

| ata               | 31:0 | DRW  |      | Value.      |

### B.19 Debug core control: 0x18

This register enables the debugger to temporarily disable logical cores. When returning from the debug interrupts, the cores set in this register will not execute. This enables single stepping to be implemented.

0x18: Debug core control

|            | Bits | Perm | Init | Description                                                                                                                                       |

|------------|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|            | 31:8 | RO   | -    | Reserved                                                                                                                                          |

| :<br>:<br> | 7:0  | DRW  |      | 1-hot vector defining which threads are stopped when not in<br>debug mode. Every bit which is set prevents the respective<br>thread from running. |

#### B.20 Debug scratch: 0x20 .. 0x27

A set of registers used by the debug ROM to communicate with an external debugger, for example over JTAG. This is the same set of registers as the Debug Scratch registers in the xCORE tile configuration.

0x20 .. 0x27: Debug scratch

| 0x27:<br>ebug | Bits | Perm | Init | Description |

|---------------|------|------|------|-------------|

| ratch         | 31:0 | DRW  |      | Value.      |

### B.21 Instruction breakpoint address: 0x30 .. 0x33

-XM()S

This register contains the address of the instruction breakpoint. If the PC matches this address, then a debug interrupt will be taken. There are four instruction breakpoints that are controlled individually.

42

# C Tile Configuration

The xCORE Tile control registers can be accessed using configuration reads and writes (use write\_tile\_config\_reg(tileref, ...) and read\_tile\_config\_reg(tileref,  $\rightarrow$  ...) for reads and writes).

| Number    | Perm | Description                                    |

|-----------|------|------------------------------------------------|

| 0x00      | CRO  | Device identification                          |

| 0x01      | CRO  | xCORE Tile description 1                       |

| 0x02      | CRO  | xCORE Tile description 2                       |

| 0x04      | CRW  | Control PSwitch permissions to debug registers |

| 0x05      | CRW  | Cause debug interrupts                         |

| 0x06      | CRW  | xCORE Tile clock divider                       |

| 0x07      | CRO  | Security configuration                         |

| 0x20 0x27 | CRW  | Debug scratch                                  |

| 0x40      | CRO  | PC of logical core 0                           |

| 0x41      | CRO  | PC of logical core 1                           |

| 0x42      | CRO  | PC of logical core 2                           |

| 0x43      | CRO  | PC of logical core 3                           |

| 0x44      | CRO  | PC of logical core 4                           |

| 0x45      | CRO  | PC of logical core 5                           |

| 0x46      | CRO  | PC of logical core 6                           |

| 0x47      | CRO  | PC of logical core 7                           |

| 0x60      | CRO  | SR of logical core 0                           |

| 0x61      | CRO  | SR of logical core 1                           |

| 0x62      | CRO  | SR of logical core 2                           |

| 0x63      | CRO  | SR of logical core 3                           |

| 0x64      | CRO  | SR of logical core 4                           |

| 0x65      | CRO  | SR of logical core 5                           |

| 0x66      | CRO  | SR of logical core 6                           |

| 0x67      | CRO  | SR of logical core 7                           |

Figure 35: Summary

### C.1 Device identification: 0x00

This register identifies the xCORE Tile

-XMOS°

**0x04:** Control PSwitch permissions to debug registers

| Bits | Perm | Init | Description                                                                                                     |

|------|------|------|-----------------------------------------------------------------------------------------------------------------|

| 31   | CRW  | 0    | When 1 the PSwitch is restricted to RO access to all CRW registers from SSwitch, XCore(PS_DBG_Scratch) and JTAG |

| 30:1 | RO   | -    | Reserved                                                                                                        |

| 0    | CRW  | 0    | When 1 the PSwitch is restricted to RO access to all CRW registers from SSwitch                                 |

### C.5 Cause debug interrupts: 0x05

This register can be used to raise a debug interrupt in this xCORE tile.

0x05: Cause debug interrupts

| Bits | Perm | Init | Description                                 |

|------|------|------|---------------------------------------------|

| 31:2 | RO   | -    | Reserved                                    |

| 1    | CRW  | 0    | 1 when the processor is in debug mode.      |

| 0    | CRW  | 0    | Request a debug interrupt on the processor. |

### C.6 xCORE Tile clock divider: 0x06

This register contains the value used to divide the PLL clock to create the xCORE tile clock. The divider is enabled under control of the tile control register

0x06: xCORE Tile clock divider

| Bits  | Perm | Init | Description                                                   |

|-------|------|------|---------------------------------------------------------------|

| 31    | CRW  | 0    | Clock disable. Writing '1' will remove the clock to the tile. |

| 30:16 | RO   | -    | Reserved                                                      |

| 15:0  | CRW  | 0    | Clock divider.                                                |

### C.7 Security configuration: 0x07

Copy of the security register as read from OTP.

48

### C.24 SR of logical core 7: 0x67

Value of the SR of logical core 7

| 0x67:         |      |      |      |             |

|---------------|------|------|------|-------------|

| SR of logical | Bits | Perm | Init | Description |

| core 7        | 31:0 | CRO  |      | Value.      |

| Bits | Perm | Init | Description                                             |

|------|------|------|---------------------------------------------------------|

| 31:5 | RO   | -    | Reserved                                                |

| 4    | RW   |      | Reserved.                                               |

| 3:2  | RO   | -    | Reserved                                                |

| 1    | RW   |      | If set, XCore1 is the source of last GlobalDebug event. |

| 0    | RW   |      | If set, XCore0 is the source of last GlobalDebug event. |

**0x1F:** Debug source

### D.15 Link status, direction, and network: 0x20 .. 0x28

These registers contain status information for low level debugging (read-only), the network number that each link belongs to, and the direction that each link is part of. The registers control links 0..7.

| Bits  | Perm | Init | Description                                                                                 |  |

|-------|------|------|---------------------------------------------------------------------------------------------|--|

| 31:26 | RO   | -    | Reserved                                                                                    |  |

| 25:24 | RO   |      | Identify the SRC_TARGET type 0 - SLink, 1 - PLink, 2 - SSCTL, 3 - Undefine.                 |  |

| 23:16 | RO   |      | When the link is in use, this is the destination link number to which all packets are sent. |  |

| 15:12 | RO   | -    | Reserved                                                                                    |  |

| 11:8  | RW   | 0    | The direction that this link operates in.                                                   |  |

| 7:6   | RO   | -    | Reserved                                                                                    |  |

| 5:4   | RW   | 0    | Determines the network to which this link belongs, reset as 0.                              |  |

| 3     | RO   | -    | Reserved                                                                                    |  |

| 2     | RO   |      | 1 when the current packet is considered junk and will be thrown away.                       |  |

| 1     | RO   |      | 1 when the dest side of the link is in use.                                                 |  |

| 0     | RO   |      | 1 when the source side of the link is in use.                                               |  |

0x20 .. 0x28: Link status, direction, and network

### D.16 PLink status and network: 0x40 .. 0x47

These registers contain status information and the network number that each processor-link belongs to.

-XMOS-

# E USB Node Configuration

The USB node control registers can be accessed using configuration reads and writes (use write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device, ...) for reads and writes).

| Number | Perm | Description                    |  |

|--------|------|--------------------------------|--|

| 0x00   | RO   | Device identification register |  |

| 0x04   | RW   | Node configuration register    |  |

| 0x05   | RW   | Node identifier                |  |

| 0x51   | RW   | System clock frequency         |  |

| 0x80   | RW   | Link Control and Status        |  |

Figure 37: Summary

#### E.1 Device identification register: 0x00

This register contains version information, and information on power-on behavior.

0x00: Device identification register

| Bits  | Perm | Init | Description                      |

|-------|------|------|----------------------------------|

| 31:24 | RO   | 0x0F | Chip identifier                  |

| 23:16 | RO   | -    | Reserved                         |

| 15:8  | RO   | 0x02 | Revision number of the USB block |

| 7:0   | RO   | 0x00 | Version number of the USB block  |

#### E.2 Node configuration register: 0x04

This register is used to set the communication model to use (1 or 3 byte headers), and to prevent any further updates.

**0x04:** Node configuration register

|           | Bits | Perm | Init | Description                                                                                          |  |

|-----------|------|------|------|------------------------------------------------------------------------------------------------------|--|

| 04:<br>de | 31   | RW   | 0    | Set to 1 to disable further updates to the node configuration and link control and status registers. |  |

| on        | 30:1 | RO   | -    | Reserved                                                                                             |  |

| er        | 0    | RW   | 0    | Header mode. 0: 3-byte headers; 1: 1-byte headers.                                                   |  |

# F USB PHY Configuration

The USB PHY is connected to the ports shown in section 10.

The USB PHY is peripheral 1. The control registers are accessed using 32-bit reads and writes (use write\_periph\_32(device, 1, ...) and read\_periph\_32(device,  $\rightarrow$  1, ...) for reads and writes).

| Number | Perm | Description             |  |

|--------|------|-------------------------|--|

| 0x00   | WO   | UIFM reset              |  |

| 0x04   | RW   | UIFM IFM control        |  |

| 0x08   | RW   | UIFM Device Address     |  |

| 0x0C   | RW   | UIFM functional control |  |

| 0x10   | RW   | UIFM on-the-go control  |  |

| 0x14   | RO   | UIFM on-the-go flags    |  |

| 0x18   | RW   | UIFM Serial Control     |  |

| 0x1C   | RW   | UIFM signal flags       |  |

| 0x20   | RW   | UIFM Sticky flags       |  |

| 0x24   | RW   | UIFM port masks         |  |

| 0x28   | RW   | UIFM SOF value          |  |

| 0x2C   | RO   | UIFM PID                |  |

| 0x30   | RO   | UIFM Endpoint           |  |

| 0x34   | RW   | UIFM Endpoint match     |  |

| 0x38   | RW   | OTG Flags mask          |  |

| 0x3C   | RW   | UIFM power signalling   |  |

| 0x40   | RW   | UIFM PHY control        |  |

Figure 38: Summary

#### F.1 UIFM reset: 0x00

A write to this register with any data resets all UIFM state, but does not otherwise affect the phy.

| 0x00:      | Bits | Perm | Init | Description |

|------------|------|------|------|-------------|

| UIFM reset | 31:0 | WO   |      | Value.      |

#### F.2 UIFM IFM control: 0x04

General settings of the UIFM IFM state machine.

| Bits | Perm | Init | Description                                        |  |

|------|------|------|----------------------------------------------------|--|

| 31:8 | RO   | -    | Reserved                                           |  |

| 7    | RW   | 0    | Set to 1 to switch UIFM to EXTVBUSIND mode.        |  |

| 6    | RW   | 0    | Set to 1 to switch UIFM to DRVVBUSEXT mode.        |  |

| 5    | RO   | -    | Reserved                                           |  |

| 4    | RW   | 0    | Set to 1 to switch UIFM to UTMI+ CHRGVBUS mode.    |  |

| 3    | RW   | 0    | Set to 1 to switch UIFM to UTMI+ DISCHRGVBUS mode. |  |

| 2    | RW   | 0    | Set to 1 to switch UIFM to UTMI+ DMPULLDOWN mode.  |  |

| 1    | RW   | 0    | Set to 1 to switch UIFM to UTMI+ DPPULLDOWN mode.  |  |

| 0    | RW   | 0    | Set to 1 to switch UIFM to IDPULLUP mode.          |  |

**0x10:** UIFM on-the-go control

## F.6 UIFM on-the-go flags: 0x14

Status flags used for on-the-go negotiation

| Bits | Perm | Init | Description                  |  |

|------|------|------|------------------------------|--|

| 31:6 | RO   | -    | Reserved                     |  |

| 5    | RO   | 0    | Value of UTMI+ Bvalid flag.  |  |

| 4    | RO   | 0    | Value of UTMI+ IDGND flag.   |  |

| 3    | RO   | 0    | Value of UTMI+ HOSTDIS flag. |  |

| 2    | RO   | 0    | Value of UTMI+ VBUSVLD flag. |  |

| 1    | RO   | 0    | Value of UTMI+ SESSVLD flag. |  |

| 0    | RO   | 0    | Value of UTMI+ SESSEND flag. |  |

-XMOS°

**0x14:** UIFM on-the-go flags