Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 18x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

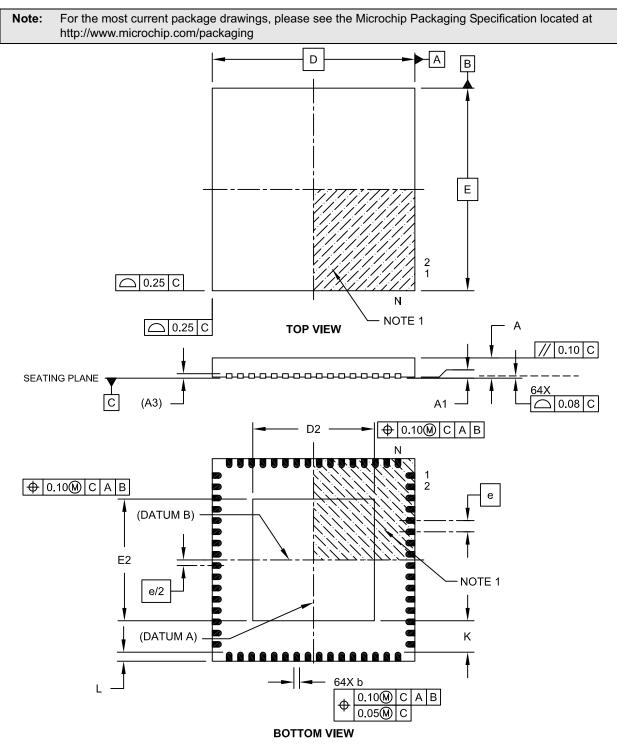

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp206a-e-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via Email at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

## Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

### TABLE 4-31: SYSTEM CONTROL REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8       | Bit 7   | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2     | Bit 1   | Bit 0 | All<br>Resets       |

|-----------|------|--------|--------|-----------|--------|--------|--------|-----------|-------------|---------|--------|--------|-------|-------|-----------|---------|-------|---------------------|

| RCON      | 0740 | TRAPR  | IOPUWR | —         | —      | —      | _      | _         | VREGS       | EXTR    | SWR    | SWDTEN | WDTO  | SLEEP | IDLE      | BOR     | POR   | xxxxx(1)            |

| OSCCON    | 0742 | _      | (      | COSC<2:0> | >      | _      | ١      | NOSC<2:0  | >           | CLKLOCK | _      | LOCK   |       | CF    | _         | LPOSCEN | OSWEN | <sub>0300</sub> (2) |

| CLKDIV    | 0744 | ROI    | [      | DOZE<2:0> | >      | DOZEN  | FI     | RCDIV<2:0 | )>          | PLLPOS  | T<1:0> | —      |       | F     | PLLPRE<4: | :0>     |       | 3040                |

| PLLFBD    | 0746 |        | —      |           | —      | —      | _      |           | PLLDIV<8:0> |         |        |        |       | 0030  |           |         |       |                     |

| OSCTUN    | 0748 |        | —      |           | _      | —      | _      | _         | TUN<5:0>    |         |        |        |       | 0000  |           |         |       |                     |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: RCON register Reset values dependent on type of Reset.

2: OSCCON register Reset values dependent on the FOSC Configuration bits and by type of Reset.

#### TABLE 4-32: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets       |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|--------|-------|--------|-------|---------------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | _      | _      | _      | —     | _     | _     | ERASE |       |       |        | NVMO  | P<3:0> |       | <sub>0000</sub> (1) |

| NVMKEY    | 0766 | —      |        | —      |        |        |        | —     |       |       |       |       | NVMKE | Y<7:0> |       |        |       | 0000                |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: Reset value shown is for POR only. Value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

#### TABLE 4-33: PMD REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|-------|--------|-------|---------------|

| PMD1      | 0770 | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | —      | _     | —     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | C2MD  | C1MD   | AD1MD | 0000          |

| PMD2      | 0772 | IC8MD  | IC7MD  | IC6MD  | IC5MD  | IC4MD  | IC3MD  | IC2MD | IC1MD | OC8MD  | OC7MD | OC6MD | OC5MD  | OC4MD  | OC3MD | OC2MD  | OC1MD | 0000          |

| PMD3      | 0774 | T9MD   | T8MD   | T7MD   | T6MD   | -      | _      | _     | —     | —      | -     | —     |        | _      | _     | I2C2MD | AD2MD | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

### 7.3 Interrupt Control and Status Registers

PIC24HJXXXGPX06A/X08A/X10A devices implement a total of 30 registers for the interrupt controller:

- INTCON1

- INTCON2

- IFS0 through IFS4

- IEC0 through IEC4

- IPC0 through IPC17

- INTTREG

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table.

The IFS registers maintain all of the interrupt request flags. Each source of interrupt has a Status bit, which is set by the respective peripherals or external signal and is cleared via software.

The IEC registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals. The IPC registers are used to set the interrupt priority level for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

The INTTREG register contains the associated interrupt vector number and the new CPU interrupt priority level, which are latched into vector number (VEC-NUM<6:0>) and Interrupt level (ILR<3:0>) bit fields in the INTTREG register. The new interrupt priority level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence that they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having vector number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0>, and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

Although they are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. The CPU STATUS register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU interrupt priority level. The user can change the current CPU priority level by writing to the IPL bits.

The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-1 through Register 7-32.

### REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

| R/W-0         | R/W-0          | U-0                                | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|---------------|----------------|------------------------------------|------------------|------------------|------------------|-----------------|---------|

| T6IF          | DMA4IF         | _                                  | OC8IF            | OC7IF            | OC6IF            | OC5IF           | IC6IF   |

| bit 15        |                |                                    |                  |                  |                  |                 | bit 8   |

| R/W-0         | R/W-0          | R/W-0                              | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| IC5IF         | IC4IF          | IC3IF                              | DMA3IF           | C1IF             | C1RXIF           | SPI2IF          | SPI2EIF |

| bit 7         |                | 10011                              | Different        | 0.11             | <b>O</b> Hour    |                 | bit (   |

| Legend:       |                |                                    |                  |                  |                  |                 |         |

| R = Readab    | le bit         | W = Writable                       | bit              | U = Unimplei     | mented bit, read | l as '0'        |         |

| -n = Value a  | t POR          | '1' = Bit is set                   |                  | '0' = Bit is cle | ared             | x = Bit is unki | nown    |

| bit 15        | TEIE. Timore   | Interrupt Flag                     | Status bit       |                  |                  |                 |         |

| DIL 15        |                | request has oc                     |                  |                  |                  |                 |         |

|               |                | request has not                    |                  |                  |                  |                 |         |

| bit 14        | DMA4IF: DM     | A Channel 4 D                      | ata Transfer C   | Complete Interr  | rupt Flag Status | bit             |         |

|               |                | request has occ                    |                  |                  |                  |                 |         |

| bit 13        | •              | request has not<br>ited: Read as ' |                  |                  |                  |                 |         |

| bit 12        | •              | ut Compare Ch                      |                  | unt Elan Statur  | e hit            |                 |         |

|               | •              | request has oc                     |                  | upi i lag Status | 5 Dit            |                 |         |

|               |                | request has not                    |                  |                  |                  |                 |         |

| bit 11        | OC7IF: Output  | ut Compare Ch                      | annel 7 Interr   | upt Flag Status  | s bit            |                 |         |

|               |                | request has oco<br>request has not |                  |                  |                  |                 |         |

| bit 10        | OC6IF: Output  | ut Compare Ch                      | annel 6 Interr   | upt Flag Status  | s bit            |                 |         |

|               |                | request has oco<br>request has not |                  |                  |                  |                 |         |

| bit 9         | OC5IF: Output  | ut Compare Ch                      | annel 5 Interr   | upt Flag Status  | s bit            |                 |         |

|               |                | request has oc                     |                  |                  |                  |                 |         |

| <b>h</b> :+ 0 | •              | request has not                    |                  | The Otative hit  |                  |                 |         |

| bit 8         | -              | Capture Channe<br>request has oce  |                  | -lag Status bit  |                  |                 |         |

|               | •              | request has not                    |                  |                  |                  |                 |         |

| bit 7         | IC5IF: Input ( | Capture Channe                     | el 5 Interrupt I | -lag Status bit  |                  |                 |         |

|               |                | request has oc                     |                  |                  |                  |                 |         |

|               | •              | request has not                    |                  |                  |                  |                 |         |

| bit 6         |                | Capture Channe                     |                  | -lag Status bit  |                  |                 |         |

|               |                | request has oco<br>request has not |                  |                  |                  |                 |         |

| bit 5         | IC3IF: Input C | Capture Channe                     | el 3 Interrupt I | -lag Status bit  |                  |                 |         |

|               |                | request has oc                     |                  |                  |                  |                 |         |

| bit 4         | -              | request has not                    |                  | amplata Intorr   | unt Flog Status  | hit             |         |

| bit 4         |                | request has oc                     |                  |                  | rupt Flag Status | UIL             |         |

|               |                | request has not                    |                  |                  |                  |                 |         |

| bit 3         | •              | I Event Interrup                   |                  | bit              |                  |                 |         |

|               |                | request has oc                     |                  |                  |                  |                 |         |

|               | 0 = Interrupt  | request has not                    | occurred         |                  |                  |                 |         |

# PIC24HJXXXGPX06A/X08A/X10A

|                         | U-0                                                                                                                                                                       | U-0                                                                                                                           | U-0                                                                                                                     | U-0                                                    | U-0             | U-0             | U-0 |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------|-----------------|-----|

| —                       | _                                                                                                                                                                         |                                                                                                                               |                                                                                                                         | _                                                      | _               |                 |     |

| bit 15                  | -                                                                                                                                                                         |                                                                                                                               |                                                                                                                         |                                                        |                 |                 | bit |

| R/W-0                   | R/W-0                                                                                                                                                                     | R/W-0                                                                                                                         | R/W-0                                                                                                                   | U-0                                                    | R/W-0           | R/W-0           | U-0 |

| C2TXIF                  | C1TXIF                                                                                                                                                                    | DMA7IF                                                                                                                        | DMA6IF                                                                                                                  | _                                                      | U2EIF           | U1EIF           | _   |

| bit 7                   |                                                                                                                                                                           |                                                                                                                               |                                                                                                                         |                                                        |                 |                 | bit |

| Legend:                 |                                                                                                                                                                           |                                                                                                                               |                                                                                                                         |                                                        |                 |                 |     |

| R = Readable            | bit                                                                                                                                                                       | W = Writable                                                                                                                  | bit                                                                                                                     | U = Unimplen                                           | nented bit, rea | id as '0'       |     |

| -n = Value at F         | POR                                                                                                                                                                       | '1' = Bit is set                                                                                                              |                                                                                                                         | '0' = Bit is cle                                       | ared            | x = Bit is unkn | own |

| bit 7<br>bit 6<br>bit 5 | 1 = Interrupt r<br>0 = Interrupt r<br>C1TXIF: ECA<br>1 = Interrupt r<br>0 = Interrupt r<br>DMA7IF: DM                                                                     | request has occ<br>request has not<br>N1 Transmit D<br>request has occ<br>request has not<br>A Channel 7 Da                   | curred<br>occurred<br>ata Request I<br>curred<br>occurred                                                               | nterrupt Flag S<br>nterrupt Flag S<br>Complete Interru | tatus bit       | s bit           |     |

|                         |                                                                                                                                                                           | request has occ<br>request has not                                                                                            |                                                                                                                         |                                                        |                 |                 |     |

|                         | 0 = Interrupt r<br>DMA6IF: DM.<br>1 = Interrupt r                                                                                                                         | request has not                                                                                                               | : occurred<br>ata Transfer C<br>curred                                                                                  | Complete Interr                                        | upt Flag Statu  | s bit           |     |

| bit 4                   | 0 = Interrupt r<br>DMA6IF: DM<br>1 = Interrupt r<br>0 = Interrupt r                                                                                                       | equest has not<br>A Channel 6 Da<br>equest has occ                                                                            | coccurred<br>ata Transfer C<br>curred<br>coccurred                                                                      | Complete Interr                                        | upt Flag Statu  | s bit           |     |

|                         | 0 = Interrupt r<br>DMA6IF: DM.<br>1 = Interrupt r<br>0 = Interrupt r<br>Unimplemen<br>U2EIF: UART<br>1 = Interrupt r                                                      | request has not<br>A Channel 6 Da<br>request has occ<br>request has not                                                       | coccurred<br>ata Transfer C<br>curred<br>coccurred<br>o'<br>ot Flag Status<br>curred                                    |                                                        | upt Flag Statu  | s bit           |     |

| bit 4<br>bit 3          | 0 = Interrupt r<br>DMA6IF: DM.<br>1 = Interrupt r<br>0 = Interrupt r<br>Unimplemen<br>U2EIF: UART<br>1 = Interrupt r<br>0 = Interrupt r<br>U1EIF: UART<br>1 = Interrupt r | equest has not<br>A Channel 6 Da<br>equest has occ<br>equest has not<br>ted: Read as '0<br>2 Error Interrup<br>equest has occ | coccurred<br>ata Transfer C<br>curred<br>coccurred<br>of Flag Status<br>curred<br>coccurred<br>of Flag Status<br>curred | bit                                                    | upt Flag Statu  | s bit           |     |

#### REGISTER 7-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

### REGISTER 7-19: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

| U-0              | R/W-1                                                                                    | R/W-0                                                    | R/W-0                                              | U-0                | U-0             | U-0             | U-0   |

|------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------|--------------------|-----------------|-----------------|-------|

| —                |                                                                                          | CNIP<2:0>                                                |                                                    | —                  |                 | —               | —     |

| bit 15           |                                                                                          |                                                          |                                                    |                    |                 |                 | bit 8 |

|                  |                                                                                          | 5444                                                     |                                                    |                    | <b>-</b>        |                 |       |

| U-0              | R/W-1                                                                                    | R/W-0                                                    | R/W-0                                              | U-0                | R/W-1           | R/W-0           | R/W-0 |

|                  |                                                                                          | MI2C1IP<2:0>                                             |                                                    | —                  |                 | SI2C1IP<2:0>    |       |

| bit 7            |                                                                                          |                                                          |                                                    |                    |                 |                 | bit ( |

| Legend:          |                                                                                          |                                                          |                                                    |                    |                 |                 |       |

| R = Readab       | le bit                                                                                   | W = Writable                                             | bit                                                | U = Unimpler       | nented bit, rea | ad as '0'       |       |

| -n = Value a     | t POR                                                                                    | '1' = Bit is set                                         |                                                    | '0' = Bit is cle   |                 | x = Bit is unkr | nown  |

|                  |                                                                                          |                                                          |                                                    |                    |                 |                 |       |

| bit 15           | Unimpleme                                                                                | nted: Read as '                                          | כי                                                 |                    |                 |                 |       |

| bit 14-12        | CNIP<2:0>:                                                                               | Change Notifica                                          | tion Interrupt                                     | t Priority bits    |                 |                 |       |

|                  | 111 = Interru                                                                            | upt is priority 7 (                                      | nighest priori                                     | ty interrupt)      |                 |                 |       |

|                  | •                                                                                        |                                                          |                                                    |                    |                 |                 |       |

|                  | •                                                                                        |                                                          |                                                    |                    |                 |                 |       |

|                  | 001 = Interru                                                                            | upt is priority 1                                        |                                                    |                    |                 |                 |       |

|                  |                                                                                          | upt source is dis                                        | abled                                              |                    |                 |                 |       |

| bit 11-7         | Unimpleme                                                                                | nted: Read as '                                          | o'                                                 |                    |                 |                 |       |

| bit 6-4          | MI2C1IP<2:                                                                               | 0>: I2C1 Master                                          | Events Inter                                       | rupt Priority bits | ;               |                 |       |

|                  | 111 = Interru                                                                            | upt is priority 7 (                                      | nighest priori                                     | ty interrupt)      |                 |                 |       |

|                  | •                                                                                        |                                                          |                                                    |                    |                 |                 |       |

|                  | •                                                                                        |                                                          |                                                    |                    |                 |                 |       |

|                  | •                                                                                        |                                                          |                                                    |                    |                 |                 |       |

|                  | •<br>001 = Interru                                                                       | upt is priority 1                                        |                                                    |                    |                 |                 |       |

|                  |                                                                                          | upt is priority 1<br>upt source is dis                   | abled                                              |                    |                 |                 |       |

| bit 3            | 000 = Interru                                                                            |                                                          |                                                    |                    |                 |                 |       |

|                  | 000 = Interru<br>Unimpleme                                                               | upt source is dis                                        | כ'                                                 | pt Priority bits   |                 |                 |       |

|                  | 000 = Interru<br>Unimpleme<br>SI2C1IP<2:0                                                | upt source is dis<br>nted: Read as '                     | o'<br>Events Interru                               |                    |                 |                 |       |

|                  | 000 = Interru<br>Unimpleme<br>SI2C1IP<2:0                                                | upt source is dis<br>nted: Read as '<br>I>: I2C1 Slave E | o'<br>Events Interru                               |                    |                 |                 |       |

|                  | 000 = Interru<br>Unimpleme<br>SI2C1IP<2:0                                                | upt source is dis<br>nted: Read as '<br>I>: I2C1 Slave E | o'<br>Events Interru                               |                    |                 |                 |       |

| bit 3<br>bit 2-0 | 000 = Intern<br>Unimplemen<br>SI2C1IP<2:0<br>111 = Intern<br>•<br>•<br>•<br>001 = Intern | upt source is dis<br>nted: Read as '<br>I>: I2C1 Slave E | <sub>D</sub> '<br>Events Interru<br>nighest priori |                    |                 |                 |       |

| U-0            | R/W-1              | R/W-0                                  | R/W-0           | U-0              | R/W-1            | R/W-0           | R/W-0 |

|----------------|--------------------|----------------------------------------|-----------------|------------------|------------------|-----------------|-------|

| —              |                    | T6IP<2:0>                              |                 | —                |                  | DMA4IP<2:0>     |       |

| bit 15         |                    |                                        |                 |                  |                  |                 | bit   |

|                |                    |                                        |                 |                  |                  |                 |       |

| U-0            | U-0                | U-0                                    | U-0             | U-0              | R/W-1            | R/W-0           | R/W-0 |

| _              | —                  | —                                      |                 |                  |                  | OC8IP<2:0>      |       |

| bit 7          |                    |                                        |                 |                  |                  |                 | bit   |

| Legend:        |                    |                                        |                 |                  |                  |                 |       |

| R = Readab     | ole bit            | W = Writable                           | bit             | U = Unimple      | mented bit, rea  | d as '0'        |       |

| -n = Value a   | at POR             | '1' = Bit is set                       |                 | '0' = Bit is cle | eared            | x = Bit is unkn | iown  |

| bit 1 <i>5</i> | l inima la vere    | nted. Deed at f                        | <u>`</u>        |                  |                  |                 |       |

| bit 15         | -                  | nted: Read as '                        |                 |                  |                  |                 |       |

| bit 14-12      |                    | Timer6 Interrupt                       | •               |                  |                  |                 |       |

|                | 111 = Intern       | upt is priority 7 (I                   | nignest priorit | y interrupt)     |                  |                 |       |

|                | •                  |                                        |                 |                  |                  |                 |       |

|                | •                  |                                        |                 |                  |                  |                 |       |

|                |                    | upt is priority 1                      | ablad           |                  |                  |                 |       |

| L:1 11         |                    | upt source is dis                      |                 |                  |                  |                 |       |

| bit 11         | -                  | nted: Read as '                        |                 |                  |                  |                 |       |

| bit 10-8       |                    | D>: DMA Channe                         |                 | •                | e interrupt Prio | ity bits        |       |

|                | •                  | upt is priority 7 (I                   | lignest phone   | y interrupt)     |                  |                 |       |

|                | •                  |                                        |                 |                  |                  |                 |       |

|                | •                  |                                        |                 |                  |                  |                 |       |

|                |                    | upt is priority 1                      | ablad           |                  |                  |                 |       |

|                |                    | upt source is dis                      |                 |                  |                  |                 |       |

| bit 7-3        | -                  | nted: Read as '                        |                 |                  |                  |                 |       |

| bit 2-0        |                    | : Output Compa                         |                 | -                | ity bits         |                 |       |

|                | 111 = Interru<br>• | upt is priority 7 (I                   | nignest priorit | y interrupt)     |                  |                 |       |

|                | •                  |                                        |                 |                  |                  |                 |       |

|                |                    |                                        |                 |                  |                  |                 |       |

|                | •                  |                                        |                 |                  |                  |                 |       |

|                |                    | upt is priority 1<br>upt source is dis |                 |                  |                  |                 |       |

#### REGISTER 7-26: IPC11: INTERRUPT PRIORITY CONTROL REGISTER 11

## 10.0 POWER-SAVING FEATURES

- **Note 1:** This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196) of "dsPIC33F/PIC24H Familv the Reference Manual", which is available site the from Microchip web (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJXXXGPX06A/X08A/X10A devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. PIC24HJXXXGPX06A/X08A/X10A devices can manage power consumption in four different ways:

- Clock frequency

- Instruction-based Sleep and Idle modes

- Software-controlled Doze mode

- Selective peripheral control in software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

## 10.1 Clock Frequency and Clock Switching

PIC24HJXXXGPX06A/X08A/X10A devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0** "Oscillator Configuration".

### 10.2 Instruction-Based Power-Saving Modes

PIC24HJXXXGPX06A/X08A/X10A devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembly syntax of the PWRSAV instruction is shown in Example 10-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

#### 10.2.1 SLEEP MODE

Sleep mode has these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled

- The LPRC clock continues to run in Sleep mode if the WDT is enabled

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode

- Some device features or peripherals may continue to operate in Sleep mode. This includes items such as the input change notification on the I/O ports, or peripherals that use an external clock input. Any peripheral that requires the system clock source for its operation is disabled in Sleep mode.

The device will wake-up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- Any form of device Reset

- A WDT time-out

On wake-up from Sleep, the processor restarts with the same clock source that was active when Sleep mode was entered.

#### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE ; Put the device into SLEEP mode

PWRSAV #IDLE\_MODE ; Put the device into IDLE mode

## 17.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 19. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195) of the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Inter-Integrated Circuit ( $I^2C$ ) module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard, with a 16-bit interface.

The PIC24HJXXXGPX06A/X08A/X10A devices have up to two I<sup>2</sup>C interface modules, denoted as I2C1 and I2C2. Each I<sup>2</sup>C module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each  $I^2C$  module 'x' (x = 1 or 2) offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Port allows bidirectional transfers between master and slaves

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and will arbitrate accordingly

## 17.1 Operating Modes

The hardware fully implements all the master and slave functions of the  $l^2C$  Standard and Fast mode specifications, as well as 7 and 10-bit addressing.

The I<sup>2</sup>C module can operate either as a slave or a master on an I<sup>2</sup>C bus.

The following types of I<sup>2</sup>C operation are supported:

- I<sup>2</sup>C slave operation with 7-bit addressing

- I<sup>2</sup>C slave operation with 10-bit addressing

- I<sup>2</sup>C master operation with 7-bit or 10-bit addressing

For details about the communication sequence in each of these modes, please refer to the *"dsPIC33F/PIC24H Family Reference Manual"*.

| bit 15 bit 16 bit 15 bit 16 bit 17 bit 10 bi | U-0          | U-0          | U-0              | U-0             | U-0               | R/W-0            | R/W-0            | R/W-0   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|------------------|-----------------|-------------------|------------------|------------------|---------|

| U-0       U-0       U-0       U-0       R/W-0       R/W-0       R/W-0         -       -       -       -       CH123NA<1:0>       CH123SA         bit 7       bit       bit       bit       bit       bit         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       bit         bit 15-11       Unimplemented: Read as '0'       CH123NB       character       x = Bit is unknown         bit 10-9       CH123NB       CH123NB       character       x = Bit is unknown         11 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11       10 = CH1 negative input is AN8, CH2 negative input is AN7, CH3 negative input is AN8         0x = CH1, CH2, CH3 negative input is VREF-       bit 8       CH123SB: Channel 1, 2, 3 Positive Input Select for Sample B bit         When AD12B = 1, CHXSB is: U-0, Unimplemented, Read as '0'       1 = CH1 positive input is AN3, CH2 positive input is AN4, CH3 positive input is AN5         0 = CH1 positive input is AN3, CH2 positive input is AN1, CH3 negative input is AN2       Dit 7-3         Unimplemented: Read as '0'       11 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11         10 = CH1 positive input is AN9, CH2 negative input is AN1, CH3 negative input is AN11       10 = CH1 negative input is AN6, CH2 negative input is AN1, CH3 negative input is AN11 <td>_</td> <td>_</td> <td>_</td> <td>_</td> <td>_</td> <td>CH123N</td> <td>NB&lt;1:0&gt;</td> <td>CH123SB</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _            | _            | _                | _               | _                 | CH123N           | NB<1:0>          | CH123SB |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 15       |              |                  |                 |                   |                  |                  | bit 8   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |              |                  |                 |                   |                  |                  |         |

| bit 7       bit         Legend: <ul> <li>R = Readable bit</li> <li>W = Writable bit</li> <li>U = Unimplemented bit, read as '0'</li> <li>-n = Value at POR</li> <li>'1' = Bit is set</li> <li>'0' = Bit is cleared</li> <li>x = Bit is unknown</li> </ul> <li>bit 15-11</li> <li>Unimplemented: Read as '0'</li> <li>CH123NB</li> <li>CH123NB</li> <li>CH123NB</li> <li>CH123NB</li> <li>CH123NB</li> <li>CH123NB</li> <li>CH123NB</li> <li>bit 10-9</li> <li>CH123NB</li> <li>CH123NB</li> <li>CH123NB</li> <li>CH1 Regative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11</li> <li>10 = CH1 negative input is AN6, CH2 negative input is AN7, CH3 negative input is AN8</li> <li>0x = CH1, CH2, CH3 negative input SVREF-</li> <li>bit 8</li> <li>CH123SB: Channel 1, 2, 3 Positive Input Select for Sample B bit</li> <li>When AD12B = 1, CHxSB is: U-0, Unimplemented, Read as '0'</li> <li>1 = CH1 positive input is AN3, CH2 positive input is AN4, CH3 positive input is AN5</li> <li>0 = CH1 positive input is AN3, CH2 positive input is AN1, CH3 positive input is AN2</li> <li>bit 2-1</li> <li>CH123NA</li> <li>CH123NA</li> <li>CH123NA</li> <li>CH2 ch3 negative input is AN1, CH3 positive input is AN11</li> <li>10 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11</li> <li>10 = CH1 negative input is AN6, CH2 negative input is AN10, CH3 negative input is AN11</li> <li>10 = CH1 negative input is AN6, CH2 negative input is AN10, CH3 negative input is AN11</li> <li>10 = CH1 negative input is AN6, CH2 negative input is AN10, CH3 negative input is AN11</li> <li>10 = CH1 negative input is AN6, CH2 negative input is AN10, CH3 negative input is AN11</li> <li>10 = CH1 negat</li>                                                                                                                                                                                                                                                                                                                                                    | U-0          | U-0          | U-0              | U-0             | U-0               | R/W-0            | R/W-0            | R/W-0   |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         .n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-11       Unimplemented: Read as '0'       CH123NB<1:0>: Channel 1, 2, 3 Negative Input Select for Sample B bits         When AD12B = 1, CHXNB is: U-0, Unimplemented, Read as '0'       11 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11         10 = CH1 negative input is AN6, CH2 negative input is AN7, CH3 negative input is AN8       0x = CH1, CH2, CH3 negative input is VREF-         bit 8       CH123SB: Channel 1, 2, 3 Positive Input Select for Sample B bit       When AD12B = 1, CHXSB is: U-0, Unimplemented, Read as '0'         1 = CH1 positive input is AN3, CH2 positive input is AN4, CH3 positive input is AN5       0 = CH1 positive input is AN3, CH2 positive input is AN1, CH3 positive input is AN2         bit 7-3       Unimplemented: Read as '0'       11 = CH1 negative input is AN0, CH2 positive input is AN1, CH3 positive input is AN2         bit 7-3       Unimplemented: Read as '0'       11 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11         10 = CH1 negative input is AN6, CH2 negative input is AN10, CH3 negative input is AN11       10 = CH1 negative input is AN6, CH2 negative input is AN10, CH3 negative input is AN11         10 = CH1 negative input is AN6, CH2 negative input is AN10, CH3 negative input is AN8       0x = CH1, CH2, CH3 negative input is VREF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              | —            | —                | _               | —                 | CH123N           | NA<1:0>          | CH123SA |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'        n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-11       Unimplemented: Read as '0'           bit 10-9       CH123NB       CH123NB       x = 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 7        |              |                  |                 |                   |                  |                  | bit 0   |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'        n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-11       Unimplemented: Read as '0'           bit 10-9       CH123NB       CH123NB       x = 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |              |                  |                 |                   |                  |                  |         |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-11       Unimplemented: Read as '0'          bit 10-9       CH123NB<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Legend:      |              |                  |                 |                   |                  |                  |         |

| <ul> <li>bit 15-11 Unimplemented: Read as '0'</li> <li>CH123NB&lt;1:0&gt;: Channel 1, 2, 3 Negative Input Select for Sample B bits</li> <li>When AD12B = 1, CHxNB is: U-0, Unimplemented, Read as '0'</li> <li>11 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11</li> <li>10 = CH1 negative input is AN6, CH2 negative input is AN7, CH3 negative input is AN8</li> <li>0x = CH1, CH2, CH3 negative input is VREF-</li> <li>bit 8 CH123SB: Channel 1, 2, 3 Positive Input Select for Sample B bit</li> <li>When AD12B = 1, CHxSB is: U-0, Unimplemented, Read as '0'</li> <li>1 = CH1 positive input is AN3, CH2 positive input is AN4, CH3 positive input is AN5</li> <li>0 = CH1 positive input is AN0, CH2 positive input is AN1, CH3 positive input is AN2</li> <li>bit 7-3 Unimplemented: Read as '0'</li> <li>bit 2-1 CH123NA</li> <li>then AD12B = 1, CHxAA is: U-0, Unimplemented, Read as '0'</li> <li>11 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11</li> <li>10 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11</li> <li>10 = CH1 negative input is AN9, CH2 negative input is AN7, CH3 negative input is AN11</li> <li>10 = CH1 negative input is AN9, CH2 negative input is AN7, CH3 negative input is AN8</li> <li>0x = CH1, CH2, CH3 negative input is VREF-</li> <li>bit 0 CH123SA: Channel 1, 2, 3 Positive Input Select for Sample A bit</li> <li>When AD12B = 1, CHxSA is: U-0, Unimplemented, Read as '0'</li> <li>11 = CH1 negative input is AN8, CH2 negative input is AN7, CH3 negative input is AN8</li> <li>0x = CH1, CH2, CH3 negative input is VREF-</li> <li>bit 0 CH123SA: Channel 1, 2, 3 Positive Input Select for Sample A bit</li> <li>When AD12B = 1, CHxSA is: U-0, Unimplemented, Read as '0'</li> <li>1 = CH1 positive input is AN3, CH2 positive input is AN4, CH3 positive input is AN5</li> </ul>                                                                                                                                                                     | R = Readab   | le bit       | W = Writable     | bit             | U = Unimple       | mented bit, read | d as '0'         |         |

| <ul> <li>bit 10-9</li> <li>CH123NB&lt;1:0&gt;: Channel 1, 2, 3 Negative Input Select for Sample B bits</li> <li>When AD12B = 1, CHxNB is: U-0, Unimplemented, Read as '0'</li> <li>11 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11</li> <li>10 = CH1 negative input is AN6, CH2 negative input is AN7, CH3 negative input is AN8</li> <li>0x = CH1, CH2, CH3 negative input SVREF-</li> <li>bit 8</li> <li>CH123SB: Channel 1, 2, 3 Positive Input Select for Sample B bit</li> <li>When AD12B = 1, CHxSB is: U-0, Unimplemented, Read as '0'</li> <li>1 = CH1 positive input is AN3, CH2 positive input is AN4, CH3 positive input is AN5</li> <li>0 = CH1 positive input is AN0, CH2 positive input is AN1, CH3 positive input is AN2</li> <li>bit 7-3</li> <li>Unimplemented: Read as '0'</li> <li>DH123NA&lt;1:0&gt;: Channel 1, 2, 3 Negative Input Select for Sample A bits</li> <li>When AD12B = 1, CHxNA is: U-0, Unimplemented, Read as '0'</li> <li>11 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11</li> <li>10 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11</li> <li>10 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11</li> <li>10 = CH1 negative input is AN9, CH2 negative input is AN7, CH3 negative input is AN8</li> <li>0x = CH1, CH2, CH3 negative input is VREF-</li> <li>bit 0</li> <li>CH123SA: Channel 1, 2, 3 Positive Input Select for Sample A bit</li> <li>When AD12B = 1, CHxSA is: U-0, Unimplemented, Read as '0'</li> <li>11 = CH1 negative input is AN6, CH2 negative input is AN7, CH3 negative input is AN8</li> <li>0x = CH1, CH2, CH3 negative input is VREF-</li> <li>bit 0</li> <li>CH123SA: Channel 1, 2, 3 Positive Input Select for Sample A bit</li> <li>When AD12B = 1, CHxSA is: U-0, Unimplemented, Read as '0'</li> <li>1 = CH1 positive input is AN3, CH2 positive input is AN4, CH3 positive input is AN5</li> </ul>                                                                                                  | -n = Value a | t POR        | '1' = Bit is set |                 | '0' = Bit is cle  | eared            | x = Bit is unl   | known   |

| <ul> <li>bit 10-9</li> <li>CH123NB&lt;1:0&gt;: Channel 1, 2, 3 Negative Input Select for Sample B bits</li> <li>When AD12B = 1, CHxNB is: U-0, Unimplemented, Read as '0'</li> <li>11 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11</li> <li>10 = CH1 negative input is AN6, CH2 negative input is AN7, CH3 negative input is AN8</li> <li>0x = CH1, CH2, CH3 negative input SVREF-</li> <li>bit 8</li> <li>CH123SB: Channel 1, 2, 3 Positive Input Select for Sample B bit</li> <li>When AD12B = 1, CHxSB is: U-0, Unimplemented, Read as '0'</li> <li>1 = CH1 positive input is AN3, CH2 positive input is AN4, CH3 positive input is AN5</li> <li>0 = CH1 positive input is AN0, CH2 positive input is AN1, CH3 positive input is AN2</li> <li>bit 7-3</li> <li>Unimplemented: Read as '0'</li> <li>DH123NA&lt;1:0&gt;: Channel 1, 2, 3 Negative Input Select for Sample A bits</li> <li>When AD12B = 1, CHxNA is: U-0, Unimplemented, Read as '0'</li> <li>11 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11</li> <li>10 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11</li> <li>10 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11</li> <li>10 = CH1 negative input is AN9, CH2 negative input is AN7, CH3 negative input is AN8</li> <li>0x = CH1, CH2, CH3 negative input is VREF-</li> <li>bit 0</li> <li>CH123SA: Channel 1, 2, 3 Positive Input Select for Sample A bit</li> <li>When AD12B = 1, CHxSA is: U-0, Unimplemented, Read as '0'</li> <li>11 = CH1 negative input is AN6, CH2 negative input is AN7, CH3 negative input is AN8</li> <li>0x = CH1, CH2, CH3 negative input is VREF-</li> <li>bit 0</li> <li>CH123SA: Channel 1, 2, 3 Positive Input Select for Sample A bit</li> <li>When AD12B = 1, CHxSA is: U-0, Unimplemented, Read as '0'</li> <li>1 = CH1 positive input is AN3, CH2 positive input is AN4, CH3 positive input is AN5</li> </ul>                                                                                                  |              |              |                  |                 |                   |                  |                  |         |

| <ul> <li>When AD12B = 1, CHxNB is: U-0, Unimplemented, Read as '0'<br/>11 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11<br/>10 = CH1 negative input is AN6, CH2 negative input is AN7, CH3 negative input is AN8<br/>0x = CH1, CH2, CH3 negative input is VREF-</li> <li>bit 8 CH123SB: Channel 1, 2, 3 Positive Input Select for Sample B bit<br/>When AD12B = 1, CHxSB is: U-0, Unimplemented, Read as '0'<br/>1 = CH1 positive input is AN3, CH2 positive input is AN4, CH3 positive input is AN5<br/>0 = CH1 positive input is AN0, CH2 positive input is AN1, CH3 positive input is AN2</li> <li>bit 7-3 Unimplemented: Read as '0'<br/>11 = CH1 negative input is AN0, CH2 positive Input Select for Sample A bits<br/>When AD12B = 1, CHxNA is: U-0, Unimplemented, Read as '0'<br/>11 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11<br/>10 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11<br/>10 = CH1 negative input is AN6, CH2 negative input is AN7, CH3 negative input is AN8<br/>0x = CH1, CH2, CH3 negative input is VREF-</li> <li>bit 0 CH123SA: Channel 1, 2, 3 Positive Input Select for Sample A bit<br/>When AD12B = 1, CHxSA is: U-0, Unimplemented, Read as '0'<br/>1 = CH1 negative input is AN6, CH2 negative input is AN7, CH3 negative input is AN8<br/>0x = CH1, CH2, CH3 negative input is VREF-</li> <li>bit 0 CH123SA: Channel 1, 2, 3 Positive Input Select for Sample A bit<br/>When AD12B = 1, CHxSA is: U-0, Unimplemented, Read as '0'<br/>1 = CH1 positive input is AN3, CH2 positive input is AN4, CH3 positive input is AN5</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                 |              | •            |                  |                 |                   |                  |                  |         |