Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | PIC                                                                              |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 18x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp206at-i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

# 2.1 Basic Connection Requirements

Getting started with the PIC24HJXXXGPX06A/X08A/X10A family of 16-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

- (see Section 2.2 "Decoupling Capacitors") VCAP

- (see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for ADC module is implemented

| Note: | The       | AVdd    | and   | AVss    | pins | mu  | st be |

|-------|-----------|---------|-------|---------|------|-----|-------|

|       | connected |         | indep | endent  | of   | the | ADC   |

|       | volta     | ge refe | rence | source. |      |     |       |

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

For remapping operations, the 8-bit Program Space Visibility register (PSVPAG) is used to define a 16K word page in the program space. When the Most Significant bit of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike table operations, this limits remapping operations strictly to the user memory area. Table 4-35 and Figure 4-6 show how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> refers to a program space word, whereas D<15:0> refers to a data space word.

## TABLE 4-35: PROGRAM SPACE ADDRESS CONSTRUCTION

|                                       | Access        | Program Space Address |               |               |                                                         |     |  |  |

|---------------------------------------|---------------|-----------------------|---------------|---------------|---------------------------------------------------------|-----|--|--|

| Access Type                           | Space         | <23>                  | <22:16>       | <15>          | <14:1><br>xx xxxx xxx0<br>Data EA<15:0><br>xx xxxx xxxx | <0> |  |  |

| Instruction Access                    | User          | 0 PC<22:1>            |               |               |                                                         | 0   |  |  |

| (Code Execution)                      |               |                       | 0xxx xxxx x   | xxx xx        | xx xxxx xxx0                                            |     |  |  |

| TBLRD/TBLWT<br>(Byte/Word Read/Write) | User          | TB                    | LPAG<7:0>     | Data EA<15:0> |                                                         |     |  |  |

|                                       |               | 0                     | xxx xxxx      | xx xxxx xxxx  |                                                         |     |  |  |

|                                       | Configuration | TBLPAG<7:0>           |               | Data EA<15:0> |                                                         |     |  |  |

|                                       |               | 1xxx xxxx xxxx x      |               |               | xxx xxxx xxxx                                           |     |  |  |

| Program Space Visibility              | User          | 0                     | 0 PSVPAG<7:0> |               | Data EA<14:0> <sup>(1)</sup>                            |     |  |  |

| (Block Remap/Read)                    |               | 0                     | xxxx xxxx     |               | xxx xxxx xxxx xxxx                                      |     |  |  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

| U-0          | R/W-1                                                                                                         | R/W-0                                              | R/W-0           | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----------------|------------------|-----------------|-----------------|-------|--|--|--|--|--|

| _            |                                                                                                               | U2TXIP<2:0>                                        |                 |                  |                 | U2RXIP<2:0>     |       |  |  |  |  |  |

| bit 15       |                                                                                                               |                                                    |                 |                  |                 |                 | bit   |  |  |  |  |  |

| U-0          | R/W-1                                                                                                         | R/W-0                                              | R/W-0           | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |

|              |                                                                                                               | INT2IP<2:0>                                        |                 | _                |                 | T5IP<2:0>       |       |  |  |  |  |  |

| bit 7        |                                                                                                               |                                                    |                 |                  | 1               |                 | bit   |  |  |  |  |  |

| Legend:      |                                                                                                               |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |

| R = Readab   | le bit                                                                                                        | W = Writable                                       | bit             | U = Unimplei     | mented bit, rea | id as '0'       |       |  |  |  |  |  |

| -n = Value a | t POR                                                                                                         | '1' = Bit is set                                   |                 | '0' = Bit is cle | eared           | x = Bit is unkr | iown  |  |  |  |  |  |

| bit 15       | Unimpleme                                                                                                     | ented: Read as '                                   | כי              |                  |                 |                 |       |  |  |  |  |  |

| bit 14-12    |                                                                                                               | <b>0&gt;:</b> UART2 Trans<br>rupt is priority 7 (I |                 |                  |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                             |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |

|              | •<br>001 = Interrupt is priority 1                                                                            |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |

|              |                                                                                                               | upt source is dis                                  | abled           |                  |                 |                 |       |  |  |  |  |  |

| bit 11       | Unimpleme                                                                                                     | ented: Read as '                                   | o'              |                  |                 |                 |       |  |  |  |  |  |

| bit 10-8     | U2RXIP<2:0>: UART2 Receiver Interrupt Priority bits                                                           |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt)                                                    |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                             |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                             |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |

|              | 001 = Interrupt is priority 1                                                                                 |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |

|              |                                                                                                               | upt source is dis                                  |                 |                  |                 |                 |       |  |  |  |  |  |

| bit 7        | -                                                                                                             | ented: Read as '                                   |                 |                  |                 |                 |       |  |  |  |  |  |

| bit 6-4      | INT2IP<2:0>: External Interrupt 2 Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |

|              | 111 = Interr                                                                                                  | rupt is priority 7 (I                              | nighest priori  | ty interrupt)    |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                             |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                             |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |

|              |                                                                                                               | upt is priority 1                                  | ablad           |                  |                 |                 |       |  |  |  |  |  |

| bit 3        |                                                                                                               | upt source is dis                                  |                 |                  |                 |                 |       |  |  |  |  |  |

| bit 2-0      | Unimplemented: Read as '0'<br>T5IP<2:0>: Timer5 Interrupt Priority bits                                       |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |

| DIL 2-0      |                                                                                                               | upt is priority 7 (I                               | -               | tv interrupt)    |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                             | арт ю р. ю. т.) · (.                               | ingineer priori | ()               |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                             |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                             |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |

|              | ()()   = Interr                                                                                               | upt is priority 1                                  |                 |                  |                 |                 |       |  |  |  |  |  |

NOTES:

| <b>REGISTER 8-1: DMAxCON: DMA CHANNEL x CONTROL REGISTER</b> |

|--------------------------------------------------------------|

|--------------------------------------------------------------|

| R/W-0                         | R/W-0                                                    | R/W-0                                                       | R/W-0          | R/W-0                                    | U-0            | U-0              | U-0     |  |  |  |  |  |

|-------------------------------|----------------------------------------------------------|-------------------------------------------------------------|----------------|------------------------------------------|----------------|------------------|---------|--|--|--|--|--|

| CHEN                          | SIZE                                                     | DIR                                                         | HALF           | NULLW                                    | —              |                  | —       |  |  |  |  |  |

| pit 15                        |                                                          |                                                             |                |                                          |                |                  | bit     |  |  |  |  |  |

| U-0                           | U-0                                                      | R/W-0                                                       | R/W-0          | U-0                                      | U-0            | R/W-0            | R/W-0   |  |  |  |  |  |

| _                             |                                                          | -                                                           | E<1:0>         |                                          | _              | MODE             |         |  |  |  |  |  |

| bit 7                         |                                                          |                                                             |                |                                          |                |                  | bit     |  |  |  |  |  |

| lagandu                       |                                                          |                                                             |                |                                          |                |                  |         |  |  |  |  |  |

| <b>Legend:</b><br>R = Readabl | e hit                                                    | W = Writable                                                | bit            | U = Unimplem                             | onted hit rea  | d as '0'         |         |  |  |  |  |  |

| -n = Value at                 |                                                          | '1' = Bit is set                                            |                | '0' = Bit is clea                        |                | x = Bit is unkr  |         |  |  |  |  |  |

|                               | FUR                                                      |                                                             |                |                                          | areu           |                  | IOWII   |  |  |  |  |  |

| bit 15                        | CHEN: Chan                                               | nel Enable bit                                              |                |                                          |                |                  |         |  |  |  |  |  |

|                               | 1 = Channel                                              | enabled                                                     |                |                                          |                |                  |         |  |  |  |  |  |

|                               | 0 = Channel                                              | disabled                                                    |                |                                          |                |                  |         |  |  |  |  |  |

| bit 14                        | SIZE: Data T                                             | ransfer Size bi                                             | t              |                                          |                |                  |         |  |  |  |  |  |

|                               | 1 = Byte<br>0 = Word                                     |                                                             |                |                                          |                |                  |         |  |  |  |  |  |

| bit 13                        | DIR: Transfe                                             | DIR: Transfer Direction bit (source/destination bus select) |                |                                          |                |                  |         |  |  |  |  |  |

|                               |                                                          |                                                             |                | to peripheral ado<br>o DMA RAM ado       |                |                  |         |  |  |  |  |  |

| bit 12                        | HALF: Early Block Transfer Complete Interrupt Select bit |                                                             |                |                                          |                |                  |         |  |  |  |  |  |

|                               |                                                          |                                                             |                | ipt when half of t<br>ipt when all of th |                |                  |         |  |  |  |  |  |

| bit 11                        |                                                          | I Data Peripher                                             | -              | -                                        |                |                  |         |  |  |  |  |  |

|                               |                                                          | write to periph                                             |                | n to DMA RAM v                           | write (DIR bit | must also be cle | ar)     |  |  |  |  |  |

| bit 10-6                      | Unimplemer                                               | ted: Read as                                                | 0'             |                                          |                |                  |         |  |  |  |  |  |

| bit 5-4                       | AMODE<1:0                                                | >: DMA Chann                                                | el Operating I | Mode Select bits                         | 5              |                  |         |  |  |  |  |  |

|                               | 11 = Reserve                                             |                                                             |                |                                          |                |                  |         |  |  |  |  |  |

|                               |                                                          | ral Indirect Add                                            |                |                                          |                |                  |         |  |  |  |  |  |

|                               |                                                          | r Indirect witho<br>r Indirect with F                       |                |                                          |                |                  |         |  |  |  |  |  |

| bit 3-2                       | Unimplemer                                               | nted: Read as '                                             | 0'             |                                          |                |                  |         |  |  |  |  |  |

| oit 1-0                       | MODE<1:0>                                                | : DMA Channe                                                | I Operating M  | ode Select bits                          |                |                  |         |  |  |  |  |  |

|                               | 11 = One-Sh<br>10 = Continu                              |                                                             |                | ed (one block tra                        | nsfer from/to  | each DMA RAM     | buffer) |  |  |  |  |  |

|                               |                                                          | ot, Ping-Pong                                               |                |                                          |                |                  |         |  |  |  |  |  |

## 10.2.2 IDLE MODE

Idle mode has these features:

- · The CPU stops executing instructions.

- The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device will wake from Idle mode on any of these events:

- Any interrupt that is individually enabled.

- · Any device Reset.

- A WDT time-out.

On wake-up from Idle, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction, or the first instruction in the ISR.

#### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

# 10.3 Doze Mode

Generally, changing clock speed and invoking one of the power-saving modes are the preferred strategies for reducing power consumption. There may be circumstances, however, where this is not practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed may introduce communication errors, while using a power-saving mode may stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate. Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

It is also possible to use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU idles, waiting for something to invoke an interrupt routine. Enabling the automatic return to full-speed CPU operation on interrupts is enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the CAN module has been configured for 500 kbps based on this device operating speed. If the device is now placed in Doze mode with a clock frequency ratio of 1:4, the CAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

# 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled via the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers will have no effect and read values will be invalid.

A peripheral module is only enabled if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

Note: If a PMD bit is set, the corresponding module is disabled after a delay of 1 instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of 1 instruction cycle (assuming the module control registers are already configured to enable module operation).

# 11.6 I/O Helpful Tips

- 1. In some cases, certain pins as defined in TABLE 24-9: "DC Characteristics: I/O Pin Input Specifications" under "Injection Current", have internal protection diodes to VDD and Vss. The term "Injection Current" is also referred to as "Clamp Current". On designated pins, with sufficient external current limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings with nominal VDD with respect to the VSS and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device that is clamped internally by the VDD and VSS power rails, may affect the ADC accuracy by four to six counts.

- I/O pins that are shared with any analog input pin, 2. (i.e., ANx), are always analog pins by default after any reset. Consequently, any pin(s) configured as an analog input pin, automatically disables the digital input pin buffer. As such, any attempt to read a digital input pin will always return a '0' regardless of the digital logic level on the pin if the analog pin is configured. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the analog pin configuration registers in the ADC module, (i.e., ADxPCFGL, AD1PCFGH), by setting the appropriate bit that corresponds to that I/O port pin to a '1'. On devices with more than one ADC, both analog pin configurations for both ADC modules must be configured as a digital I/O pin for that pin to function as a digital I/O pin.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in the data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each CN pin has a configurable internal weak pull-up resistor. The pull-ups act as a current source connected to the pin, and eliminates the need for external resistors in certain applications. The internal pull-up is to ~(VDD-0.8) not VDD. This is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH and at or below the VOL levels. However, for LEDs unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of the data sheet. For example:

VOH = 2.4v @ IOH = -8 mA and VDD = 3.3V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 24.0 "Electrical Characteristics" for additional information.

# 11.7 I/O Resources

Many useful resources related to I/O are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en546061

# 11.7.1 KEY RESOURCES

- Section 10. "I/O Ports" (DS70193)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| R/W-0         | U-0                                                                      | R/W-0           | U-0            | U-0                    | U-0             | U-0                | U-0 |  |  |  |  |

|---------------|--------------------------------------------------------------------------|-----------------|----------------|------------------------|-----------------|--------------------|-----|--|--|--|--|

| TON           |                                                                          | TSIDL           |                | —                      |                 | —                  |     |  |  |  |  |

| bit 15        |                                                                          |                 |                |                        |                 |                    | bit |  |  |  |  |

| U-0           | R/W-0                                                                    | R/W-0           | R/W-0          | R/W-0                  | U-0             | R/W-0              | U-0 |  |  |  |  |

| 0-0           | TGATE                                                                    |                 | S<1:0>         | T32                    | 0-0             | TCS <sup>(1)</sup> | 0-0 |  |  |  |  |

| <br>bit 7     | IGAIE                                                                    | TCKP            | 5<1.0>         | 132                    | _               | 1030               | bit |  |  |  |  |

|               |                                                                          |                 |                |                        |                 |                    |     |  |  |  |  |

| Legend:       |                                                                          |                 |                |                        |                 |                    |     |  |  |  |  |

| R = Readable  | e bit                                                                    | W = Writable    | bit            | U = Unimplem           | nented bit, rea | d as '0'           |     |  |  |  |  |

| -n = Value at | POR                                                                      | '1' = Bit is se | t              | '0' = Bit is clea      | ared            | x = Bit is unkno   | own |  |  |  |  |

| bit 15        | TON: Timerx                                                              | On bit          |                |                        |                 |                    |     |  |  |  |  |

|               | When T32 = 1                                                             | L:              |                |                        |                 |                    |     |  |  |  |  |

|               | 1 = Starts 32-<br>0 = Stops 32-                                          |                 |                |                        |                 |                    |     |  |  |  |  |

|               | <u>When T32 = 0</u>                                                      |                 |                |                        |                 |                    |     |  |  |  |  |

|               | 1 = Starts 16-<br>0 = Stops 16-                                          |                 |                |                        |                 |                    |     |  |  |  |  |

| bit 14        | Unimplemen                                                               |                 | ٠́ ()'         |                        |                 |                    |     |  |  |  |  |

| bit 13        | TSIDL: Stop i                                                            |                 |                |                        |                 |                    |     |  |  |  |  |

|               | •                                                                        | ue module ope   | eration when d | evice enters Idl<br>de | e mode          |                    |     |  |  |  |  |

| bit 12-7      | Unimplemen                                                               | -               |                |                        |                 |                    |     |  |  |  |  |

| bit 6         | TGATE: Timerx Gated Time Accumulation Enable bit                         |                 |                |                        |                 |                    |     |  |  |  |  |

|               | When TCS = 1:                                                            |                 |                |                        |                 |                    |     |  |  |  |  |

|               | This bit is ignored.                                                     |                 |                |                        |                 |                    |     |  |  |  |  |

|               | $\frac{\text{When TCS} = 0}{1 = \text{Gated time accumulation enabled}}$ |                 |                |                        |                 |                    |     |  |  |  |  |

|               | 0 = Gated tim                                                            |                 |                |                        |                 |                    |     |  |  |  |  |

| bit 5-4       | TCKPS<1:0>: Timerx Input Clock Prescale Select bits                      |                 |                |                        |                 |                    |     |  |  |  |  |

|               | 11 = 1:256                                                               |                 |                |                        |                 |                    |     |  |  |  |  |

|               | 10 = 1:64                                                                |                 |                |                        |                 |                    |     |  |  |  |  |

|               | 01 = 1:8<br>00 = 1:1                                                     |                 |                |                        |                 |                    |     |  |  |  |  |

| bit 3         | T32: 32-bit Ti                                                           | mer Mode Sel    | ect bit        |                        |                 |                    |     |  |  |  |  |

|               | 1 = Timerx an<br>0 = Timerx an                                           |                 |                |                        |                 |                    |     |  |  |  |  |

| bit 2         | Unimplemen                                                               | -               |                |                        |                 |                    |     |  |  |  |  |

| bit 1         | TCS: Timerx                                                              |                 |                |                        |                 |                    |     |  |  |  |  |

|               | 1 = External c<br>0 = Internal cl                                        | clock from pin  |                | rising edge)           |                 |                    |     |  |  |  |  |

|               |                                                                          | · · /           |                |                        |                 |                    |     |  |  |  |  |

## REGISTER 13-1: TxCON (T2CON, T4CON, T6CON OR T8CON) CONTROL REGISTER

Note 1: The TxCK pin is not available on all timers. Refer to the "Pin Diagrams" section for the available pins.

### 16.1 SPI Helpful Tips

- 1. In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPIxCON2<13>) = 1, use a pull-down resistor on SSx.

- b) If FRMPOL = 0, use a pull-up resistor on  $\overline{SSx}$ .

| Note: | This   | insures    | that  | the        | first | fr | ame |

|-------|--------|------------|-------|------------|-------|----|-----|

|       | transr | mission a  | after | initializa | ation | is | not |

|       | shifte | d or corru | pted. |            |       |    |     |

- 2. In non-framed 3-wire mode, (i.e., not using SSx from a master):

- a) If CKP (SPIxCON1<6>) = 1, always place a pull-up resistor on SSx.

- b) If CKP = 0, always place a pull-down resistor on  $\overline{SSx}$ .

- **Note:** This will insure that during power-up and initialization the master/slave will not lose sync due to an errant SCK transition that would cause the slave to accumulate data shift errors for both transmit and receive appearing as corrupted data.

- FRMEN (SPIxCON2<15>) = 1 and SSEN (SPIxCON1<7>) = 1 are exclusive and invalid. In Frame mode, SCKx is continuous and the Frame sync pulse is active on the SSx pin, which indicates the start of a data frame.

| Note: | Not all third-party devices support Frame |

|-------|-------------------------------------------|

|       | mode timing. Refer to the SPI electrical  |

|       | characteristics for details.              |

- In Master mode only, set the SMP bit (SPIxCON1<9>) to a '1' for the fastest SPI data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPIxCON1<5>) is set.

- 5. To avoid invalid slave read data to the master, the user's master software must guarantee enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPIxBUF transmit register in advance of the next master transaction cycle. SPIxBUF is transferred to the SPI shift register and is empty once the data transmission begins.

## 16.2 SPI Resources

Many useful resources related to SPI are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en546061                                        |

#### 16.2.1 KEY RESOURCES

- Section 18. "Serial Peripheral Interface (SPI)" (DS70206)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

### REGISTER 19-8: CIEC: ECAN™ MODULE TRANSMIT/RECEIVE ERROR COUNT REGISTER

| R-0                                | R-0 | R-0            | R-0               | R-0                                | R-0                | R-0 | R-0   |

|------------------------------------|-----|----------------|-------------------|------------------------------------|--------------------|-----|-------|

|                                    |     |                | TERR              | CNT<7:0>                           |                    |     |       |

| bit 15                             |     |                |                   |                                    |                    |     | bit 8 |

|                                    |     |                |                   |                                    |                    |     |       |

| R-0                                | R-0 | R-0            | R-0               | R-0                                | R-0                | R-0 | R-0   |

|                                    |     |                | RERR              | CNT<7:0>                           |                    |     |       |

| bit 7                              |     |                |                   |                                    |                    |     | bit C |

| Laward                             |     |                |                   |                                    |                    |     |       |

| Legend:                            |     |                |                   |                                    |                    |     |       |

| R = Readable b                     | bit | W = Writable b | bit               | U = Unimplemented bit, read as '0' |                    |     |       |

| -n = Value at POR '1' = Bit is set |     |                | '0' = Bit is clea | ared                               | x = Bit is unknown |     |       |

bit 15-8 TERRCNT<7:0>: Transmit Error Count bits

bit 7-0 RERRCNT<7:0>: Receive Error Count bits

## REGISTER 19-13: CIBUFPNT2: ECAN™ MODULE FILTER 4-7 BUFFER POINTER REGISTER

| R/W-0         | R/W-0         | R/W-0                                                   | R/W-0         | R/W-0               | R/W-0          | R/W-0              | R/W-0 |

|---------------|---------------|---------------------------------------------------------|---------------|---------------------|----------------|--------------------|-------|

|               | F7BP          | <3:0>                                                   |               |                     | F6BP           | ><3:0>             |       |

| bit 15        |               |                                                         |               |                     |                |                    | bit 8 |

| R/W-0         | R/W-0         | R/W-0                                                   | R/W-0         | R/W-0               | R/W-0          | R/W-0              | R/W-0 |

|               | F5BP          | <3:0>                                                   |               |                     | F4BP           | <sup>2</sup> <3:0> |       |

| bit 7         |               |                                                         |               |                     |                |                    | bit ( |

| Legend:       |               |                                                         |               |                     |                |                    |       |

| R = Readable  | e bit         | W = Writable                                            | bit           | U = Unimplemer      | nted bit, read | l as '0'           |       |

| -n = Value at | POR           | '1' = Bit is set                                        |               | '0' = Bit is cleare |                | x = Bit is unkr    | nown  |

| bit 15-12     | 1111 = Filter | RX Buffer Writt<br>hits received ir<br>hits received ir | n RX FIFO bu  | uffer               |                |                    |       |

|               | •             |                                                         |               |                     |                |                    |       |

|               |               | hits received ir                                        |               |                     |                |                    |       |

| bit 11-8      | 1111 = Filter | RX Buffer Writt<br>hits received ir<br>hits received ir | n RX FIFO bu  | uffer               |                |                    |       |

|               | •             |                                                         |               |                     |                |                    |       |

|               |               | hits received ir hits received ir                       |               |                     |                |                    |       |

| bit 7-4       | 1111 = Filter | RX Buffer Writt<br>hits received ir<br>hits received ir | n RX FIFO bu  | uffer               |                |                    |       |

|               | •             |                                                         |               |                     |                |                    |       |

|               |               | hits received ir hits received ir                       |               |                     |                |                    |       |

| bit 3-0       | 1111 = Filter | RX Buffer Writt<br>hits received ir<br>hits received ir | n RX FIFO bu  | uffer               |                |                    |       |

|               | •             |                                                         |               |                     |                |                    |       |

|               | 0001 = Filter | hits received ir                                        | n RX Buffer 1 |                     |                |                    |       |

| REGISTER     | 20-5. ADXC    | 13123: ADC)                                                                                                                                                                    |                | ANNEL $1, 2,$                                                            | SELECT RE          | GIGIER         |         |  |  |  |  |  |

|--------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------|--------------------|----------------|---------|--|--|--|--|--|

| U-0          | U-0           | U-0                                                                                                                                                                            | U-0            | U-0                                                                      | R/W-0              | R/W-0          | R/W-0   |  |  |  |  |  |

| _            | —             | _                                                                                                                                                                              | _              | —                                                                        | CH123N             | NB<1:0>        | CH123SB |  |  |  |  |  |

| bit 15       |               |                                                                                                                                                                                |                |                                                                          |                    |                | bit 8   |  |  |  |  |  |

|              |               |                                                                                                                                                                                |                |                                                                          |                    |                |         |  |  |  |  |  |

| U-0          | U-0           | U-0                                                                                                                                                                            | U-0            | U-0                                                                      | R/W-0              | R/W-0          | R/W-0   |  |  |  |  |  |

| _            |               |                                                                                                                                                                                | _              |                                                                          | CH123N             | VA<1:0>        | CH123SA |  |  |  |  |  |

| bit 7        |               |                                                                                                                                                                                |                |                                                                          |                    |                | bit 0   |  |  |  |  |  |

|              |               |                                                                                                                                                                                |                |                                                                          |                    |                |         |  |  |  |  |  |

| Legend:      |               |                                                                                                                                                                                |                |                                                                          |                    |                |         |  |  |  |  |  |

| R = Readab   | ole bit       | W = Writable                                                                                                                                                                   | bit            | U = Unimple                                                              | mented bit, read   | d as '0'       |         |  |  |  |  |  |

| -n = Value a | It POR        | '1' = Bit is set                                                                                                                                                               |                | '0' = Bit is cle                                                         | eared              | x = Bit is unl | known   |  |  |  |  |  |

|              |               |                                                                                                                                                                                |                |                                                                          |                    |                |         |  |  |  |  |  |

| bit 15-11    | -             | ted: Read as '                                                                                                                                                                 |                |                                                                          |                    |                |         |  |  |  |  |  |

| bit 10-9     |               |                                                                                                                                                                                | •              | •                                                                        | or Sample B bit    | S              |         |  |  |  |  |  |

|              |               |                                                                                                                                                                                |                | lemented, Read as 'o'<br>itive input is AN10, CH3 negative input is AN11 |                    |                |         |  |  |  |  |  |

|              |               | , ,                                                                                                                                                                            | · U            |                                                                          | N7, CH3 negati     |                |         |  |  |  |  |  |

|              | -             | I2, CH3 negati                                                                                                                                                                 | -              |                                                                          | intr, en le negati |                |         |  |  |  |  |  |

| bit 8        |               | nannel 1, 2, 3 F                                                                                                                                                               | •              |                                                                          | ple B bit          |                |         |  |  |  |  |  |

|              | When AD12E    | s = 1, CHxSB i                                                                                                                                                                 | s: U-0, Unim   | plemented, Re                                                            | ad as '0'          |                |         |  |  |  |  |  |

|              |               | 1 = CH1 positive input is AN3, CH2 positive input is AN4, CH3 positive input is AN5                                                                                            |                |                                                                          |                    |                |         |  |  |  |  |  |

|              | •             | •                                                                                                                                                                              | •              | e input is AN1                                                           | , CH3 positive i   | nput is AN2    |         |  |  |  |  |  |

| bit 7-3      | •             | ted: Read as '                                                                                                                                                                 |                |                                                                          |                    |                |         |  |  |  |  |  |

| bit 2-1      |               |                                                                                                                                                                                | •              | •                                                                        | or Sample A bit    | S              |         |  |  |  |  |  |

|              |               | B = 1, CHxNA i                                                                                                                                                                 |                |                                                                          |                    |                |         |  |  |  |  |  |

|              |               | 11 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11<br>10 = CH1 negative input is AN6, CH2 negative input is AN7, CH3 negative input is AN8 |                |                                                                          |                    |                |         |  |  |  |  |  |

|              |               | I2, CH3 negati                                                                                                                                                                 |                |                                                                          | in, cho negati     |                | 10      |  |  |  |  |  |

| bit 0        |               | nannel 1, 2, 3 F                                                                                                                                                               | •              |                                                                          | ple A bit          |                |         |  |  |  |  |  |

| -            |               | B = 1, CHxSA i                                                                                                                                                                 | •              |                                                                          | •                  |                |         |  |  |  |  |  |

|              | 1 = CH1 posit | ive input is AN                                                                                                                                                                | 3, CH2 positiv | e input is AN4                                                           | , CH3 positive i   |                |         |  |  |  |  |  |

|              | 0 = CH1 posit | ive input is AN                                                                                                                                                                | 0, CH2 positiv | e input is AN1                                                           | , CH3 positive i   | nput is AN2    |         |  |  |  |  |  |

|              |               |                                                                                                                                                                                |                |                                                                          |                    |                |         |  |  |  |  |  |

# REGISTER 20-5: ADxCHS123: ADCx INPUT CHANNEL 1, 2, 3 SELECT REGISTER

# 21.2 On-Chip Voltage Regulator

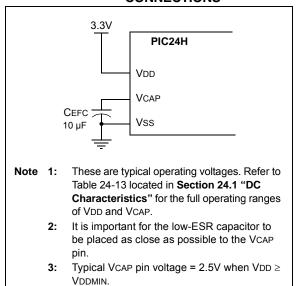

All of the PIC24HJXXXGPX06A/X08A/X10A devices power their core digital logic at a nominal 2.5V. This may create an issue for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the PIC24HJXXXGPX06A/X08A/X10A family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. The regulator requires that a low-ESR (less than 5 ohms) capacitor (such as tantalum or ceramic) be connected to the VCAP pin (Figure 21-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 24-13 of **Section 24.1** "**DC Characteristics**".

| Note: | It is important for the low-ESR capacitor to |

|-------|----------------------------------------------|

|       | be placed as close as possible to the VCAP   |

|       | pin.                                         |

On a POR, it takes approximately 20  $\mu$ s for the on-chip voltage regulator to generate an output voltage. During this time, designated as TSTARTUP, code execution is disabled. TSTARTUP is applied every time the device resumes operation after any power-down.

#### FIGURE 21-1: ON-CHIP VOLTAGE REGULATOR CONNECTIONS<sup>(1,2,3)</sup>

# 21.3 Brown-out Reset (BOR)

The BOR (Brown-out Reset) module is based on an internal voltage reference circuit that monitors the regulated voltage VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (i.e., missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR will generate a Reset pulse which will reset the device. The BOR will select the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>). Furthermore, if an oscillator mode is selected, the BOR will activate the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock will be held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT time-out (TPWRT) will be applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, a nominal delay of TFSCM = 100 is applied. The total delay in this case is TFSCM.

The BOR Status bit (RCON<1>) will be set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and will reset the device should VDD fall below the BOR threshold voltage.

# 24.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of PIC24HJXXXGPX06A/X08A/X10A electrical characteristics. Additional information is provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC24HJXXXGPX06A/X08A/X10A family are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

## **Absolute Maximum Ratings**

### (See Note 1)

| Ambient temperature under bias                                                    | 40°C to +125°C |

|-----------------------------------------------------------------------------------|----------------|

| Storage temperature                                                               | 65°C to +160°C |

| Voltage on VDD with respect to Vss                                                |                |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(4)</sup>     |                |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(4)}$      | 0.3V to +5.6V  |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(4)</sup> | 0.3V to 3.6V   |

| Maximum current out of Vss pin                                                    |                |

| Maximum current into Vod pin <sup>(2)</sup>                                       | 250 mA         |

| Maximum current sourced/sunk by any 2x I/O pin <sup>(3)</sup>                     | 8 mA           |

| Maximum current sourced/sunk by any 4x I/O pin <sup>(3)</sup>                     | 15 mA          |

| Maximum current sourced/sunk by any 8x I/O pin <sup>(3)</sup>                     | 25 mA          |

| Maximum current sunk by all ports                                                 | 200 mA         |

| Maximum current sourced by all ports <sup>(2)</sup>                               | 200 mA         |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods can affect device reliability.

- **2:** Maximum allowable current is a function of device maximum power dissipation (see Table 24-2).

- Exceptions are CLKOUT, which is able to sink/source 25 mA, and the VREF+, VREF-, SCLx, SDAx, PGECx and PGEDx pins, which are able to sink/source 12 mA.

- 4: See the "Pin Diagrams" section for 5V tolerant pins.

## 24.1 DC Characteristics

| Characteristic | VDD Range                | Temp Range      | Max MIPS                   |  |  |  |  |  |  |

|----------------|--------------------------|-----------------|----------------------------|--|--|--|--|--|--|

| Characteristic | (in Volts)               | (in °C)         | PIC24HJXXXGPX06A/X08A/X10A |  |  |  |  |  |  |

|                | VBOR-3.6V <sup>(1)</sup> | -40°C to +85°C  | 40                         |  |  |  |  |  |  |

| _              | VBOR-3.6V <sup>(1)</sup> | -40°C to +125°C | 40                         |  |  |  |  |  |  |

#### TABLE 24-1: OPERATING MIPS VS. VOLTAGE

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules such as the ADC will have degraded performance. Device functionality is tested but not characterized. Refer to parameter BO10 in Table 24-11 for the minimum and maximum BOR values.

### TABLE 24-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                      | Symbol | Min           | Тур | Max  | Unit |

|---------------------------------------------------------------------------------------------|--------|---------------|-----|------|------|

| Industrial Temperature Devices                                                              |        |               |     |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40           | —   | +125 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40           | —   | +85  | °C   |

| Extended Temperature Devices                                                                |        |               |     |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40           | —   | +150 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40           | —   | +125 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$ | PD     | PINT + PI/O   |     |      | W    |

| I/O Pin Power Dissipation:<br>I/O = $\Sigma$ ({VDD - VOH} x IOH) + $\Sigma$ (VOL x IOL)     |        |               |     |      |      |

| Maximum Allowed Power Dissipation                                                           | PDMAX  | (Tj – Ta)/θja |     |      | W    |

### TABLE 24-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                        | Symbol | Тур | Max | Unit | Notes |

|-------------------------------------------------------|--------|-----|-----|------|-------|

| Package Thermal Resistance, 100-pin TQFP (14x14x1 mm) | θja    | 40  |     | °C/W | 1     |

| Package Thermal Resistance, 100-pin TQFP (12x12x1 mm) | θja    | 40  | _   | °C/W | 1     |

| Package Thermal Resistance, 64-pin TQFP (10x10x1 mm)  | θја    | 40  | _   | °C/W | 1     |

| Package Thermal Resistance, 64-pin QFN (9x9x0.9 mm)   | θja    | 28  | _   | °C/W | 1     |

Note 1: Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

|              |        |                                                                                |                    | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |            |        |                                                                                          |  |  |

|--------------|--------|--------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|------------------------------------------------------------------------------------------|--|--|

| Param<br>No. | Symbol | Characteristic                                                                 | Min                | Тур <sup>(1)</sup>                                                                                                                                                                                                                                                                      | Max        | Units  | Conditions                                                                               |  |  |

|              | VIL    | Input Low Voltage                                                              |                    |                                                                                                                                                                                                                                                                                         |            |        |                                                                                          |  |  |

| DI10         |        | I/O pins                                                                       | Vss                | —                                                                                                                                                                                                                                                                                       | 0.2 VDD    | V      |                                                                                          |  |  |

| DI15         |        | MCLR                                                                           | Vss                | —                                                                                                                                                                                                                                                                                       | 0.2 VDD    | V      |                                                                                          |  |  |