Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 32x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp210a-e-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

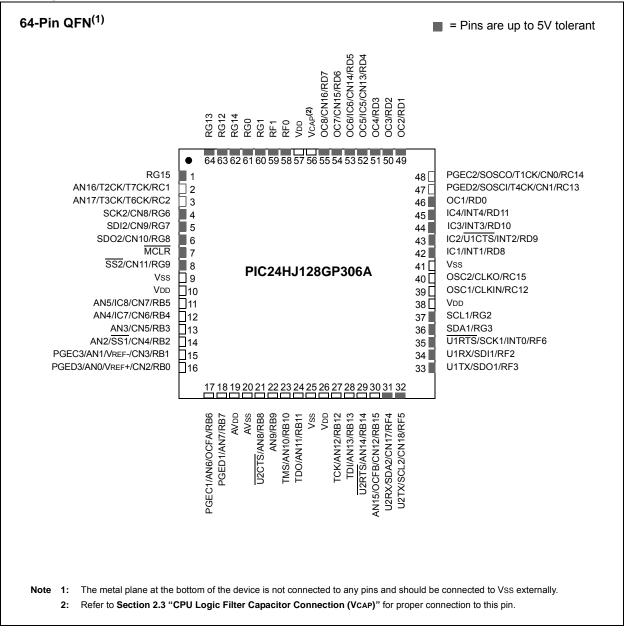

## Pin Diagrams (Continued)

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D15 D0                                |               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W0/WREG                               | PUSH.S Shadow |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W1                                    |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W2                                    | oo Shadow     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W3 Le                                 | egend         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W4                                    | 0             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W5                                    |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W6                                    |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W7                                    |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W8 Working Register                   | S             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W9                                    |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W10                                   |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W11                                   |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W12                                   |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W13                                   |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W14/Frame Pointer                     |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W15/Stack Pointer                     |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SPLIM Stack Pointer Limit Reg         | ister         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                       |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 Program Counter                     |               |

| 7 0<br>PSVPAG Pro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | gram Space Visibility Page Address    |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RCOUNT REPEAT Loop Counter            |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15 0<br>CORCON Core Configuration Reg | gister        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DC IPL2 IPL1 IPL0 RA N OV Z C STATUS  | Register      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SRL SRL                               |               |

| —   —   —   —   —   —   — ▲ SRH — SRH |                                       |               |

| —   —   —   —   —   — ▲ SRH — S |                                       |               |

## TABLE 4-17: DMA REGISTER MAP

| File Name | -17:<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6 | Bit 5 | Bit 4  | Bit 3     | Bit 2 | Bit 1 | Bit 0 | All    |

|-----------|--------------|--------|--------|--------|--------|--------|--------|-------|-------|----------|-------|-------|--------|-----------|-------|-------|-------|--------|

|           |              |        |        |        |        |        |        |       |       |          |       |       |        |           |       |       |       | Resets |

| DMA0CON   | 0380         | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      |       |       |          | _     | AMOD  |        | —         | —     | MODE  | <1:0> | 0000   |

| DMA0REQ   | 0382         | FORCE  | —      | —      |        | —      | —      |       |       | —        |       |       |        | RQSEL<6:0 | >     |       |       | 0000   |

| DMA0STA   | 0384         |        |        |        |        |        |        |       |       | TA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA0STB   | 0386         |        |        |        |        |        |        |       |       | TB<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA0PAD   | 0388         |        |        |        |        |        |        | r     | P     | AD<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA0CNT   | 038A         | _      |        | —      | —      | —      | —      |       |       |          |       |       | <9:0>  | -         |       | r     |       | 0000   |

| DMA1CON   | 038C         | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      |       |       | _        |       | AMOD  |        | _         | —     | MODE  | <1:0> | 0000   |

| DMA1REQ   | 038E         | FORCE  | —      | —      |        | —      | —      |       |       | —        |       |       | I      | RQSEL<6:0 | >     |       |       | 0000   |

| DMA1STA   | 0390         |        |        |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA1STB   | 0392         |        |        |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA1PAD   | 0394         |        |        |        |        |        |        | 1     | P     | AD<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA1CNT   | 0396         | —      | —      | —      | —      | —      | —      |       |       |          |       | CNT   | <9:0>  | T         |       |       |       | 0000   |

| DMA2CON   | 0398         | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      |       |       | _        | _     | AMOD  | E<1:0> | —         | —     | MODE  | <1:0> | 0000   |

| DMA2REQ   | 039A         | FORCE  | —      | —      |        | —      | —      |       |       | —        |       |       |        | RQSEL<6:0 | >     |       |       | 0000   |

| DMA2STA   | 039C         |        |        |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA2STB   | 039E         |        |        |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA2PAD   | 03A0         |        |        |        |        |        |        |       | Р     | AD<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA2CNT   | 03A2         | —      | —      | —      | —      | —      | —      |       |       |          |       | CNT   | <9:0>  |           |       |       |       | 0000   |

| DMA3CON   | 03A4         | CHEN   | SIZE   | DIR    | HALF   | NULLW  | —      | —     | —     | —        | —     | AMOD  | E<1:0> | —         | —     | MODE  | <1:0> | 0000   |

| DMA3REQ   | 03A6         | FORCE  | —      | —      | —      | —      | —      | —     | —     | —        |       |       | I      | RQSEL<6:0 | >     |       |       | 0000   |

| DMA3STA   | 03A8         |        |        |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA3STB   | 03AA         |        |        |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA3PAD   | 03AC         |        |        |        |        |        |        |       | Р     | AD<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA3CNT   | 03AE         | -      | -      | _      | _      | _      | _      |       |       |          |       | CNT   | <9:0>  |           |       |       |       | 0000   |

| DMA4CON   | 03B0         | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _     | —        | _     | AMOD  | E<1:0> | _         | —     | MODE  | <1:0> | 0000   |

| DMA4REQ   | 03B2         | FORCE  | _      | _      | _      | _      | _      | _     | _     | _        |       |       | I      | RQSEL<6:0 | >     |       |       | 0000   |

| DMA4STA   | 03B4         |        |        |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA4STB   | 03B6         |        |        |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA4PAD   | 03B8         |        |        |        |        |        |        |       | Р     | AD<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA4CNT   | 03BA         | _      | _      | _      | —      | _      | _      |       |       |          |       | CNT   | <9:0>  |           |       |       |       | 0000   |

| DMA5CON   | 03BC         | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | —     | —     | —        | —     | AMOD  | E<1:0> | —         | _     | MODE  | <1:0> | 0000   |

| DMA5REQ   | 03BE         | FORCE  | _      | _      | —      | _      | _      | _     | _     | _        |       | •     | I      | RQSEL<6:0 | >     |       |       | 0000   |

| DMA5STA   | 03C0         |        |        |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA5STB   | 03C2         |        |        |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000   |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

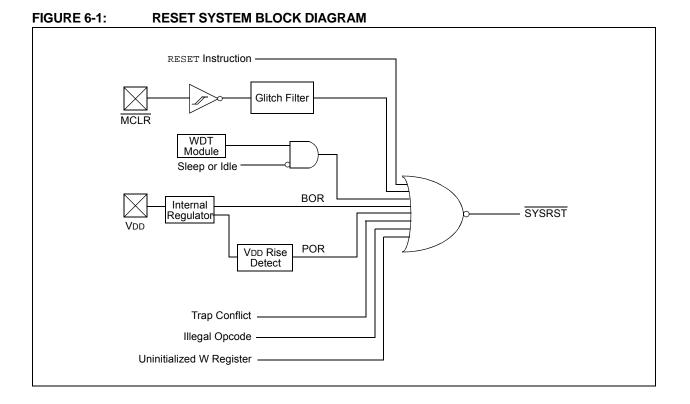

## 6.0 RESET

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Reset" (DS70192) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- · BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDT: Watchdog Timer Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Opcode and Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on POR and unchanged by all other Resets.

**Note:** Refer to the specific peripheral or CPU section of this data sheet for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1). A POR will clear all bits, except for the POR bit (RCON<0>), that are set. The user can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

## REGISTER 7-1: SR: CPU STATUS REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | -   | —   | —   | —   | DC    |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------------------|----------------------|----------------------|-----|-------|-------|-------|-------|

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA  | Ν     | OV    | Z     | C     |

| bit 7                |                      |                      |     |       |       |       | bit 0 |

| Legend:            |                      |                                    |

|--------------------|----------------------|------------------------------------|

| C = Clear only bit | R = Readable bit     | U = Unimplemented bit, read as '0' |

| S = Set only bit   | W = Writable bit     | -n = Value at POR                  |

| '1' = Bit is set   | '0' = Bit is cleared | x = Bit is unknown                 |

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2)</sup>

111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled

- 110 = CPU Interrupt Priority Level is 6 (14)

- 101 = CPU Interrupt Priority Level is 5 (13) 100 = CPU Interrupt Priority Level is 4 (12)

- 011 = CPU Interrupt Priority Level is 3 (11)

- 010 = CPU Interrupt Priority Level is 2 (10)

- 001 = CPU Interrupt Priority Level is 1 (9)

- 000 = CPU Interrupt Priority Level is 0 (8)

- **Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

## REGISTER 7-2: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| U-0               | U-0           | U-0                                                        | U-0              | U-0                 | U-0              | U-0              | U-0   |

|-------------------|---------------|------------------------------------------------------------|------------------|---------------------|------------------|------------------|-------|

| _                 |               |                                                            | _                |                     |                  |                  |       |

| bit 15            |               |                                                            |                  |                     |                  |                  | bit 8 |

|                   |               |                                                            |                  |                     |                  |                  |       |

| U-0               | U-0           | U-0                                                        | U-0              | R/C-0               | R/W-0            | U-0              | U-0   |

|                   | —             | —                                                          | —                | IPL3 <sup>(2)</sup> | PSV              | —                | _     |

| bit 7             |               |                                                            |                  |                     |                  |                  | bit 0 |

|                   |               |                                                            |                  |                     |                  |                  |       |

| Legend:           |               | C = Clear only                                             | / bit            |                     |                  |                  |       |

| R = Readable I    | oit           | W = Writable                                               | bit              | -n = Value at       | POR              | '1' = Bit is set |       |

| 0' = Bit is clear | ed            | ʻx = Bit is unki                                           | nown             | U = Unimpler        | nented bit, read | as '0'           |       |

| bit 3             | 1 = CPU inter | terrupt Priority<br>rupt priority lev<br>rupt priority lev | el is greater th |                     |                  |                  |       |

**Note 1:** For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

## REGISTER 7-11: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1

| R/W-0           | R/W-0           | R/W-0                            | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|-----------------|-----------------|----------------------------------|------------------|------------------|------------------|-----------------|---------|

| U2TXIE          | U2RXIE          | INT2IE                           | T5IE             | T4IE             | OC4IE            | OC3IE           | DMA2IE  |

| bit 15          |                 | •                                |                  |                  |                  |                 | bit 8   |

| D/// 0          | DAMO            | DAVO                             | DAVA             | DAVO             |                  | DAMO            | DAMO    |

| R/W-0           | R/W-0           | R/W-0                            | R/W-0            | R/W-0            | U-0              | R/W-0           | R/W-0   |

| IC8IE           | IC7IE           | AD2IE                            | INT1IE           | CNIE             |                  | MI2C1IE         | SI2C1IE |

| bit 7           |                 |                                  |                  |                  |                  |                 | bit 0   |

| Legend:         |                 |                                  |                  |                  |                  |                 |         |

| R = Readable    | bit             | W = Writable                     | bit              | U = Unimpler     | mented bit, read | d as '0'        |         |

| -n = Value at F | POR             | '1' = Bit is set                 |                  | '0' = Bit is cle |                  | x = Bit is unkr | iown    |

|                 |                 |                                  |                  |                  |                  |                 |         |

| bit 15          | U2TXIE: UAR     | T2 Transmitte                    | r Interrupt Ena  | able bit         |                  |                 |         |

|                 | •               | equest enable                    |                  |                  |                  |                 |         |

|                 | •               | equest not ena                   |                  |                  |                  |                 |         |

| bit 14          |                 | RT2 Receiver I                   | •                | le bit           |                  |                 |         |

|                 |                 | equest enable<br>equest not ena  |                  |                  |                  |                 |         |

| bit 13          | •               | nal Interrupt 2                  |                  |                  |                  |                 |         |

|                 |                 | equest enable                    |                  |                  |                  |                 |         |

|                 | 0 = Interrupt r | equest not ena                   | abled            |                  |                  |                 |         |

| bit 12          |                 | Interrupt Enab                   |                  |                  |                  |                 |         |

|                 | •               | equest enable                    |                  |                  |                  |                 |         |

| bit 11          | •               | equest not ena<br>Interrupt Enab |                  |                  |                  |                 |         |

|                 |                 | request enable                   |                  |                  |                  |                 |         |

|                 |                 | equest not ena                   |                  |                  |                  |                 |         |

| bit 10          | OC4IE: Outpu    | ut Compare Ch                    | annel 4 Interr   | upt Enable bit   |                  |                 |         |

|                 |                 | equest enable<br>equest not ena  |                  |                  |                  |                 |         |

| bit 9           | •               | ut Compare Ch                    |                  | upt Enable bit   |                  |                 |         |

|                 |                 | equest enable                    |                  |                  |                  |                 |         |

|                 | •               | equest not ena                   |                  |                  |                  |                 |         |

| bit 8           | DMA2IE: DM      | A Channel 2 D                    | ata Transfer (   | Complete Interr  | upt Enable bit   |                 |         |

|                 |                 | equest enable<br>equest not ena  |                  |                  |                  |                 |         |

| bit 7           | •               | Capture Chann                    |                  | Enable bit       |                  |                 |         |

|                 |                 | equest enable                    | -                |                  |                  |                 |         |

|                 |                 | equest not ena                   |                  |                  |                  |                 |         |

| bit 6           | IC7IE: Input C  | Capture Chann                    | el 7 Interrupt I | Enable bit       |                  |                 |         |

|                 |                 | equest enable<br>equest not ena  |                  |                  |                  |                 |         |

| bit 5           |                 |                                  |                  | rupt Enable bit  |                  |                 |         |

|                 |                 | equest enable                    | •                | •                |                  |                 |         |

|                 | 0 = Interrupt r | equest not ena                   | abled            |                  |                  |                 |         |

| bit 4           |                 | nal Interrupt 1                  |                  |                  |                  |                 |         |

|                 | 1 = Interrupt r | oquest enable                    | Ч                |                  |                  |                 |         |

| U-0           | R/W-1             | R/W-0                                   | R/W-0          | U-0               | R/W-1            | R/W-0           | R/W-0 |

|---------------|-------------------|-----------------------------------------|----------------|-------------------|------------------|-----------------|-------|

| —             |                   | T2IP<2:0>                               |                | _                 |                  | OC2IP<2:0>      |       |