Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 32x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp210a-i-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IADLE 4  | -/. I       | NFUIC                        | JAFIU  |        | JOIER  |        |          |       |            |                 |             |                 |       |       |       |          |       |               |

|----------|-------------|------------------------------|--------|--------|--------|--------|----------|-------|------------|-----------------|-------------|-----------------|-------|-------|-------|----------|-------|---------------|

| SFR Name | SFR<br>Addr | Bit 15                       | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10   | Bit 9 | Bit 8      | Bit 7           | Bit 6       | Bit 5           | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

| IC1BUF   | 0140        |                              |        |        |        |        |          |       | Input 1 Ca | pture Regis     | er          |                 |       |       |       |          |       | xxxx          |

| IC1CON   | 0142        | —                            | _      | ICSIDL | —      | —      | _        |       |            | ICTMR           | ICI<        | 1:0>            | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC2BUF   | 0144        | 144 Input 2 Capture Register |        |        |        |        |          |       |            |                 |             | xxxx            |       |       |       |          |       |               |

| IC2CON   | 0146        | —                            | _      | ICSIDL | —      | —      | _        |       |            | ICTMR           | ICI<        | 1:0>            | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC3BUF   | 0148        |                              |        |        |        |        |          |       | Input 3 Ca | apture Regis    | er          |                 |       |       |       |          |       | xxxx          |

| IC3CON   | 014A        | —                            | _      | ICSIDL | —      | —      | _        |       |            | ICTMR           | ICI<        | ICI<1:0> ICOV I |       |       |       | ICM<2:0> |       | 0000          |

| IC4BUF   | 014C        |                              |        |        |        |        |          |       | Input 4 Ca | apture Regis    | er          |                 |       |       |       |          |       | xxxx          |

| IC4CON   | 014E        | —                            | _      | ICSIDL | —      | —      | _        |       |            | ICTMR           | ICI<        | 1:0>            | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC5BUF   | 0150        |                              |        |        |        |        |          |       | Input 5 Ca | apture Regis    | er          |                 |       |       |       |          |       | xxxx          |

| IC5CON   | 0152        | —                            | _      | ICSIDL | —      | —      | _        |       |            | ICTMR           | ICI<        | 1:0>            | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC6BUF   | 0154        |                              |        |        |        |        |          |       | Input 6 Ca | apture Regis    | er          |                 |       |       |       |          |       | xxxx          |

| IC6CON   | 0156        | —                            | _      | ICSIDL | —      | —      | _        |       |            | ICTMR           | ICI<        | 1:0>            | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC7BUF   | 0158        |                              |        |        |        |        |          |       | Input 7 Ca | apture Regis    | er          |                 |       |       |       |          |       | xxxx          |

| IC7CON   | 015A        | —                            | _      | ICSIDL | —      | —      | _        | _     | _          | ICTMR           | ICI<        | 1:0>            | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC8BUF   | 015C        |                              |        |        |        |        |          |       | Input 8 Ca | apture Regis    | er          |                 |       |       |       |          |       | xxxx          |

| IC8CON   | 015E        | —                            | —      | ICSIDL | —      | —      | —        | —     | _          | ICTMR           | ICI<        | 1:0>            | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| Logondu  |             |                              | Decet  |        |        |        | Desetual |       |            | المعادم والأحما | Din∐iah day |                 |       |       |       |          |       |               |

C24HJXXXGPX06A/X08A/X10A

#### TABLE 4-7: INPUT CAPTURE REGISTER MAP

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

### 7.3 Interrupt Control and Status Registers

PIC24HJXXXGPX06A/X08A/X10A devices implement a total of 30 registers for the interrupt controller:

- INTCON1

- INTCON2

- IFS0 through IFS4

- IEC0 through IEC4

- IPC0 through IPC17

- INTTREG

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table.

The IFS registers maintain all of the interrupt request flags. Each source of interrupt has a Status bit, which is set by the respective peripherals or external signal and is cleared via software.

The IEC registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals. The IPC registers are used to set the interrupt priority level for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

The INTTREG register contains the associated interrupt vector number and the new CPU interrupt priority level, which are latched into vector number (VEC-NUM<6:0>) and Interrupt level (ILR<3:0>) bit fields in the INTTREG register. The new interrupt priority level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence that they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having vector number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0>, and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

Although they are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. The CPU STATUS register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU interrupt priority level. The user can change the current CPU priority level by writing to the IPL bits.

The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-1 through Register 7-32.

### REGISTER 7-12: IEC2: INTERRUPT ENABLE CONTROL REGISTER 2

| R/W-0         | R/W-0           | U-0                             | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|---------------|-----------------|---------------------------------|----------------|------------------|------------------|-----------------|---------|

| T6IE          | DMA4IE          | —                               | OC8IE          | OC7IE            | OC6IE            | OC5IE           | IC6IE   |

| bit 15        |                 |                                 |                |                  | •                |                 | bit 8   |

| R/W-0         | R/W-0           | R/W-0                           | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| IC5IE         | IC4IE           | IC3IE                           | DMA3IE         | C1IE             | C1RXIE           | SPI2IE          | SPI2EIE |

| bit 7         |                 |                                 |                | 0                |                  |                 | bit (   |

| Legend:       |                 |                                 |                |                  |                  |                 |         |

| R = Readable  | e bit           | W = Writable                    | bit            | U = Unimpler     | mented bit, read | l as '0'        |         |

| -n = Value at | POR             | '1' = Bit is set                |                | '0' = Bit is cle | eared            | x = Bit is unki | nown    |

| bit 15        | T6IE: Timer6    | Interrupt Enabl                 | e bit          |                  |                  |                 |         |

|               |                 | request enable                  |                |                  |                  |                 |         |

|               | 0 = Interrupt r | equest not ena                  | bled           |                  |                  |                 |         |

| bit 14        |                 | A Channel 4 D                   |                | Complete Interi  | rupt Enable bit  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 13        | •               | ted: Read as '                  |                |                  |                  |                 |         |

| bit 12        | •               | ut Compare Ch                   |                | unt Enable bit   |                  |                 |         |

| 511 12        | •               | request enable                  |                |                  |                  |                 |         |

|               |                 | equest not ena                  |                |                  |                  |                 |         |

| bit 11        | OC7IE: Outpu    | ut Compare Ch                   | annel 7 Interr | upt Enable bit   |                  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 10        | OC6IE: Outpu    | ut Compare Ch                   | annel 6 Interr | upt Enable bit   |                  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 9         | OC5IE: Outpu    | ut Compare Ch                   | annel 5 Interr | upt Enable bit   |                  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 8         |                 | Capture Channe                  |                | Enable bit       |                  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 7         |                 | Capture Channe                  |                | Enable bit       |                  |                 |         |

|               | -               | equest enable                   |                |                  |                  |                 |         |

|               | •               | request not ena                 |                |                  |                  |                 |         |

| bit 6         | -               | Capture Channe                  |                | Enable bit       |                  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 5         | •               | Capture Channe                  |                | -nable bit       |                  |                 |         |

|               | -               | equest enable                   | -              |                  |                  |                 |         |

|               | 0 = Interrupt r | equest not ena                  | bled           |                  |                  |                 |         |

| bit 4         | DMA3IE: DM      | A Channel 3 D                   | ata Transfer C | Complete Interi  | rupt Enable bit  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 3         | -               | Event Interrup                  |                |                  |                  |                 |         |

| bit J         |                 | equest enable                   |                |                  |                  |                 |         |

|               |                 | equest not ena                  |                |                  |                  |                 |         |

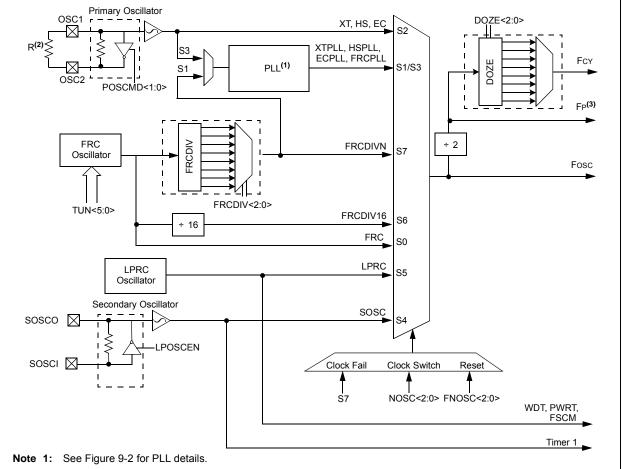

## 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 7. "Oscillator" (DS70186) of the "dsPIC33F/dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJXXXGPX06A/X08A/X10A oscillator system provides:

- Various external and internal oscillator options as clock sources

- An on-chip PLL to scale the internal operating frequency to the required system clock frequency

- The internal FRC oscillator can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- Clock switching between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- An Oscillator Control register (OSCCON)

- Nonvolatile Configuration bits for main oscillator selection.

A simplified diagram of the oscillator system is shown in Figure 9-1.

### FIGURE 9-1: PIC24HJXXXGPX06A/X08A/X10A OSCILLATOR SYSTEM DIAGRAM

- 2: If the Oscillator is used with XT or HS modes, an extended parallel resistor with the value of 1 MΩ must be connected.

- **3:** The term, FP refers to the clock source for all the peripherals, while FCY refers to the clock source for the CPU. Throughout this document FP and FCY are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used in any ratio other than 1:1, which is the default.

## REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER<sup>(1)</sup>

| U-0           | U-0                    | U-0              | U-0             | U-0              | U-0              | U-0                | R/W-0     |  |

|---------------|------------------------|------------------|-----------------|------------------|------------------|--------------------|-----------|--|

| —             | —                      | —                | —               | —                | —                | _                  | PLLDIV<8> |  |

| bit 15        |                        |                  |                 |                  |                  |                    | bit 8     |  |

|               |                        |                  |                 |                  |                  |                    |           |  |

| R/W-0         | R/W-0                  | R/W-1            | R/W-1           | R/W-0            | R/W-0            | R/W-0              | R/W-0     |  |

|               |                        |                  | PLLDI           | V<7:0>           |                  |                    |           |  |

| bit 7         |                        |                  |                 |                  |                  |                    | bit 0     |  |

|               |                        |                  |                 |                  |                  |                    |           |  |

| Legend:       |                        |                  |                 |                  |                  |                    |           |  |

| R = Readabl   | e bit                  | W = Writable     | bit             | U = Unimplei     | mented bit, read | l as '0'           |           |  |

| -n = Value at | POR                    | '1' = Bit is set | t               | '0' = Bit is cle | eared            | x = Bit is unknown |           |  |

|               |                        |                  |                 |                  |                  |                    |           |  |

| bit 15-9      | Unimpleme              | nted: Read as '  | 0'              |                  |                  |                    |           |  |

| bit 8-0       | PLLDIV<8:0             | >: PLL Feedba    | ck Divisor bits | (also denoted    | as 'M', PLL mu   | ltiplier)          |           |  |

|               | 111111111              | = 513            |                 |                  |                  |                    |           |  |

|               | •                      |                  |                 |                  |                  |                    |           |  |

|               | •                      |                  |                 |                  |                  |                    |           |  |

|               | •                      |                  |                 |                  |                  |                    |           |  |

|               | 000110000              | = 50 (default)   |                 |                  |                  |                    |           |  |

|               | •                      |                  |                 |                  |                  |                    |           |  |

|               | •                      |                  |                 |                  |                  |                    |           |  |

|               | •                      |                  |                 |                  |                  |                    |           |  |

|               | 000000010<br>000000001 |                  |                 |                  |                  |                    |           |  |

|               | 000000000              | -                |                 |                  |                  |                    |           |  |

|               | 300000000              | -                |                 |                  |                  |                    |           |  |

Note 1: This register is reset only on a Power-on Reset (POR).

| U-0                 | U-0                                                                                    | U-0                                                                                     | U-0                                                                          | U-0                                     | U-0              | U-0                | U-0   |  |  |

|---------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------|------------------|--------------------|-------|--|--|

| —                   | _                                                                                      |                                                                                         | _                                                                            | —                                       | _                |                    | _     |  |  |

| bit 15              |                                                                                        |                                                                                         |                                                                              |                                         |                  |                    | bit   |  |  |

|                     |                                                                                        |                                                                                         |                                                                              |                                         |                  |                    |       |  |  |

| U-0                 | U-0                                                                                    | R/W-0                                                                                   | R/W-0                                                                        | R/W-0                                   | R/W-0            | R/W-0              | R/W-0 |  |  |

|                     |                                                                                        |                                                                                         |                                                                              |                                         |                  |                    |       |  |  |

| bit 7               |                                                                                        |                                                                                         |                                                                              |                                         |                  |                    | bit ( |  |  |

|                     |                                                                                        |                                                                                         |                                                                              |                                         |                  |                    |       |  |  |

| Legend:             |                                                                                        |                                                                                         |                                                                              |                                         |                  |                    |       |  |  |

| R = Readable        | e bit                                                                                  | W = Writable                                                                            | bit                                                                          | U = Unimplem                            | nented bit, read | d as '0'           |       |  |  |

| -n = Value at       | POR                                                                                    | '1' = Bit is set                                                                        |                                                                              | '0' = Bit is clea                       | ared             | x = Bit is unknown |       |  |  |

|                     |                                                                                        |                                                                                         |                                                                              |                                         |                  |                    |       |  |  |

|                     |                                                                                        |                                                                                         |                                                                              |                                         |                  |                    |       |  |  |

| bit 15-6            | Unimplemen                                                                             | ted: Read as '                                                                          | 0'                                                                           |                                         |                  |                    |       |  |  |

| bit 15-6<br>bit 5-0 | •                                                                                      | <b>ted:</b> Read as '<br>RC Oscillator T                                                |                                                                              |                                         |                  |                    |       |  |  |

|                     | <b>TUN&lt;5:0&gt;:</b> F                                                               |                                                                                         | uning bits <sup>(1)</sup>                                                    | 345 MHz)                                |                  |                    |       |  |  |

|                     | <b>TUN&lt;5:0&gt;:</b> F                                                               | RC Oscillator T                                                                         | uning bits <sup>(1)</sup>                                                    | 345 MHz)                                |                  |                    |       |  |  |

|                     | <b>TUN&lt;5:0&gt;:</b> F                                                               | RC Oscillator T                                                                         | uning bits <sup>(1)</sup>                                                    | 345 MHz)                                |                  |                    |       |  |  |

|                     | TUN<5:0>: F<br>111111 = Ce<br>•<br>•                                                   | RC Oscillator T<br>nter frequency                                                       | <sup>-</sup> uning bits <sup>(1)</sup><br>– 0.375% (7.                       | ·                                       |                  |                    |       |  |  |

|                     | TUN<5:0>: F<br>111111 = Ce<br>100001 = Ce                                              | RC Oscillator T                                                                         | - 0.375% (7.<br>– 11.625% (6                                                 | .52 MHz)                                |                  |                    |       |  |  |

|                     | TUN<5:0>: F<br>111111 = Ce<br>•<br>•<br>100001 = Ce<br>100000 = Ce<br>011111 = Ce      | RC Oscillator T<br>nter frequency<br>nter frequency<br>nter frequency<br>nter frequency | - 0.375% (7.<br>- 0.375% (7.<br>- 11.625% (6<br>- 12% (6.49<br>+ 11.625% (8  | .52 MHz)<br>MHz)<br>.23 MHz)            |                  |                    |       |  |  |

|                     | TUN<5:0>: F<br>111111 = Ce<br>•<br>•<br>100001 = Ce<br>100000 = Ce<br>011111 = Ce      | RC Oscillator T<br>nter frequency<br>nter frequency<br>nter frequency                   | - 0.375% (7.<br>- 0.375% (7.<br>- 11.625% (6<br>- 12% (6.49<br>+ 11.625% (8  | .52 MHz)<br>MHz)<br>.23 MHz)            |                  |                    |       |  |  |

|                     | TUN<5:0>: F<br>111111 = Ce<br>•<br>•<br>100001 = Ce<br>100000 = Ce<br>011111 = Ce      | RC Oscillator T<br>nter frequency<br>nter frequency<br>nter frequency<br>nter frequency | - 0.375% (7.<br>- 0.375% (7.<br>- 11.625% (6<br>- 12% (6.49<br>+ 11.625% (8  | .52 MHz)<br>MHz)<br>.23 MHz)            |                  |                    |       |  |  |

|                     | TUN<5:0>: F<br>111111 = Ce<br>•<br>•<br>100001 = Ce<br>100000 = Ce<br>011111 = Ce      | RC Oscillator T<br>nter frequency<br>nter frequency<br>nter frequency<br>nter frequency | - 0.375% (7.<br>- 0.375% (7.<br>- 11.625% (6<br>- 12% (6.49<br>+ 11.625% (8  | .52 MHz)<br>MHz)<br>.23 MHz)            |                  |                    |       |  |  |

|                     | TUN<5:0>: F<br>111111 = Ce<br>100001 = Ce<br>100000 = Ce<br>011111 = Ce<br>011110 = Ce | RC Oscillator T<br>nter frequency<br>nter frequency<br>nter frequency<br>nter frequency | - 0.375% (7.<br>- 11.625% (6<br>- 12% (6.49<br>+ 11.625% (8<br>+ 11.25% (8.1 | .52 MHz)<br>MHz)<br>.23 MHz)<br>20 MHz) |                  |                    |       |  |  |

## REGISTER 9-4: OSCTUN: FRC OSCILLATOR TUNING REGISTER<sup>(2)</sup>

- **Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation and is neither characterized nor tested.

- 2: This register is reset only on a Power-on Reset (POR).

NOTES:

| R/W-0         | U-0                                                                                           | R/W-0                                                                    | U-0            | U-0                    | U-0             | U-0                | U-0 |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------|------------------------|-----------------|--------------------|-----|--|--|--|--|--|

| TON           |                                                                                               | TSIDL                                                                    |                | —                      |                 | —                  |     |  |  |  |  |  |

| bit 15        |                                                                                               |                                                                          |                |                        |                 |                    | bit |  |  |  |  |  |

| U-0           | R/W-0                                                                                         | R/W-0                                                                    | R/W-0          | R/W-0                  | U-0             | R/W-0              | U-0 |  |  |  |  |  |

| 0-0           | TGATE                                                                                         |                                                                          | S<1:0>         | T32                    | 0-0             | TCS <sup>(1)</sup> | 0-0 |  |  |  |  |  |

| <br>bit 7     | IGAIE                                                                                         | TCKP                                                                     | 5<1.0>         | 132                    | _               | 1030               | bit |  |  |  |  |  |

|               |                                                                                               |                                                                          |                |                        |                 |                    |     |  |  |  |  |  |

| Legend:       |                                                                                               |                                                                          |                |                        |                 |                    |     |  |  |  |  |  |

| R = Readable  | e bit                                                                                         | W = Writable                                                             | bit            | U = Unimplem           | nented bit, rea | d as '0'           |     |  |  |  |  |  |

| -n = Value at | POR                                                                                           | '1' = Bit is se                                                          | t              | '0' = Bit is clea      | ared            | x = Bit is unkno   | own |  |  |  |  |  |

| bit 15        | TON: Timerx                                                                                   | On bit                                                                   |                |                        |                 |                    |     |  |  |  |  |  |

|               | When T32 = 1                                                                                  | L:                                                                       |                |                        |                 |                    |     |  |  |  |  |  |

|               | 1 = Starts 32-<br>0 = Stops 32-                                                               |                                                                          |                |                        |                 |                    |     |  |  |  |  |  |

|               | <u>When T32 = 0</u>                                                                           |                                                                          |                |                        |                 |                    |     |  |  |  |  |  |

|               | 1 = Starts 16-<br>0 = Stops 16-                                                               |                                                                          |                |                        |                 |                    |     |  |  |  |  |  |

| bit 14        | Unimplemen                                                                                    |                                                                          | ٠́ ()'         |                        |                 |                    |     |  |  |  |  |  |

| bit 13        | TSIDL: Stop i                                                                                 |                                                                          |                |                        |                 |                    |     |  |  |  |  |  |

|               | •                                                                                             | ue module ope                                                            | eration when d | evice enters Idl<br>de | e mode          |                    |     |  |  |  |  |  |

| bit 12-7      | Unimplemen                                                                                    | -                                                                        |                |                        |                 |                    |     |  |  |  |  |  |

| bit 6         | TGATE: Timerx Gated Time Accumulation Enable bit                                              |                                                                          |                |                        |                 |                    |     |  |  |  |  |  |

|               | When TCS = 1:                                                                                 |                                                                          |                |                        |                 |                    |     |  |  |  |  |  |

|               | This bit is igno                                                                              |                                                                          |                |                        |                 |                    |     |  |  |  |  |  |

|               |                                                                                               | $\frac{\text{When TCS} = 0}{1 = \text{Gated time accumulation enabled}}$ |                |                        |                 |                    |     |  |  |  |  |  |

|               | <ol> <li>Gated time accumulation enabled</li> <li>Gated time accumulation disabled</li> </ol> |                                                                          |                |                        |                 |                    |     |  |  |  |  |  |

| bit 5-4       | TCKPS<1:0>                                                                                    | : Timerx Input                                                           | Clock Presca   | le Select bits         |                 |                    |     |  |  |  |  |  |

|               | 11 = 1:256                                                                                    |                                                                          |                |                        |                 |                    |     |  |  |  |  |  |

|               | 10 = 1:64                                                                                     |                                                                          |                |                        |                 |                    |     |  |  |  |  |  |

|               | 01 = 1:8<br>00 = 1:1                                                                          |                                                                          |                |                        |                 |                    |     |  |  |  |  |  |

| bit 3         | T32: 32-bit Ti                                                                                | mer Mode Sel                                                             | ect bit        |                        |                 |                    |     |  |  |  |  |  |

|               | 1 = Timerx an<br>0 = Timerx an                                                                |                                                                          |                |                        |                 |                    |     |  |  |  |  |  |

| bit 2         | Unimplemen                                                                                    | -                                                                        |                |                        |                 |                    |     |  |  |  |  |  |

| bit 1         | TCS: Timerx                                                                                   |                                                                          |                |                        |                 |                    |     |  |  |  |  |  |

|               | 1 = External c<br>0 = Internal cl                                                             | clock from pin                                                           |                | rising edge)           |                 |                    |     |  |  |  |  |  |

|               |                                                                                               | · · /                                                                    |                |                        |                 |                    |     |  |  |  |  |  |

### REGISTER 13-1: TxCON (T2CON, T4CON, T6CON OR T8CON) CONTROL REGISTER

Note 1: The TxCK pin is not available on all timers. Refer to the "Pin Diagrams" section for the available pins.

## 20.4 ADC Helpful Tips

- 1. The SMPI<3:0> (AD1CON2<5:2>) control bits:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated if enabled.

- b) When the CSCNA bit (AD1CON2<10>) is set to '1', determines when the ADC analog scan channel list defined in the AD1CSSL/ AD1CSSH registers starts over from the beginning.

- c) On devices without a DMA peripheral, determines when ADC result buffer pointer to ADC1BUF0-ADC1BUFF, gets reset back to the beginning at ADC1BUF0.

- On devices without a DMA module, the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF regardless of which analog inputs are being used subject to the SMPI<3:0> bits (AD1CON2<5:2>) and the condition described in 1c above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- On devices with a DMA module, the ADC module has only 1 ADC result buffer, (i.e., ADC1BUF0), per ADC peripheral and the ADC conversion result must be read either by the CPU or DMA controller before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (AD1CON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in manual sample mode, particularly where the users code is setting the SAMP bit (AD1CON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

- 5. On devices with two ADC modules, the ADCxPCFG registers for both ADC modules must be set to a logic '1' to configure a target I/O pin as a digital I/O pin. Failure to do so means that any alternate digital input function will always see only a logic '0' as the digital input buffer is held in Disable mode.

### 20.5 ADC Resources

Many useful resources related to ADC are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en546061                                        |

#### 20.5.1 KEY RESOURCES

- Section 16. "Analog-to-Digital Converter (ADC)" (DS70183)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

## 24.1 DC Characteristics

| Characteristic | VDD Range                | Temp Range      | Max MIPS                   |  |  |  |  |  |  |  |

|----------------|--------------------------|-----------------|----------------------------|--|--|--|--|--|--|--|

| Characteristic | (in Volts)               | (in °C)         | PIC24HJXXXGPX06A/X08A/X10A |  |  |  |  |  |  |  |

|                | VBOR-3.6V <sup>(1)</sup> | -40°C to +85°C  | 40                         |  |  |  |  |  |  |  |

| _              | VBOR-3.6V <sup>(1)</sup> | -40°C to +125°C | 40                         |  |  |  |  |  |  |  |

#### TABLE 24-1: OPERATING MIPS VS. VOLTAGE

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules such as the ADC will have degraded performance. Device functionality is tested but not characterized. Refer to parameter BO10 in Table 24-11 for the minimum and maximum BOR values.

#### TABLE 24-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                      | Symbol | Min         | Тур         | Max  | Unit |

|---------------------------------------------------------------------------------------------|--------|-------------|-------------|------|------|

| Industrial Temperature Devices                                                              |        |             |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40         |             | +125 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40         |             | +85  | °C   |

| Extended Temperature Devices                                                                |        |             |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40         |             | +150 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40         |             | +125 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$ | PD     | PINT + PI/O |             |      | W    |

| I/O Pin Power Dissipation:<br>I/O = $\Sigma$ ({VDD - VOH} x IOH) + $\Sigma$ (VOL x IOL)     |        |             |             |      |      |

| Maximum Allowed Power Dissipation                                                           | Pdmax  | (           | TJ — ΤΑ)/θ. | IA   | W    |

#### TABLE 24-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                        | Symbol | Тур | Max | Unit | Notes |

|-------------------------------------------------------|--------|-----|-----|------|-------|

| Package Thermal Resistance, 100-pin TQFP (14x14x1 mm) | θja    | 40  |     | °C/W | 1     |

| Package Thermal Resistance, 100-pin TQFP (12x12x1 mm) | θja    | 40  | _   | °C/W | 1     |

| Package Thermal Resistance, 64-pin TQFP (10x10x1 mm)  | θја    | 40  | _   | °C/W | 1     |

| Package Thermal Resistance, 64-pin QFN (9x9x0.9 mm)   | θja    | 28  | _   | °C/W | 1     |

Note 1: Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

| DC CHA       | RACTER                | ISTICS                                                                | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                    |                       |       |                                                                                                                                    |  |

|--------------|-----------------------|-----------------------------------------------------------------------|-------------------------------------------------------|--------------------|-----------------------|-------|------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No. | Symbol Characteristic |                                                                       |                                                       | Typ <sup>(1)</sup> | Max                   | Units | Conditions                                                                                                                         |  |

| DI60a        | licl                  | Input Low Injection Current                                           | 0                                                     | _                  | <sub>-5</sub> (5,8)   | mA    | All pins except VDD, Vss, AVDD,<br>AVss, MCLR, Vcap, SOSCI,<br>SOSCO, and RB11                                                     |  |

| DI60b        | ІІСН                  | Input High Injection Current                                          | 0                                                     | _                  | +5 <sup>(6,7,8)</sup> | mA    | All pins except VDD, Vss, AVDD,<br>AVss, MCLR, VcAP, SOSCI,<br>SOSCO, RB11, and all 5V<br>tolerant pins <sup>(7)</sup>             |  |

| DI60c        | Σ ΙΙΟΤ                | Total Input Injection Current<br>(sum of all I/O and control<br>pins) | -20 <sup>(9)</sup>                                    | _                  | +20 <sup>(9)</sup>    | mA    | Absolute instantaneous sum of<br>all $\pm$ input injection currents<br>from all I/O pins<br>(   IICL +   IICH   ) $\leq \sum$ IICT |  |

#### TABLE 24-9: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

- 4: See "Pin Diagrams" for a list of 5V tolerant pins.

- **5:** VIL source < (Vss 0.3). Characterized but not tested.

- **6:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 7: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 8: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

- **9:** Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

| DC CHA       | RACTER | ISTICS                                                                                                                                    | Standard<br>(unless of<br>Operating | therwis | e stated<br>ature | l)<br>-40°C ≤ | <b>3.0V to 3.6V</b><br>TA $\leq$ +85°C for Industrial<br>TA $\leq$ +125°C for Extended                        |

|--------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------|-------------------|---------------|---------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Symbol | Characteristic                                                                                                                            | Min                                 | Тур     | Max               | Units         | Conditions                                                                                                    |

|              |        | Output Low Voltage<br>I/O Pins:<br>2x Sink Driver Pins - All pins not<br>defined by 4x or 8x driver pins                                  | _                                   | _       | 0.4               | V             | IOL $\leq$ 3 mA, VDD = 3.3V                                                                                   |

| DO10         | Vol    | <b>Output Low Voltage</b><br>I/O Pins:<br>4x Sink Driver Pins - RA2, RA3,<br>RA9, RA10, RA14, RA15, RB0,<br>RB1, RB11, RF4, RF5, RG2, RG3 | _                                   | _       | 0.4               | V             | IOL $\leq$ 6 mA, VDD = 3.3V                                                                                   |

|              |        | Output Low Voltage<br>I/O Pins:<br>8x Sink Driver Pins - OSC2, CLKO,<br>RC15                                                              | _                                   | _       | 0.4               | V             | IOL $\leq$ 10 mA, VDD = 3.3V                                                                                  |

|              |        | Output High Voltage<br>I/O Pins:<br>2x Source Driver Pins - All pins not<br>defined by 4x or 8x driver pins                               | 2.4                                 | _       | _                 | V             | $IOL \ge -3$ mA, VDD = 3.3V                                                                                   |

| DO20         | Vон    | Output High Voltage<br>I/O Pins:<br>4x Source Driver Pins - RA2, RA3,<br>RA9, RA10, RA14, RA15, RB0,<br>RB1, RB11, RF4, RF5, RG2, RG3     | 2.4                                 | _       | _                 | V             | $IOL \ge -6$ mA, VDD = 3.3V                                                                                   |

|              |        | Output High Voltage<br>I/O Pins:<br>8x Source Driver Pins - OSC2,<br>CLKO, RC15                                                           | 2.4                                 | _       | _                 | V             | IOL ≥ -10 mA, VDD = 3.3V                                                                                      |

|              |        | Output High Voltage<br>I/O Pins:                                                                                                          | 1.5                                 | _       | _                 |               | IOH ≥ -6 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                  |

|              |        | 2x Source Driver Pins - All pins not defined by 4x or 8x driver pins                                                                      | 2.0                                 | _       | _                 | V             | IOH ≥ -5 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                  |

|              |        |                                                                                                                                           | 3.0                                 | _       | _                 |               | IOH ≥ -2 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                  |

|              |        | <b>Output High Voltage</b><br>4x Source Driver Pins - RA2, RA3,                                                                           | 1.5                                 | _       | _                 |               | IOH ≥ -12 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                 |

| DO20A        | Voн1   | RA9, RA10, RA14, RA15, RB0,<br>RB1, RB11, RF4, RF5, RG2, RG3                                                                              | 2.0                                 | -       | _                 | V             | IOH ≥ -11 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                 |

|              |        |                                                                                                                                           | 3.0                                 | _       | _                 |               | $\label{eq:IOH} \begin{array}{l} \mbox{IOH} \geq -3 \mbox{ mA, VDD} = 3.3 V \\ \mbox{See Note 1} \end{array}$ |

|              |        | Output High Voltage<br>8x Source Driver Pins - OSC2,                                                                                      | 1.5                                 | _       | _                 |               | IOH ≥ -16 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                 |

|              |        | CLKO, RC15                                                                                                                                | 2.0                                 |         |                   | V             | IOH ≥ -12 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                 |

|              |        |                                                                                                                                           | 3.0                                 |         |                   |               | IOH ≥ -4 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                  |

#### TABLE 24-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

**Note 1:** Parameters are characterized, but not tested.

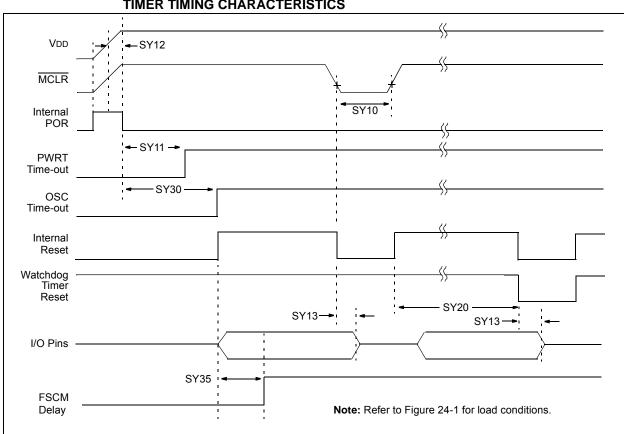

## FIGURE 24-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING CHARACTERISTICS

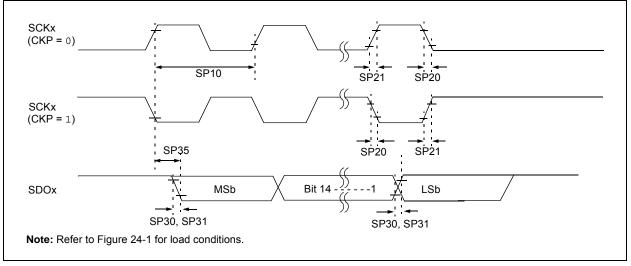

#### TABLE 24-28: SPIx MAXIMUM DATA/CLOCK RATE SUMMARY

| AC CHARAG            | CTERISTICS                               |                                             | $\begin{tabular}{ l l l l l l l l l l l l l l l l l l l$ |     |     |     |

|----------------------|------------------------------------------|---------------------------------------------|----------------------------------------------------------|-----|-----|-----|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)               | CKE | СКР | SMP |

| 15 MHz               | Table 24-29                              | —                                           | —                                                        | 0,1 | 0,1 | 0,1 |

| 10 MHz               | —                                        | Table 24-30                                 | —                                                        | 1   | 0,1 | 1   |

| 10 MHz               | —                                        | Table 24-31                                 | —                                                        | 0   | 0,1 | 1   |

| 15 MHz               | —                                        | —                                           | Table 24-32                                              | 1   | 0   | 0   |

| 11 MHz               | —                                        | —                                           | Table 24-33                                              | 1   | 1   | 0   |

| 15 MHz               | _                                        | _                                           | Table 24-34                                              | 0   | 1   | 0   |

| 11 MHz               |                                          |                                             | Table 24-35                                              | 0   | 0   | 0   |

#### FIGURE 24-9: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY CKE = 0) TIMING CHARACTERISTICS

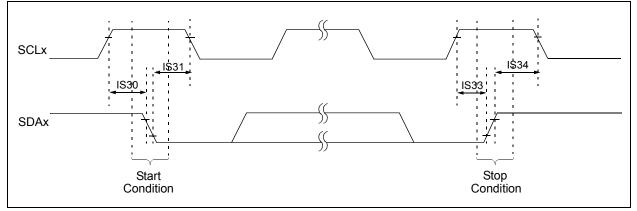

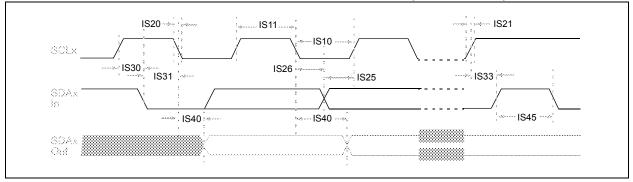

#### FIGURE 24-19: I2Cx BUS START/STOP BITS TIMING CHARACTERISTICS (SLAVE MODE)

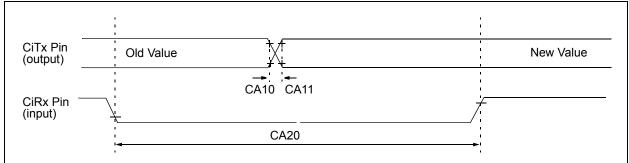

### FIGURE 24-21: ECAN™ MODULE I/O TIMING CHARACTERISTICS

#### TABLE 24-38: ECAN™ MODULE I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industria} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extende} \end{array}$ |                    |     |       | $A \le +85^{\circ}C$ for Industrial |

|--------------------|--------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|-------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                | Min                                                                                                                                                                                                                                                                                   | Typ <sup>(2)</sup> | Max | Units | Conditions                          |

| CA10               | TioF   | Port Output Fall Time                        | —                                                                                                                                                                                                                                                                                     |                    | _   | ns    | See parameter D032                  |

| CA11               | TioR   | Port Output Rise Time                        | —                                                                                                                                                                                                                                                                                     |                    | _   | ns    | See parameter D031                  |

| CA20               | Tcwf   | Pulse-Width to Trigger<br>CAN Wake-up Filter | 120                                                                                                                                                                                                                                                                                   | —                  | l   | ns    | —                                   |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

| АС СНА       | RACTERIS | TICS                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |           |           |           |                                                  |  |

|--------------|----------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|-----------|--------------------------------------------------|--|

| Param<br>No. | Symbol   | Characteristic                 | Min.                                                                                                                                                                                                                                                                                    | Тур       | Max.      | Units     | Conditions                                       |  |

|              |          | ADC Accuracy (10-bit Mode      | e) – Meas                                                                                                                                                                                                                                                                               | uremen    | ts with e | xternal   | VREF+/VREF-                                      |  |

| AD20b        | Nr       | Resolution                     | 1                                                                                                                                                                                                                                                                                       | 0 data bi | its       | bits      |                                                  |  |

| AD21b        | INL      | Integral Nonlinearity          | -1.5                                                                                                                                                                                                                                                                                    | —         | +1.5      | LSb       | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| AD22b        | DNL      | Differential Nonlinearity      | >-1                                                                                                                                                                                                                                                                                     | —         | <1        | LSb       | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| AD23b        | Gerr     | Gain Error                     | —                                                                                                                                                                                                                                                                                       | 3         | 6         | LSb       | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| AD24b        | EOFF     | Offset Error                   | —                                                                                                                                                                                                                                                                                       | 2         | 5         | LSb       | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| AD25b        | —        | Monotonicity                   |                                                                                                                                                                                                                                                                                         |           | _         | —         | Guaranteed                                       |  |

|              |          | ADC Accuracy (10-bit Mode      | e) – Meas                                                                                                                                                                                                                                                                               | uremen    | ts with i | nternal V | VREF+/VREF-                                      |  |

| AD20b        | Nr       | Resolution                     | 1                                                                                                                                                                                                                                                                                       | 0 data bi | its       | bits      |                                                  |  |

| AD21b        | INL      | Integral Nonlinearity          | -1                                                                                                                                                                                                                                                                                      |           | +1        | LSb       | VINL = AVSS = 0V, AVDD = 3.6V                    |  |

| AD22b        | DNL      | Differential Nonlinearity      | >-1                                                                                                                                                                                                                                                                                     |           | <1        | LSb       | VINL = AVSS = 0V, AVDD = 3.6V                    |  |

| AD23b        | Gerr     | Gain Error                     | —                                                                                                                                                                                                                                                                                       | 7         | 15        | LSb       | VINL = AVSS = 0V, AVDD = 3.6V                    |  |

| AD24b        | EOFF     | Offset Error                   | —                                                                                                                                                                                                                                                                                       | 3         | 7         | LSb       | VINL = AVSS = 0V, AVDD = 3.6V                    |  |

| AD25b        | —        | Monotonicity                   | —                                                                                                                                                                                                                                                                                       |           | _         | —         | Guaranteed                                       |  |

|              |          | Dynamic                        | Performa                                                                                                                                                                                                                                                                                | ance (10  | -bit Mod  | e)        |                                                  |  |

| AD30b        | THD      | Total Harmonic Distortion      | —                                                                                                                                                                                                                                                                                       | —         | -64       | dB        | —                                                |  |

| AD31b        | SINAD    | Signal to Noise and Distortion | 57                                                                                                                                                                                                                                                                                      | 58.5      | _         | dB        | _                                                |  |

| AD32b        | SFDR     | Spurious Free Dynamic<br>Range | 72                                                                                                                                                                                                                                                                                      | —         | —         | dB        | _                                                |  |

| AD33b        | Fnyq     | Input Signal Bandwidth         |                                                                                                                                                                                                                                                                                         |           | 550       | kHz       | _                                                |  |

| AD34b        | ENOB     | Effective Number of Bits       | 9.16                                                                                                                                                                                                                                                                                    | 9.4       |           | bits      | —                                                |  |

## TABLE 24-41: ADC MODULE SPECIFICATIONS (10-BIT MODE)<sup>(1)</sup>

Note 1: Injection currents > |0| can affect the ADC results by approximately 4-6 counts (i.e., VIH source > (VDD + 0.3) or VIL source < (VSS - 0.3)).

| DC CHARACTERISTICS |        |                                                                                                                                       | UTPUT SPECIFICATIONSStandard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for High<br>Temperature |      |      |       |                                                    |

|--------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|----------------------------------------------------|

| Param.             | Symbol | Characteristic                                                                                                                        | Min.                                                                                                                                                                         | Тур. | Max. | Units | Conditions                                         |

|                    |        | Output Low Voltage<br>I/O Pins:<br>2x Sink Driver Pins - All pins not<br>defined by 4x or 8x driver pins                              | _                                                                                                                                                                            | _    | 0.4  | V     | IOL ≤ 1.8 mA, VDD = 3.3V<br>See <b>Note 1</b>      |

| HDO10              | Vol    | Output Low Voltage<br>I/O Pins:<br>4x Sink Driver Pins - RA2, RA3, RA9,<br>RA10, RA14, RA15, RB0, RB1, RB11,<br>RF4, RF5, RG2, RG3    | _                                                                                                                                                                            | _    | 0.4  | V     | IOL ≤ 3.6 mA, VDD = 3.3V<br>See <b>Note 1</b>      |

|                    |        | Output Low Voltage<br>I/O Pins:<br>8x Sink Driver Pins - OSC2, CLKO,<br>RC15                                                          | _                                                                                                                                                                            | _    | 0.4  | V     | Io∟ ≤ 6 mA, Voo = 3.3V<br>See <b>Note 1</b>        |

|                    |        | Output High Voltage<br>I/O Pins:<br>2x Source Driver Pins - All pins not<br>defined by 4x or 8x driver pins                           | 2.4                                                                                                                                                                          | _    | _    | V     | Io∟ ≥ -1.8 mA, VDD = 3.3V<br>See <b>Note 1</b>     |