Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | PIC                                                                              |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | · · · · · · · · · · · · · · · · · · ·                                            |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 32x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp210at-i-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

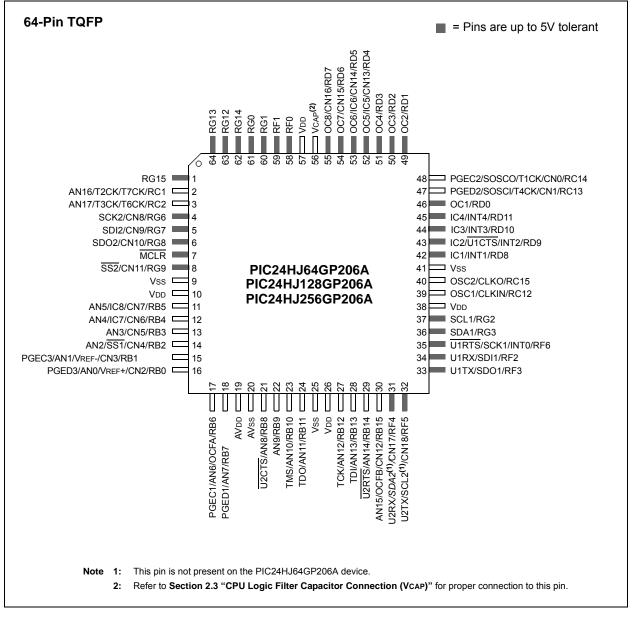

#### Pin Diagrams (Continued)

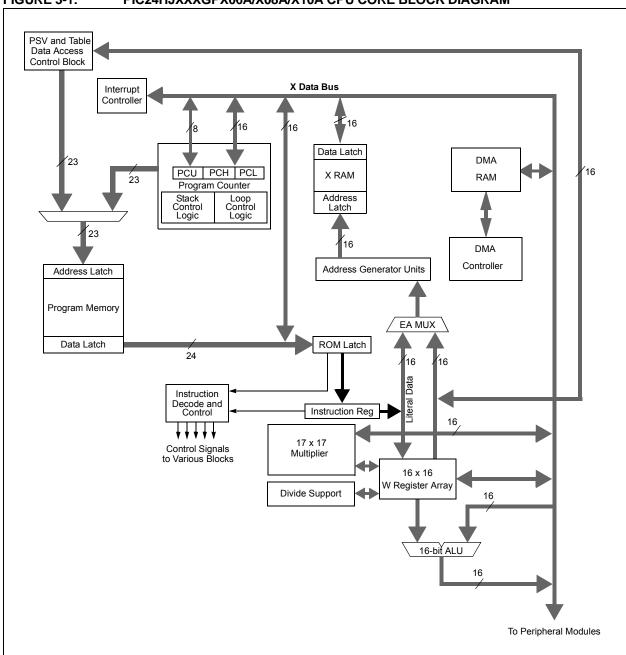

#### FIGURE 3-1: PIC24HJXXXGPX06A/X08A/X10A CPU CORE BLOCK DIAGRAM

| File Name  | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7                                                         | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|------------|------|--------|--------|--------|--------|--------|--------|-------|-------|---------------------------------------------------------------|----------|-------|-------|-------|--------|--------|--------|---------------|

| C1RXF1EID  | 0446 |        | 1      | 1      | EID<   | :15:8> |        |       |       |                                                               |          |       | EID<  | 7:0>  |        |        |        | xxxx          |

| C1RXF2SID  | 0448 |        |        |        | SID<   | :10:3> |        |       |       |                                                               | SID<2:0> |       | —     | EXIDE | _      | EID<   | 17:16> | xxxx          |

| C1RXF2EID  | 044A |        |        |        | EID<   | :15:8> |        |       |       |                                                               |          |       | EID<  | 7:0>  |        |        |        | xxxx          |

| C1RXF3SID  | 044C |        |        |        | SID<   | :10:3> |        |       |       |                                                               | SID<2:0> |       | _     | EXIDE | _      | EID<   | 17:16> | xxxx          |

| C1RXF3EID  | 044E |        |        |        | EID<   | :15:8> |        |       |       |                                                               |          |       | EID<  | 7:0>  |        |        |        | xxxx          |

| C1RXF4SID  | 0450 |        |        |        | SID<   | :10:3> |        |       |       |                                                               | SID<2:0> |       | _     | EXIDE | _      | EID<   | 17:16> | xxxx          |

| C1RXF4EID  | 0452 |        |        |        | EID<   | :15:8> |        |       |       |                                                               |          |       | EID<  | 7:0>  |        |        |        | xxxx          |

| C1RXF5SID  | 0454 |        |        |        | SID<   | :10:3> |        |       |       |                                                               | SID<2:0> |       | _     | EXIDE | —      | EID<'  | 17:16> | xxxx          |

| C1RXF5EID  | 0456 |        |        |        | EID<   | :15:8> |        |       |       |                                                               |          |       | EID<  | 7:0>  |        |        |        | xxxx          |

| C1RXF6SID  | 0458 |        |        |        | SID<   | :10:3> |        |       |       |                                                               | SID<2:0> |       | _     | EXIDE | _      | EID<'  | 17:16> | xxxx          |

| C1RXF6EID  | 045A |        |        |        | EID<   | :15:8> |        |       |       |                                                               |          |       | EID<  | 7:0>  |        |        |        | xxxx          |

| C1RXF7SID  | 045C |        |        |        | SID<   | :10:3> |        |       |       | SID<2:0> — EXIDE —                                            |          |       |       | EID<' | 17:16> | xxxx   |        |               |

| C1RXF7EID  | 045E |        |        |        | EID<   | :15:8> |        |       |       | EID<7:0>                                                      |          |       |       |       |        | xxxx   |        |               |

| C1RXF8SID  | 0460 |        |        |        | SID<   | :10:3> |        |       |       |                                                               | SID<2:0> |       | —     | EXIDE | _      | EID<'  | 17:16> | xxxx          |

| C1RXF8EID  | 0462 |        |        |        | EID<   | :15:8> |        |       |       | EID<7:0>                                                      |          |       |       |       |        | xxxx   |        |               |

| C1RXF9SID  | 0464 |        |        |        | SID<   | :10:3> |        |       |       | SID<2:0> — EXIDE — EID<17:16>                                 |          |       |       |       | 17:16> | xxxx   |        |               |

| C1RXF9EID  | 0466 |        |        |        | EID<   | :15:8> |        |       |       | EID<7:0>                                                      |          |       |       |       |        |        | xxxx   |               |

| C1RXF10SID | 0468 |        |        |        | SID<   | :10:3> |        |       |       | SID<2:0>         —         EXIDE         —         EID<17:16> |          |       |       |       |        | 17:16> | xxxx   |               |

| C1RXF10EID | 046A |        |        |        | EID<   | :15:8> |        |       |       |                                                               |          |       | EID<  | 7:0>  |        |        |        | xxxx          |

| C1RXF11SID | 046C |        |        |        | SID<   | :10:3> |        |       |       |                                                               | SID<2:0> |       | —     | EXIDE | —      | EID<'  | 17:16> | xxxx          |

| C1RXF11EID | 046E |        |        |        | EID<   | :15:8> |        |       |       |                                                               |          |       | EID<  | 7:0>  |        |        |        | xxxx          |

| C1RXF12SID | 0470 |        |        |        | SID<   | :10:3> |        |       |       |                                                               | SID<2:0> |       | —     | EXIDE | —      | EID<   | 17:16> | xxxx          |

| C1RXF12EID | 0472 |        |        |        | EID<   | :15:8> |        |       |       |                                                               |          |       | EID<  | 7:0>  |        |        |        | xxxx          |

| C1RXF13SID | 0474 |        |        |        | SID<   | :10:3> |        |       |       |                                                               | SID<2:0> |       | —     | EXIDE | —      | EID<   | 17:16> | xxxx          |

| C1RXF13EID | 0476 |        |        |        | EID<   | :15:8> |        |       |       | EID<7:0>                                                      |          |       |       |       | xxxx   |        |        |               |

| C1RXF14SID | 0478 |        |        |        | SID<   | :10:3> |        |       |       |                                                               | SID<2:0> |       | -     | EXIDE | —      | EID<   | 17:16> | xxxx          |

| C1RXF14EID | 047A |        |        |        | EID<   | :15:8> |        |       |       |                                                               |          |       | EID<  | 7:0>  |        |        |        | xxxx          |

| C1RXF15SID | 047C |        |        |        | SID<   | :10:3> |        |       |       |                                                               | SID<2:0> |       | —     | EXIDE | —      | EID<'  | 17:16> | xxxx          |

| C1RXF15EID | 047E |        |        |        | EID<   | :15:8> |        |       |       |                                                               |          |       | EID<  | 7:0>  |        |        |        | xxxx          |

#### ONILY (CONTINUED) DICOALLINNY ODEACA/E40A/C40A DEVICES

Legend:

© 2009-2012 Microchip Technology Inc.

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

| Addressing Mode                        | Description                                                                                            |

|----------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                   | The address of the file register is specified explicitly.                                              |

| Register Direct                        | The contents of a register are accessed directly.                                                      |

| Register Indirect                      | The contents of Wn forms the EA.                                                                       |

| Register Indirect Post-Modified        | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified         | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset  | The sum of Wn and a literal forms the EA.                                                              |

#### TABLE 4-34: FUNDAMENTAL ADDRESSING MODES SUPPORTED

#### 4.3.3 MOVE INSTRUCTIONS

Move instructions provide a greater degree of addressing flexibility than other instructions. In addition to the Addressing modes supported by most MCU instructions, move instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the Addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared between both source and destination (but typically only used by one).

In summary, the following Addressing modes are supported by move instructions:

- Register Direct

- · Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-bit Literal

- 16-bit Literal

| Note: | Not all   | instructi | ons   | suppo | ort | all  | the  |

|-------|-----------|-----------|-------|-------|-----|------|------|

|       | Addressi  | ng mo     | des   | give  | n   | ab   | ove. |

|       | Individua | l instru  | ction | s ma  | ay  | sup  | port |

|       | different | subsets   | of    | these | Ado | dres | sing |

|       | modes.    |           |       |       |     |      |      |

#### 4.3.4 OTHER INSTRUCTIONS

Besides the various addressing modes outlined above, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

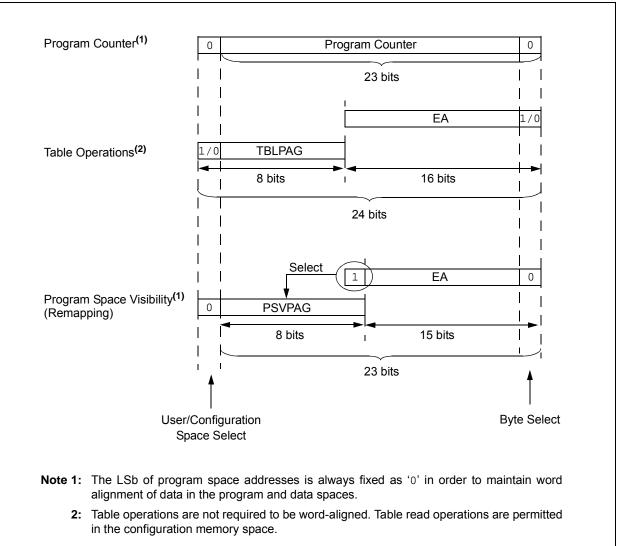

### 4.4 Interfacing Program and Data Memory Spaces

The PIC24HJXXXGPX06A/X08A/X10A architecture uses a 24-bit wide program space and a 16-bit wide data space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the PIC24HJXXXGPX06A/X08A/X10A architecture provides two methods by which program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the data space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated from time to time. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look ups from a large table of static data. It can only access the least significant word of the program word.

#### 4.4.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Page register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the Most Significant bit of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

#### FIGURE 4-6: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

| ABLE 7-1         | 1 1                                  | T VECTORS   | 1            | 1                                    |

|------------------|--------------------------------------|-------------|--------------|--------------------------------------|

| Vector<br>Number | Interrupt<br>Request (IRQ)<br>Number | IVT Address | AIVT Address | Interrupt Source                     |

| 8                | 0                                    | 0x000014    | 0x000114     | INT0 – External Interrupt 0          |

| 9                | 1                                    | 0x000016    | 0x000116     | IC1 – Input Capture 1                |

| 10               | 2                                    | 0x000018    | 0x000118     | OC1 – Output Compare 1               |

| 11               | 3                                    | 0x00001A    | 0x00011A     | T1 – Timer1                          |

| 12               | 4                                    | 0x00001C    | 0x00011C     | DMA0 – DMA Channel 0                 |

| 13               | 5                                    | 0x00001E    | 0x00011E     | IC2 – Input Capture 2                |

| 14               | 6                                    | 0x000020    | 0x000120     | OC2 – Output Compare 2               |

| 15               | 7                                    | 0x000022    | 0x000122     | T2 – Timer2                          |

| 16               | 8                                    | 0x000024    | 0x000124     | T3 – Timer3                          |

| 17               | 9                                    | 0x000026    | 0x000126     | SPI1E – SPI1 Error                   |

| 18               | 10                                   | 0x000028    | 0x000128     | SPI1 – SPI1 Transfer Done            |

| 19               | 11                                   | 0x00002A    | 0x00012A     | U1RX – UART1 Receiver                |

| 20               | 12                                   | 0x00002C    | 0x00012C     | U1TX – UART1 Transmitter             |

| 21               | 13                                   | 0x00002E    | 0x00012E     | ADC1 – Analog-to-Digital Converter 1 |

| 22               | 14                                   | 0x000030    | 0x000130     | DMA1 – DMA Channel 1                 |

| 23               | 15                                   | 0x000032    | 0x000132     | Reserved                             |

| 24               | 16                                   | 0x000034    | 0x000134     | SI2C1 – I2C1 Slave Events            |

| 25               | 17                                   | 0x000036    | 0x000136     | MI2C1 – I2C1 Master Events           |

| 26               | 18                                   | 0x000038    | 0x000138     | Reserved                             |

| 27               | 19                                   | 0x00003A    | 0x00013A     | CN - Change Notification Interrupt   |

| 28               | 20                                   | 0x00003C    | 0x00013C     | INT1 – External Interrupt 1          |

| 29               | 21                                   | 0x00003E    | 0x00013E     | ADC2 – Analog-to-Digital Converter 2 |

| 30               | 22                                   | 0x000040    | 0x000140     | IC7 – Input Capture 7                |

| 31               | 23                                   | 0x000042    | 0x000142     | IC8 – Input Capture 8                |

| 32               | 24                                   | 0x000044    | 0x000144     | DMA2 – DMA Channel 2                 |

| 33               | 25                                   | 0x000046    | 0x000146     | OC3 – Output Compare 3               |

| 34               | 26                                   | 0x000048    | 0x000148     | OC4 – Output Compare 4               |

| 35               | 27                                   | 0x00004A    | 0x00014A     | T4 – Timer4                          |

| 36               | 28                                   | 0x00004C    | 0x00014C     | T5 – Timer5                          |

| 37               | 29                                   | 0x00004E    | 0x00014E     | INT2 – External Interrupt 2          |

| 38               | 30                                   | 0x000050    | 0x000150     | U2RX – UART2 Receiver                |

| 39               | 31                                   | 0x000052    | 0x000152     | U2TX – UART2 Transmitter             |

| 40               | 32                                   | 0x000054    | 0x000154     | SPI2E – SPI2 Error                   |

| 41               | 33                                   | 0x000056    | 0x000156     | SPI1 – SPI1 Transfer Done            |

| 42               | 34                                   | 0x000058    | 0x000158     | C1RX – ECAN1 Receive Data Ready      |

| 43               | 35                                   | 0x00005A    | 0x00015A     | C1 – ECAN1 Event                     |

| 44               | 36                                   | 0x00005C    | 0x00015C     | DMA3 – DMA Channel 3                 |

| 45               | 37                                   | 0x00005E    | 0x00015E     | IC3 – Input Capture 3                |

| 46               | 38                                   | 0x000060    | 0x000160     | IC4 – Input Capture 4                |

| 47               | 39                                   | 0x000062    | 0x000162     | IC5 – Input Capture 5                |

| 48               | 40                                   | 0x000064    | 0x000164     | IC6 – Input Capture 6                |

| 49               | 41                                   | 0x000066    | 0x000166     | OC5 – Output Compare 5               |

| 50               | 42                                   | 0x000068    | 0x000168     | OC6 – Output Compare 6               |

| 51               | 43                                   | 0x00006A    | 0x00016A     | OC7 – Output Compare 7               |

| 52               | 44                                   | 0x00006C    | 0x00016C     | OC8 – Output Compare 8               |

| 53               | 45                                   | 0x00006E    | 0x00016E     | Reserved                             |

TABLE 7-1: INTERRUPT VECTORS

|                         | U-0                                                                                                                                                                       | U-0                                                                                                                                  | U-0                                                                                                                     | U-0                                                    | U-0             | U-0             | U-0 |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------|-----------------|-----|

| —                       | _                                                                                                                                                                         |                                                                                                                                      |                                                                                                                         | _                                                      | _               |                 |     |

| bit 15                  | -                                                                                                                                                                         |                                                                                                                                      |                                                                                                                         |                                                        |                 |                 | bit |

| R/W-0                   | R/W-0                                                                                                                                                                     | R/W-0                                                                                                                                | R/W-0                                                                                                                   | U-0                                                    | R/W-0           | R/W-0           | U-0 |

| C2TXIF                  | C1TXIF                                                                                                                                                                    | DMA7IF                                                                                                                               | DMA6IF                                                                                                                  | _                                                      | U2EIF           | U1EIF           | _   |

| bit 7                   |                                                                                                                                                                           |                                                                                                                                      |                                                                                                                         |                                                        |                 |                 | bit |

| Legend:                 |                                                                                                                                                                           |                                                                                                                                      |                                                                                                                         |                                                        |                 |                 |     |

| R = Readable            | bit                                                                                                                                                                       | W = Writable                                                                                                                         | bit                                                                                                                     | U = Unimplen                                           | nented bit, rea | id as '0'       |     |

| -n = Value at F         | POR                                                                                                                                                                       | '1' = Bit is set                                                                                                                     |                                                                                                                         | '0' = Bit is cle                                       | ared            | x = Bit is unkn | own |

| bit 7<br>bit 6<br>bit 5 | 1 = Interrupt r<br>0 = Interrupt r<br>C1TXIF: ECA<br>1 = Interrupt r<br>0 = Interrupt r<br>DMA7IF: DM                                                                     | request has occ<br>request has not<br>N1 Transmit D<br>request has occ<br>request has not<br>A Channel 7 Da                          | curred<br>occurred<br>ata Request I<br>curred<br>occurred                                                               | nterrupt Flag S<br>nterrupt Flag S<br>Complete Interru | tatus bit       | s bit           |     |

|                         |                                                                                                                                                                           | request has occ<br>request has not                                                                                                   |                                                                                                                         |                                                        |                 |                 |     |

|                         | 0 = Interrupt r<br>DMA6IF: DM.<br>1 = Interrupt r                                                                                                                         | request has not                                                                                                                      | : occurred<br>ata Transfer C<br>curred                                                                                  | Complete Interr                                        | upt Flag Statu  | s bit           |     |

| bit 4                   | 0 = Interrupt r<br>DMA6IF: DM<br>1 = Interrupt r<br>0 = Interrupt r                                                                                                       | equest has not<br>A Channel 6 Da<br>equest has occ                                                                                   | coccurred<br>ata Transfer C<br>curred<br>coccurred                                                                      | Complete Interr                                        | upt Flag Statu  | s bit           |     |

|                         | 0 = Interrupt r<br>DMA6IF: DM.<br>1 = Interrupt r<br>0 = Interrupt r<br>Unimplemen<br>U2EIF: UART<br>1 = Interrupt r                                                      | request has not<br>A Channel 6 Da<br>request has occ<br>request has not                                                              | coccurred<br>ata Transfer C<br>curred<br>coccurred<br>o'<br>ot Flag Status<br>curred                                    |                                                        | upt Flag Statu  | s bit           |     |

| bit 4<br>bit 3          | 0 = Interrupt r<br>DMA6IF: DM.<br>1 = Interrupt r<br>0 = Interrupt r<br>Unimplemen<br>U2EIF: UART<br>1 = Interrupt r<br>0 = Interrupt r<br>U1EIF: UART<br>1 = Interrupt r | equest has not<br>A Channel 6 Da<br>equest has occ<br>equest has not<br><b>ted:</b> Read as '0<br>2 Error Interrup<br>equest has occ | coccurred<br>ata Transfer C<br>curred<br>coccurred<br>of Flag Status<br>curred<br>coccurred<br>of Flag Status<br>curred | bit                                                    | upt Flag Statu  | s bit           |     |

#### REGISTER 7-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

### REGISTER 7-12: IEC2: INTERRUPT ENABLE CONTROL REGISTER 2 (CONTINUED)

| bit 2 | <b>C1RXIE:</b> ECAN1 Receive Data Ready Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled |

|-------|------------------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>SPI2IE:</b> SPI2 Event Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled               |

| bit 0 | <b>SPI2EIE:</b> SPI2 Error Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled              |

| U-0                           | R/W-1                                                       | R/W-0                                            | R/W-0          | U-0                            | R/W-1                | R/W-0           | R/W-0   |  |  |  |  |  |

|-------------------------------|-------------------------------------------------------------|--------------------------------------------------|----------------|--------------------------------|----------------------|-----------------|---------|--|--|--|--|--|

| —                             |                                                             | IC5IP<2:0>                                       |                | —                              |                      | IC4IP<2:0>      |         |  |  |  |  |  |

| bit 15                        |                                                             |                                                  |                |                                |                      |                 | bit 8   |  |  |  |  |  |

| U-0                           | R/W-1                                                       | R/W-0                                            | R/W-0          | U-0                            | R/W-1                | R/W-0           | R/W-0   |  |  |  |  |  |

|                               | N/W-1                                                       | IC3IP<2:0>                                       | FX/VV-0        |                                | N/W-1                | DMA3IP<2:0>     | N/ VV-U |  |  |  |  |  |

| bit 7                         |                                                             |                                                  |                |                                |                      |                 | bit 0   |  |  |  |  |  |

|                               |                                                             |                                                  |                |                                |                      |                 |         |  |  |  |  |  |

| Legend:                       | - h:4                                                       |                                                  | .:4            |                                | waa mata al hiit waa |                 |         |  |  |  |  |  |

| R = Readable<br>-n = Value at |                                                             | W = Writable k<br>'1' = Bit is set               | JIL            | 0 = Onimple<br>0' = Bit is cle | mented bit, rea      | x = Bit is unkn | own     |  |  |  |  |  |

|                               | TOR                                                         |                                                  |                |                                | arcu                 |                 | lowin   |  |  |  |  |  |

| bit 15                        | Unimpleme                                                   | nted: Read as '0                                 | )'             |                                |                      |                 |         |  |  |  |  |  |

| bit 14-12                     | IC5IP<2:0>: Input Capture Channel 5 Interrupt Priority bits |                                                  |                |                                |                      |                 |         |  |  |  |  |  |

|                               | 111 = Interr                                                | upt is priority 7 (h                             | nighest priori | ty interrupt)                  |                      |                 |         |  |  |  |  |  |

|                               | •                                                           |                                                  |                |                                |                      |                 |         |  |  |  |  |  |

|                               | •                                                           |                                                  |                |                                |                      |                 |         |  |  |  |  |  |

|                               |                                                             | upt is priority 1<br>upt source is disa          | abled          |                                |                      |                 |         |  |  |  |  |  |

| bit 11                        |                                                             | nted: Read as '0                                 |                |                                |                      |                 |         |  |  |  |  |  |

| bit 10-8                      | IC4IP<2:0>: Input Capture Channel 4 Interrupt Priority bits |                                                  |                |                                |                      |                 |         |  |  |  |  |  |

|                               | 111 = Interrupt is priority 7 (highest priority interrupt)  |                                                  |                |                                |                      |                 |         |  |  |  |  |  |

|                               | •                                                           |                                                  |                |                                |                      |                 |         |  |  |  |  |  |

|                               | •                                                           |                                                  |                |                                |                      |                 |         |  |  |  |  |  |

|                               |                                                             | upt is priority 1                                | a la d         |                                |                      |                 |         |  |  |  |  |  |

| bit 7                         |                                                             | upt source is disa<br><b>nted:</b> Read as '0    |                |                                |                      |                 |         |  |  |  |  |  |

| bit 6-4                       | -                                                           | Input Capture C                                  |                | errunt Priority h              | nite                 |                 |         |  |  |  |  |  |

|                               |                                                             | upt is priority 7 (h                             |                |                                |                      |                 |         |  |  |  |  |  |

|                               | •                                                           |                                                  | 5 1            | 5 17                           |                      |                 |         |  |  |  |  |  |

|                               | •                                                           |                                                  |                |                                |                      |                 |         |  |  |  |  |  |

|                               | 001 = Interr                                                | upt is priority 1                                |                |                                |                      |                 |         |  |  |  |  |  |

|                               |                                                             | upt source is disa                               |                |                                |                      |                 |         |  |  |  |  |  |

| bit 3                         | -                                                           | nted: Read as '0                                 |                |                                |                      | 10 L 10 L       |         |  |  |  |  |  |

| bit 2-0                       |                                                             | <b>0&gt;:</b> DMA Channe<br>upt is priority 7 (h |                | -                              | e Interrupt Pric     | ority bits      |         |  |  |  |  |  |

|                               | •                                                           |                                                  | lighest phon   | iy interrupt)                  |                      |                 |         |  |  |  |  |  |

|                               | •                                                           |                                                  |                |                                |                      |                 |         |  |  |  |  |  |

|                               | •                                                           |                                                  |                |                                |                      |                 |         |  |  |  |  |  |

|                               | 001 = Interr                                                | upt is priority 1                                |                |                                |                      |                 |         |  |  |  |  |  |

#### REGISTER 7-24: IPC9: INTERRUPT PRIORITY CONTROL REGISTER 9

### REGISTER 8-7: DMACS0: DMA CONTROLLER STATUS REGISTER 0 (CONTINUED)

| bit 3 | <b>XWCOL3:</b> Channel 3 DMA RAM Write Collision Flag bit<br>1 = Write collision detected<br>0 = No write collision detected                          |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | <ul> <li>XWCOL2: Channel 2 DMA RAM Write Collision Flag bit</li> <li>1 = Write collision detected</li> <li>0 = No write collision detected</li> </ul> |

| bit 1 | <b>XWCOL1:</b> Channel 1 DMA RAM Write Collision Flag bit<br>1 = Write collision detected<br>0 = No write collision detected                          |

| bit 0 | <b>XWCOL0:</b> Channel 0 DMA RAM Write Collision Flag bit<br>1 = Write collision detected<br>0 = No write collision detected                          |

### 15.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual", Section 13. "Output Compare" (DS70209), which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The output compare module can select either Timer2 or Timer3 for its time base. The module compares the value of the timer with the value of one or two Compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the Compare register value. The output compare module generates either a single output pulse, or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events.

The output compare module has multiple operating modes:

- Active-Low One-Shot mode

- Active-High One-Shot mode

- Toggle mode

- · Delayed One-Shot mode

- Continuous Pulse mode

- PWM mode without Fault Protection

- PWM mode with Fault Protection

#### FIGURE 15-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

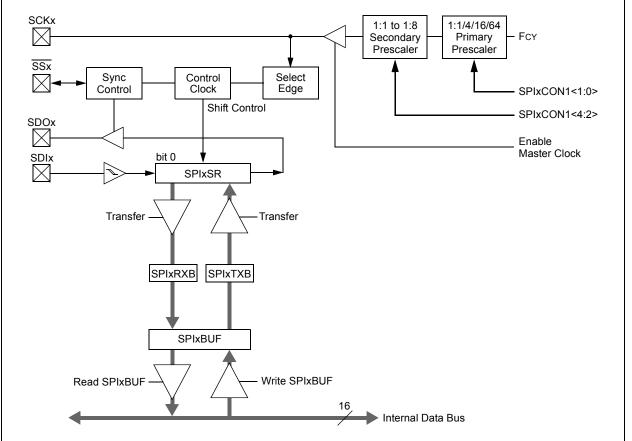

### 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual", Section 18. "Serial Peripheral Interface (SPI)" (DS70206), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, Analog-to-Digital converters, etc. The SPI module is compatible with SPI and SIOP from Motorola<sup>®</sup>.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers will follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 or SPI2 module.

Each SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates various status conditions.

The serial interface consists of 4 pins: SDIx (serial data input), SDOx (serial data output), SCKx (shift clock input or output), and SSx (active-low slave select).

In Master mode operation, SCK is a clock output but in Slave mode, it is a clock input.

© 2009-2012 Microchip Technology Inc.

### FIGURE 16-1: SPI MODULE BLOCK DIAGRAM

#### REGISTER 19-14: CIBUFPNT3: ECAN™ MODULE FILTER 8-11 BUFFER POINTER REGISTER

| R/W-0         | R/W-0                          | R/W-0                                                   | R/W-0                        | R/W-0                   | R/W-0 | R/W-0          | R/W-0 |

|---------------|--------------------------------|---------------------------------------------------------|------------------------------|-------------------------|-------|----------------|-------|

|               | F11BF                          | °<3:0>                                                  |                              |                         | F10B  | P<3:0>         |       |

| bit 15        |                                |                                                         |                              |                         |       |                | bit 8 |

|               |                                |                                                         |                              |                         |       |                |       |

| R/W-0         | R/W-0                          | R/W-0                                                   | R/W-0                        | R/W-0                   | R/W-0 | R/W-0          | R/W-0 |

|               | F9BP                           | <3:0>                                                   |                              |                         | F8BF  | P<3:0>         |       |

| bit 7         |                                |                                                         |                              |                         |       |                | bit ( |

|               |                                |                                                         |                              |                         |       |                |       |

| Legend:       |                                |                                                         |                              |                         |       |                |       |

| R = Readable  |                                | W = Writable                                            |                              | U = Unimpleme           |       |                |       |

| -n = Value at | POR                            | '1' = Bit is set                                        |                              | '0' = Bit is cleare     | ed    | x = Bit is unk | nown  |

| bit 15-12     | 1111 = Filter                  | : RX Buffer Wri<br>hits received ir<br>hits received ir | n RX FIFO bi                 | uffer                   |       |                |       |

|               |                                |                                                         |                              |                         |       |                |       |

|               | •                              |                                                         |                              |                         |       |                |       |

|               |                                | hits received ir hits received ir                       |                              |                         |       |                |       |

| bit 11-8      | 1111 = Filter                  | : RX Buffer Wri<br>hits received ir<br>hits received ir | n RX FIFO bi                 | uffer                   |       |                |       |

|               | •                              |                                                         |                              |                         |       |                |       |

|               | •                              |                                                         |                              |                         |       |                |       |

|               | •                              |                                                         |                              |                         |       |                |       |

|               |                                | hits received ir hits received ir                       |                              |                         |       |                |       |

| bit 7-4       | 1111 = Filter                  | RX Buffer Writt<br>hits received in<br>hits received in | n RX FIFO bi                 | uffer                   |       |                |       |

|               | •                              |                                                         |                              |                         |       |                |       |

|               | •                              |                                                         |                              |                         |       |                |       |

|               |                                | hits received ir hits received ir                       |                              |                         |       |                |       |

| bit 3-0       | F8BP<3:0>:<br>1111 = Filter    | RX Buffer Writt<br>hits received ir<br>hits received ir | en when Filten<br>RX FIFO be | er 8 Hits bits<br>uffer |       |                |       |

|               | •                              |                                                         |                              |                         |       |                |       |

|               | •                              |                                                         |                              |                         |       |                |       |

|               | 0001 = Filter<br>0000 = Filter | hits received in                                        |                              |                         |       |                |       |

| Bit Field | Register | RTSP<br>Effect | Description                                                                                                                                                                                                                                                               |

|-----------|----------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSS<2:0>  | FSS      | Immediate      | Secure Segment Program Flash Code Protection Size<br>(FOR 128K and 256K DEVICES)<br>x11 = No Secure program Flash segment                                                                                                                                                 |

|           |          |                | Secure space is 8K IW less BS<br>110 = Standard security; secure program Flash segment starts at End of<br>BS, ends at 0x003FFE<br>010 = High security; secure program Flash segment starts at End of BS,<br>ends at 0x003FFE                                             |

|           |          |                | Secure space is 16K IW less BS<br>101 = Standard security; secure program Flash segment starts at End of<br>BS, ends at 0x007FFE<br>001 = High security; secure program Flash segment starts at End of BS,<br>ends at 0x007FFE                                            |

|           |          |                | Secure space is 32K IW less BS<br>100 = Standard security; secure program Flash segment starts at End of<br>BS, ends at 0x00FFFE<br>000 = High security; secure program Flash segment starts at End of BS,<br>ends at 0x00FFFE                                            |

|           |          |                | (FOR 64K DEVICES)<br>x11 = No Secure program Flash segment                                                                                                                                                                                                                |

|           |          |                | Secure space is 4K IW less BS<br>110 = Standard security; secure program Flash segment starts at End of<br>BS, ends at 0x001FFE<br>010 = High security; secure program Flash segment starts at End of BS,<br>ends at 0x001FFE                                             |

|           |          |                | Secure space is 8K IW less BS<br>101 = Standard security; secure program Flash segment starts at End of<br>BS, ends at 0x003FFE<br>001 = High security; secure program Flash segment starts at End of BS,<br>ends at 0x003FFE                                             |

|           |          |                | Secure space is 16K IW less BS<br>100 = Standard security; secure program Flash segment starts at End of<br>BS, ends at 0x007FFE<br>000 = High security; secure program Flash segment starts at End of BS,<br>ends at 0x007FFE                                            |

| RSS<1:0>  | FSS      | Immediate      | Secure Segment RAM Code Protection<br>11 = No Secure RAM defined<br>10 = Secure RAM is 256 Bytes less BS RAM<br>01 = Secure RAM is 2048 Bytes less BS RAM<br>00 = Secure RAM is 4096 Bytes less BS RAM                                                                    |

| GSS<1:0>  | FGS      | Immediate      | General Segment Code-Protect bit<br>11 = User program memory is not code-protected<br>10 = Standard Security; general program Flash segment starts at End of<br>SS, ends at EOM<br>0x = High Security; general program Flash segment starts at End of ESS,<br>ends at EOM |

| GWRP      | FGS      | Immediate      | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                         |

#### TABLE 21-2: CONFIGURATION BITS DESCRIPTION (CONTINUED)

#### 21.5 JTAG Interface

PIC24HJXXXGPX06A/X08A/X10A devices implement a JTAG interface, which supports boundary scan device testing, as well as in-circuit programming. Detailed information on the interface will be provided in future revisions of the document.

Note: For further information, refer to the dsPIC33F/PIC24H Family Reference Manual", Section 24. "Programming and Diagnostics" (DS70207), which is available from the Microchip web site (www.microchip.com).

#### 21.6 Code Protection and CodeGuard<sup>™</sup> Security

The PIC24H product families offer advanced implementation of CodeGuard<sup>™</sup> Security. CodeGuard Security enables multiple parties to securely share resources (memory, interrupts and peripherals) on a single chip. This feature helps protect individual Intellectual Property in collaborative system designs.

When coupled with software encryption libraries, CodeGuard Security can be used to securely update Flash even when multiple IP are resident on the single chip. The code protection features vary depending on the actual PIC24H implemented. The following sections provide an overview these features.

The code protection features are controlled by the Configuration registers: FBS, FSS and FGS.

Note: For further information, refer to the "dsPIC33F/PIC24H Family Reference Manual", Section 23. "CodeGuard™ Security" (DS70239), which is available from the Microchip web site (www.microchip.com).

#### 21.7 In-Circuit Serial Programming Programming Capability

PIC24HJXXXGPX06A/X08A/X10A family digital signal controllers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming sequence. This allows customers to manufacture boards with unprogrammed devices and then program the digital signal controller just before shipping the product. This also allows the most recent firmware or a custom firmware, to be programmed. Please refer to the "dsPIC33F/PIC24H Flash Programming Specification" (DS70152) document for details about ICSP programming capability.

Any one out of three pairs of programming clock/data pins may be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

#### 21.8 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3 is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx (Emulation/Debug Clock) and PGEDx (Emulation/Debug Data) pin functions.

Any one out of three pairs of debugging clock/data pins may be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- · PGEC3 and PGED3

To use the in-circuit debugger function of the device, the design must implement ICSP programming capability connections to MCLR, VDD, VSS and the PGEDx/ PGECx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

#### TABLE 24-28: SPIx MAXIMUM DATA/CLOCK RATE SUMMARY

| AC CHARAG            | CTERISTICS                     |             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |     |     |  |

|----------------------|--------------------------------|-------------|-------------------------------------------------------|-----|-----|-----|--|

| Maximum<br>Data Rate | Transmit Only Transmit/Receive |             | Slave<br>Transmit/Receive<br>(Full-Duplex)            | CKE | СКР | SMP |  |

| 15 MHz               | Table 24-29                    |             | —                                                     | 0,1 | 0,1 | 0,1 |  |

| 10 MHz               | —                              | Table 24-30 | —                                                     | 1   | 0,1 | 1   |  |

| 10 MHz               | —                              | Table 24-31 | —                                                     | 0   | 0,1 | 1   |  |

| 15 MHz               | —                              | —           | Table 24-32                                           | 1   | 0   | 0   |  |

| 11 MHz               | —                              | —           | Table 24-33                                           | 1   | 1   | 0   |  |

| 15 MHz               | _                              | _           | Table 24-34                                           | 0   | 1   | 0   |  |

| 11 MHz               |                                |             | Table 24-35                                           | 0   | 0   | 0   |  |

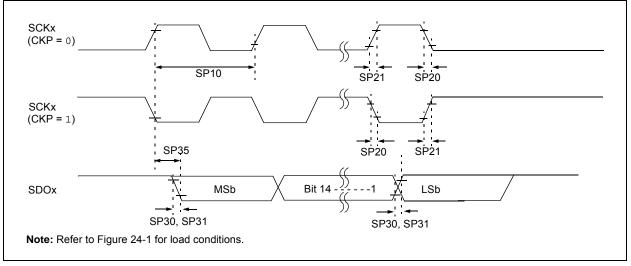

#### FIGURE 24-9: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY CKE = 0) TIMING CHARACTERISTICS

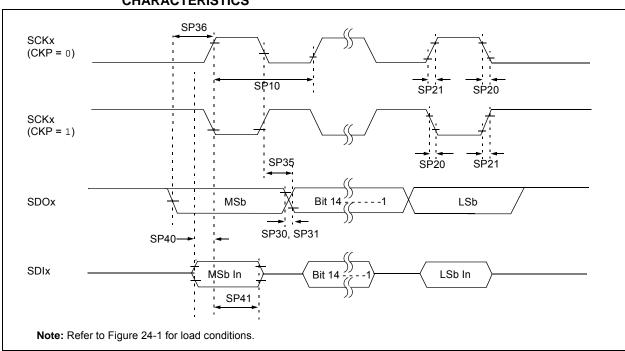

### FIGURE 24-11: SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = X, SMP = 1) TIMING CHARACTERISTICS

### TABLE 24-30:SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING<br/>REQUIREMENTS

| AC CHARACTERISTICS |                       |                                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                    |     |       |                                      |

|--------------------|-----------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------------------------|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                 | Min                                                                                                                                                                                                                                                                                     | Тур <sup>(2)</sup> | Max | Units | Conditions                           |

| SP10               | TscP                  | Maximum SCK Frequency                         | _                                                                                                                                                                                                                                                                                       | _                  | 10  | MHz   | See Note 3                           |

| SP20               | TscF                  | SCKx Output Fall Time                         | _                                                                                                                                                                                                                                                                                       | —                  |     | ns    | See parameter DO32 and <b>Note 4</b> |

| SP21               | TscR                  | SCKx Output Rise Time                         | —                                                                                                                                                                                                                                                                                       | —                  | _   | ns    | See parameter DO31 and <b>Note 4</b> |

| SP30               | TdoF                  | SDOx Data Output Fall Time                    | —                                                                                                                                                                                                                                                                                       | —                  | _   | ns    | See parameter DO32 and <b>Note 4</b> |

| SP31               | TdoR                  | SDOx Data Output Rise Time                    | —                                                                                                                                                                                                                                                                                       | _                  | —   | ns    | See parameter DO31 and <b>Note 4</b> |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge     | —                                                                                                                                                                                                                                                                                       | 6                  | 20  | ns    | _                                    |

| SP36               | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to<br>First SCKx Edge  | 30                                                                                                                                                                                                                                                                                      | —                  |     | ns    | _                                    |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 30                                                                                                                                                                                                                                                                                      | _                  |     | ns    | _                                    |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge  | 30                                                                                                                                                                                                                                                                                      | —                  | —   | ns    | —                                    |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

- **3:** The minimum clock period for SCKx is 100 ns. The clock generated in Master mode must not violate this specification.

- **4:** Assumes 50 pF load on all SPIx pins.

NOTES:

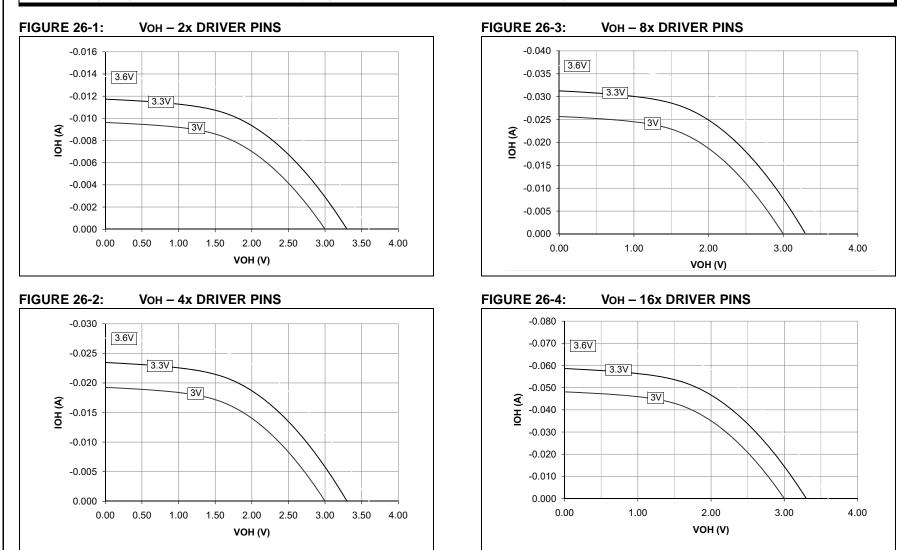

### 26.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS

Note: The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

PIC24HJXXXGPX06A/X08A/X10A

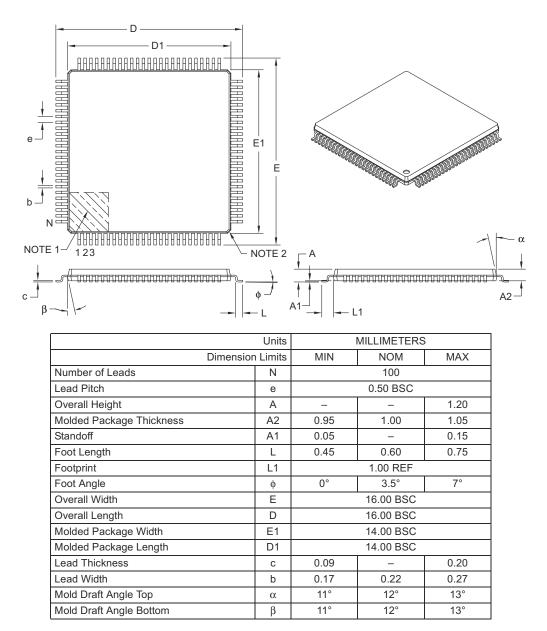

#### 100-Lead Plastic Thin Quad Flatpack (PF) – 14x14x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-110B