Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 18x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp306a-e-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

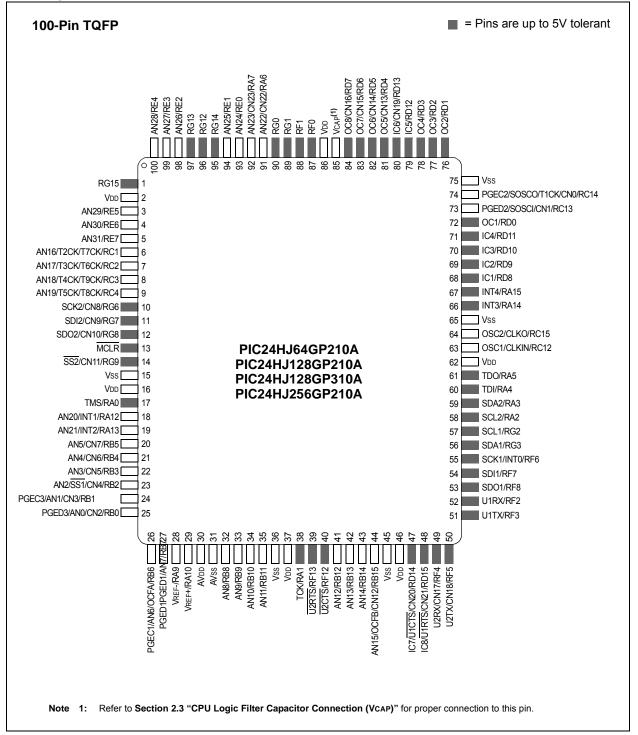

## Pin Diagrams (Continued)

### TABLE 4-24: PORTA REGISTER MAP<sup>(1)</sup>

|           |      |         |         |         |         |        | -       | -      |       |        | -      |        |        |        |        |        |        |               |

|-----------|------|---------|---------|---------|---------|--------|---------|--------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10  | Bit 9  | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| TRISA     | 02C0 | TRISA15 | TRISA14 | TRISA13 | TRISA12 | —      | TRISA10 | TRISA9 | -     | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | F6FF          |

| PORTA     | 02C2 | RA15    | RA14    | RA13    | RA12    | _      | RA10    | RA9    | _     | RA7    | RA6    | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx          |

| LATA      | 02C4 | LATA15  | LATA14  | LATA13  | LATA12  | _      | LATA10  | LATA9  | _     | LATA7  | LATA6  | LATA5  | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | xxxx          |

| ODCA      | 06C0 | ODCA15  | ODCA14  | _       | _       |        | _       | _      | -     |        |        | ODCA5  | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

## TABLE 4-25: PORTB REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB     | 02C6 | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB     | 02C8 | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB      | 02CA | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

# TABLE 4-26: PORTC REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|---------|---------|---------|---------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|-------|---------------|

| TRISC     | 02CC | TRISC15 | TRISC14 | TRISC13 | TRISC12 | _      | _      | —     | _     | _     | _     |       | TRISC4 | TRISC3 | TRISC2 | TRISC1 | —     | F01E          |

| PORTC     | 02CE | RC15    | RC14    | RC13    | RC12    | _      | —      | _     | _     | _     | _     | —     | RC4    | RC3    | RC2    | RC1    | —     | xxxx          |

| LATC      | 02D0 | LATC15  | LATC14  | LATC13  | LATC12  | _      | _      | _     | _     | _     | _     | -     | LATC4  | LATC3  | LATC2  | LATC1  | —     | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

# TABLE 4-27: PORTD REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISD     | 02D2 | TRISD15 | TRISD14 | TRISD13 | TRISD12 | TRISD11 | TRISD10 | TRISD9 | TRISD8 | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | FFFF          |

| PORTD     | 02D4 | RD15    | RD14    | RD13    | RD12    | RD11    | RD10    | RD9    | RD8    | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | xxxx          |

| LATD      | 02D6 | LATD15  | LATD14  | LATD13  | LATD12  | LATD11  | LATD10  | LATD9  | LATD8  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | xxxx          |

| ODCD      | 06D2 | ODCD15  | ODCD14  | ODCD13  | ODCD12  | ODCD11  | ODCD10  | ODCD9  | ODCD8  | ODCD7  | ODCD6  | ODCD5  | ODCD4  | ODCD3  | ODCD2  | ODCD1  | ODCD0  | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

## REGISTER 7-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| U-0                 | U-0                                                                                                                 | R/W-0                            | U-0            | U-0              | U-0              | U-0             | R/W-0 |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------|------------------|------------------|-----------------|-------|--|--|

| —                   | —                                                                                                                   | DMA5IF                           | —              | —                | —                | —               | C2IF  |  |  |

| bit 15              |                                                                                                                     |                                  |                |                  |                  |                 | bit 8 |  |  |

|                     |                                                                                                                     |                                  |                |                  |                  |                 |       |  |  |

| R/W-0               | R/W-0                                                                                                               | R/W-0                            | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |

| C2RXIF              | INT4IF                                                                                                              | INT3IF                           | T9IF           | T8IF             | MI2C2IF          | SI2C2IF         | T7IF  |  |  |

| bit 7               |                                                                                                                     |                                  |                |                  |                  |                 | bit 0 |  |  |

| <b>F</b>            |                                                                                                                     |                                  |                |                  |                  |                 |       |  |  |

| Legend:             |                                                                                                                     |                                  |                |                  |                  |                 |       |  |  |

| R = Readable        |                                                                                                                     | W = Writable                     |                | -                | nented bit, reac |                 |       |  |  |

| -n = Value at F     | POR                                                                                                                 | '1' = Bit is set                 |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |

|                     |                                                                                                                     | tod. Dood oo (                   | 0'             |                  |                  |                 |       |  |  |

| bit 15-14<br>bit 13 | -                                                                                                                   | ted: Read as '                   |                | omploto Intorr   | unt Elog Statua  | hit             |       |  |  |

| DIL 13              | <b>DMA5IF:</b> DMA Channel 5 Data Transfer Complete Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                                  |                |                  |                  |                 |       |  |  |

|                     |                                                                                                                     | equest has not                   |                |                  |                  |                 |       |  |  |

| bit 12-9            | Unimplemen                                                                                                          | ted: Read as '                   | 0'             |                  |                  |                 |       |  |  |

| bit 8               | C2IF: ECAN2 Event Interrupt Flag Status bit                                                                         |                                  |                |                  |                  |                 |       |  |  |

|                     | 1 = Interrupt request has occurred                                                                                  |                                  |                |                  |                  |                 |       |  |  |

|                     | 0 = Interrupt request has not occurred                                                                              |                                  |                |                  |                  |                 |       |  |  |

| bit 7               | C2RXIF: ECAN2 Receive Data Ready Interrupt Flag Status bit                                                          |                                  |                |                  |                  |                 |       |  |  |

|                     | <ol> <li>I = Interrupt request has occurred</li> <li>Interrupt request has not occurred</li> </ol>                  |                                  |                |                  |                  |                 |       |  |  |

| bit 6               | •                                                                                                                   | nal Interrupt 4                  |                | t                |                  |                 |       |  |  |

|                     |                                                                                                                     | equest has oc                    | •              | •                |                  |                 |       |  |  |

|                     |                                                                                                                     | equest has no                    |                |                  |                  |                 |       |  |  |

| bit 5               | INT3IF: Exter                                                                                                       | nal Interrupt 3                  | Flag Status bi | t                |                  |                 |       |  |  |

|                     |                                                                                                                     | equest has oc                    |                |                  |                  |                 |       |  |  |

| 1.11.4              | -                                                                                                                   | equest has not                   |                |                  |                  |                 |       |  |  |

| bit 4               |                                                                                                                     | Interrupt Flag Street            |                |                  |                  |                 |       |  |  |

|                     |                                                                                                                     | equest has occorrequest has not  |                |                  |                  |                 |       |  |  |

| bit 3               | -                                                                                                                   | Interrupt Flag                   |                |                  |                  |                 |       |  |  |

|                     | 1 = Interrupt r                                                                                                     | equest has oc                    | curred         |                  |                  |                 |       |  |  |

|                     | 0 = Interrupt r                                                                                                     | equest has not                   | occurred       |                  |                  |                 |       |  |  |

| bit 2               |                                                                                                                     | 2 Master Even                    | =              | ag Status bit    |                  |                 |       |  |  |

|                     |                                                                                                                     | equest has oc                    |                |                  |                  |                 |       |  |  |

| bit 1               | -                                                                                                                   | equest has not<br>2 Slave Events |                | Statua hit       |                  |                 |       |  |  |

| bit 1               |                                                                                                                     | equest has oc                    |                | J Status Dit     |                  |                 |       |  |  |

|                     |                                                                                                                     | equest has not                   |                |                  |                  |                 |       |  |  |

| bit 0               |                                                                                                                     | Interrupt Flag                   |                |                  |                  |                 |       |  |  |

|                     | 1 = Interrupt r                                                                                                     | equest has oc                    | curred         |                  |                  |                 |       |  |  |

|                     | 0 = Interrupt r                                                                                                     | equest has not                   | occurred       |                  |                  |                 |       |  |  |

| REGISTER 7-10: IE | EC0: INTERRUPT ENABLE CONTROL REGISTER 0 |

|-------------------|------------------------------------------|

|-------------------|------------------------------------------|

| U-0           | R/W-0           | R/W-0                            | R/W-0                   | R/W-0            | R/W-0            | R/W-0           | R/W-0           |

|---------------|-----------------|----------------------------------|-------------------------|------------------|------------------|-----------------|-----------------|

| —             | DMA1IE          | AD1IE                            | U1TXIE                  | U1RXIE           | SPI1IE           | SPI1EIE         | T3IE            |

| bit 15        |                 |                                  |                         |                  |                  |                 | bit 8           |

|               | <b>.</b>        | <b>D</b> 444 0                   | <b>DAA</b> ( <b>a</b> ) | <b>D</b> 444 0   | <b>D</b> 444 0   | DAVA            | <b>D</b> 444 0  |

| R/W-0         | R/W-0           | R/W-0                            | R/W-0                   | R/W-0            | R/W-0            | R/W-0           | R/W-0           |

| T2IE<br>bit 7 | OC2IE           | IC2IE                            | DMA0IE                  | T1IE             | OC1IE            | IC1IE           | INTOIE<br>bit C |

|               |                 |                                  |                         |                  |                  |                 |                 |

| Legend:       |                 |                                  |                         |                  |                  |                 |                 |

| R = Readable  | e bit           | W = Writable                     | bit                     | U = Unimpler     | mented bit, read | d as '0'        |                 |

| -n = Value at | POR             | '1' = Bit is se                  | t                       | '0' = Bit is cle | ared             | x = Bit is unkn | own             |

|               |                 |                                  |                         |                  |                  |                 |                 |

| bit 15        | -               | ted: Read as                     |                         |                  |                  |                 |                 |

| bit 14        |                 |                                  |                         | Complete Interr  | rupt Enable bit  |                 |                 |

|               |                 | request enable<br>request not en |                         |                  |                  |                 |                 |

| bit 13        | •               | •                                |                         | rupt Enable bit  |                  |                 |                 |

|               |                 | request enable                   |                         |                  |                  |                 |                 |

|               | -               | request not en                   |                         |                  |                  |                 |                 |

| bit 12        |                 | RT1 Transmitte                   |                         | able bit         |                  |                 |                 |

|               | •               | request enable<br>request not en |                         |                  |                  |                 |                 |

| bit 11        | -               | RT1 Receiver I                   |                         | le bit           |                  |                 |                 |

|               |                 | request enable                   | •                       |                  |                  |                 |                 |

|               | 0 = Interrupt r | request not en                   | abled                   |                  |                  |                 |                 |

| bit 10        |                 | Event Interrup                   |                         |                  |                  |                 |                 |

|               |                 | request enable<br>request not en |                         |                  |                  |                 |                 |

| bit 9         | -               | 1 Error Interru                  |                         |                  |                  |                 |                 |

| bit o         |                 | request enable                   | •                       |                  |                  |                 |                 |

|               | 0 = Interrupt r | request not en                   | abled                   |                  |                  |                 |                 |

| bit 8         |                 | Interrupt Enab                   |                         |                  |                  |                 |                 |

|               |                 | request enable<br>request not en |                         |                  |                  |                 |                 |

| bit 7         | •               | Interrupt Enab                   |                         |                  |                  |                 |                 |

| bit i         |                 | request enable                   |                         |                  |                  |                 |                 |

|               |                 | request not en                   |                         |                  |                  |                 |                 |

| bit 6         | OC2IE: Outpu    | ut Compare Cl                    | nannel 2 Interr         | upt Enable bit   |                  |                 |                 |

|               |                 | request enable                   |                         |                  |                  |                 |                 |

| hit E         | •               | request not en                   |                         | Enabla bit       |                  |                 |                 |

| bit 5         | -               | Capture Chanr<br>request enable  |                         |                  |                  |                 |                 |

|               | •               | request not en                   |                         |                  |                  |                 |                 |

| bit 4         | DMA0IE: DM      | A Channel 0 E                    | ata Transfer (          | Complete Interr  | upt Enable bit   |                 |                 |

|               |                 | request enable                   |                         |                  |                  |                 |                 |

|               | 0 = Interrupt r | request not en                   | abled                   |                  |                  |                 |                 |

| 1.11.0        | •               | •                                |                         |                  |                  |                 |                 |

| bit 3         | T1IE: Timer1    | Interrupt Enab                   | ole bit                 |                  |                  |                 |                 |

| U-0           | R/W-1             | R/W-0                                   | R/W-0          | U-0               | R/W-1            | R/W-0           | R/W-0 |

|---------------|-------------------|-----------------------------------------|----------------|-------------------|------------------|-----------------|-------|

| —             |                   | T2IP<2:0>                               |                | _                 |                  | OC2IP<2:0>      |       |

| bit 15        |                   |                                         |                |                   |                  |                 | bit 8 |

| U-0           | R/W-1             | R/W-0                                   | R/W-0          | U-0               | R/W-1            | R/W-0           | R/W-0 |

| _             |                   | IC2IP<2:0>                              |                | -                 |                  | DMA0IP<2:0>     |       |

| bit 7         |                   |                                         |                |                   |                  |                 | bit 0 |

| Legend:       |                   |                                         |                |                   |                  |                 |       |

| R = Readable  | e bit             | W = Writable I                          | oit            | U = Unimple       | mented bit, re   | ad as '0'       |       |

| -n = Value at | POR               | '1' = Bit is set                        |                | '0' = Bit is cle  | eared            | x = Bit is unkn | own   |

| bit 15        | Unimpleme         | ented: Read as 'o                       | )'             |                   |                  |                 |       |

| bit 14-12     | T2IP<2:0>:        | Timer2 Interrupt                        | Priority bits  |                   |                  |                 |       |

|               | 111 = Interr      | upt is priority 7 (ł                    | nighest priori | ty interrupt)     |                  |                 |       |

|               | •                 |                                         |                |                   |                  |                 |       |

|               | •                 |                                         |                |                   |                  |                 |       |

|               |                   | upt is priority 1                       |                |                   |                  |                 |       |

| L:1 44        |                   | upt source is disa                      |                |                   |                  |                 |       |

| bit 11        | -                 | ented: Read as '(                       |                | Latorrupt Drig    | ritu hita        |                 |       |

| bit 10-8      |                   | : Output Compa<br>upt is priority 7 (I  |                | -                 | ity bits         |                 |       |

|               | •                 |                                         | lightest phon  | ty interrupt)     |                  |                 |       |

|               | •                 |                                         |                |                   |                  |                 |       |

|               | •<br>001 = Interr | upt is priority 1                       |                |                   |                  |                 |       |

|               |                   | upt source is disa                      | abled          |                   |                  |                 |       |

| bit 7         | Unimpleme         | nted: Read as '0                        | )'             |                   |                  |                 |       |

| bit 6-4       | IC2IP<2:0>:       | : Input Capture C                       | hannel 2 Inte  | errupt Priority b | oits             |                 |       |

|               | 111 = Interr      | upt is priority 7 (h                    | nighest priori | ty interrupt)     |                  |                 |       |

|               | •                 |                                         |                |                   |                  |                 |       |

|               | •                 |                                         |                |                   |                  |                 |       |

|               |                   | upt is priority 1                       |                |                   |                  |                 |       |

|               |                   | upt source is disa                      |                |                   |                  |                 |       |

| bit 3         | -                 | ented: Read as '0                       |                |                   |                  |                 |       |

| bit 2-0       |                   | 0>: DMA Channe                          |                |                   | e Interrupt Pric | ority bits      |       |

|               | 111 = Interr<br>• | upt is priority 7 (h                    | lignest priori | ty interrupt)     |                  |                 |       |

|               | •                 |                                         |                |                   |                  |                 |       |

|               | •                 | and in and the d                        |                |                   |                  |                 |       |

|               |                   | upt is priority 1<br>upt source is disa | ahled          |                   |                  |                 |       |

|               |                   |                                         |                |                   |                  |                 |       |

## REGISTER 7-16: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

### REGISTER 7-29: IPC14: INTERRUPT PRIORITY CONTROL REGISTER 14

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0   | U-0       | U-0   |

|---------|-----|-----|-----|-----|-------|-----------|-------|

| —       | —   | —   | —   | —   | —     | —         | —     |

| bit 15  |     | •   |     |     |       |           | bit 8 |

|         |     |     |     |     |       |           |       |

| U-0     | U-0 | U-0 | U-0 | U-0 | R/W-1 | R/W-0     | R/W-0 |

| _       | —   | —   | —   | —   |       | C2IP<2:0> |       |

| bit 7   |     |     |     |     |       |           | bit 0 |

|         |     |     |     |     |       |           |       |

| Logond: |     |     |     |     |       |           |       |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-3 | Unimplemented: Read as '0' |

|----------|----------------------------|

|----------|----------------------------|

- C2IP<2:0>: ECAN2 Event Interrupt Priority bits

- 111 = Interrupt is priority 7 (highest priority interrupt)

- •

bit 2-0

- •

- 001 = Interrupt is priority 1

- 000 = Interrupt source is disabled

## REGISTER 7-30: IPC15: INTERRUPT PRIORITY CONTROL REGISTER 15

| U-0           | U-0           | U-0                | U-0             | U-0              | U-0               | U-0             | U-0   |

|---------------|---------------|--------------------|-----------------|------------------|-------------------|-----------------|-------|

| _             | —             | —                  | _               |                  | —                 | —               | _     |

| bit 15        |               |                    |                 |                  |                   |                 | bit 8 |

|               |               |                    |                 |                  |                   |                 |       |

| U-0           | R/W-1         | R/W-0              | R/W-0           | U-0              | U-0               | U-0             | U-0   |

| —             |               | DMA5IP<2:0>        |                 |                  | —                 | —               | —     |

| bit 7         |               |                    |                 |                  |                   |                 | bit 0 |

|               |               |                    |                 |                  |                   |                 |       |

| Legend:       |               |                    |                 |                  |                   |                 |       |

| R = Readable  | e bit         | W = Writable       | bit             | U = Unimpler     | nented bit, read  | as '0'          |       |

| -n = Value at | POR           | '1' = Bit is set   |                 | '0' = Bit is cle | ared              | x = Bit is unkr | nown  |

|               |               |                    |                 |                  |                   |                 |       |

| bit 15-7      | Unimplemer    | ted: Read as '     | 0'              |                  |                   |                 |       |

| bit 6-4       | DMA5IP<2:0    | >: DMA Chann       | el 5 Data Tra   | nsfer Complete   | Interrupt Priorit | y bits          |       |

|               | 111 = Interru | pt is priority 7 ( | highest priorit | y interrupt)     |                   |                 |       |

|               | •             |                    |                 |                  |                   |                 |       |

|               |               |                    |                 |                  |                   |                 |       |

001 = Interrupt is priority 1 000 = Interrupt source is disabled

bit 3-0 Unimplemented: Read as '0'

## REGISTER 7-32: IPC17: INTERRUPT PRIORITY CONTROL REGISTER 17

|                 | R/W-1              | R/W-0                | R/W-0           | U-0              | R/W-1            | R/W-0           | R/W-0 |

|-----------------|--------------------|----------------------|-----------------|------------------|------------------|-----------------|-------|

| —               |                    | C2TXIP<2:0>          |                 | —                |                  | C1TXIP<2:0>     |       |

| bit 15          |                    |                      |                 |                  |                  |                 | bit 8 |

|                 |                    |                      |                 |                  |                  |                 |       |

| U-0             | R/W-1              | R/W-0                | R/W-0           | U-0              | R/W-1            | R/W-0           | R/W-0 |

|                 |                    | DMA7IP<2:0>          |                 | —                |                  | DMA6IP<2:0>     |       |

| bit 7           |                    |                      |                 |                  |                  |                 | bit   |

| Legend:         |                    |                      |                 |                  |                  |                 |       |

| R = Readable    | bit                | W = Writable I       | bit             | U = Unimple      | mented bit, re   | ad as '0'       |       |

| -n = Value at F | POR                | '1' = Bit is set     |                 | '0' = Bit is cle | eared            | x = Bit is unkn | own   |

| bit 15          | Unimplemer         | nted: Read as 'd     | )'              |                  |                  |                 |       |

| bit 14-12       | -                  | >: ECAN2 Trans       |                 | quest Interrupt  | Priority bits    |                 |       |

|                 |                    | ipt is priority 7 (ł |                 |                  |                  |                 |       |

|                 | •                  |                      |                 |                  |                  |                 |       |

|                 | •                  |                      |                 |                  |                  |                 |       |

|                 | 001 = Interru      | pt is priority 1     |                 |                  |                  |                 |       |

|                 |                    | pt source is disa    | abled           |                  |                  |                 |       |

| bit 11          | Unimplemer         | nted: Read as 'd     | )'              |                  |                  |                 |       |

| bit 10-8        | C1TXIP<2:0         | >: ECAN1 Trans       | smit Data Rec   | quest Interrupt  | Priority bits    |                 |       |

|                 | 111 = Interru      | ipt is priority 7 (ł | nighest priorit | y interrupt)     |                  |                 |       |

|                 | •                  |                      |                 |                  |                  |                 |       |

|                 | •                  |                      |                 |                  |                  |                 |       |

|                 | •<br>001 = Interru | pt is priority 1     |                 |                  |                  |                 |       |

|                 |                    | ipt source is disa   | abled           |                  |                  |                 |       |

| bit 7           | Unimplemer         | nted: Read as '0     | )'              |                  |                  |                 |       |

| bit 6-4         | DMA7IP<2:0         | >: DMA Channe        | el 7 Data Trar  | nsfer Complete   | e Interrupt Pric | ority bits      |       |

|                 | 111 = Interru      | ıpt is priority 7 (ł | nighest priorit | y interrupt)     |                  |                 |       |

|                 | •                  |                      |                 |                  |                  |                 |       |

|                 | •                  |                      |                 |                  |                  |                 |       |

|                 | •<br>001 = Interru | pt is priority 1     |                 |                  |                  |                 |       |

|                 |                    | ipt source is disa   | abled           |                  |                  |                 |       |

| bit 3           |                    | nted: Read as '0     |                 |                  |                  |                 |       |

| bit 2-0         | DMA6IP<2:0         | >: DMA Channe        | el 6 Data Trar  | nsfer Complete   | e Interrupt Pric | ority bits      |       |

|                 |                    | ipt is priority 7 (h |                 | •                |                  | 5               |       |

|                 | •                  |                      |                 |                  |                  |                 |       |

|                 | •                  |                      |                 |                  |                  |                 |       |

|                 | •<br>001 = Interru | unt in priority 1    |                 |                  |                  |                 |       |

|                 |                    |                      |                 |                  |                  |                 |       |

# 10.0 POWER-SAVING FEATURES

- **Note 1:** This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196) of "dsPIC33F/PIC24H Familv the Reference Manual", which is available site the from Microchip web (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJXXXGPX06A/X08A/X10A devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. PIC24HJXXXGPX06A/X08A/X10A devices can manage power consumption in four different ways:

- · Clock frequency

- Instruction-based Sleep and Idle modes

- Software-controlled Doze mode

- Selective peripheral control in software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

## 10.1 Clock Frequency and Clock Switching

PIC24HJXXXGPX06A/X08A/X10A devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0** "Oscillator Configuration".

## 10.2 Instruction-Based Power-Saving Modes

PIC24HJXXXGPX06A/X08A/X10A devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembly syntax of the PWRSAV instruction is shown in Example 10-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

## 10.2.1 SLEEP MODE

Sleep mode has these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled

- The LPRC clock continues to run in Sleep mode if the WDT is enabled

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode

- Some device features or peripherals may continue to operate in Sleep mode. This includes items such as the input change notification on the I/O ports, or peripherals that use an external clock input. Any peripheral that requires the system clock source for its operation is disabled in Sleep mode.

The device will wake-up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- Any form of device Reset

- A WDT time-out

On wake-up from Sleep, the processor restarts with the same clock source that was active when Sleep mode was entered.

#### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE ; Put the device into SLEEP mode

PWRSAV #IDLE\_MODE ; Put the device into IDLE mode

## REGISTER 13-2: TyCON (T3CON, T5CON, T7CON OR T9CON) CONTROL REGISTER

| R/W-0              | U-0 | R/W-0                | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------------------|-----|----------------------|-----|-----|-----|-----|-------|

| TON <sup>(1)</sup> | —   | TSIDL <sup>(2)</sup> | _   | —   | —   | —   | —     |

| bit 15             |     |                      |     |     |     |     | bit 8 |

|                    |     |                      |     |     |     |     |       |

| U-0   | R/W-0                | R/W-0 | R/W-0    | U-0 | U-0 | R/W-0                | U-0   |

|-------|----------------------|-------|----------|-----|-----|----------------------|-------|

| _     | TGATE <sup>(1)</sup> | TCKPS | <1:0>(1) | —   | —   | TCS <sup>(1,3)</sup> | —     |

| bit 7 |                      |       |          |     |     |                      | bit 0 |

| Legend:    |                                                          |                                                             |                                   |                                     |

|------------|----------------------------------------------------------|-------------------------------------------------------------|-----------------------------------|-------------------------------------|

| R = Read   | able bit                                                 | W = Writable bit                                            | U = Unimplemented bit,            | read as '0'                         |

| -n = Value | at POR                                                   | '1' = Bit is set                                            | '0' = Bit is cleared              | x = Bit is unknown                  |

| bit 15     | 1 = Starts                                               | nery On bit <sup>(1)</sup><br>s 16-bit Timery               |                                   |                                     |

|            | •                                                        | s 16-bit Timery                                             |                                   |                                     |

| bit 14     | •                                                        | mented: Read as '0'                                         |                                   |                                     |

| bit 13     |                                                          | top in Idle Mode bit <sup>(2)</sup>                         |                                   |                                     |

|            |                                                          | ontinue module operation wh<br>nue module operation in Idle |                                   |                                     |

| bit 12-7   | Unimple                                                  | mented: Read as '0'                                         |                                   |                                     |

| bit 6      | TGATE:                                                   | Timery Gated Time Accumul                                   | ation Enable bit <sup>(1)</sup>   |                                     |

|            |                                                          | s ignored.                                                  |                                   |                                     |

| bit 5-4    | TCKPS<<br>11 = 1:25<br>10 = 1:64<br>01 = 1:8<br>00 = 1:1 |                                                             | escale Select bits <sup>(1)</sup> |                                     |

| bit 3-2    | Unimple                                                  | mented: Read as '0'                                         |                                   |                                     |

| bit 1      | TCS: Tim                                                 | nery Clock Source Select bit <sup>(</sup>                   | 1,3)                              |                                     |

|            |                                                          | nal clock from pin TyCK (on nal clock (Fcy)                 | the rising edge)                  |                                     |

| bit 0      | Unimple                                                  | mented: Read as '0'                                         |                                   |                                     |

| Note 1:    |                                                          | peration is enabled (T2CON-<br>set through T2CON.           | <3> = 1), these bits have no ef   | ffect on Timery operation; all time |

- 2: When 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

- 3: The TyCK pin is not available on all timers. Refer to the "Pin Diagrams" section for the available pins.

## **REGISTER 15-1:** OCxCON: OUTPUT COMPARE x CONTROL REGISTER (x = 1, 2)

| U-0    | U-0 | R/W-0  | U-0     | U-0    | U-0   | U-0      | U-0   |

|--------|-----|--------|---------|--------|-------|----------|-------|

| _      | —   | OCSIDL |         | —      | —     | —        | —     |

| bit 15 |     |        | •       |        |       |          | bit 8 |

|        |     |        |         |        |       |          |       |

| U-0    | U-0 | U-0    | R-0, HC | R/W-0  | R/W-0 | R/W-0    | R/W-0 |

|        | —   | —      | OCFLT   | OCTSEL |       | OCM<2:0> |       |

| bit 7  |     |        | •       |        |       |          | bit 0 |

|        |     |        |         |        |       |          |       |

| Legend:           | HC = Hardware Clearable bit |                           |                    |

|-------------------|-----------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared      | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                          |

|-----------|-------------------------------------------------------------------------------------|

| bit 13    | OCSIDL: Stop Output Compare in Idle Mode Control bit                                |

|           | 1 = Output Compare x halts in CPU Idle mode                                         |

|           | 0 = Output Compare x continues to operate in CPU Idle mode                          |

| bit 12-5  | Unimplemented: Read as '0'                                                          |

| bit 4     | OCFLT: PWM Fault Condition Status bit                                               |

|           | 1 = PWM Fault condition has occurred (cleared in hardware only)                     |

|           | 0 = No PWM Fault condition has occurred (this bit is only used when OCM<2:0> = 111) |

| bit 3     | OCTSEL: Output Compare Timer Select bit                                             |

|           | 1 = Timer3 is the clock source for Compare x                                        |

|           | 0 = Timer2 is the clock source for Compare x                                        |

| bit 2-0   | OCM<2:0>: Output Compare Mode Select bits                                           |

|           | 111 = PWM mode on OCx, Fault pin enabled                                            |

|           | 110 = PWM mode on OCx, Fault pin disabled                                           |

|           | 101 = Initialize OCx pin low, generate continuous output pulses on OCx pin          |

|           | 100 = Initialize OCx pin low, generate single output pulse on OCx pin               |

|           | 011 = Compare event toggles OCx pin                                                 |

|           | 010 = Initialize OCx pin high, compare event forces OCx pin low                     |

|           | 001 = Initialize OCx pin low, compare event forces OCx pin high                     |

|           | 000 = Output compare channel is disabled                                            |

# REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | <ul> <li>Start bit</li> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul>                                                               |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | Hardware set or clear when Start, Repeated Start or Stop detected.<br><b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)<br>1 = Read – indicates data transfer is output from slave          |

|       | 0 = Write - indicates data transfer is input to slaveHardware set or clear after reception of I2C device address byte.                                                                                                      |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                                                                                                         |

|       | <ul> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> </ul> |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                                                                                                        |

|       | <ul> <li>1 = Transmit in progress, I2CxTRN is full</li> <li>0 = Transmit complete, I2CxTRN is empty</li> <li>Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.</li> </ul>       |

### REGISTER 20-4: ADxCON4: ADCx CONTROL REGISTER 4

| U-0             | U-0 | U-0              | U-0 | U-0                                     | U-0              | U-0        | U-0   |

|-----------------|-----|------------------|-----|-----------------------------------------|------------------|------------|-------|

| —               | —   | —                | _   | —                                       | —                | —          | —     |

| bit 15          |     |                  |     |                                         |                  |            | bit 8 |

|                 |     |                  |     |                                         |                  |            |       |

| U-0             | U-0 | U-0              | U-0 | U-0                                     | R/W-0            | R/W-0      | R/W-0 |

| —               | _   | —                | _   | —                                       |                  | DMABL<2:0> |       |

| bit 7           |     |                  |     |                                         |                  |            | bit 0 |

|                 |     |                  |     |                                         |                  |            |       |

| Legend:         |     |                  |     |                                         |                  |            |       |

| R = Readable    | bit | W = Writable b   | bit | U = Unimplei                            | mented bit, read | d as '0'   |       |

| -n = Value at P | POR | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |                  |            | nown  |

#### bit 15-3 Unimplemented: Read as '0'

bit 2-0

DMABL<2:0>: Selects Number of DMA Buffer Locations per Analog Input bits

111 = Allocates 128 words of buffer to each analog input

110 = Allocates 64 words of buffer to each analog input

101 = Allocates 32 words of buffer to each analog input

100 = Allocates 16 words of buffer to each analog input

011 = Allocates 8 words of buffer to each analog input

010 = Allocates 4 words of buffer to each analog input

001 = Allocates 2 words of buffer to each analog input

000 = Allocates 1 word of buffer to each analog input

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax | Description                  | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|--------|-----------------|------------------------------|---------------|----------------|--------------------------|

| 66                 | TBLRDL               | TBLRDL | Ws,Wd           | Read Prog<15:0> to Wd        | 1             | 2              | None                     |

| 67                 | TBLWTH               | TBLWTH | Ws,Wd           | Write Ws<7:0> to Prog<23:16> | 1             | 2              | None                     |

| 68                 | TBLWTL               | TBLWTL | Ws,Wd           | Write Ws to Prog<15:0>       | 1             | 2              | None                     |

| 69                 | ULNK                 | ULNK   |                 | Unlink Frame Pointer         | 1             | 1              | None                     |

| 70                 | XOR                  | XOR    | f               | f = f .XOR. WREG             | 1             | 1              | N,Z                      |

|                    |                      | XOR    | f,WREG          | WREG = f .XOR. WREG          | 1             | 1              | N,Z                      |

|                    |                      | XOR    | #lit10,Wn       | Wd = lit10 .XOR. Wd          | 1             | 1              | N,Z                      |

|                    |                      | XOR    | Wb,Ws,Wd        | Wd = Wb .XOR. Ws             | 1             | 1              | N,Z                      |

|                    |                      | XOR    | Wb,#lit5,Wd     | Wd = Wb .XOR. lit5           | 1             | 1              | N,Z                      |

| 71                 | ZE                   | ZE     | Ws,Wnd          | Wnd = Zero-extend Ws         | 1             | 1              | C,Z,N                    |

## TABLE 22-2: INSTRUCTION SET OVERVIEW (CONTINUED)

## 23.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

## 23.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

## 23.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

## 23.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 23.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- · MPLAB IDE compatibility

## TABLE 24-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACI                      | ERISTICS                   |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                  |       |                                              |  |  |

|---------------------------------|----------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|----------------------------------------------|--|--|

| Parameter<br>No. <sup>(3)</sup> | Typical <sup>(2)</sup>     | Max  | Units                                                                                                                                                                                                                                                                                   | Units Conditions |       |                                              |  |  |

| Power-Down                      | Current (IPD) <sup>(</sup> | 1)   |                                                                                                                                                                                                                                                                                         |                  |       |                                              |  |  |

| DC60d                           | 50                         | 200  | μA                                                                                                                                                                                                                                                                                      | -40°C            |       |                                              |  |  |

| DC60a                           | 50                         | 200  | μA                                                                                                                                                                                                                                                                                      | +25°C            | 2.01/ | Base Power-Down Current <sup>(3)</sup>       |  |  |

| DC60b                           | 200                        | 500  | μA                                                                                                                                                                                                                                                                                      | +85°C            | 3.3V  | Base Power-Down Currents?                    |  |  |

| DC60c                           | 600                        | 1000 | μA                                                                                                                                                                                                                                                                                      | +125°C           |       |                                              |  |  |

| DC61d                           | 8                          | 13   | μA                                                                                                                                                                                                                                                                                      | -40°C            |       |                                              |  |  |

| DC61a                           | 10                         | 15   | μA                                                                                                                                                                                                                                                                                      | +25°C            | 2.21/ | Watabdag Timor Current: Alwor(3)             |  |  |

| DC61b                           | 12                         | 20   | μA                                                                                                                                                                                                                                                                                      | +85°C            | 3.3V  | Watchdog Timer Current: ∆IwDT <sup>(3)</sup> |  |  |

| DC61c                           | 13                         | 25   | μΑ                                                                                                                                                                                                                                                                                      | +125°C           |       |                                              |  |  |

Note 1: IPD (Sleep) current is measured as follows:

- CPU core is off, oscillator is configured in EC mode and external clock active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- CLKO is configured as an I/O input pin in the Configuration word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled, all peripheral modules except the ADC are disabled (PMDx bits are all '1's). The following ADC settings are enabled for each ADC module (ADCx) prior to executing the PWRSAV instruction: ADON = 1, VCFG = 1, AD12B = 1 and ADxMD = 0.

- VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to stand-by while the device is in Sleep mode)

- RTCC is disabled.

- JTAG is disabled

- 2: Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The Watchdog Timer Current is the additional current consumed when the WDT module is enabled. This current should be added to the base IPD current.

- 4: These currents are measured on the device containing the most memory in this family.

- 5: These parameters are characterized, but are not tested in manufacturing.

| AC CHA       |        | STICS                                                                     | (unless   | d Operati<br>otherwise<br>g tempera | e stated)<br>ature -4 | ł0°C ≤ Ta | <b>bV to 3.6V</b><br>≤ +85°C for Industrial<br>≤ +125°C for Extended |

|--------------|--------|---------------------------------------------------------------------------|-----------|-------------------------------------|-----------------------|-----------|----------------------------------------------------------------------|

| Param<br>No. | Symbol | Characteristic                                                            | Min.      | Тур <sup>(2)</sup>                  | Max.                  | Units     | Conditions                                                           |

|              |        | Clock                                                                     | Paramete  | ers <sup>(1)</sup>                  |                       |           |                                                                      |

| AD50         | Tad    | ADC Clock Period                                                          | 117.6     |                                     |                       | ns        | _                                                                    |

| AD51         | tRC    | ADC Internal RC Oscillator<br>Period                                      | —         | 250                                 | _                     | ns        | —                                                                    |

|              |        | Con                                                                       | version R | ate                                 |                       |           |                                                                      |

| AD55         | tCONV  | Conversion Time                                                           |           | 14 Tad                              |                       | ns        | _                                                                    |

| AD56         | FCNV   | Throughput Rate                                                           | _         |                                     | 500                   | ksps      | _                                                                    |

| AD57         | TSAMP  | Sample Time                                                               | 3 Tad     |                                     |                       | _         | _                                                                    |

|              | •      | Timir                                                                     | g Parame  | ters                                |                       |           |                                                                      |

| AD60         | tPCS   | Conversion Start from Sample<br>Trigger <sup>(2)</sup>                    | 2.0 Tad   | —                                   | 3.0 Tad               |           | Auto convert trigger not selected                                    |

| AD61         | tPSS   | Sample Start from Setting Sample (SAMP) bit <sup>(2)</sup>                | 2.0 TAD   | —                                   | 3.0 Tad               |           | _                                                                    |

| AD62         | tcss   | Conversion Completion to<br>Sample Start (ASAM = $1$ ) <sup>(2)</sup>     | —         | 0.5 Tad                             | _                     | _         | _                                                                    |

| AD63         | tdpu   | Time to Stabilize Analog Stage<br>from ADC Off to ADC On <sup>(2,3)</sup> | _         |                                     | 20                    | μS        | _                                                                    |

# TABLE 24-42: ADC CONVERSION (12-BIT MODE) TIMING REQUIREMENTS

**Note 1:** Because the sample caps eventually loses charge, clock rates below 10 kHz may affect linearity performance, especially at elevated temperatures.

**2:** These parameters are characterized but not tested in manufacturing.

**3:** tDPU is the time required for the ADC module to stabilize when it is turned on (AD1CON1<ADON> = 1). During this time, the ADC result is indeterminate.

| CHARAG       | AC<br>CTERISTICS | Standard Operating Condition<br>Operating temperature -40°C |           | •   |     |       | -          |

|--------------|------------------|-------------------------------------------------------------|-----------|-----|-----|-------|------------|

| Param<br>No. | Symbol           | Characteristic                                              | Min       | Тур | Max | Units | Conditions |

|              | Clock Parameters |                                                             |           |     |     |       |            |

| HAD50        | TAD              | ADC Clock Period <sup>(1)</sup>                             | 147       |     |     | ns    | —          |

|              |                  | Con                                                         | version R | ate |     |       |            |

|              |                  | 001                                                         |           |     |     |       |            |

### TABLE 25-17: ADC CONVERSION (12-BIT MODE) TIMING REQUIREMENTS

Note 1: These parameters are characterized but not tested in manufacturing.

## TABLE 25-18: ADC CONVERSION (10-BIT MODE) TIMING REQUIREMENTS

| -            | AC<br>TERISTICS | Standard Operating Condition<br>Operating temperature -40°C |           |      |     |       | ed)        |

|--------------|-----------------|-------------------------------------------------------------|-----------|------|-----|-------|------------|

| Param<br>No. | Symbol          | Characteristic                                              | Min       | Тур  | Max | Units | Conditions |

|              |                 | Cloc                                                        | k Parame  | ters |     |       |            |