Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 18x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

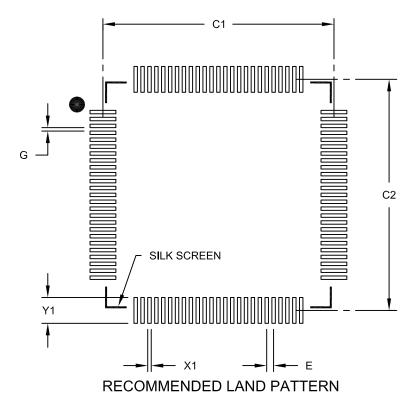

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp306a-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

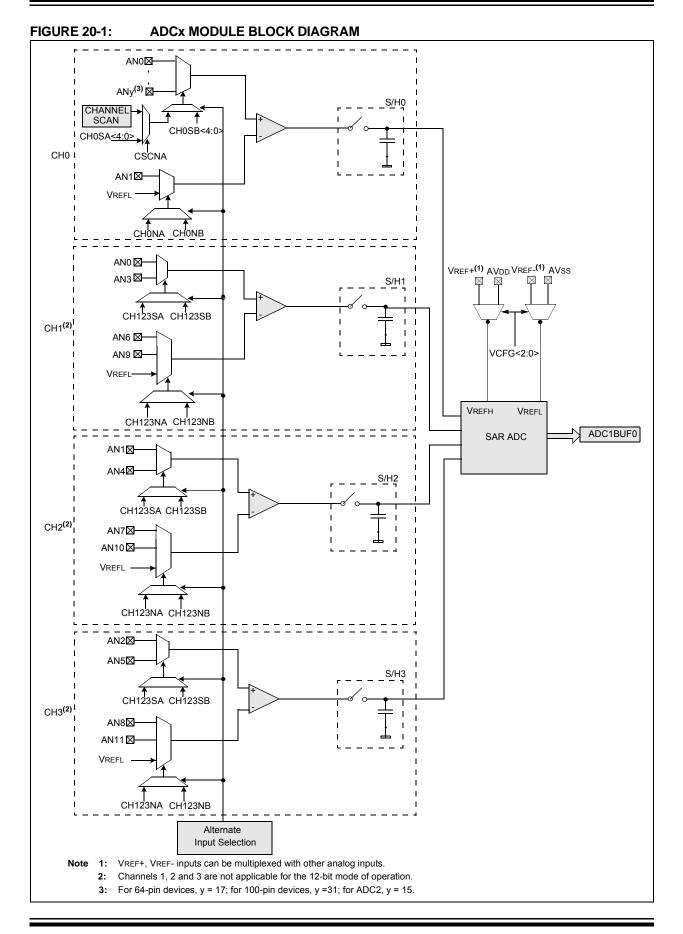

### TABLE 4-15: ADC1 REGISTER MAP

| File Name               | Addr          | Bit 15 | Bit 14    | Bit 13 | Bit 12  | Bit 11 | Bit 10    | Bit 9   | Bit 8    | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2     | Bit 1    | Bit 0   | All<br>Resets |

|-------------------------|---------------|--------|-----------|--------|---------|--------|-----------|---------|----------|----------|-----------|--------|--------|--------|-----------|----------|---------|---------------|

| ADC1BUF0                | 0300          |        |           |        |         |        |           |         | ADC Data | Buffer 0 |           |        |        |        |           |          |         | xxxx          |

| AD1CON1                 | 0320          | ADON   | _         | ADSIDL | ADDMABM | _      | AD12B     | FOR     | M<1:0>   | :        | SSRC<2:0> |        | _      | SIMSAM | ASAM      | SAMP     | DONE    | 0000          |

| AD1CON2                 | 0322          | ,      | VCFG<2:0> | >      |         |        | CSCNA     | CHP     | S<1:0>   | BUFS     | —         |        | SMPI   | <3:0>  |           | BUFM     | ALTS    | 0000          |

| AD1CON3                 | 0324          | ADRC   |           |        |         | S      | AMC<4:0>  |         |          |          |           |        | ADCS   | <7:0>  |           |          |         | 0000          |

| AD1CHS123               | 0326          | _      |           |        |         | _      | CH1231    | NB<1:0> | CH123SB  | —        | —         |        |        |        | CH123     | NA<1:0>  | CH123SA | 0000          |

| AD1CHS0                 | 0328          | CH0NB  |           |        |         | CI     | +0SB<4:0> | >       |          | CH0NA    | —         |        |        | C      | CH0SA<4:0 | )>       |         | 0000          |

| AD1PCFGH <sup>(1)</sup> | 032A          | PCFG31 | PCFG30    | PCFG29 | PCFG28  | PCFG27 | PCFG26    | PCFG25  | PCFG24   | PCFG23   | PCFG22    | PCFG21 | PCFG20 | PCFG19 | PCFG18    | PCFG17   | PCFG16  | 0000          |

| AD1PCFGL                | 032C          | PCFG15 | PCFG14    | PCFG13 | PCFG12  | PCFG11 | PCFG10    | PCFG9   | PCFG8    | PCFG7    | PCFG6     | PCFG5  | PCFG4  | PCFG3  | PCFG2     | PCFG1    | PCFG0   | 0000          |

| AD1CSSH(1)              | 032E          | CSS31  | CSS30     | CSS29  | CSS28   | CSS27  | CSS26     | CSS25   | CSS24    | CSS23    | CSS22     | CSS21  | CSS20  | CSS19  | CSS18     | CSS17    | CSS16   | 0000          |

| AD1CSSL                 | 0330          | CSS15  | CSS14     | CSS13  | CSS12   | CSS11  | CSS10     | CSS9    | CSS8     | CSS7     | CSS6      | CSS5   | CSS4   | CSS3   | CSS2      | CSS1     | CSS0    | 0000          |

| AD1CON4                 | 0332          | _      |           |        |         | _      |           |         | —        | —        | —         |        |        |        | -         | DMABL<2: | 0>      | 0000          |

| Reserved                | 0334-<br>033E | _      | _         |        | _       |        |           |         | _        | —        | _         |        | _      | _      | _         | _        | _       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: Not all ANx inputs are available on all devices. See the device pin diagrams for available ANx inputs.

### TABLE 4-16: ADC2 REGISTER MAP

| File Name | Addr          | Bit 15 | Bit 14    | Bit 13 | Bit 12  | Bit 11 | Bit 10   | Bit 9   | Bit 8    | Bit 7    | Bit 6    | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1    | Bit 0   | All<br>Resets |

|-----------|---------------|--------|-----------|--------|---------|--------|----------|---------|----------|----------|----------|-------|-------|--------|-------|----------|---------|---------------|

| ADC2BUF0  | 0340          |        |           |        |         |        |          |         | ADC Data | Buffer 0 |          |       |       |        |       |          |         | xxxx          |

| AD2CON1   | 0360          | ADON   | _         | ADSIDL | ADDMABM | _      | AD12B    | FORI    | VI<1:0>  | :        | SSRC<2:0 | >     | _     | SIMSAM | ASAM  | SAMP     | DONE    | 0000          |

| AD2CON2   | 0362          | Y      | VCFG<2:0> | >      | —       |        | CSCNA    | CHP     | S<1:0>   | BUFS     | —        |       | SMPI  | <3:0>  |       | BUFM     | ALTS    | 0000          |

| AD2CON3   | 0364          | ADRC   | _         | _      |         | S      | AMC<4:0> |         |          |          |          |       | ADC   | S<7:0> |       |          |         | 0000          |

| AD2CHS123 | 0366          | _      | _         | _      | _       | _      | CH123N   | NB<1:0> | CH123SB  | _        | _        | _     | _     | _      | CH123 | NA<1:0>  | CH123SA | 0000          |

| AD2CHS0   | 0368          | CH0NB  | _         | _      | _       |        | CH0S     | B<3:0>  |          | CH0NA    | _        | _     | _     |        | CH0S  | A<3:0>   |         | 0000          |

| Reserved  | 036A          | _      | _         | _      | _       | _      | _        | _       | _        | _        | _        | _     | _     | _      | _     | _        | _       | 0000          |

| AD2PCFGL  | 036C          | PCFG15 | PCFG14    | PCFG13 | PCFG12  | PCFG11 | PCFG10   | PCFG9   | PCFG8    | PCFG7    | PCFG6    | PCFG5 | PCFG4 | PCFG3  | PCFG2 | PCFG1    | PCFG0   | 0000          |

| Reserved  | 036E          | _      | _         | _      | _       | _      | _        | _       | _        | _        | _        | _     | _     | _      | _     | _        | _       | 0000          |

| AD2CSSL   | 0370          | CSS15  | CSS14     | CSS13  | CSS12   | CSS11  | CSS10    | CSS9    | CSS8     | CSS7     | CSS6     | CSS5  | CSS4  | CSS3   | CSS2  | CSS1     | CSS0    | 0000          |

| AD2CON4   | 0372          | _      | _         | _      | _       | _      | _        | _       | _        | _        | _        | _     | _     | _      | I     | DMABL<2: | 0>      | 0000          |

| Reserved  | 0374-<br>037E | —      | —         | —      | —       |        | —        |         | —        | _        | —        | —     | —     | —      | _     | —        | —       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

## 7.0 INTERRUPT CONTROLLER

- **Note 1:** This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 6. "Interrupts" (DS70184) of the "dsPIC33F/PIC24H Familv Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJXXXGPX06A/X08A/X10A interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the PIC24HJXXXGPX06A/X08A/X10A CPU. It has the following features:

- · Up to 8 processor exceptions and software traps

- 7 user-selectable priority levels

- Interrupt Vector Table (IVT) with up to 118 vectors

- A unique vector for each interrupt or exception source

- · Fixed priority within a specified user priority level

- Alternate Interrupt Vector Table (AIVT) for debug support

- Fixed interrupt entry and return latencies

### 7.1 Interrupt Vector Table

The Interrupt Vector Table (IVT) is shown in Figure 7-1. The IVT resides in program memory, starting at location 000004h. The IVT contains 126 vectors consisting of 8 nonmaskable trap vectors plus up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority; this priority is linked to their position in the vector table. All other things being equal, lower addresses have a higher natural priority. For example, the interrupt associated with vector 0 will take priority over interrupts at any other vector address.

PIC24HJXXXGPX06A/X08A/X10A devices implement up to 61 unique interrupts and 5 nonmaskable traps. These are summarized in Table 7-1 and Table 7-2.

### 7.1.1 ALTERNATE VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 7-1. Access to the AIVT is provided by the ALTIVT control bit (INTCON2<15>). If the ALTIVT bit is set, all interrupt and exception processes use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports debugging by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

### 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The PIC24HJXXXGPX06A/X08A/X10A device clears its registers in response to a Reset which forces the PC to zero. The digital signal controller then begins program execution at location 0x000000. The user programs a GOTO instruction at the Reset address which redirects program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

### REGISTER 7-13: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3

| R/W-0       R/W-0 <th< th=""><th>U-0</th><th>U-0</th><th>R/W-0</th><th>U-0</th><th>U-0</th><th>U-0</th><th>U-0</th><th>R/W-0</th></th<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | U-0       | U-0           | R/W-0           | U-0            | U-0            | U-0             | U-0      | R/W-0 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------|-----------------|----------------|----------------|-----------------|----------|-------|

| R/W-0       R/W-0 <th< td=""><td>—</td><td>—</td><td>DMA5IE</td><td>—</td><td>—</td><td>—</td><td>—</td><td>C2IE</td></th<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | —         | —             | DMA5IE          | —              | —              | —               | —        | C2IE  |

| C2RXIE       INT4IE       INT3IE       T9IE       T8IE       MI2C2IE       SI2C2IE       T7IE         bit 7       bit       bit       bit       bit       bit         segend:       R Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       bit         n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 13       DMASIE: DMA Channel 5 Data Transfer Complete Interrupt Enable bit       1       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0       = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0       = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0       = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0 = Interrupt request not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 15    |               |                 |                |                |                 |          | bit 8 |

| C2RXIE       INT4IE       INT3IE       T9IE       T8IE       MI2C2IE       SI2C2IE       T7IE         bit 7       bit       bit       bit       bit       bit         segend:       R Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       bit         n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 13       DMASIE: DMA Channel 5 Data Transfer Complete Interrupt Enable bit       1       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0       = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0       = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0       = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0 = Interrupt request not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |               |                 |                |                |                 |          |       |

| it 7       bit         cegend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 13       DMASIE: DMA Channel 5 Data Transfer Complete Interrupt Enable bit       1       Is interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request enabled       0       Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request enabled       0       Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request not enabled       0       Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-0     | R/W-0         | R/W-0           | R/W-0          | R/W-0          | R/W-0           | R/W-0    | R/W-0 |

| segend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'       i'' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 13       DMASIE: DMA Channel 5 Data Transfer Complete Interrupt Enable bit       1 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 3       C2RXIE: ECAN2 Event Interrupt Enable bit       1 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 4       Interrupt request not enabled       0 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 5       INT3IE: External Interrupt 3 Enable bit       1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 4       T9IE: Timer9 Interrupt Enable bit       1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 4       T9IE: Timer9 Interrupt Enable bit       1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 4       T9IE: Timer8 Interrupt Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | C2RXIE    | INT4IE        | INT3IE          | T9IE           | T8IE           | MI2C2IE         | SI2C2IE  | T7IE  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 13       DMASIE: DMA Channel 5 Data Transfer Complete Interrupt Enable bit       1       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request not enabled       0       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0       = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0       = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request enabled       0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 7     |               |                 |                |                |                 |          | bit   |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 13       DMASIE: DMA Channel 5 Data Transfer Complete Interrupt Enable bit       1       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request not enabled       0       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0       = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0       = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request enabled       0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Logondi   |               |                 |                |                |                 |          |       |

| n = Value at POR 1' = Bit is set 0' = Bit is cleared x = Bit is unknown<br>bit 15-14 Unimplemented: Read as '0'<br>bit 13 DMASIE: DMA Channel 5 Data Transfer Complete Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled<br>bit 12-9 Unimplemented: Read as '0'<br>bit 8 C2IE: ECAN2 Event Interrupt Enable bit<br>1 = Interrupt request not enabled<br>0 = Interrupt request not enabled<br>bit 5 INT3IE: External Interrupt 3 Enable bit<br>1 = Interrupt request not enabled<br>0 = Interrupt request not enabled<br>bit 4 T9IE: Timer9 Interrupt Enable bit<br>1 = Interrupt request not enabled<br>0 = Interrupt request not enabled<br>0 = Interrupt request not enabled<br>bit 3 T8IE: Timer8 Interrupt Enable bit<br>1 = Interrupt request not enabled<br>0 = Interrupt request not enabled<br>0 = Interrupt request not enabled<br>0 = Interrupt request not enabled<br>1 = Interrupt request not enabled<br>0 = Interrupt request enabled<br>0 = Interrupt request enabled<br>0 = Interrupt req                                                                                       | •         | hit           | W = Writable    | hit            | II = Unimple   | mented hit rear | 1 as 'N' |       |

| Dit 15-14       Unimplemented: Read as '0'         Dit 13       DMASIE: DMA Channel 5 Data Transfer Complete Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request not enabled         Dit 12-9       Unimplemented: Read as '0'         Dit 8       C2IE: ECAN2 Event Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request enabled         Dit 7       C2RXIE: ECAN2 Receive Data Ready Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request enabled         Dit 6       INT4IE: External Interrupt 4 Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         Dit 5       INT3IE: External Interrupt 3 Enable bit         1 = Interrupt request not enabled       0 = Interrupt request enabled         Dit 4       T9IE: Timer9 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request enabled         Dit 4       T9IE: Timer9 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         Dit 4       T9IE: Timer9 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         Dit 4       T9IE: Timer8 Interrupt Terupt Enable bit         1 = Interrupt request not enabled       0 = Inter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |               |                 |                | •              |                 |          | own   |

| bit 13       DMASIE: DMA Channel 5 Data Transfer Complete Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request not enabled         0 bit 12-9       Unimplemented: Read as '0'         bit 8       C2IE: ECAN2 Event Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request en                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           | Ölt           |                 |                |                |                 |          |       |

| 1 = Interrupt request enabled<br>0 = Interrupt request not enabled<br>0 = Interrupt request not enabled<br>0 = Interrupt request enabled<br>0 = Interrupt request enabled<br>0 = Interrupt request not enabled<br>0 = Interrupt request not enabled<br>0 = Interrupt request enabled<br>0 = Interrupt req | bit 15-14 | Unimplemen    | nted: Read as ' | 0'             |                |                 |          |       |

| 0 = Interrupt request not enabled         oit 12-9       Unimplemented: Read as '0'         oit 8       C2IE: ECAN2 Event Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request enabled         oit 7       C2RXIE: ECAN2 Receive Data Ready Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         oit 7       C2RXIE: ECAN2 Receive Data Ready Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         oit 6       INT4IE: External Interrupt 4 Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         oit 5       INT3IE: External Interrupt 3 Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         oit 4       T9IE: Timer9 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         oit 3       T8IE: Timer8 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         oit 2       MI2C2IE: I2C2 Master Events Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request not enabled         oit 1       SI2C2IE: I2C2 Slave Events Interrupt Enable bit         1 = Interrupt request not enabled       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 13    | DMA5IE: DM    | IA Channel 5 D  | ata Transfer ( | Complete Inter | rupt Enable bit |          |       |

| bit 12-9       Unimplemented: Read as '0'         bit 8       C2IE: ECAN2 Event Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 6       INT4IE: External Interrupt 4 Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 5       INT3IE: External Interrupt 3 Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 4       T9IE: Timer9 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 3       T8IE: Timer9 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 3       T8IE: Timer8 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 4       T9IE: Timer8 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 4       Interrupt request not enabled         bit 5       MI2C2IE: I2C2 Mast                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |               |                 |                |                |                 |          |       |

| bit 8       C2IE: ECAN2 Event Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request not enabled         bit 7       C2RXIE: ECAN2 Receive Data Ready Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request enabled         bit 6       INT4IE: External Interrupt 4 Enable bit         1 = Interrupt request enabled       0 = Interrupt request enabled         bit 5       INT3IE: External Interrupt 3 Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 5       INT3IE: External Interrupt 3 Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 4       T9IE: Timer9 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 3       T8IE: Timer9 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 4       T9IE: Timer9 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 3       T8IE: Timer9 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 4       SI2C2IE: I2C2 Master Events Interrupt Enable bit         1 = Interrupt request not enabled<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           | -             | -               |                |                |                 |          |       |

| 1 = Interrupt request enabled         0 = Interrupt request not enabled         0it 7       C2RXIE: ECAN2 Receive Data Ready Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request not enabled         0it 6       INT4IE: External Interrupt 4 Enable bit         1 = Interrupt request on enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           | •             |                 |                |                |                 |          |       |

| <ul> <li>0 = Interrupt request not enabled</li> <li>0 = Interrupt request not enabled</li> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> <li>0 = Interrupt request enabled<!--</td--><td>bit 8</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></li></ul>                                                                                                                                                                                                                                                                                                   | bit 8     |               |                 |                |                |                 |          |       |

| bit 7       C2RXIE: ECAN2 Receive Data Ready Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request not enabled         bit 6       INT4IE: External Interrupt 4 Enable bit         1 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request ont enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt reque                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           | •             | •               |                |                |                 |          |       |

| 1 = Interrupt request enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled         0 = Interrupt request enabled         0 = Interrupt request enabled         0 = Interrupt request not enabled         0 = Interrupt request not enabled         0 = Interrupt request enabled         0 = Interrupt request not enabled         0 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 7     | -             | •               |                | errupt Enable  | bit             |          |       |

| bit 6       INT4IE: External Interrupt 4 Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled         bit 5       INT3IE: External Interrupt 3 Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |               |                 | -              | ·              |                 |          |       |

| 1 = Interrupt request enabled         0 = Interrupt request not enabled         bit 5       INT3IE: External Interrupt 3 Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled         bit 4       T9IE: Timer9 Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled         0 = Interrupt request enabled         0 = Interrupt request enabled         0 = Interrupt request not enabled         bit 3       T8IE: Timer8 Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled         bit 2       MI2C2IE: I2C2 Master Events Interrupt Enable bit         1 = Interrupt request not enabled         bit 1       Interrupt request not enabled         bit 2       MI2C2IE: I2C2 Slave Events Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 1       SI2C2IE: I2C2 Slave Events Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 0       T7IE: Timer7 Interrupt Enable bit         1 = Interrupt request enabled       1 = Interrupt request enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |               | -               |                |                |                 |          |       |

| 0 = Interrupt request not enabled         bit 5       INT3IE: External Interrupt 3 Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled         bit 4       T9IE: Timer9 Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled         0 = Interrupt request enabled         0 = Interrupt request not enabled         0 = Int                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 6     |               | •               |                |                |                 |          |       |

| bit 5       INT3IE: External Interrupt 3 Enable bit         1 = Interrupt request enabled       0 = Interrupt request not enabled         bit 4       T9IE: Timer9 Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request not enabled         bit 3       T8IE: Timer8 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 3       T8IE: Timer8 Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request not enabled         bit 2       MI2C2IE: I2C2 Master Events Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 1       Interrupt request not enabled         bit 2       MI2C2IE: I2C2 Master Events Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 1       Interrupt request not enabled         bit 0       TrIE: Timer7 Interrupt Enable bit <t< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |               |                 |                |                |                 |          |       |

| <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> <li>0 = Interrupt Interrupt Enable bit</li> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> <li>0 = Interrupt request not enabled</li> <li>0 = Interrupt request not enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | hit 5     | •             | ·               |                |                |                 |          |       |

| <ul> <li>0 = Interrupt request not enabled</li> <li>oit 4</li> <li>T9IE: Timer9 Interrupt Enable bit</li> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> <li>oit 3</li> <li>T8IE: Timer8 Interrupt Enable bit</li> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request enabled</li> <li>0 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> <li>0 = Interrupt request enabled</li> <li>0 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> <li>0 = Interrupt request not enabled</li> <li>0 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> <li>0 = Interrupt request enabled</li> <li>0 = Interrupt request enabled</li> <li>0 = Interrupt request enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit o     |               |                 |                |                |                 |          |       |

| 1 = Interrupt request enabled         0 = Interrupt request not enabled         0 = Interrupt request enabled         0 = Interrupt request enabled         0 = Interrupt request not enabled         0 = Interrupt request enabled         0 = Interrupt request enabled         0 = Interrupt request not enabled         1 = Interrupt request enabled         1 = Interrupt request enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |               |                 |                |                |                 |          |       |

| <ul> <li>0 = Interrupt request not enabled</li> <li>5 T8IE: Timer8 Interrupt Enable bit</li> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> <li>6 = Interrupt request not enabled</li> <li>7 MI2C2IE: I2C2 Master Events Interrupt Enable bit</li> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> <li>1 = Interrupt request enabled</li> <li>1 = Interrupt request not enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 4     | T9IE: Timer9  | Interrupt Enab  | le bit         |                |                 |          |       |

| bit 3       T8IE: Timer8 Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled         bit 2       MI2C2IE: I2C2 Master Events Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled         0 = Interrupt request enabled         0 = Interrupt request not enabled         bit 1       SI2C2IE: I2C2 Slave Events Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled         1 = Interrupt request not enabled         0 = Interrupt request not enabled         bit 0       T7IE: Timer7 Interrupt Enable bit         1 = Interrupt request enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |               |                 |                |                |                 |          |       |

| 1 = Interrupt request enabled         0 = Interrupt request not enabled         bit 2       MI2C2IE: I2C2 Master Events Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled         bit 1       SI2C2IE: I2C2 Slave Events Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled         bit 1       SI2C2IE: I2C2 Slave Events Interrupt Enable bit         1 = Interrupt request enabled         0 = Interrupt request not enabled         bit 0       T7IE: Timer7 Interrupt Enable bit         1 = Interrupt request enabled         bit 1       Interrupt request enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | hit 0     | -             | -               |                |                |                 |          |       |

| <ul> <li>0 = Interrupt request not enabled</li> <li>MI2C2IE: I2C2 Master Events Interrupt Enable bit</li> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> <li>bit 1</li> <li>SI2C2IE: I2C2 Slave Events Interrupt Enable bit</li> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> <li>bit 0</li> <li>T7IE: Timer7 Interrupt Enable bit</li> <li>1 = Interrupt request enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DIE 3     |               |                 |                |                |                 |          |       |

| <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> <li>bit 1</li> <li>SI2C2IE: I2C2 Slave Events Interrupt Enable bit</li> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> <li>bit 0</li> <li>T7IE: Timer7 Interrupt Enable bit</li> <li>1 = Interrupt request enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |               |                 |                |                |                 |          |       |

| <ul> <li>0 = Interrupt request not enabled</li> <li>5I2C2IE: I2C2 Slave Events Interrupt Enable bit</li> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> <li>bit 0</li> <li>T7IE: Timer7 Interrupt Enable bit</li> <li>1 = Interrupt request enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | bit 2     | MI2C2IE: 120  | 2 Master Even   | ts Interrupt E | nable bit      |                 |          |       |