Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 18x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp306a-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

### 2.1 Basic Connection Requirements

Getting started with the PIC24HJXXXGPX06A/X08A/X10A family of 16-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

- (see Section 2.2 "Decoupling Capacitors") VCAP

- (see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for ADC module is implemented

| Note: | The   | AVdd    | and   | AVss   | pins | mu  | st be |

|-------|-------|---------|-------|--------|------|-----|-------|

|       | conn  | ected   | indep | endent | of   | the | ADC   |

|       | volta | ge refe | rence |        |      |     |       |

### 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

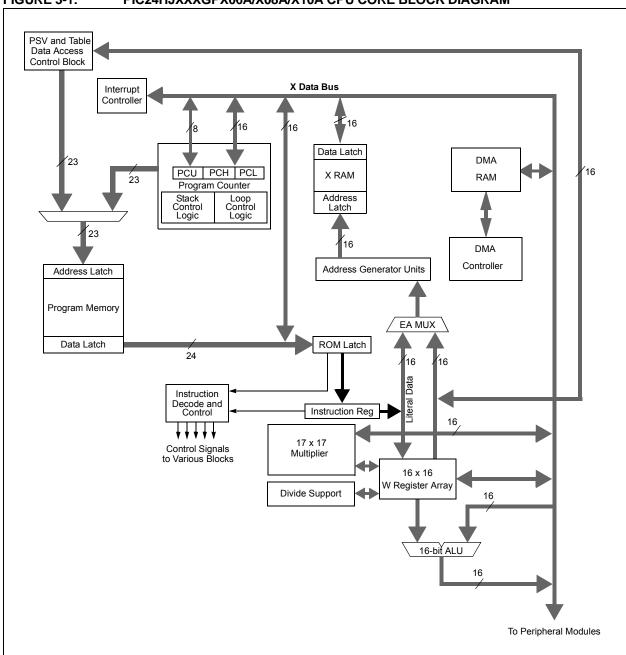

### FIGURE 3-1: PIC24HJXXXGPX06A/X08A/X10A CPU CORE BLOCK DIAGRAM

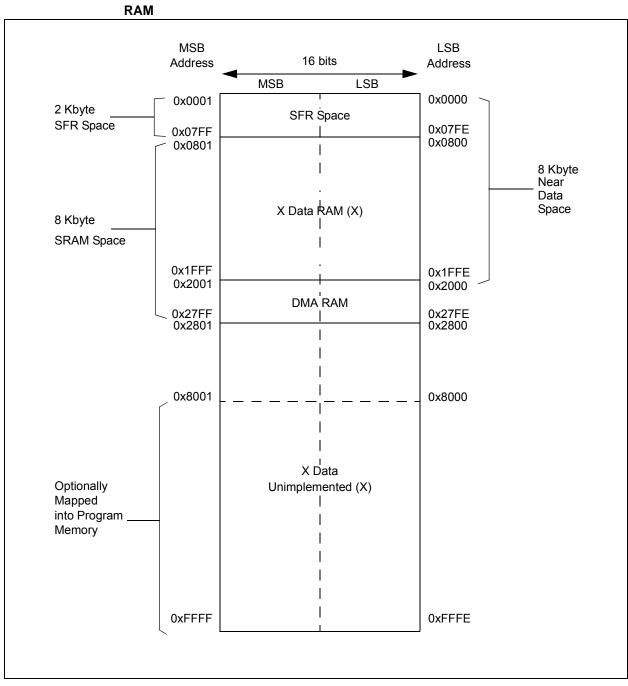

### FIGURE 4-3: DATA MEMORY MAP FOR PIC24HJXXXGPX06A/X08A/X10A DEVICES WITH 8 KB

| R/W-      | 0 R/W-0                                                            | U-0                                                     | U-0                       | U-0                                                 | U-0                | U-0              | R/W-0                |  |

|-----------|--------------------------------------------------------------------|---------------------------------------------------------|---------------------------|-----------------------------------------------------|--------------------|------------------|----------------------|--|

| TRAP      | R IOPUWR                                                           | —                                                       | —                         | —                                                   | —                  | —                | VREGS <sup>(3)</sup> |  |

| bit 15    | ·                                                                  |                                                         |                           |                                                     |                    |                  | bit                  |  |

| R/W-      | 0 R/W-0                                                            | R/W-0                                                   | R/W-0                     | R/W-0                                               | R/W-0              | R/W-1            | R/W-1                |  |

| EXTR      |                                                                    | SWDTEN <sup>(2)</sup>                                   | WDTO                      | SLEEP                                               | IDLE               | BOR              | POR                  |  |

| bit 7     |                                                                    |                                                         |                           |                                                     |                    |                  | bit                  |  |

| Legend:   |                                                                    |                                                         |                           |                                                     |                    |                  |                      |  |

| R = Read  | = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                         |                           |                                                     |                    |                  |                      |  |

| -n = Valu | e at POR                                                           | '1' = Bit is set                                        |                           | '0' = Bit is cle                                    | ared               | x = Bit is unk   | nown                 |  |

| bit 15    | 1 = A Trap Co                                                      | Reset Flag bit<br>onflict Reset ha<br>onflict Reset ha  | s occurred                | d                                                   |                    |                  |                      |  |

| bit 14    | 1 = An illega<br>Address                                           | l opcode deter<br>Pointer caused                        | ction, an ille<br>a Reset | W Access Rese<br>gal address mo<br>Reset has not oo | ode or uninitiali  | zed W regist     | er used as a         |  |

| bit 13-9  | Unimplemen                                                         | ted: Read as 'o                                         | )'                        |                                                     |                    |                  |                      |  |

| bit 8     | 1 = Voltage R                                                      | age Regulator S<br>egulator is acti<br>egulator goes i  | ve during Sle             |                                                     | еер                |                  |                      |  |

| bit 7     | 1 = A Master                                                       | al Reset (MCL<br>Clear (pin) Res<br>Clear (pin) Res     | et has occur              |                                                     |                    |                  |                      |  |

| bit 6     | 1 <b>= A</b> reset                                                 | re Reset (Instru<br>instruction has<br>instruction has  | been execut               | ed                                                  |                    |                  |                      |  |

| bit 5     | <b>SWDTEN:</b> So<br>1 = WDT is en<br>0 = WDT is di                |                                                         | Disable of W              | DT bit <sup>(2)</sup>                               |                    |                  |                      |  |

| bit 4     | 1 = WDT time                                                       | hdog Timer Tim<br>e-out has occur<br>e-out has not oc   | red                       | it                                                  |                    |                  |                      |  |

| bit 3     | SLEEP: Wake<br>1 = Device ha                                       | e-up from Sleep<br>as been in Slee<br>as not been in S  | o Flag bit<br>p mode      |                                                     |                    |                  |                      |  |

| bit 2     | IDLE: Wake-u<br>1 = Device wa                                      | up from Idle Fla<br>as in Idle mode<br>as not in Idle m | g bit                     |                                                     |                    |                  |                      |  |

| bit 1     | 1 = A Brown-                                                       | out Reset Flag<br>out Reset has c<br>out Reset has r    | occurred                  |                                                     |                    |                  |                      |  |

| bit 0     | <b>POR:</b> Power-<br>1 = A Power-                                 | on Reset Flag I<br>on Reset has o<br>on Reset has n     | bit<br>ccurred            |                                                     |                    |                  |                      |  |

| Note 1:   | All of the Reset sta<br>cause a device Re                          | -                                                       | set or cleare             | ed in software. S                                   | Setting one of the | ese bits in soff | tware does no        |  |

| 2:        | If the FWDTEN Co<br>SWDTEN bit settin                              | ig.                                                     |                           | -                                                   | -                  | -                |                      |  |

| 3:        | For PIC24HJ256G                                                    | PX06A/X08A/X                                            | (10A devices              | , this bit is unim                                  | plemented and      | reads back p     | rogrammed            |  |

**3:** For PIC24HJ256GPX06A/X08A/X10A devices, this bit is unimplemented and reads back programmed value.

### 7.3 Interrupt Control and Status Registers

PIC24HJXXXGPX06A/X08A/X10A devices implement a total of 30 registers for the interrupt controller:

- INTCON1

- INTCON2

- IFS0 through IFS4

- IEC0 through IEC4

- IPC0 through IPC17

- INTTREG

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table.

The IFS registers maintain all of the interrupt request flags. Each source of interrupt has a Status bit, which is set by the respective peripherals or external signal and is cleared via software.

The IEC registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals. The IPC registers are used to set the interrupt priority level for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

The INTTREG register contains the associated interrupt vector number and the new CPU interrupt priority level, which are latched into vector number (VEC-NUM<6:0>) and Interrupt level (ILR<3:0>) bit fields in the INTTREG register. The new interrupt priority level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence that they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having vector number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0>, and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

Although they are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. The CPU STATUS register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU interrupt priority level. The user can change the current CPU priority level by writing to the IPL bits.

The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-1 through Register 7-32.

### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

| U-0             | R/W-0           | R/W-0                            | R/W-0            | R/W-0                                    | R/W-0            | R/W-0           | R/W-0  |

|-----------------|-----------------|----------------------------------|------------------|------------------------------------------|------------------|-----------------|--------|

| _               | DMA1IF          | AD1IF                            | U1TXIF           | U1RXIF                                   | SPI1IF           | SPI1EIF         | T3IF   |

| bit 15          |                 |                                  |                  |                                          |                  |                 | bit 8  |

|                 |                 |                                  |                  |                                          |                  |                 |        |

| R/W-0           | R/W-0           | R/W-0                            | R/W-0            | R/W-0                                    | R/W-0            | R/W-0           | R/W-0  |

| T2IF            | OC2IF           | IC2IF                            | DMA01IF          | T1IF                                     | OC1IF            | IC1IF           | INTOIF |

| bit 7           |                 |                                  |                  |                                          |                  |                 | bit C  |

| Legend:         |                 |                                  |                  |                                          |                  |                 |        |

| R = Readable    | bit             | W = Writable                     | bit              | U = Unimpler                             | mented bit, rea  | d as '0'        |        |

| -n = Value at F | OR              | '1' = Bit is se                  |                  | '0' = Bit is cle                         |                  | x = Bit is unkn | iown   |

|                 |                 |                                  |                  |                                          |                  |                 |        |

| bit 15          | Unimplemen      | ted: Read as                     | 0'               |                                          |                  |                 |        |

| bit 14          | DMA1IF: DM      | A Channel 1 D                    | ata Transfer C   | Complete Interr                          | rupt Flag Status | bit             |        |

|                 |                 | request has oc                   |                  |                                          |                  |                 |        |

| bit 13          |                 | request has no<br>I Conversion C |                  | unt Elog Statu                           | o hit            |                 |        |

| DIL 13          |                 | request has oc                   | •                | upi riay Sialu                           |                  |                 |        |

|                 |                 | request has no                   |                  |                                          |                  |                 |        |

| bit 12          | U1TXIF: UAF     | RT1 Transmitte                   | r Interrupt Flag | g Status bit                             |                  |                 |        |

|                 |                 | request has oc                   |                  |                                          |                  |                 |        |

|                 |                 | request has no                   |                  |                                          |                  |                 |        |

| bit 11          |                 | RT1 Receiver I<br>request has oc |                  | Status Dit                               |                  |                 |        |

|                 |                 | request has oc                   |                  |                                          |                  |                 |        |

| bit 10          | -               | Event Interrup                   |                  | bit                                      |                  |                 |        |

|                 |                 | request has oc                   |                  |                                          |                  |                 |        |

|                 |                 | request has no                   |                  |                                          |                  |                 |        |

| bit 9           |                 | 1 Fault Interru                  | •                | bit                                      |                  |                 |        |

|                 |                 | request has oc<br>request has no |                  |                                          |                  |                 |        |

| bit 8           |                 | Interrupt Flag                   |                  |                                          |                  |                 |        |

|                 |                 | request has oc                   |                  |                                          |                  |                 |        |

|                 | -               | request has no                   |                  |                                          |                  |                 |        |

| bit 7           |                 | Interrupt Flag                   |                  |                                          |                  |                 |        |

|                 |                 | request has oc<br>request has no |                  |                                          |                  |                 |        |

| bit 6           |                 | ut Compare Ch                    |                  | upt Flag Status                          | s bit            |                 |        |

|                 |                 | request has oc                   |                  | -p · · · · · · · · · · · · · · · · · · · |                  |                 |        |

|                 | 0 = Interrupt i | request has no                   | t occurred       |                                          |                  |                 |        |

| bit 5           | -               | Capture Chann                    | •                | -lag Status bit                          |                  |                 |        |

|                 |                 | request has oc<br>request has no |                  |                                          |                  |                 |        |

| bit 4           | -               | -                                |                  | Complete Inte                            | rrupt Flag Statu | ıs bit          |        |

|                 |                 | request has oc                   |                  |                                          |                  |                 |        |

|                 |                 | request has no                   |                  |                                          |                  |                 |        |

| bit 3           |                 | Interrupt Flag                   |                  |                                          |                  |                 |        |

|                 |                 | request has oc                   |                  |                                          |                  |                 |        |

|                 | 0 = interrupt i | request has no                   | coccurred        |                                          |                  |                 |        |

### REGISTER 7-23: IPC8: INTERRUPT PRIORITY CONTROL REGISTER 8

| U-0           | R/W-1        | R/W-0                                     | R/W-0           | U-0              | R/W-1          | R/W-0           | R/W-0 |

|---------------|--------------|-------------------------------------------|-----------------|------------------|----------------|-----------------|-------|

| —             |              | C1IP<2:0>                                 |                 | —                |                | C1RXIP<2:0>     |       |

| bit 15        |              |                                           |                 |                  |                |                 | bit 8 |

|               |              | R/W-0                                     | R/W-0           | U-0              |                | R/W-0           |       |

| U-0           | R/W-1        | SPI2IP<2:0>                               | R/W-U           | 0-0              | R/W-1          | SPI2EIP<2:0>    | R/W-0 |

| <br>bit 7     |              | 51 1211 ~2.02                             |                 | _                |                | 51 12L11 ~2.02  | bit   |

|               |              |                                           |                 |                  |                |                 |       |

| Legend:       |              |                                           |                 |                  |                |                 |       |

| R = Readable  | e bit        | W = Writable I                            | bit             | U = Unimpler     | mented bit, re | ad as '0'       |       |

| -n = Value at | POR          | '1' = Bit is set                          |                 | '0' = Bit is cle | ared           | x = Bit is unkn | iown  |

| bit 15        | Unimpleme    | ented: Read as '                          | )'              |                  |                |                 |       |

| bit 14-12     | -            | ECAN1 Event In                            |                 | ty bits          |                |                 |       |

|               |              | rupt is priority 7 (ł                     | =               | -                |                |                 |       |

|               | •            |                                           |                 |                  |                |                 |       |

|               | •            |                                           |                 |                  |                |                 |       |

|               | 001 = Intern | rupt is priority 1                        |                 |                  |                |                 |       |

|               |              | rupt source is disa                       | abled           |                  |                |                 |       |

| bit 11        | Unimpleme    | ented: Read as 'o                         | )'              |                  |                |                 |       |

| bit 10-8      |              | 0>: ECAN1 Rece                            |                 |                  | iority bits    |                 |       |

|               | 111 = Interr | rupt is priority 7 (I                     | nighest priorit | y interrupt)     |                |                 |       |

|               | •            |                                           |                 |                  |                |                 |       |

|               | •            |                                           |                 |                  |                |                 |       |

|               |              | rupt is priority 1<br>rupt source is disa | abled           |                  |                |                 |       |

| bit 7         | Unimpleme    | ented: Read as 'o                         | )'              |                  |                |                 |       |

| bit 6-4       | SPI2IP<2:0   | >: SPI2 Event Inf                         | errupt Priorit  | y bits           |                |                 |       |

|               | 111 = Interr | rupt is priority 7 (I                     | nighest priorif | y interrupt)     |                |                 |       |

|               | •            |                                           |                 |                  |                |                 |       |

|               | •            |                                           |                 |                  |                |                 |       |

|               |              | rupt is priority 1<br>rupt source is disa | abled           |                  |                |                 |       |

| bit 3         | Unimpleme    | ented: Read as 'o                         | )'              |                  |                |                 |       |

| bit 2-0       | SPI2EIP<2:   | :0>: SPI2 Error In                        | terrupt Priori  | ty bits          |                |                 |       |

|               | 111 = Interr | rupt is priority 7 (ł                     | nighest priorit | y interrupt)     |                |                 |       |

|               | •            |                                           |                 |                  |                |                 |       |

|               | •            |                                           |                 |                  |                |                 |       |

|               | 001 = Interr | rupt is priority 1                        |                 |                  |                |                 |       |

|               |              |                                           |                 |                  |                |                 |       |

NOTES:

### REGISTER 8-3: DMAXSTA: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER A

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |  |

|------------------------------------|-------|-------|-------|-----------------------------------------|-----------------|----------|-------|--|

|                                    |       |       | STA   | <15:8>                                  |                 |          |       |  |

| bit 15                             |       |       |       |                                         |                 |          | bit 8 |  |

|                                    |       |       |       |                                         |                 |          |       |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |  |

|                                    |       |       | STA   | <7:0>                                   |                 |          |       |  |

| bit 7                              |       |       |       |                                         |                 |          | bit 0 |  |

|                                    |       |       |       |                                         |                 |          |       |  |

| Legend:                            |       |       |       |                                         |                 |          |       |  |

| R = Readable bit W = Writable bit  |       |       | bit   | U = Unimpler                            | nented bit, rea | d as '0' |       |  |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is cleared x = Bit is unknown |                 |          |       |  |

bit 15-0 STA<15:0>: Primary DMA RAM Start Address bits (source or destination)

#### REGISTER 8-4: DMAxSTB: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER B

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------------------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                                   |       |                  | STB   | <15:8>           |                 |                 |       |

| bit 15                            |       |                  |       |                  |                 |                 | bit 8 |

|                                   |       |                  |       |                  |                 |                 |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                                   |       |                  | STE   | 3<7:0>           |                 |                 |       |

| bit 7                             |       |                  |       |                  |                 |                 | bit 0 |

| Legend:                           |       |                  |       |                  |                 |                 |       |

| R = Readable bit W = Writable bit |       |                  | it    | U = Unimpler     | mented bit, rea | ad as '0'       |       |

| -n = Value at POR '1' = Bit is    |       | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkı | nown  |

bit 15-0 STB<15:0>: Secondary DMA RAM Start Address bits (source or destination)

| U-0                 | U-0                                                                                    | U-0                                                                                     | U-0                                                                          | U-0                                     | U-0              | U-0                | U-0   |  |  |

|---------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------|------------------|--------------------|-------|--|--|

| —                   | _                                                                                      |                                                                                         | _                                                                            | —                                       | _                |                    | _     |  |  |

| bit 15              |                                                                                        |                                                                                         |                                                                              |                                         |                  |                    | bit   |  |  |

|                     |                                                                                        |                                                                                         |                                                                              |                                         |                  |                    |       |  |  |

| U-0                 | U-0                                                                                    | R/W-0                                                                                   | R/W-0                                                                        | R/W-0                                   | R/W-0            | R/W-0              | R/W-0 |  |  |

|                     | — — TUN<5:0> <sup>(1)</sup>                                                            |                                                                                         |                                                                              |                                         |                  |                    |       |  |  |

| bit 7               |                                                                                        |                                                                                         |                                                                              |                                         |                  |                    | bit ( |  |  |

|                     |                                                                                        |                                                                                         |                                                                              |                                         |                  |                    |       |  |  |

| Legend:             |                                                                                        |                                                                                         |                                                                              |                                         |                  |                    |       |  |  |

| R = Readable        | e bit                                                                                  | W = Writable                                                                            | bit                                                                          | U = Unimplem                            | nented bit, read | d as '0'           |       |  |  |

| -n = Value at       | POR                                                                                    | '1' = Bit is set                                                                        |                                                                              | '0' = Bit is clea                       | ared             | x = Bit is unknown |       |  |  |

|                     |                                                                                        |                                                                                         |                                                                              |                                         |                  |                    |       |  |  |

|                     |                                                                                        |                                                                                         |                                                                              |                                         |                  |                    |       |  |  |

| bit 15-6            | Unimplemen                                                                             | ted: Read as '                                                                          | 0'                                                                           |                                         |                  |                    |       |  |  |

| bit 15-6<br>bit 5-0 | •                                                                                      | <b>ted:</b> Read as '<br>RC Oscillator T                                                |                                                                              |                                         |                  |                    |       |  |  |

|                     | <b>TUN&lt;5:0&gt;:</b> F                                                               |                                                                                         | uning bits <sup>(1)</sup>                                                    | 345 MHz)                                |                  |                    |       |  |  |

|                     | <b>TUN&lt;5:0&gt;:</b> F                                                               | RC Oscillator T                                                                         | uning bits <sup>(1)</sup>                                                    | 345 MHz)                                |                  |                    |       |  |  |

|                     | <b>TUN&lt;5:0&gt;:</b> F                                                               | RC Oscillator T                                                                         | uning bits <sup>(1)</sup>                                                    | 345 MHz)                                |                  |                    |       |  |  |

|                     | TUN<5:0>: F<br>111111 = Ce<br>•<br>•                                                   | RC Oscillator T<br>nter frequency                                                       | <sup>-</sup> uning bits <sup>(1)</sup><br>– 0.375% (7.                       | ·                                       |                  |                    |       |  |  |

|                     | TUN<5:0>: F<br>111111 = Ce<br>100001 = Ce                                              | RC Oscillator T                                                                         | - 0.375% (7.<br>– 11.625% (6                                                 | .52 MHz)                                |                  |                    |       |  |  |

|                     | TUN<5:0>: F<br>111111 = Ce<br>•<br>•<br>100001 = Ce<br>100000 = Ce<br>011111 = Ce      | RC Oscillator T<br>nter frequency<br>nter frequency<br>nter frequency<br>nter frequency | - 0.375% (7.<br>- 0.375% (7.<br>- 11.625% (6<br>- 12% (6.49<br>+ 11.625% (8  | .52 MHz)<br>MHz)<br>.23 MHz)            |                  |                    |       |  |  |

|                     | TUN<5:0>: F<br>111111 = Ce<br>•<br>•<br>100001 = Ce<br>100000 = Ce<br>011111 = Ce      | RC Oscillator T<br>nter frequency<br>nter frequency<br>nter frequency                   | - 0.375% (7.<br>- 0.375% (7.<br>- 11.625% (6<br>- 12% (6.49<br>+ 11.625% (8  | .52 MHz)<br>MHz)<br>.23 MHz)            |                  |                    |       |  |  |

|                     | TUN<5:0>: F<br>111111 = Ce<br>•<br>•<br>100001 = Ce<br>100000 = Ce<br>011111 = Ce      | RC Oscillator T<br>nter frequency<br>nter frequency<br>nter frequency<br>nter frequency | - 0.375% (7.<br>- 0.375% (7.<br>- 11.625% (6<br>- 12% (6.49<br>+ 11.625% (8  | .52 MHz)<br>MHz)<br>.23 MHz)            |                  |                    |       |  |  |

|                     | TUN<5:0>: F<br>111111 = Ce<br>•<br>•<br>100001 = Ce<br>100000 = Ce<br>011111 = Ce      | RC Oscillator T<br>nter frequency<br>nter frequency<br>nter frequency<br>nter frequency | - 0.375% (7.<br>- 0.375% (7.<br>- 11.625% (6<br>- 12% (6.49<br>+ 11.625% (8  | .52 MHz)<br>MHz)<br>.23 MHz)            |                  |                    |       |  |  |

|                     | TUN<5:0>: F<br>111111 = Ce<br>100001 = Ce<br>100000 = Ce<br>011111 = Ce<br>011110 = Ce | RC Oscillator T<br>nter frequency<br>nter frequency<br>nter frequency<br>nter frequency | - 0.375% (7.<br>- 11.625% (6<br>- 12% (6.49<br>+ 11.625% (8<br>+ 11.25% (8.1 | .52 MHz)<br>MHz)<br>.23 MHz)<br>20 MHz) |                  |                    |       |  |  |

### REGISTER 9-4: OSCTUN: FRC OSCILLATOR TUNING REGISTER<sup>(2)</sup>

- **Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation and is neither characterized nor tested.

- 2: This register is reset only on a Power-on Reset (POR).

### REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | <ul> <li>Start bit</li> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul>                                                               |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | Hardware set or clear when Start, Repeated Start or Stop detected.<br><b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)<br>1 = Read – indicates data transfer is output from slave          |

|       | 0 = Write - indicates data transfer is input to slaveHardware set or clear after reception of I2C device address byte.                                                                                                      |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                                                                                                         |

|       | <ul> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> </ul> |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                                                                                                        |

|       | <ul> <li>1 = Transmit in progress, I2CxTRN is full</li> <li>0 = Transmit complete, I2CxTRN is empty</li> <li>Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.</li> </ul>       |

### REGISTER 19-31: CITRBnSTAT: ECAN™ MODULE RECEIVE BUFFER n STATUS

|                | (n = 0, | 1,, 31)      |             |              |                  |        |       |  |

|----------------|---------|--------------|-------------|--------------|------------------|--------|-------|--|

| U-0            | U-0     | U-0          | R/W-x       | R/W-x        | R/W-x            | R/W-x  | R/W-x |  |

| —              | —       | —            | FILHIT<4:0> |              |                  |        |       |  |

| bit 15         |         |              |             |              |                  |        | bit 8 |  |

|                |         |              |             |              |                  |        |       |  |

| U-0            | U-0     | U-0          | U-0         | U-0          | U-0              | U-0    | U-0   |  |

|                |         |              | -           | —            | —                | —      |       |  |

| bit 7          |         |              |             |              |                  |        | bit 0 |  |

|                |         |              |             |              |                  |        |       |  |

| Legend:        |         |              |             |              |                  |        |       |  |

| R = Readable I | bit     | W = Writable | bit         | U = Unimpler | mented bit, read | as '0' |       |  |

bit 15-13 **Unimplemented:** Read as '0'

-n = Value at POR

'1' = Bit is set

bit 12-8 **FILHIT<4:0>:** Filter Hit Code bits (only written by module for receive buffers, unused for transmit buffers) Encodes number of filter that resulted in writing this buffer.

'0' = Bit is cleared

bit 7-0 Unimplemented: Read as '0'

x = Bit is unknown

#### Base Assembly # of # of Status Flags Instr Assembly Syntax Description Mnemonic Words Cycles Affected # 47 Relative Call RCALL RCALL 1 2 None Expr RCALL Computed Call 1 2 None Wn 48 REPEAT REPEAT #lit14 Repeat Next Instruction lit14 + 1 times 1 1 None REPEAT Repeat Next Instruction (Wn) + 1 times 1 1 None Wn 1 1 49 RESET RESET Software device Reset None 50 RETFIE RETFIE Return from interrupt 1 3 (2) None 51 RETLW #lit10,Wn Return with literal in Wn 1 3 (2) None RETLW 52 1 RETURN RETURN Return from Subroutine 3 (2) None 53 RLC RLC f = Rotate Left through Carry f 1 1 C,N,Z f RLC f,WREG WREG = Rotate Left through Carry f 1 1 C,N,Z RLC Ws,Wd Wd = Rotate Left through Carry Ws 1 1 C,N,Z 54 f = Rotate Left (No Carry) f 1 1 N,Z RLNC RUNC f 1 RLNC f,WREG WREG = Rotate Left (No Carry) f 1 N,Z RLNC Ws,Wd Wd = Rotate Left (No Carry) Ws 1 1 N,Z 55 RRC RRC f = Rotate Right through Carry f 1 1 C,N,Z f WREG = Rotate Right through Carry f 1 1 C,N,Z RRC f,WREG RRC Wd = Rotate Right through Carry Ws 1 1 C,N,Z Ws,Wd 56 RRNC RRNC f = Rotate Right (No Carry) f 1 1 N,Z f WREG = Rotate Right (No Carry) f 1 1 N,Z RRNC f,WREG Wd = Rotate Right (No Carry) Ws 1 1 N,Z RRNC Ws,Wd 1 C,N,Z 57 SE SE Ws,Wnd Wnd = sign-extended Ws 1 58 SETM SETM f f = 0xFFFF1 1 None WREG = 0xFFFF 1 1 SETM WREG None Ws = 0xFFFF 1 SETM Ws 1 None 59 SL SL f f = Left Shift f 1 1 C,N,OV,Z SL f,WREG WREG = Left Shift f 1 1 C,N,OV,Z Wd = Left Shift Ws 1 1 C,N,OV,Z SL Ws,Wd Wnd = Left Shift Wb by Wns 1 1 SL N.Z Wb, Wns, Wnd SL Wb,#lit5,Wnd Wnd = Left Shift Wb by lit5 1 1 N,Z 60 SUB SUB f = f – WREG 1 1 C,DC,N,OV,Z f WREG = f - WREG 1 1 C,DC,N,OV,Z SUB f,WREG Wn = Wn - lit10SUB #lit10,Wn 1 1 C,DC,N,OV,Z SUB Wb,Ws,Wd Wd = Wb - Ws1 1 C,DC,N,OV,Z Wd = Wb - lit5 1 1 C,DC,N,OV,Z SUB Wb,#lit5,Wd 61 SUBB $f = f - WREG - (\overline{C})$ C,DC,N,OV,Z 1 1 SUBB f WREG = $f - WREG - (\overline{C})$ 1 SUBB f,WREG 1 C,DC,N,OV,Z $Wn = Wn - lit10 - (\overline{C})$ 1 C,DC,N,OV,Z 1 SUBB #lit10,Wn SUBB $Wd = Wb - Ws - (\overline{C})$ 1 1 C,DC,N,OV,Z Wb,Ws,Wd SUBB Wb,#lit5,Wd $Wd = Wb - lit5 - (\overline{C})$ 1 1 C,DC,N,OV,Z 62 SUBR f = WREG - f 1 1 C,DC,N,OV,Z SUBR f WREG = WREG - f 1 1 C,DC,N,OV,Z SUBR f,WREG SUBR Wb,Ws,Wd Wd = Ws - Wb 1 1 C,DC,N,OV,Z Wd = lit5 - Wb1 1 C,DC,N,OV,Z SUBR Wb, #lit5, Wd 63 SUBBR $f = WREG - f - (\overline{C})$ 1 1 C,DC,N,OV,Z SUBBR f WREG = WREG - f - $(\overline{C})$ 1 SUBBR f,WREG 1 C,DC,N,OV,Z $Wd = Ws - Wb - (\overline{C})$ 1 1 C,DC,N,OV,Z SUBBR Wb.Ws.Wd $Wd = lit5 - Wb - (\overline{C})$ 1 C,DC,N,OV,Z SUBBR Wb,#lit5,Wd 1 64 1 SWAP SWAP.b Wn Wn = nibble swap Wn 1 None SWAP Wn = byte swap Wn 1 1 None Wn 1 2 65 Read Prog<23:16> to Wd<7:0> TBLRDH TBLRDH Ws,Wd None

#### TABLE 22-2: INSTRUCTION SET OVERVIEW (CONTINUED)

### TABLE 24-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACTERISTICSStandard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Inde<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended<br>(unless otherwise stated)<br>(unless otherwise stated)<br>(unless otherwise stated)<br>(Derived the states)<br>(Derived the states)<br>(Derived the states)<br>(Derived the states)<br>(Derived the states)<br>(Unless otherwise states)<br>(Unless otherwise states)<br>(Unless otherwise states)<br>(Unless otherwise states)<br>(Derived the states)<br><th>≤ +85°C for Industrial</th> |                        |      |       |                | ≤ +85°C for Industrial |                                              |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|----------------|------------------------|----------------------------------------------|--|--|--|--|

| Parameter<br>No. <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Typical <sup>(2)</sup> | Max  | Units | its Conditions |                        |                                              |  |  |  |  |

| Power-Down Current (IPD) <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |      |       |                |                        |                                              |  |  |  |  |

| DC60d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50                     | 200  | μA    | -40°C          |                        |                                              |  |  |  |  |

| DC60a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50                     | 200  | μA    | +25°C          | 2.01/                  | Base Power-Down Current <sup>(3)</sup>       |  |  |  |  |

| DC60b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 200                    | 500  | μΑ    | +85°C          | 3.3V                   | Base Power-Down Currents?                    |  |  |  |  |

| DC60c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 600                    | 1000 | μΑ    | +125°C         |                        |                                              |  |  |  |  |

| DC61d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8                      | 13   | μA    | -40°C          |                        |                                              |  |  |  |  |

| DC61a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10                     | 15   | μA    | +25°C          | 2.21/                  | Watabdag Timor Current: Alwor(3)             |  |  |  |  |

| DC61b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12                     | 20   | μA    | +85°C          | 3.3V                   | Watchdog Timer Current: ∆IwDT <sup>(3)</sup> |  |  |  |  |

| DC61c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13                     | 25   | μΑ    | +125°C         |                        |                                              |  |  |  |  |

Note 1: IPD (Sleep) current is measured as follows:

- CPU core is off, oscillator is configured in EC mode and external clock active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- CLKO is configured as an I/O input pin in the Configuration word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled, all peripheral modules except the ADC are disabled (PMDx bits are all '1's). The following ADC settings are enabled for each ADC module (ADCx) prior to executing the PWRSAV instruction: ADON = 1, VCFG = 1, AD12B = 1 and ADxMD = 0.

- VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to stand-by while the device is in Sleep mode)

- RTCC is disabled.

- JTAG is disabled

- 2: Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The Watchdog Timer Current is the additional current consumed when the WDT module is enabled. This current should be added to the base IPD current.

- 4: These currents are measured on the device containing the most memory in this family.

- 5: These parameters are characterized, but are not tested in manufacturing.

### TABLE 24-21: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER TIMING REQUIREMENTS

| AC CHA       | RACTER | ISTICS                                                         | (unles | ard Operatin<br>s otherwise<br>ting tempera | <b>stated)</b><br>ture -4 | 40°C ≤ ⊺   | <b>3.0V to 3.6V</b><br>TA $\leq$ +85°C for Industrial<br>A $\leq$ +125°C for Extended  |

|--------------|--------|----------------------------------------------------------------|--------|---------------------------------------------|---------------------------|------------|----------------------------------------------------------------------------------------|

| Param<br>No. | Symbol | Characteristic <sup>(1)</sup>                                  | Min    | Тур <sup>(2)</sup>                          | Max                       | Conditions |                                                                                        |

| SY10         | ТмсL   | MCLR Pulse Width (low)                                         | 2      | _                                           |                           | μS         | -40°C to +85°C                                                                         |

| SY11         | Tpwrt  | Power-up Timer Period                                          | _      | 2<br>4<br>8<br>16<br>32<br>64<br>128        | _                         | ms         | -40°C to +85°C<br>User programmable                                                    |

| SY12         | TPOR   | Power-on Reset Delay                                           | 3      | 10                                          | 30                        | μS         | -40°C to +85°C                                                                         |