Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 32x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp310a-e-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

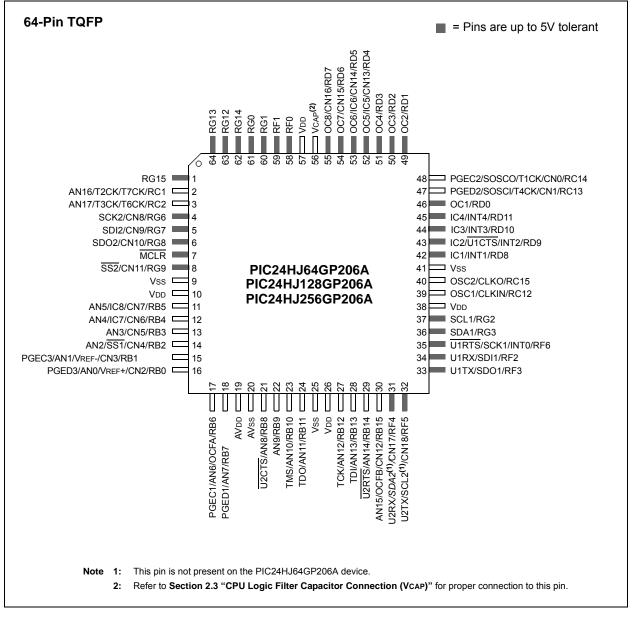

## Pin Diagrams (Continued)

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and requirements timing information in the "dsPIC33F/PIC24H Flash Programming Specification" (DS70152) for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3 In-Circuit Debugger" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- *"Using MPLAB<sup>®</sup> REAL ICE™"* (poster) DS51749

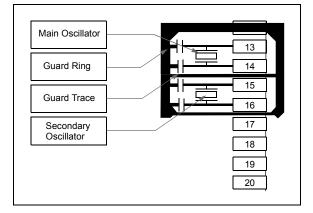

## 2.6 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 9.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### FIGURE 2-3: SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

## 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to  $\leq$  8 MHz for start-up with PLL enabled to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLDBF to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration word.

## 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 3 or REAL ICE is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins, by setting all bits in the AD1PCFGL register.

The bits in this register that correspond to the A/D pins that are initialized by MPLAB ICD 3 or REAL ICE, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFGL register during initialization of the ADC module.

When MPLAB ICD 3 or REAL ICE is used as a programmer, the user application firmware must correctly configure the AD1PCFGL register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

## 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic-low state.

Alternatively, connect a 1k to 10k resistor between Vss and the unused pins.

| Reset Type      | Clock Source  | SYSRST Delay           | System Clock<br>Delay | FSCM<br>Delay | See Notes        |

|-----------------|---------------|------------------------|-----------------------|---------------|------------------|

| POR             | EC, FRC, LPRC | TPOR + TSTARTUP + TRST | —                     | _             | 1, 2, 3          |

|                 | ECPLL, FRCPLL | TPOR + TSTARTUP + TRST | TLOCK                 | TFSCM         | 1, 2, 3, 5, 6    |

|                 | XT, HS, SOSC  | TPOR + TSTARTUP + TRST | Тоѕт                  | TFSCM         | 1, 2, 3, 4, 6    |

|                 | XTPLL, HSPLL  | TPOR + TSTARTUP + TRST | TOST + TLOCK          | TFSCM         | 1, 2, 3, 4, 5, 6 |

| MCLR            | Any Clock     | Trst                   | —                     | _             | 3                |

| WDT             | Any Clock     | Trst                   | —                     | _             | 3                |

| Software        | Any clock     | Trst                   | —                     | _             | 3                |

| Illegal Opcode  | Any Clock     | Trst                   | —                     | _             | 3                |

| Uninitialized W | Any Clock     | Trst                   | —                     | _             | 3                |

| Trap Conflict   | Any Clock     | Trst                   | —                     | —             | 3                |

#### TABLE 6-3: RESET DELAY TIMES FOR VARIOUS DEVICE RESETS

**Note 1:** TPOR = Power-on Reset delay (10 μs nominal).

**2:** TSTARTUP = Conditional POR delay of 20 μs nominal (if on-chip regulator is enabled) or 64 ms nominal Power-up Timer delay (if regulator is disabled). TSTARTUP is also applied to all returns from powered-down states, including waking from Sleep mode, only if the regulator is enabled.

- 3: TRST = Internal state Reset time (20 μs nominal).

- **4:** TOST = Oscillator Start-up Timer. A 10-bit counter counts 1024 oscillator periods before releasing the oscillator clock to the system.

- **5:** TLOCK = PLL lock time (20  $\mu$ s nominal).

- **6:** TFSCM = Fail-Safe Clock Monitor delay (100 μs nominal).

#### 6.2.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) have a relatively long start-up time. Therefore, one or more of the following conditions is possible after the Reset signal is released:

- The oscillator circuit has not begun to oscillate

- The Oscillator Start-up Timer has not expired (if a crystal oscillator is used)

- The PLL has not achieved a lock (if PLL is used)

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

#### 6.2.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it begins to monitor the system clock source when the Reset signal is released. If a valid clock source is not available at this time, the device automatically switches to the FRC oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine.

#### 6.2.2.1 FSCM Delay for Crystal and PLL Clock Sources

When the system clock source is provided by a crystal oscillator and/or the PLL, a small delay, TFSCM, is automatically inserted after the POR and PWRT delay times. The FSCM does not begin to monitor the system clock source until this delay expires. The FSCM delay time is nominally 500  $\mu$ s and provides additional time for the oscillator and/or PLL to stabilize. In most cases, the FSCM delay prevents an oscillator failure trap at a device Reset when the PWRT is disabled.

## 6.3 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset, with the exception of two registers. The Reset value for the Reset Control register, RCON, depends on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, depends on the type of Reset and the programmed values of the oscillator Configuration bits in the FOSC Configuration register.

#### REGISTER 7-11: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

| bit 3 | <b>CNIE:</b> Input Change Notification Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | Unimplemented: Read as '0'                                                                                                        |

| bit 1 | MI2C1IE: I2C1 Master Events Interrupt Enable bit                                                                                  |

|       | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enabled</li></ul>                                         |

| bit 0 | SI2C1IE: I2C1 Slave Events Interrupt Enable bit                                                                                   |

|       | <ul> <li>Let e e e e e e e e e e e e e e e e e e</li></ul>                                                                        |

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

### REGISTER 7-17: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

| U-0              | R/W-1                                           | R/W-0                                                                                                                          | R/W-0          | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

|------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|--|

| —                |                                                 | U1RXIP<2:0>                                                                                                                    |                | —                |                 | SPI1IP<2:0>     |       |  |  |  |  |

| bit 15           |                                                 |                                                                                                                                |                |                  |                 |                 | bit   |  |  |  |  |

| 11.0             |                                                 | R/W-0                                                                                                                          |                | 11.0             |                 | R/W-0           |       |  |  |  |  |

| U-0              | R/W-1                                           | SPI1EIP<2:0>                                                                                                                   | R/W-0          | U-0              | R/W-1           | T3IP<2:0>       | R/W-0 |  |  |  |  |

| bit 7            |                                                 | 0111211 \2.02                                                                                                                  |                |                  |                 | 1011 \2.02      | bit   |  |  |  |  |

| 510 1            |                                                 |                                                                                                                                |                |                  |                 |                 | bit   |  |  |  |  |

| Legend:          |                                                 |                                                                                                                                |                |                  |                 |                 |       |  |  |  |  |

| R = Readabl      | e bit                                           | W = Writable                                                                                                                   | bit            | U = Unimple      | mented bit, rea | d as '0'        |       |  |  |  |  |

| -n = Value at    | POR                                             | '1' = Bit is set                                                                                                               |                | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |  |  |  |  |

| bit 15           | Unimpleme                                       | ented: Read as '                                                                                                               | 0'             |                  |                 |                 |       |  |  |  |  |

| bit 14-12        | -                                               |                                                                                                                                |                | Prioritv bits    |                 |                 |       |  |  |  |  |

|                  |                                                 | <b>U1RXIP&lt;2:0&gt;:</b> UART1 Receiver Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                |                  |                 |                 |       |  |  |  |  |

|                  | •                                               |                                                                                                                                |                |                  |                 |                 |       |  |  |  |  |

|                  | •                                               |                                                                                                                                |                |                  |                 |                 |       |  |  |  |  |

|                  | 001 = Inter                                     | rupt is priority 1                                                                                                             |                |                  |                 |                 |       |  |  |  |  |

|                  |                                                 | rupt source is dis                                                                                                             | abled          |                  |                 |                 |       |  |  |  |  |

| bit 11           | Unimpleme                                       | ented: Read as '                                                                                                               | 0'             |                  |                 |                 |       |  |  |  |  |

| bit 10-8         | SPI1IP<2:0>: SPI1 Event Interrupt Priority bits |                                                                                                                                |                |                  |                 |                 |       |  |  |  |  |

|                  | 111 = Inter                                     | rupt is priority 7 (                                                                                                           | highest priori | ty interrupt)    |                 |                 |       |  |  |  |  |

|                  | •                                               |                                                                                                                                |                |                  |                 |                 |       |  |  |  |  |

|                  | •                                               |                                                                                                                                |                |                  |                 |                 |       |  |  |  |  |

|                  |                                                 | rupt is priority 1<br>rupt source is dis                                                                                       | abled          |                  |                 |                 |       |  |  |  |  |

| bit 7            |                                                 | ented: Read as '                                                                                                               |                |                  |                 |                 |       |  |  |  |  |

| bit 6-4          | -                                               | :0>: SPI1 Error II                                                                                                             |                | ty bits          |                 |                 |       |  |  |  |  |

|                  |                                                 | rupt is priority 7 (                                                                                                           | -              | -                |                 |                 |       |  |  |  |  |

|                  | •                                               |                                                                                                                                |                |                  |                 |                 |       |  |  |  |  |

|                  | •                                               |                                                                                                                                |                |                  |                 |                 |       |  |  |  |  |

|                  |                                                 | rupt is priority 1                                                                                                             |                |                  |                 |                 |       |  |  |  |  |

| <b>h</b> :+ 0    |                                                 | rupt source is dis                                                                                                             |                |                  |                 |                 |       |  |  |  |  |

| bit 3<br>bit 2-0 | -                                               | ented: Read as '                                                                                                               |                |                  |                 |                 |       |  |  |  |  |

| DIL 2-0          |                                                 | : Timer3 Interrupt<br>rupt is priority 7 (                                                                                     | -              | v interrunt)     |                 |                 |       |  |  |  |  |

|                  | •                                               |                                                                                                                                | riighest phon  | ly interrupt)    |                 |                 |       |  |  |  |  |

|                  | •                                               |                                                                                                                                |                |                  |                 |                 |       |  |  |  |  |

|                  | •<br>001 = Inter                                | muchic criteriter d                                                                                                            |                |                  |                 |                 |       |  |  |  |  |

|                  |                                                 |                                                                                                                                |                |                  |                 |                 |       |  |  |  |  |

| U-0                           | R/W-1                                                                                                                     | R/W-0                                            | R/W-0          | U-0                             | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------|---------------------------------|------------------|-----------------|---------|--|--|--|--|

| —                             |                                                                                                                           | IC5IP<2:0>                                       |                | —                               |                  | IC4IP<2:0>      |         |  |  |  |  |

| bit 15                        |                                                                                                                           |                                                  |                |                                 |                  |                 | bit 8   |  |  |  |  |

| U-0                           | R/W-1                                                                                                                     | R/W-0                                            | R/W-0          | U-0                             | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |

|                               | N/W-1                                                                                                                     | IC3IP<2:0>                                       | FX/VV-0        |                                 | N/W-1            | DMA3IP<2:0>     | N/ VV-U |  |  |  |  |

| bit 7                         |                                                                                                                           |                                                  |                |                                 |                  |                 | bit 0   |  |  |  |  |

|                               |                                                                                                                           |                                                  |                |                                 |                  |                 |         |  |  |  |  |

| Legend:                       | - h:4                                                                                                                     |                                                  | .:4            |                                 | manufad hit va   |                 |         |  |  |  |  |

| R = Readable<br>-n = Value at |                                                                                                                           | W = Writable k<br>'1' = Bit is set               | JIL            | 0 = Onimple<br>'0' = Bit is cle | mented bit, rea  | x = Bit is unkn | own     |  |  |  |  |

|                               | TOR                                                                                                                       |                                                  |                |                                 | arcu             |                 | lowin   |  |  |  |  |

| bit 15                        | Unimpleme                                                                                                                 | nted: Read as '0                                 | )'             |                                 |                  |                 |         |  |  |  |  |

| bit 14-12                     | IC5IP<2:0>:                                                                                                               | Input Capture C                                  | hannel 5 Inte  | errupt Priority b               | oits             |                 |         |  |  |  |  |

|                               | 111 = Interr                                                                                                              | upt is priority 7 (h                             | nighest priori | ty interrupt)                   |                  |                 |         |  |  |  |  |

|                               | •                                                                                                                         |                                                  |                |                                 |                  |                 |         |  |  |  |  |

|                               | •                                                                                                                         |                                                  |                |                                 |                  |                 |         |  |  |  |  |

|                               |                                                                                                                           | upt is priority 1<br>upt source is disa          | abled          |                                 |                  |                 |         |  |  |  |  |

| bit 11                        |                                                                                                                           | nted: Read as '0                                 |                |                                 |                  |                 |         |  |  |  |  |

| bit 10-8                      | IC4IP<2:0>: Input Capture Channel 4 Interrupt Priority bits                                                               |                                                  |                |                                 |                  |                 |         |  |  |  |  |

|                               | 111 = Interrupt is priority 7 (highest priority interrupt)                                                                |                                                  |                |                                 |                  |                 |         |  |  |  |  |

|                               | •                                                                                                                         |                                                  |                |                                 |                  |                 |         |  |  |  |  |

|                               | •                                                                                                                         |                                                  |                |                                 |                  |                 |         |  |  |  |  |

|                               | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                       |                                                  |                |                                 |                  |                 |         |  |  |  |  |

| bit 7                         |                                                                                                                           | nted: Read as '0                                 |                |                                 |                  |                 |         |  |  |  |  |

| bit 6-4                       | -                                                                                                                         |                                                  |                | errunt Priority h               | nite             |                 |         |  |  |  |  |

|                               | IC3IP<2:0>: Input Capture Channel 3 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                                                  |                |                                 |                  |                 |         |  |  |  |  |

|                               | •                                                                                                                         |                                                  |                |                                 |                  |                 |         |  |  |  |  |

|                               |                                                                                                                           |                                                  |                |                                 |                  |                 |         |  |  |  |  |

|                               | 001 = Interrupt is priority 1                                                                                             |                                                  |                |                                 |                  |                 |         |  |  |  |  |

|                               |                                                                                                                           | upt source is disa                               |                |                                 |                  |                 |         |  |  |  |  |

| bit 3                         | -                                                                                                                         | nted: Read as '0                                 |                |                                 |                  | 10 L 10 L       |         |  |  |  |  |

| bit 2-0                       |                                                                                                                           | <b>0&gt;:</b> DMA Channe<br>upt is priority 7 (h |                | -                               | e Interrupt Pric | ority bits      |         |  |  |  |  |

|                               | •                                                                                                                         |                                                  | lighest phon   | iy interrupt)                   |                  |                 |         |  |  |  |  |

|                               | •                                                                                                                         |                                                  |                |                                 |                  |                 |         |  |  |  |  |

|                               | •                                                                                                                         |                                                  |                |                                 |                  |                 |         |  |  |  |  |

|                               | 001 = Interr                                                                                                              | upt is priority 1                                |                |                                 |                  |                 |         |  |  |  |  |

#### REGISTER 7-24: IPC9: INTERRUPT PRIORITY CONTROL REGISTER 9

| R/W-0         | U-0                                                                                                         | R/W-0                                           | U-0        | U-0              | U-0              | U-0             | U-0 |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------|------------------|------------------|-----------------|-----|--|--|--|

| TON           |                                                                                                             | TSIDL                                           | —          | _                | _                | _               | _   |  |  |  |

| bit 15        |                                                                                                             |                                                 |            |                  |                  |                 | bit |  |  |  |

|               |                                                                                                             |                                                 |            |                  |                  |                 |     |  |  |  |

| U-0           | R/W-0                                                                                                       | R/W-0                                           | R/W-0      | U-0              | R/W-0            | R/W-0           | U-0 |  |  |  |

| _             | TGATE                                                                                                       | TCKP                                            | S<1:0>     | —                | TSYNC            | TCS             | —   |  |  |  |

| bit 7         |                                                                                                             |                                                 |            |                  |                  |                 | bit |  |  |  |

| Legend:       |                                                                                                             |                                                 |            |                  |                  |                 |     |  |  |  |

| R = Readabl   | e bit                                                                                                       | W = Writable                                    | bit        | U = Unimple      | mented bit, read | l as '0'        |     |  |  |  |

| -n = Value at | POR                                                                                                         | '1' = Bit is set                                | t          | '0' = Bit is cle | eared            | x = Bit is unkn | own |  |  |  |

|               |                                                                                                             |                                                 |            |                  |                  |                 |     |  |  |  |

| bit 15        | TON: Timer1                                                                                                 | On bit                                          |            |                  |                  |                 |     |  |  |  |

|               | 1 = Starts 16                                                                                               | -bit Timer1                                     |            |                  |                  |                 |     |  |  |  |

|               | 0 = Stops 16                                                                                                | -bit Timer1                                     |            |                  |                  |                 |     |  |  |  |

| bit 14        | Unimplemer                                                                                                  | nted: Read as '                                 | 0'         |                  |                  |                 |     |  |  |  |

| bit 13        | TSIDL: Stop in Idle Mode bit                                                                                |                                                 |            |                  |                  |                 |     |  |  |  |

|               |                                                                                                             | nue module ope<br>e module operat               |            |                  | dle mode         |                 |     |  |  |  |

| bit 12-7      | Unimplemer                                                                                                  | nted: Read as '                                 | 0'         |                  |                  |                 |     |  |  |  |

| bit 6         | TGATE: Timer1 Gated Time Accumulation Enable bit                                                            |                                                 |            |                  |                  |                 |     |  |  |  |

|               | <u>When TCS = 1:</u><br>This bit is ignored.                                                                |                                                 |            |                  |                  |                 |     |  |  |  |

|               |                                                                                                             | <u>: 0:</u><br>ne accumulatio<br>ne accumulatio |            |                  |                  |                 |     |  |  |  |

| bit 5-4       | TCKPS<1:0>: Timer1 Input Clock Prescale Select bits                                                         |                                                 |            |                  |                  |                 |     |  |  |  |

|               | 11 = 1:256                                                                                                  |                                                 |            |                  |                  |                 |     |  |  |  |

|               | 10 = 1:64                                                                                                   |                                                 |            |                  |                  |                 |     |  |  |  |

|               | 01 = 1:8<br>00 = 1:1                                                                                        |                                                 |            |                  |                  |                 |     |  |  |  |

| L:1 0         |                                                                                                             | stad. Daad as '                                 | 0'         |                  |                  |                 |     |  |  |  |

| bit 3         | -                                                                                                           | Unimplemented: Read as '0'                      |            |                  |                  |                 |     |  |  |  |

| bit 2         | TSYNC: Timer1 External Clock Input Synchronization Select bit                                               |                                                 |            |                  |                  |                 |     |  |  |  |

|               | <u>When TCS = 1:</u><br>1 = Synchronize external clock input<br>0 = Do not synchronize external clock input |                                                 |            |                  |                  |                 |     |  |  |  |

|               | <u>When TCS = 0:</u><br>This bit is ignored.                                                                |                                                 |            |                  |                  |                 |     |  |  |  |

| bit 1         | TCS: Timer1                                                                                                 | Clock Source                                    | Select bit |                  |                  |                 |     |  |  |  |

|               | <b>TCS:</b> Timer1 Clock Source Select bit<br>1 = External clock from pin T1CK (on the rising edge)         |                                                 |            |                  |                  |                 |     |  |  |  |

|               | 0 = Internal o                                                                                              |                                                 | - (        | 3 - 3 - 9        |                  |                 |     |  |  |  |

## 13.0 TIMER2/3, TIMER4/5, TIMER6/7 AND TIMER8/9

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 11. "Timers" (DS70205) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer2/3, Timer4/5, Timer6/7 and Timer8/9 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As a 32-bit timer, Timer2/3, Timer4/5, Timer6/7 and Timer8/9 operate in three modes:

- Two Independent 16-bit Timers (e.g., Timer2 and Timer3) with all 16-bit operating modes (except Asynchronous Counter mode)

- Single 32-bit Timer

- Single 32-bit Synchronous Counter

They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- Interrupt on a 32-bit Period Register Match

- Time Base for Input Capture and Output Compare Modules (Timer2 and Timer3 only)

- ADC1 Event Trigger (Timer2/3 only)

- ADC2 Event Trigger (Timer4/5 only)

Individually, all eight of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed above, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON, T5CON, T6CON, T7CON, T8CON and T9CON registers. T2CON, T4CON, T6CON and T8CON are shown in generic form in Register 13-1. T3CON, T5CON, T7CON and T9CON are shown in Register 13-2. For 32-bit timer/counter operation, Timer2, Timer4, Timer6 or Timer8 is the least significant word; Timer3, Timer5, Timer7 or Timer9 is the most significant word of the 32-bit timers.

| Note: | For 32-bit operation, T3CON, T5CON,         |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|

|       | T7CON and T9CON control bits are            |  |  |  |  |  |  |

|       | ignored. Only T2CON, T4CON, T6CON           |  |  |  |  |  |  |

|       | and T8CON control bits are used for setup   |  |  |  |  |  |  |

|       | and control. Timer2, Timer4, Timer6 and     |  |  |  |  |  |  |

|       | Timer8 clock and gate inputs are utilized   |  |  |  |  |  |  |

|       | for the 32-bit timer modules, but an inter- |  |  |  |  |  |  |

|       | rupt is generated with the Timer3, Timer5,  |  |  |  |  |  |  |

|       | Ttimer7 and Timer9 interrupt flags.         |  |  |  |  |  |  |

To configure Timer2/3, Timer4/5, Timer6/7 or Timer8/9 for 32-bit operation:

- 1. Set the corresponding T32 control bit.

- 2. Select the prescaler ratio for Timer2, Timer4, Timer6 or Timer8 using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the corresponding TCS and TGATE bits.

- 4. Load the timer period value. PR3, PR5, PR7 or PR9 contains the most significant word of the value, while PR2, PR4, PR6 or PR8 contains the least significant word.

- 5. If interrupts are required, set the interrupt enable bit, T3IE, T5IE, T7IE or T9IE. Use the priority bits, T3IP<2:0>, T5IP<2:0>, T7IP<2:0> or T9IP<2:0>, to set the interrupt priority. While Timer2, Timer4, Timer6 or Timer8 control the timer, the interrupt appears as a Timer3, Timer5, Timer7 or Timer9 interrupt.

- 6. Set the corresponding TON bit.

The timer value at any point is stored in the register pair, TMR3:TMR2, TMR5:TMR4, TMR7:TMR6 or TMR9:TMR8. TMR3, TMR5, TMR7 or TMR9 always contains the most significant word of the count, while TMR2, TMR4, TMR6 or TMR8 contains the least significant word.

To configure any of the timers for individual 16-bit operation:

- 1. Clear the T32 bit corresponding to that timer.

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the interrupt enable bit, TxIE. Use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON bit.

## 15.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual", Section 13. "Output Compare" (DS70209), which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The output compare module can select either Timer2 or Timer3 for its time base. The module compares the value of the timer with the value of one or two Compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the Compare register value. The output compare module generates either a single output pulse, or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events.

The output compare module has multiple operating modes:

- Active-Low One-Shot mode

- Active-High One-Shot mode

- Toggle mode

- · Delayed One-Shot mode

- Continuous Pulse mode

- PWM mode without Fault Protection

- PWM mode with Fault Protection

## FIGURE 15-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

#### 16.1 SPI Helpful Tips

- 1. In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPIxCON2<13>) = 1, use a pull-down resistor on SSx.

- b) If FRMPOL = 0, use a pull-up resistor on  $\overline{SSx}$ .

| Note: | This           | insures               | that  | the        | first | fr | ame |

|-------|----------------|-----------------------|-------|------------|-------|----|-----|

|       | transmission a |                       | after | initializa | ation | is | not |

|       | shifte         | shifted or corrupted. |       |            |       |    |     |

- 2. In non-framed 3-wire mode, (i.e., not using SSx from a master):

- a) If CKP (SPIxCON1<6>) = 1, always place a pull-up resistor on SSx.

- b) If CKP = 0, always place a pull-down resistor on  $\overline{SSx}$ .

- **Note:** This will insure that during power-up and initialization the master/slave will not lose sync due to an errant SCK transition that would cause the slave to accumulate data shift errors for both transmit and receive appearing as corrupted data.

- FRMEN (SPIxCON2<15>) = 1 and SSEN (SPIxCON1<7>) = 1 are exclusive and invalid. In Frame mode, SCKx is continuous and the Frame sync pulse is active on the SSx pin, which indicates the start of a data frame.

| Note: | Not all third-party devices support Frame |

|-------|-------------------------------------------|

|       | mode timing. Refer to the SPI electrical  |

|       | characteristics for details.              |

- In Master mode only, set the SMP bit (SPIxCON1<9>) to a '1' for the fastest SPI data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPIxCON1<5>) is set.

- 5. To avoid invalid slave read data to the master, the user's master software must guarantee enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPIxBUF transmit register in advance of the next master transaction cycle. SPIxBUF is transferred to the SPI shift register and is empty once the data transmission begins.

## 16.2 SPI Resources

Many useful resources related to SPI are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en546061                                        |

#### 16.2.1 KEY RESOURCES

- Section 18. "Serial Peripheral Interface (SPI)" (DS70206)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

#### REGISTER 19-2: CiCTRL2: ECAN™ MODULE CONTROL REGISTER 2

| U-0          | U-0                | U-0                               | U-0             | U-0                                | U-0        | U-0                | U-0   |  |  |  |  |

|--------------|--------------------|-----------------------------------|-----------------|------------------------------------|------------|--------------------|-------|--|--|--|--|

| _            | _                  | _                                 | _               | —                                  | —          |                    | —     |  |  |  |  |

| bit 15       |                    |                                   |                 |                                    |            |                    | bit 8 |  |  |  |  |

|              |                    |                                   |                 |                                    |            |                    |       |  |  |  |  |

| U-0          | U-0                | U-0                               | R-0             | R-0                                | R-0        | R-0                | R-0   |  |  |  |  |

| —            | —                  |                                   |                 |                                    | DNCNT<4:0> |                    |       |  |  |  |  |

| bit 7        |                    |                                   |                 |                                    |            |                    | bit 0 |  |  |  |  |

|              |                    |                                   |                 |                                    |            |                    |       |  |  |  |  |

| Legend:      |                    |                                   |                 |                                    |            |                    |       |  |  |  |  |

| R = Readab   | le bit             | W = Writable                      | bit             | U = Unimplemented bit, read as '0' |            |                    |       |  |  |  |  |

| -n = Value a | t POR              | '1' = Bit is set                  | t               | '0' = Bit is cleared               |            | x = Bit is unknown |       |  |  |  |  |

|              |                    |                                   |                 |                                    |            |                    |       |  |  |  |  |

| bit 15-5     | Unimplemen         | ted: Read as '                    | 0'              |                                    |            |                    |       |  |  |  |  |

| bit 4-0      | DNCNT<4:0>         | : DeviceNet™                      | Filter Bit Num  | ber bits                           |            |                    |       |  |  |  |  |

|              | 10010-1111         | 10010-11111 = Invalid selection   |                 |                                    |            |                    |       |  |  |  |  |

|              | 10001 <b>= Con</b> | npare up to dat                   | a byte 3, bit 6 | with EID<17>                       |            |                    |       |  |  |  |  |

|              | •                  |                                   |                 |                                    |            |                    |       |  |  |  |  |

|              | •                  |                                   |                 |                                    |            |                    |       |  |  |  |  |

|              | •                  |                                   |                 |                                    |            |                    |       |  |  |  |  |

|              |                    | npare up to dat<br>not compare da | -               | with EID<0>                        |            |                    |       |  |  |  |  |

| U-0          | U-0                          | U-0                    | R-0       | R-0             | R-0            | R-0             | R-0  |  |  |

|--------------|------------------------------|------------------------|-----------|-----------------|----------------|-----------------|------|--|--|

| _            | —                            | —                      |           |                 | FILHIT<4:      | 0>              |      |  |  |

| bit 15       | ·                            |                        |           |                 |                |                 | bit  |  |  |

|              |                              |                        |           |                 |                |                 |      |  |  |

| U-0          | R-1                          | R-0                    | R-0       | R-0             | R-0            | R-0             | R-0  |  |  |

|              |                              |                        |           | ICODE<6:0       | >              |                 |      |  |  |

| bit 7        |                              |                        |           |                 |                |                 | bit  |  |  |

| Legend:      |                              |                        |           |                 |                |                 |      |  |  |

| R = Readab   | le bit                       | W = Writable           | bit       | U = Unimple     | mented bit, re | ead as '0'      |      |  |  |

| -n = Value a | t POR                        | '1' = Bit is set       | :         | '0' = Bit is cl | eared          | x = Bit is unkr | nown |  |  |

| bit 15-13    | Unimplement                  | t <b>ed:</b> Read as ' | 0'        |                 |                |                 |      |  |  |

| bit 12-8     | FILHIT<4:0>:                 |                        |           |                 |                |                 |      |  |  |

|              | 10000-1111:                  |                        |           |                 |                |                 |      |  |  |

|              | 01111 = Filter               | r 15                   |           |                 |                |                 |      |  |  |

|              | •                            |                        |           |                 |                |                 |      |  |  |

|              | •                            |                        |           |                 |                |                 |      |  |  |

|              | 00001 = Filter 1             |                        |           |                 |                |                 |      |  |  |

|              | 00000 = Filter               |                        |           |                 |                |                 |      |  |  |

| bit 7        | Unimplement                  | ted: Read as '         | 0'        |                 |                |                 |      |  |  |

| bit 6-0      | ICODE<6:0>:                  | Interrupt Flag         | Code bits |                 |                |                 |      |  |  |

|              | 1000101-11                   |                        |           |                 |                |                 |      |  |  |

|              | 1000100 = FI<br>1000011 = Re |                        |           |                 |                |                 |      |  |  |

|              | 1000010 <b>=</b> W           | /ake-up interru        |           |                 |                |                 |      |  |  |

|              | 1000001 = Er                 |                        |           |                 |                |                 |      |  |  |

|              | 1000000 <b>= N</b>           | omenupi                |           |                 |                |                 |      |  |  |

|              | 0010000-013                  |                        |           |                 |                |                 |      |  |  |

|              | 0001111 <b>= R</b> I         | B15 buffer Inte        | errupt    |                 |                |                 |      |  |  |

|              | •                            |                        |           |                 |                |                 |      |  |  |

|              | •                            |                        |           |                 |                |                 |      |  |  |

|              | 0001001 <b>= R</b> I         | B9 buffer inter        | rupt      |                 |                |                 |      |  |  |

|              | 0001000 <b>= R</b>           | B8 buffer inter        | rupt      |                 |                |                 |      |  |  |

|              | 0000111 = TF                 |                        |           |                 |                |                 |      |  |  |

|              | 0000110 = TF<br>0000101 = TF |                        |           |                 |                |                 |      |  |  |

|              | 0000100 = TF                 |                        |           |                 |                |                 |      |  |  |

|              | 0000011 = TF                 |                        |           |                 |                |                 |      |  |  |

|              | 0000010 = TF<br>0000001 = TF |                        |           |                 |                |                 |      |  |  |

|              |                              | RB0 Buffer inte        |           |                 |                |                 |      |  |  |

## REGISTER 19-3: CiVEC: ECAN™ MODULE INTERRUPT CODE REGISTER

## 20.6 ADC Control Registers

## **REGISTER 20-1:** ADxCON1: ADCx CONTROL REGISTER 1(where x = 1 or 2)

| R/W-0  | U-0       | R/W-0  | R/W-0   | U-0    | R/W-0 | R/W-0 | R/W-0  |

|--------|-----------|--------|---------|--------|-------|-------|--------|

| ADON   | _         | ADSIDL | ADDMABM |        | AD12B | FORM  | 1<1:0> |

| bit 15 |           |        |         |        |       |       | bit 8  |

|        |           |        |         |        |       |       |        |

| R/W-0  | R/W-0     | R/W-0  | U-0     | R/W-0  | R/W-0 | R/W-0 | R/C-0  |

|        |           |        |         |        |       | HC,HS | HC, HS |

|        | SSRC<2:0> |        | —       | SIMSAM | ASAM  | SAMP  | DONE   |

| bit 7  |           |        |         |        |       |       | bit 0  |

| Legend:           | HC = Cleared by hardware |                            |                    |

|-------------------|--------------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15  | ADON: ADC Operating Mode bit                                                                                                                                                                                   |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = ADC module is operating                                                                                                                                                                                    |

|         | 0 = ADC module is off                                                                                                                                                                                          |

| bit 14  | Unimplemented: Read as '0'                                                                                                                                                                                     |

| bit 13  | ADSIDL: Stop in Idle Mode bit                                                                                                                                                                                  |

|         | 1 = Discontinue module operation when device enters Idle mode                                                                                                                                                  |

|         | 0 = Continue module operation in Idle mode                                                                                                                                                                     |

| bit 12  | ADDMABM: DMA Buffer Build Mode bit                                                                                                                                                                             |

|         | 1 = DMA buffers are written in the order of conversion. The module will provide an address to the DMA channel that is the same as the address used for the non-DMA stand-alone buffer                          |

|         | <ul> <li>DMA buffers are written in Scatter/Gather mode. The module will provide a scatter/gather address to the DMA channel, based on the index of the analog input and the size of the DMA buffer</li> </ul> |

| bit 11  | Unimplemented: Read as '0'                                                                                                                                                                                     |

| bit 10  | AD12B: 10-Bit or 12-Bit Operation Mode bit                                                                                                                                                                     |

|         | 1 = 12-bit, 1-channel ADC operation                                                                                                                                                                            |

|         | 0 = 10-bit, 4-channel ADC operation                                                                                                                                                                            |

| bit 9-8 | FORM<1:0>: Data Output Format bits                                                                                                                                                                             |

|         | For 10-bit operation:                                                                                                                                                                                          |

|         | 11 = Reserved                                                                                                                                                                                                  |

|         | 10 = Reserved                                                                                                                                                                                                  |

|         | 01 = Signed integer (Dout = ssss sssd dddd dddd, where s = .NOT.d<9>)<br>00 = Integer (Dout = 0000 00dd dddd dddd)                                                                                             |

|         | For 12-bit operation:                                                                                                                                                                                          |

|         | 11 = Reserved                                                                                                                                                                                                  |

|         | 10 = Reserved                                                                                                                                                                                                  |

|         | 01 = Signed Integer (DOUT = ssss sddd dddd dddd, where s = .NOT.d<11>)                                                                                                                                         |

|         | 00 = Integer (DOUT = 0000  dddd  dddd  dddd)                                                                                                                                                                   |

| bit 7-5 | SSRC<2:0>: Sample Clock Source Select bits                                                                                                                                                                     |

|         | 111 = Internal counter ends sampling and starts conversion (auto-convert)                                                                                                                                      |

|         | 110 = Reserved<br>101 = Reserved                                                                                                                                                                               |

|         | 100 = GP timer (Timer5 for ADC1, Timer3 for ADC2) compare ends sampling and starts conversion                                                                                                                  |

|         | 011 = Reserved                                                                                                                                                                                                 |

|         | 010 = GP timer (Timer3 for ADC1, Timer5 for ADC2) compare ends sampling and starts conversion                                                                                                                  |

|         | 001 = Active transition on INTO pin ends sampling and starts conversion                                                                                                                                        |

|         | 000 = Clearing sample bit ends sampling and starts conversion                                                                                                                                                  |

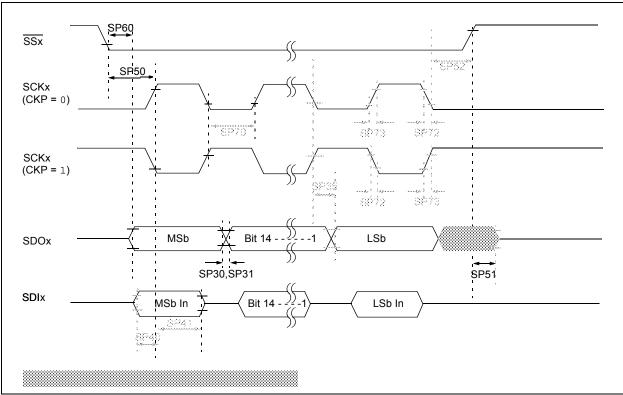

## FIGURE 24-13: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

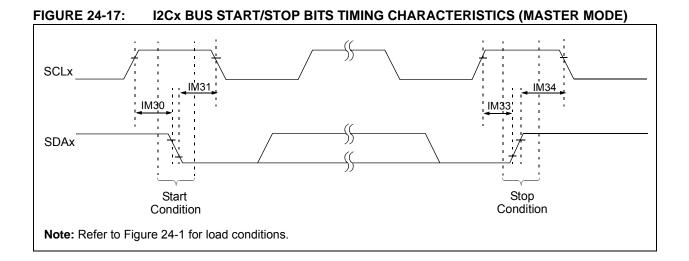

| AC CHARACTERISTICS |             |                               |                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |       |                                             |  |

|--------------------|-------------|-------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|---------------------------------------------|--|

| Param.             | Symbol      | Charac                        | teristic                  | Min                                                                                                                                                                                                                                                                                     | Max  | Units | Conditions                                  |  |

| IS10               | TLO:SCL     | Clock Low Time                | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                                     |      | μS    | Device must operate at a minimum of 1.5 MHz |  |

|                    |             |                               | 400 kHz mode              | 1.3                                                                                                                                                                                                                                                                                     | _    | μS    | Device must operate at a minimum of 10 MHz  |  |

|                    |             |                               | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                                                                                                                                                                     | —    | μS    | _                                           |  |

| IS11               | THI:SCL     | Clock High Time               | 100 kHz mode              | 4.0                                                                                                                                                                                                                                                                                     | —    | μS    | Device must operate at a minimum of 1.5 MHz |  |

|                    |             |                               | 400 kHz mode              | 0.6                                                                                                                                                                                                                                                                                     | —    | μS    | Device must operate at a minimum of 10 MHz  |  |

|                    |             |                               | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                                                                                                                                                                     | —    | μS    | _                                           |  |

| IS20               | TF:SCL      | SDAx and SCLx                 | 100 kHz mode              | —                                                                                                                                                                                                                                                                                       | 300  | ns    | CB is specified to be from                  |  |

|                    |             | Fall Time                     | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                             | 300  | ns    | 10 to 400 pF                                |  |

|                    |             |                               | 1 MHz mode <sup>(1)</sup> | —                                                                                                                                                                                                                                                                                       | 100  | ns    |                                             |  |