Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 32x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp310a-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

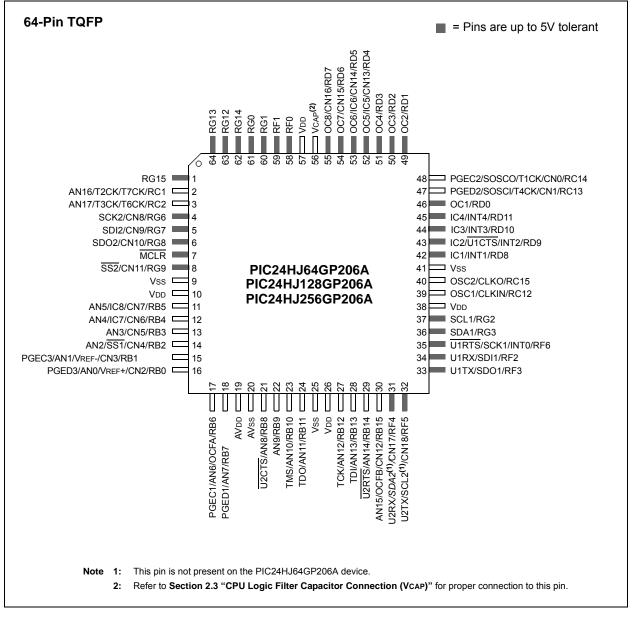

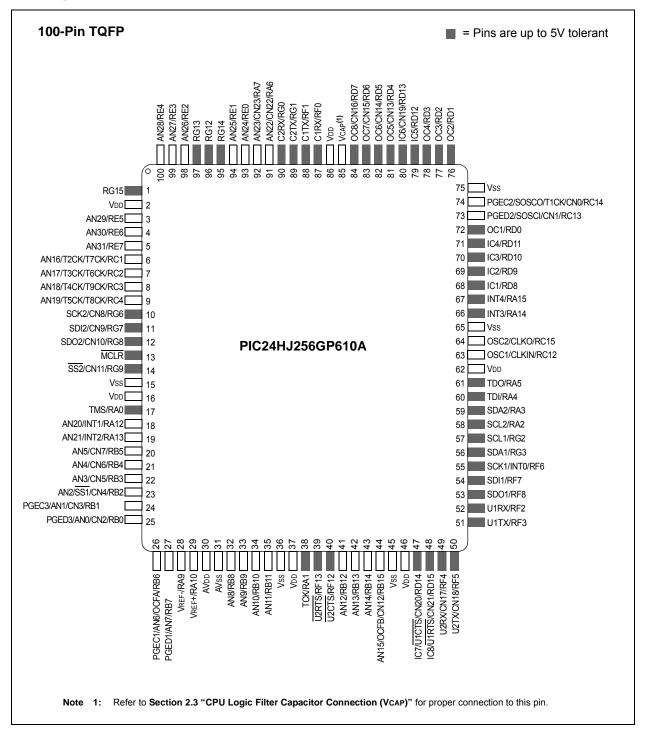

# Pin Diagrams (Continued)

### Pin Diagrams (Continued)

© 2009-2012 Microchip Technology Inc.

#### 5.4.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of program Flash memory at a time. To do this, it is necessary to erase the 8-row erase page that contains the desired row. The general process is:

- 1. Read eight rows of program memory (512 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase the page (see Example 5-1):

- a) Set the NVMOP bits (NVMCON<3:0>) to '0010' to configure for block erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the page to be erased into the TBLPAG and W registers.

- Perform a dummy table write operation (TBLWTL) to any address within the page that needs to be erased.

- d) Write 0x55 to NVMKEY.

- e) Write 0xAA to NVMKEY.

- f) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 64 instructions from data RAM into the program memory buffers (see Example 5-2).

- 5. Write the program block to Flash memory:

- a) Set the NVMOP bits to '0001' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 0x55 to NVMKEY.

- c) Write 0xAA to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

- Repeat steps 4 and 5, using the next available 64 instructions from the block in data RAM by incrementing the value in TBLPAG, until all 512 instructions are written back to Flash memory.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-3.

### EXAMPLE 5-1: ERASING A PROGRAM MEMORY PAGE

| ; Set up NVMCON for block erase operation |                                         |

|-------------------------------------------|-----------------------------------------|

| MOV #0x4042, W0                           | i                                       |

| MOV W0, NVMCON                            | ; Initialize NVMCON                     |

| ; Init pointer to row to be ERASED        |                                         |

| MOV #tblpage(PROG_ADDR), W0               | ;                                       |

| MOV W0, TBLPAG                            | ; Initialize PM Page Boundary SFR       |

| MOV #tbloffset(PROG_ADDR), W0             | ; Initialize in-page EA<15:0> pointer   |

| TBLWTL W0, [W0]                           | ; Set base address of erase block       |

| DISI #5                                   | ; Block all interrupts with priority <7 |

|                                           | ; for next 5 instructions               |

| MOV #0x55, W0                             |                                         |

| MOV W0, NVMKEY                            | ; Write the 55 key                      |

| MOV #0xAA, W1                             | ;                                       |

| MOV W1, NVMKEY                            | ; Write the AA key                      |

| BSET NVMCON, #WR                          | ; Start the erase sequence              |

| NOP                                       | ; Insert two NOPs after the erase       |

| NOP                                       | ; command is asserted                   |

|                                           |                                         |

Note: A program memory page erase operation is set up by performing a dummy table write (TBLWTL) operation to any address within the page. This methodology is different from the page erase operation on dsPIC30F/33F devices in which the erase page was selected using a dedicated pair of registers (NVMADRU and NVMADR).

| Flag Bit          | Setting Event                                        | Clearing Event               |

|-------------------|------------------------------------------------------|------------------------------|

| TRAPR (RCON<15>)  | Trap conflict event                                  | POR, BOR                     |

| IOPUWR (RCON<14>) | Illegal opcode or uninitialized<br>W register access | POR, BOR                     |

| EXTR (RCON<7>)    | MCLR Reset                                           | POR                          |

| SWR (RCON<6>)     | RESET instruction                                    | POR, BOR                     |

| WDTO (RCON<4>)    | WDT time-out                                         | PWRSAV instruction, POR, BOR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP instruction                            | POR, BOR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE instruction                             | POR, BOR                     |

| BOR (RCON<1>)     | BOR, POR                                             | _                            |

| POR (RCON<0>)     | POR                                                  | _                            |

#### TABLE 6-1:RESET FLAG BIT OPERATION

Note: All Reset flag bits may be set or cleared by the user software.

# 6.1 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen, as shown in Table 6-2. If clock switching is disabled, the system clock source is always selected according to the oscillator Configuration bits. Refer to **Section 9.0** "Oscillator Configuration" for further details.

# TABLE 6-2:OSCILLATOR SELECTION vs.TYPE OF RESET (CLOCK<br/>SWITCHING ENABLED)

| Reset Type | Clock Source Determinant      |

|------------|-------------------------------|

| POR        | Oscillator Configuration bits |

| BOR        | (FNOSC<2:0>)                  |

| MCLR       | COSC Control bits             |

| WDTR       | (OSCCON<14:12>)               |

| SWR        | ]                             |

# 6.2 Device Reset Times

The Reset times for various types of device Reset are summarized in Table 6-3. The system Reset signal is released after the POR and PWRT delay times expire.

The time at which the device actually begins to execute code also depends on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable reset delay times.

The FSCM delay determines the time at which the FSCM begins to monitor the system clock source after the reset signal is released.

# REGISTER 7-10: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

| bit 2 | <b>OC1IE:</b> Output Compare Channel 1 Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>IC1IE:</b> Input Capture Channel 1 Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled  |

| bit 0 | INTOIE: External Interrupt 0 Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled                     |

#### REGISTER 8-2: DMAxREQ: DMA CHANNEL x IRQ SELECT REGISTER

| R/W-0                | U-0   |

|----------------------|-----|-----|-----|-----|-----|-----|-------|

| FORCE <sup>(1)</sup> | —   | —   | —   | —   | —   | —   | —     |

| bit 15               |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0      | R/W-0                  | R/W-0      | R/W-0      |

|-------|------------------------|------------------------|------------------------|------------|------------------------|------------|------------|

| —     | IRQSEL6 <sup>(2)</sup> | IRQSEL5 <sup>(2)</sup> | IRQSEL4 <sup>(2)</sup> | IRQSEL3(2) | IRQSEL2 <sup>(2)</sup> | IRQSEL1(2) | IRQSEL0(2) |

| bit 7 |                        |                        |                        |            |                        |            | bit 0      |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 **FORCE:** Force DMA Transfer bit<sup>(1)</sup>

1 = Force a single DMA transfer (Manual mode)

0 = Automatic DMA transfer initiation by DMA request

bit 14-7 Unimplemented: Read as '0'

- bit 6-0 IRQSEL<6:0>: DMA Peripheral IRQ Number Select bits<sup>(2)</sup> 0000000-1111111 = DMAIRQ0-DMAIRQ127 selected to be Channel DMAREQ

- **Note 1:** The FORCE bit cannot be cleared by the user. The FORCE bit is cleared by hardware when the forced DMA transfer is complete.

2: Please see Table 8-1 for a complete listing of IRQ numbers for all interrupt sources.

### REGISTER 16-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- bit 4-2 SPRE<2:0>: Secondary Prescale bits (Master mode)<sup>(2)</sup>

- 111 = Secondary prescale 1:1

- 110 = Secondary prescale 2:1

- •

- •

- 000 = Secondary prescale 8:1

- bit 1-0 **PPRE<1:0>:** Primary Prescale bits (Master mode)<sup>(2)</sup>

- 11 = Primary prescale 1:1

- 10 = Primary prescale 4:1

- 01 = Primary prescale 16:1

- 00 = Primary prescale 64:1

- **Note 1:** The CKE bit is not used in the Framed SPI modes. The user should program this bit to '0' for the Framed SPI modes (FRMEN = 1).

- **2:** Do not set both Primary and Secondary prescalers to a value of 1:1.

- **3:** This bit must be cleared when FRMEN = 1.

# 17.2 <sup>2</sup>C Resources

Many useful resources related to  $I^2C$  are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the<br>product page using the link above, enter |

|-------|-----------------------------------------------------------------------------------------|

|       |                                                                                         |

|       | this URL in your browser:                                                               |

|       | http://www.microchip.com/wwwproducts/                                                   |

|       | Devices.aspx?dDocName=en546061                                                          |

### 17.2.1 KEY RESOURCES

- Section 11. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

# 17.3 I<sup>2</sup>C Registers

I2CxCON and I2CxSTAT are control and status registers, respectively. The I2CxCON register is readable and writable. The lower six bits of I2CxSTAT are read-only. The remaining bits of the I2CSTAT are read/write.

I2CxRSR is the shift register used for shifting data, whereas I2CxRCV is the buffer register to which data bytes are written, or from which data bytes are read. I2CxRCV is the receive buffer. I2CxTRN is the transmit register to which bytes are written during a transmit operation.

The I2CxADD register holds the slave address. A status bit, ADD10, indicates 10-bit Address mode. The I2CxBRG acts as the Baud Rate Generator (BRG) reload value.

In receive operations, I2CxRSR and I2CxRCV together form a double-buffered receiver. When I2CxRSR receives a complete byte, it is transferred to I2CxRCV and an interrupt pulse is generated.

| U-0                                                    | U-0                | R/W-0            | R/W-0         | r-0               | R/W-1            | R/W-0           | R/W-0 |  |  |  |

|--------------------------------------------------------|--------------------|------------------|---------------|-------------------|------------------|-----------------|-------|--|--|--|

| _                                                      | _                  | CSIDL            | ABAT          |                   |                  | REQOP<2:0>      |       |  |  |  |

| bit 15                                                 |                    |                  |               |                   |                  |                 | bit   |  |  |  |

| P_1                                                    | P_0                | P.0              | 11-0          | P/M/O             | 11-0             | 11-0            | R/W-0 |  |  |  |

|                                                        |                    |                  | 0-0           | -                 | 0-0              | 0-0             | WIN   |  |  |  |

| -       -       CSIDL       ABAT       -       REQOP<2 |                    | _                | bit           |                   |                  |                 |       |  |  |  |

|                                                        |                    |                  |               |                   |                  |                 |       |  |  |  |

| Legend:                                                |                    | r = Bit is Res   | erved         |                   |                  |                 |       |  |  |  |

| R = Readable b                                         | bit                | W = Writable     | bit           | U = Unimplen      | nented bit, read | l as '0'        |       |  |  |  |

| -n = Value at P                                        | OR                 | '1' = Bit is se  | t             | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |  |  |  |

| bit 15-14                                              | Unimpleme          | nted: Read as    | 0'            |                   |                  |                 |       |  |  |  |

| bit 13                                                 | CSIDL: Sto         | p in Idle Mode b | bit           |                   |                  |                 |       |  |  |  |

|                                                        |                    | •                |               |                   | e mode           |                 |       |  |  |  |

|                                                        |                    | -                |               |                   |                  |                 |       |  |  |  |

| bit 12                                                 | -                  |                  |               |                   |                  |                 |       |  |  |  |

|                                                        | •                  |                  |               |                   | borted           |                 |       |  |  |  |

| bit 11                                                 |                    |                  |               |                   |                  |                 |       |  |  |  |

| bit 10-8                                               |                    |                  |               |                   |                  |                 |       |  |  |  |

|                                                        |                    |                  |               |                   |                  |                 |       |  |  |  |

|                                                        |                    |                  |               |                   |                  |                 |       |  |  |  |

|                                                        |                    |                  |               |                   |                  |                 |       |  |  |  |

|                                                        |                    |                  |               |                   |                  |                 |       |  |  |  |

|                                                        |                    |                  |               |                   |                  |                 |       |  |  |  |

|                                                        |                    |                  |               |                   |                  |                 |       |  |  |  |

|                                                        | 000 <b>= Set N</b> | ormal Operation  | n mode        |                   |                  |                 |       |  |  |  |

| bit 7-5                                                | OPMODE<2           | 2:0>: Operation  | Mode bits     |                   |                  |                 |       |  |  |  |

|                                                        |                    |                  | ll Messages n | node              |                  |                 |       |  |  |  |

|                                                        |                    |                  |               |                   |                  |                 |       |  |  |  |

|                                                        |                    |                  | ation mode    |                   |                  |                 |       |  |  |  |

|                                                        |                    |                  |               |                   |                  |                 |       |  |  |  |

|                                                        | 010 = Modu         | le is in Loopbac | k mode        |                   |                  |                 |       |  |  |  |

|                                                        |                    |                  |               | do.               |                  |                 |       |  |  |  |

| bit 4                                                  |                    |                  | -             |                   |                  |                 |       |  |  |  |

|                                                        | -                  |                  |               | Capture Event     | Enable bit       |                 |       |  |  |  |

|                                                        | 1 = Enable i       | nput capture ba  |               | -                 |                  |                 |       |  |  |  |

| bit 2-1                                                |                    | •                | 0'            |                   |                  |                 |       |  |  |  |

| bit 0                                                  | •                  |                  |               |                   |                  |                 |       |  |  |  |

|                                                        | 1 = Use filte      | -                |               |                   |                  |                 |       |  |  |  |

|                                                        |                    |                  |               |                   |                  |                 |       |  |  |  |

# REGISTER 19-1: CiCTRL1: ECAN™ MODULE CONTROL REGISTER 1

# REGISTER 19-13: CIBUFPNT2: ECAN™ MODULE FILTER 4-7 BUFFER POINTER REGISTER

| R/W-0                              | R/W-0         | R/W-0                                                   | R/W-0               | R/W-0          | R/W-0           | R/W-0              | R/W-0 |

|------------------------------------|---------------|---------------------------------------------------------|---------------------|----------------|-----------------|--------------------|-------|

|                                    | F7BP          | <3:0>                                                   |                     |                | F6BP            | ><3:0>             |       |

| bit 15                             |               |                                                         |                     |                |                 |                    | bit 8 |

| R/W-0                              | R/W-0         | R/W-0                                                   | R/W-0               | R/W-0          | R/W-0           | R/W-0              | R/W-0 |

|                                    | F5BP          | <3:0>                                                   |                     |                | F4BP            | <sup>2</sup> <3:0> |       |

| bit 7                              |               |                                                         |                     |                |                 |                    | bit ( |

| Legend:                            |               |                                                         |                     |                |                 |                    |       |

| R = Readable                       | e bit         | W = Writable                                            | bit                 | U = Unimplemer | nted bit, read  | l as '0'           |       |

| -n = Value at POR '1' = Bit is set |               |                                                         | '0' = Bit is cleare |                | x = Bit is unkr | nown               |       |

| bit 15-12                          | 1111 = Filter | RX Buffer Writt<br>hits received ir<br>hits received ir | n RX FIFO bu        | uffer          |                 |                    |       |

|                                    | •             |                                                         |                     |                |                 |                    |       |

|                                    |               | hits received ir                                        |                     |                |                 |                    |       |

| bit 11-8                           | 1111 = Filter | RX Buffer Writt<br>hits received ir<br>hits received ir | n RX FIFO bu        | uffer          |                 |                    |       |

|                                    | •             |                                                         |                     |                |                 |                    |       |

|                                    |               | hits received ir hits received ir                       |                     |                |                 |                    |       |

| bit 7-4                            | 1111 = Filter | RX Buffer Writt<br>hits received ir<br>hits received ir | n RX FIFO bu        | uffer          |                 |                    |       |

|                                    | •             |                                                         |                     |                |                 |                    |       |

|                                    |               | hits received ir hits received ir                       |                     |                |                 |                    |       |

| bit 3-0                            | 1111 = Filter | RX Buffer Writt<br>hits received ir<br>hits received ir | n RX FIFO bu        | uffer          |                 |                    |       |

|                                    | •             |                                                         |                     |                |                 |                    |       |

|                                    | 0001 = Filter | hits received ir                                        | n RX Buffer 1       |                |                 |                    |       |

### REGISTER 19-19: CIFMSKSEL2: ECAN™ FILTER 15-8 MASK SELECTION REGISTER

| R/W-0         | R/W-0        | R/W-0                                       | R/W-0           | R/W-0            | R/W-0           | R/W-0           | R/W    | /-0   |

|---------------|--------------|---------------------------------------------|-----------------|------------------|-----------------|-----------------|--------|-------|

| F15M          | SK<1:0>      | F14MS                                       | K<1:0>          | F13M             | SK<1:0>         | F12MS           | K<1:0> |       |

| bit 15        |              |                                             |                 |                  |                 |                 |        | bit 8 |

| R/W-0         | R/W-0        |                                             | R/W-0           |                  | R/W-0           |                 | R/W    | 10    |

|               |              | R/W-0                                       | -               | R/W-0            |                 | R/W-0           |        | /-0   |

|               | SK<1:0>      | F10MS                                       | K<1:0>          | F9MS             | SK<1:0>         | F8MS            | K<1:0> | 1.1.4 |

| bit 7         |              |                                             |                 |                  |                 |                 |        | bit ( |

| Legend:       |              |                                             |                 |                  |                 |                 |        |       |

| R = Readabl   | e bit        | W = Writable                                | bit             | U = Unimplei     | mented bit, rea | d as '0'        |        |       |

| -n = Value at | POR          | '1' = Bit is set                            |                 | '0' = Bit is cle |                 | x = Bit is unkr | nown   |       |

|               |              |                                             |                 |                  |                 |                 |        |       |

| bit 15-14     | F15MSK<1:0   | >: Mask Sourc                               | e for Filter 15 | bit              |                 |                 |        |       |

|               |              | ed; do not use                              |                 |                  |                 |                 |        |       |

|               |              | ance Mask 2 reg                             |                 |                  |                 |                 |        |       |

|               |              | ance Mask 1 reg<br>ance Mask 0 reg          |                 |                  |                 |                 |        |       |

| bit 13-12     | -            | )>: Mask Sourc                              | -               |                  |                 |                 |        |       |

| DIL 13-12     |              | ed; do not use                              |                 | DIL              |                 |                 |        |       |

|               |              | ance Mask 2 reg                             | gisters contair | n mask           |                 |                 |        |       |

|               |              | ance Mask 1 reg                             |                 |                  |                 |                 |        |       |

|               | 00 = Accepta | ance Mask 0 reg                             | gisters contair | n mask           |                 |                 |        |       |

| bit 11-10     |              | >: Mask Sourc                               | e for Filter 13 | bit              |                 |                 |        |       |

|               |              | ed; do not use                              | niatana aantain |                  |                 |                 |        |       |

|               |              | ance Mask 2 reg<br>ance Mask 1 reg          |                 |                  |                 |                 |        |       |

|               |              | ance Mask 0 reg                             |                 |                  |                 |                 |        |       |

| bit 9-8       | -            | )>: Mask Sourc                              | -               |                  |                 |                 |        |       |

|               | 11 = Reserve | ed; do not use                              |                 |                  |                 |                 |        |       |

|               |              | ance Mask 2 reg                             |                 |                  |                 |                 |        |       |

|               |              | ance Mask 1 reg                             |                 |                  |                 |                 |        |       |

| h:+ 7 C       |              | ance Mask 0 reg<br><b>)&gt;:</b> Mask Sourc | -               |                  |                 |                 |        |       |

| bit 7-6       |              | ed; do not use                              | e for Filter II | DIL              |                 |                 |        |       |

|               |              | ance Mask 2 reg                             | pisters contair | n mask           |                 |                 |        |       |

|               |              | ance Mask 1 reg                             |                 |                  |                 |                 |        |       |

|               | 00 = Accepta | ance Mask 0 reg                             | gisters contair | n mask           |                 |                 |        |       |

| bit 5-4       |              | D>: Mask Sourc                              | e for Filter 10 | bit              |                 |                 |        |       |

|               |              | ed; do not use                              |                 |                  |                 |                 |        |       |

|               | -            | ance Mask 2 reg                             | -               |                  |                 |                 |        |       |

|               | -            | ance Mask 1 reg<br>ance Mask 0 reg          | -               |                  |                 |                 |        |       |

| bit 3-2       | -            | : Mask Source                               | -               |                  |                 |                 |        |       |

|               |              | ed; do not use                              |                 |                  |                 |                 |        |       |

|               |              | ance Mask 2 reg                             | gisters contair | n mask           |                 |                 |        |       |

|               | -            | ance Mask 1 reg                             | -               |                  |                 |                 |        |       |

|               | -            | ance Mask 0 reg                             | -               |                  |                 |                 |        |       |

| bit 1-0       |              | : Mask Source                               | for Filter 8 bi | t                |                 |                 |        |       |

|               |              | ed; do not use                              |                 |                  |                 |                 |        |       |

|               |              | ance Mask 2 reg                             |                 |                  |                 |                 |        |       |

|               |              | ance Mask 1 reg<br>ance Mask 0 reg          |                 |                  |                 |                 |        |       |

|               |              |                                             | Julie Contain   |                  |                 |                 |        |       |

|               |              |                                             |                 |                  |                 |                 |        |       |

# 20.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual", Section 16. "Analog-to-Digital Converter (ADC)" (DS70183), which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJXXXGPX06A/X08A/X10A devices have up to 32 Analog-to-Digital input channels. These devices also have up to 2 Analog-to-Digital converter modules (ADCx, where 'x' = 1 or 2), each with its own set of Special Function Registers.

The AD12B bit (ADxCON1<10>) allows each of the ADC modules to be configured by the user as either a 10-bit, 4-sample/hold ADC (default configuration) or a 12-bit, 1-sample/hold ADC.

Note: The ADC module needs to be disabled before modifying the AD12B bit.

# 20.1 Key Features

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- Conversion speeds of up to 1.1 Msps

- · Up to 32 analog input pins

- External voltage reference input pins

- Simultaneous sampling of up to four analog input pins

- Automatic Channel Scan mode

- Selectable conversion trigger source

- Selectable Buffer Fill modes

- Two result alignment options (signed/unsigned)

- · Operation during CPU Sleep and Idle modes

The 12-bit ADC configuration supports all the above features, except:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only 1 sample/hold amplifier in the 12-bit configuration, so simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the Analog-to-Digital Converter can have up to 32 analog input pins, designated AN0 through AN31. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins. The actual number of analog input pins and external voltage reference input configuration will depend on the specific device.

A block diagram of the Analog-to-Digital Converter is shown in Figure 20-1.

# 20.2 Analog-to-Digital Initialization

The following configuration steps should be performed.

- 1. Configure the ADC module:

- a) Select port pins as analog inputs (ADxPCFGH<15:0> or ADxPCFGL<15:0>)

- b) Select voltage reference source to match expected range on analog inputs (ADxCON2<15:13>)

- c) Select the analog conversion clock to match desired data rate with processor clock (ADxCON3<7:0>)

- d) Determine how many S/H channels will be used (ADxCON2<9:8> and ADxPCFGH<15:0> or ADxPCFGL<15:0>)

- e) Select the appropriate sample/conversion sequence (ADxCON1<7:5> and ADxCON3<12:8>)

- f) Select how conversion results are presented in the buffer (ADxCON1<9:8>)

- g) Turn on the ADC module (ADxCON1<15>)

- Configure ADC interrupt (if required):

- a) Clear the ADxIF bit

2.

b) Select ADC interrupt priority

# 20.3 ADC and DMA

If more than one conversion result needs to be buffered before triggering an interrupt, DMA data transfers can be used. Both ADC1 and ADC2 can trigger a DMA data transfer. If ADC1 or ADC2 is selected as the DMA IRQ source, a DMA transfer occurs when the AD1IF or AD2IF bit gets set as a result of an ADC1 or ADC2 sample conversion sequence.

The SMPI<3:0> bits (ADxCON2<5:2>) are used to select how often the DMA RAM buffer pointer is incremented.

The ADDMABM bit (ADxCON1<12>) determines how the conversion results are filled in the DMA RAM buffer area being used for ADC. If this bit is set, DMA buffers are written in the order of conversion. The module will provide an address to the DMA channel that is the same as the address used for the non-DMA stand-alone buffer. If the ADDMABM bit is cleared, the DMA buffers are written in Scatter/Gather mode. The module will provide a scatter/gather address to the DMA channel, based on the index of the analog input and the size of the DMA buffer.

# 20.6 ADC Control Registers

# **REGISTER 20-1:** ADxCON1: ADCx CONTROL REGISTER 1(where x = 1 or 2)

| R/W-0  | U-0       | R/W-0  | R/W-0   | U-0    | R/W-0 | R/W-0 | R/W-0  |

|--------|-----------|--------|---------|--------|-------|-------|--------|

| ADON   | _         | ADSIDL | ADDMABM |        | AD12B | FORM  | 1<1:0> |

| bit 15 |           |        |         |        |       |       | bit 8  |

|        |           |        |         |        |       |       |        |

| R/W-0  | R/W-0     | R/W-0  | U-0     | R/W-0  | R/W-0 | R/W-0 | R/C-0  |

|        |           |        |         |        |       | HC,HS | HC, HS |

|        | SSRC<2:0> |        | —       | SIMSAM | ASAM  | SAMP  | DONE   |

| bit 7  |           |        |         |        |       |       | bit 0  |

| Legend: HC = Cleared by hardware |                  | HS = Set by hardware               |                    |  |  |  |

|----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit                 | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR                | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 15  | ADON: ADC Operating Mode bit                                                                                                                                                                                   |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = ADC module is operating                                                                                                                                                                                    |

|         | 0 = ADC module is off                                                                                                                                                                                          |

| bit 14  | Unimplemented: Read as '0'                                                                                                                                                                                     |

| bit 13  | ADSIDL: Stop in Idle Mode bit                                                                                                                                                                                  |

|         | 1 = Discontinue module operation when device enters Idle mode                                                                                                                                                  |

|         | 0 = Continue module operation in Idle mode                                                                                                                                                                     |

| bit 12  | ADDMABM: DMA Buffer Build Mode bit                                                                                                                                                                             |

|         | 1 = DMA buffers are written in the order of conversion. The module will provide an address to the DMA channel that is the same as the address used for the non-DMA stand-alone buffer                          |

|         | <ul> <li>DMA buffers are written in Scatter/Gather mode. The module will provide a scatter/gather address to the DMA channel, based on the index of the analog input and the size of the DMA buffer</li> </ul> |

| bit 11  | Unimplemented: Read as '0'                                                                                                                                                                                     |

| bit 10  | AD12B: 10-Bit or 12-Bit Operation Mode bit                                                                                                                                                                     |

|         | 1 = 12-bit, 1-channel ADC operation                                                                                                                                                                            |

|         | 0 = 10-bit, 4-channel ADC operation                                                                                                                                                                            |

| bit 9-8 | FORM<1:0>: Data Output Format bits                                                                                                                                                                             |

|         | For 10-bit operation:                                                                                                                                                                                          |

|         | 11 = Reserved                                                                                                                                                                                                  |

|         | 10 = Reserved                                                                                                                                                                                                  |

|         | 01 = Signed integer (Dout = ssss sssd dddd dddd, where s = .NOT.d<9>)<br>00 = Integer (Dout = 0000 00dd dddd dddd)                                                                                             |

|         | For 12-bit operation:                                                                                                                                                                                          |

|         | 11 = Reserved                                                                                                                                                                                                  |

|         | 10 = Reserved                                                                                                                                                                                                  |

|         | 01 = Signed Integer (DOUT = ssss sddd dddd dddd, where s = .NOT.d<11>)                                                                                                                                         |

|         | 00 = Integer (DOUT = 0000  dddd  dddd  dddd)                                                                                                                                                                   |

| bit 7-5 | SSRC<2:0>: Sample Clock Source Select bits                                                                                                                                                                     |

|         | 111 = Internal counter ends sampling and starts conversion (auto-convert)                                                                                                                                      |

|         | 110 = Reserved<br>101 = Reserved                                                                                                                                                                               |

|         | 100 = GP timer (Timer5 for ADC1, Timer3 for ADC2) compare ends sampling and starts conversion                                                                                                                  |

|         | 011 = Reserved                                                                                                                                                                                                 |

|         | 010 = GP timer (Timer3 for ADC1, Timer5 for ADC2) compare ends sampling and starts conversion                                                                                                                  |

|         | 001 = Active transition on INTO pin ends sampling and starts conversion                                                                                                                                        |

|         | 000 = Clearing sample bit ends sampling and starts conversion                                                                                                                                                  |

# 22.0 INSTRUCTION SET SUMMARY

**Note:** This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A families of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The PIC24H instruction set is identical to that of the PIC24F, and is a subset of the dsPIC30F/33F instruction set.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- · Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- DSP operations

- · Control operations

Table 22-1 shows the general symbols used in describing the instructions.

The PIC24H instruction set summary in Table 22-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand which is typically a register 'Wb' without any address modifier

- The second source operand which is typically a register 'Ws' with or without an address modifier

- The destination of the result which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could either be the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement may use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by the value of 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand which is a register 'Wb' without any address modifier

- The second source operand which is a literal value

- The destination of the result (only if not the same as the first source operand) which is typically a register 'Wd' with or without an address modifier

The control instructions may use some of the following operands:

- A program memory address

- The mode of the table read and table write instructions

All instructions are a single word, except for certain double word instructions, which were made double word instructions so that all the required information is available in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all table reads and writes and RETURN/RETFIE instructions, which are single-word instructions but take two or three cycles. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or double word instruction. Moreover, double word moves require two cycles. The double word instructions execute in two instruction cycles.

Note: For more details on the instruction set, refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157).

#### Base Assembly # of # of Status Flags Instr Assembly Syntax Description Mnemonic Words Cycles Affected # 47 Relative Call RCALL RCALL 1 2 None Expr RCALL Computed Call 1 2 None Wn 48 REPEAT REPEAT #lit14 Repeat Next Instruction lit14 + 1 times 1 1 None REPEAT Repeat Next Instruction (Wn) + 1 times 1 1 None Wn 1 1 49 RESET RESET Software device Reset None 50 RETFIE RETFIE Return from interrupt 1 3 (2) None 51 RETLW #lit10,Wn Return with literal in Wn 1 3 (2) None RETLW 52 1 RETURN RETURN Return from Subroutine 3 (2) None 53 RLC RLC f = Rotate Left through Carry f 1 1 C,N,Z f RLC f,WREG WREG = Rotate Left through Carry f 1 1 C,N,Z RLC Ws,Wd Wd = Rotate Left through Carry Ws 1 1 C,N,Z 54 f = Rotate Left (No Carry) f 1 1 N,Z RLNC RUNC f 1 RLNC f,WREG WREG = Rotate Left (No Carry) f 1 N,Z RLNC Ws,Wd Wd = Rotate Left (No Carry) Ws 1 1 N,Z 55 RRC RRC f = Rotate Right through Carry f 1 1 C,N,Z f WREG = Rotate Right through Carry f 1 1 C,N,Z RRC f,WREG RRC Wd = Rotate Right through Carry Ws 1 1 C,N,Z Ws,Wd 56 RRNC RRNC f = Rotate Right (No Carry) f 1 1 N,Z f WREG = Rotate Right (No Carry) f 1 1 N,Z RRNC f,WREG Wd = Rotate Right (No Carry) Ws 1 1 N,Z RRNC Ws,Wd 1 C,N,Z 57 SE SE Ws,Wnd Wnd = sign-extended Ws 1 58 SETM SETM f f = 0xFFFF1 1 None WREG = 0xFFFF 1 1 SETM WREG None Ws = 0xFFFF 1 SETM Ws 1 None 59 SL SL f f = Left Shift f 1 1 C,N,OV,Z SL f,WREG WREG = Left Shift f 1 1 C,N,OV,Z Wd = Left Shift Ws 1 1 C,N,OV,Z SL Ws,Wd Wnd = Left Shift Wb by Wns 1 1 SL N.Z Wb, Wns, Wnd SL Wb,#lit5,Wnd Wnd = Left Shift Wb by lit5 1 1 N,Z 60 SUB SUB f = f – WREG 1 1 C,DC,N,OV,Z f WREG = f - WREG 1 1 C,DC,N,OV,Z SUB f,WREG Wn = Wn - lit10SUB #lit10,Wn 1 1 C,DC,N,OV,Z SUB Wb,Ws,Wd Wd = Wb - Ws1 1 C,DC,N,OV,Z Wd = Wb - lit5 1 1 C,DC,N,OV,Z SUB Wb,#lit5,Wd 61 SUBB $f = f - WREG - (\overline{C})$ C,DC,N,OV,Z 1 1 SUBB f WREG = $f - WREG - (\overline{C})$ 1 SUBB f,WREG 1 C,DC,N,OV,Z $Wn = Wn - lit10 - (\overline{C})$ 1 C,DC,N,OV,Z 1 SUBB #lit10,Wn SUBB $Wd = Wb - Ws - (\overline{C})$ 1 1 C,DC,N,OV,Z Wb,Ws,Wd SUBB Wb,#lit5,Wd $Wd = Wb - lit5 - (\overline{C})$ 1 1 C,DC,N,OV,Z 62 SUBR f = WREG - f 1 1 C,DC,N,OV,Z SUBR f WREG = WREG - f 1 1 C,DC,N,OV,Z SUBR f,WREG SUBR Wb,Ws,Wd Wd = Ws - Wb 1 1 C,DC,N,OV,Z Wd = lit5 - Wb1 1 C,DC,N,OV,Z SUBR Wb, #lit5, Wd 63 SUBBR $f = WREG - f - (\overline{C})$ 1 1 C,DC,N,OV,Z SUBBR f WREG = WREG - f - $(\overline{C})$ 1 SUBBR f,WREG 1 C,DC,N,OV,Z $Wd = Ws - Wb - (\overline{C})$ 1 1 C,DC,N,OV,Z SUBBR Wb.Ws.Wd $Wd = lit5 - Wb - (\overline{C})$ 1 C,DC,N,OV,Z SUBBR Wb,#lit5,Wd 1 64 1 SWAP SWAP.b Wn Wn = nibble swap Wn 1 None SWAP Wn = byte swap Wn 1 1 None Wn 1 2 65 Read Prog<23:16> to Wd<7:0> TBLRDH TBLRDH Ws,Wd None

#### TABLE 22-2: INSTRUCTION SET OVERVIEW (CONTINUED)

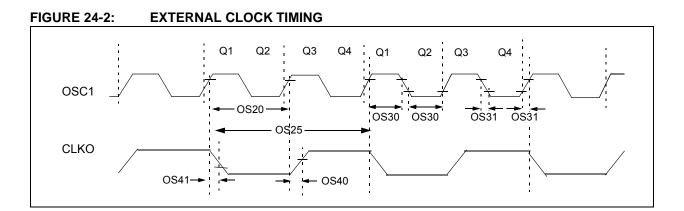

| AC CHARACTERISTICS |               |                                                                                    | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                    |                |                   |                          |  |

|--------------------|---------------|------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------|----------------|-------------------|--------------------------|--|

| Param<br>No.       | Symbol        | Characteristic                                                                     | Min                                                   | Typ <sup>(1)</sup> | Max            | Units             | Conditions               |  |

| OS10               | FIN           | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC                                                    |                    | 40             | MHz               | EC                       |  |

|                    |               | Oscillator Crystal Frequency                                                       | 3.5<br>10                                             |                    | 10<br>40<br>33 | MHz<br>MHz<br>kHz | XT<br>HS<br>SOSC         |  |

| OS20               | Tosc          | Tosc = 1/Fosc                                                                      | 12.5                                                  | _                  | DC             | ns                | _                        |  |

| OS25               | Тсү           | Instruction Cycle Time <sup>(2)</sup>                                              | 25                                                    |                    | DC             | ns                | —                        |  |

| OS30               | TosL,<br>TosH | External Clock in (OSC1)<br>High or Low Time                                       | 0.375 x Tosc                                          | _                  | 0.625 x Tosc   | ns                | EC                       |  |

| OS31               | TosR,<br>TosF | External Clock in (OSC1)<br>Rise or Fall Time                                      | —                                                     |                    | 20             | ns                | EC                       |  |

| OS40               | TckR          | CLKO Rise Time <sup>(3)</sup>                                                      | _                                                     | 5.2                |                | ns                | —                        |  |

| OS41               | TckF          | CLKO Fall Time <sup>(3)</sup>                                                      |                                                       | 5.2                | _              | ns                | —                        |  |

| OS42               | Gм            | External Oscillator<br>Transconductance <sup>(4)</sup>                             | 14                                                    | 16                 | 18             | mA/V              | VDD = 3.3V<br>TA = +25°C |  |

#### TABLE 24-16: EXTERNAL CLOCK TIMING REQUIREMENTS

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: Instruction cycle period (TCY) equals two times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

- 3: Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin.

- 4: Data for this parameter is Preliminary. This parameter is characterized, but not tested in manufacturing.

# 25.1 High Temperature DC Characteristics

#### TABLE 25-1: OPERATING MIPS VS. VOLTAGE

| Characteristic | VDD Range                   | Temperature Range | Max MIPS                   |

|----------------|-----------------------------|-------------------|----------------------------|

| Characteristic | (in Volts)                  | (in °C)           | PIC24HJXXXGPX06A/X08A/X10A |

| HDC5           | VBOR to 3.6V <sup>(1)</sup> | -40°C to +150°C   | 20                         |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules such as the ADC will have degraded performance. Device functionality is tested but not characterized. Refer to parameter BO10 in Table 24-11 for the minimum and maximum BOR values.

### TABLE 25-2: THERMAL OPERATING CONDITIONS

| TABLE 23-2. THERMAL OPERATING CONDITIONS                                                                                                                                               |               |                           |     |      |      |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------|-----|------|------|--|

| Rating                                                                                                                                                                                 | Symbol        | Min                       | Тур | Max  | Unit |  |

| High Temperature Devices                                                                                                                                                               |               |                           |     |      |      |  |

| Operating Junction Temperature Range                                                                                                                                                   | TJ            | -40                       | —   | +155 | °C   |  |

| Operating Ambient Temperature Range                                                                                                                                                    | TA -40 — +150 |                           |     |      |      |  |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD            | -40 — +150<br>PINT + PI/O |     |      | W    |  |

| Maximum Allowed Power Dissipation                                                                                                                                                      | Pdmax         | (TJ - ΤΑ)/θJΑ             |     |      |      |  |

#### TABLE 25-3: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |           |                                                                                     | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |     |            |  |  |  |

|--------------------|-----------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|--|--|--|

| Parameter<br>No.   | Symbol    | Characteristic                                                                      | Min                                                                                                                                                    | Тур | Conditions |  |  |  |

| Operating V        | Voltage   |                                                                                     |                                                                                                                                                        |     |            |  |  |  |

| HDC10              | Supply Vo | Itage                                                                               |                                                                                                                                                        |     |            |  |  |  |

|                    | Vdd       | VDD         —         3.0         3.3         3.6         V         -40°C to +150°C |                                                                                                                                                        |     |            |  |  |  |

#### TABLE 25-4: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACT                                                                                                    | ERISTICS      |      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |                                                      |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------|---------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|--|--|

| Parameter<br>No.                                                                                              | Typical       | Мах  | Units                                                                                                                                                    | Conditions                                           |  |  |  |  |

| Power-Down                                                                                                    | Current (IPD) |      |                                                                                                                                                          |                                                      |  |  |  |  |

| HDC60e                                                                                                        | 250           | 2000 | μA                                                                                                                                                       | +150°C 3.3V Base Power-Down Current <sup>(1,3)</sup> |  |  |  |  |

| Note 1: Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as inputs and |               |      |                                                                                                                                                          |                                                      |  |  |  |  |

**Note 1:** Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as inputs and pulled to Vss. WDT, etc., are all switched off, and VREGS (RCON<8>) = 1.

2: The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

3: These currents are measured on the device containing the most memory in this family.

4: These parameters are characterized, but are not tested in manufacturing.

### TABLE 25-9: INTERNAL LPRC ACCURACY

| AC<br>CHARACTERISTICS | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |                    |   |                    |   |                                           |   |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---|--------------------|---|-------------------------------------------|---|--|--|

| Param<br>No.          | Characteristic Min Typ Max Units Conditio                                                                                                               |                    |   |                    |   | Conditions                                |   |  |  |

|                       | LPRC @ 32.768 kHz <sup>(1)</sup>                                                                                                                        |                    |   |                    |   |                                           |   |  |  |

| HF21                  | LPRC                                                                                                                                                    | -70 <sup>(2)</sup> | _ | +70 <sup>(2)</sup> | % | $-40^{\circ}C \leq TA \leq +150^{\circ}C$ | _ |  |  |

Note 1: Change of LPRC frequency as VDD changes.

2: Characterized but not tested.

### TABLE 25-10: SPIX MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| AC<br>CHARACTERISTICS |                       | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |                                       |    |     |       |            |  |  |  |

|-----------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----|-----|-------|------------|--|--|--|

| Param<br>No.          | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                               | racteristic <sup>(1)</sup> Min Typ Ma |    | Max | Units | Conditions |  |  |  |

| HSP35                 | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                                   |                                       | 10 | 25  | ns    | _          |  |  |  |

| HSP40                 | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                                  | 28                                    |    | _   | ns    | _          |  |  |  |

| HSP41                 | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                                   | 35                                    |    |     | ns    | _          |  |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

#### TABLE 25-11: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC<br>CHARACTERISTICS |                       | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |     |     |     |       |            |  |  |  |

|-----------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------|--|--|--|

| Param<br>No.          | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                               | Min | Тур | Max | Units | Conditions |  |  |  |

| HSP35                 | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                                   | —   | 10  | 25  | ns    | _          |  |  |  |

| HSP36                 | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to<br>First SCKx Edge                                                                                                                | 35  | _   | —   | ns    | _          |  |  |  |

| HSP40                 | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                                  | 28  | _   | —   | ns    | _          |  |  |  |

| HSP41                 | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                                   | 35  | _   | —   | ns    | _          |  |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

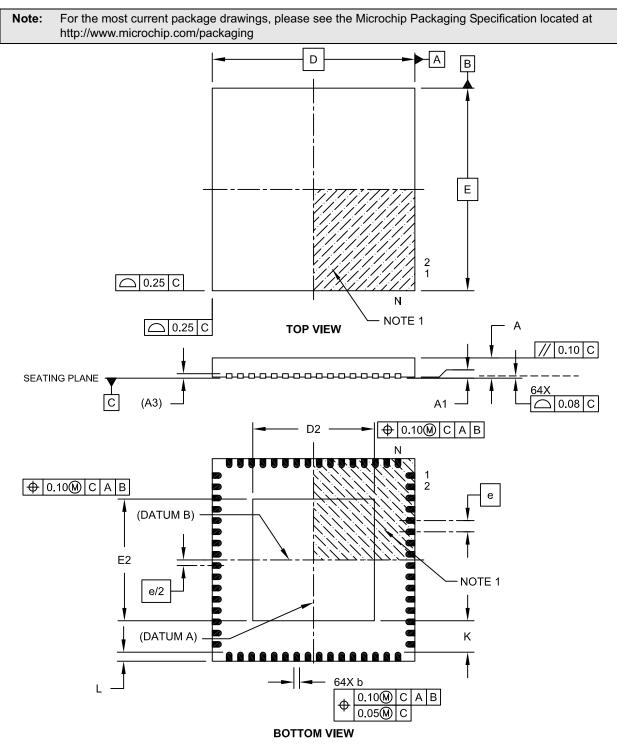

# 27.2 Package Details

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

Microchip Technology Drawing C04-154A Sheet 1 of 2