#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 32x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp310a-i-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

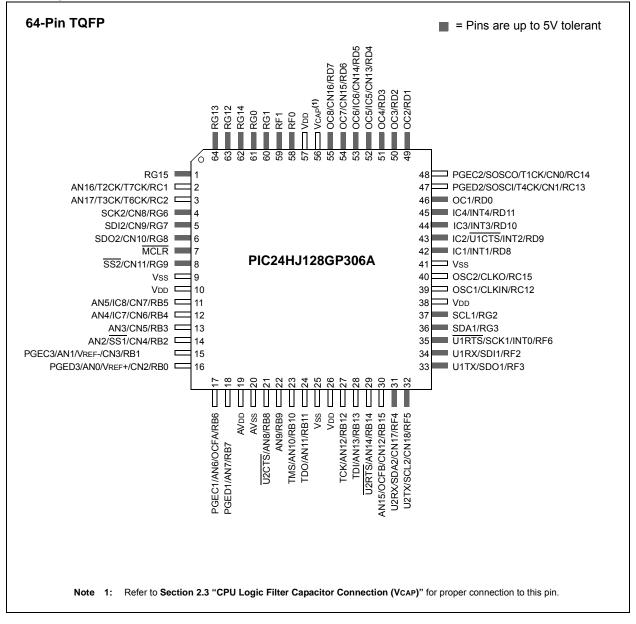

## Pin Diagrams (Continued)

### TABLE 4-9: I2C1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8              | Bit 7 | Bit 6 | Bit 5      | Bit 4        | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|--------|--------------------|-------|-------|------------|--------------|------------|-------|-------|-------|---------------|

| I2C1RCV  | 0200        | _       | _      | _       | _      | -      | —      | _      | — Receive Register |       |       |            |              |            |       |       | 0000  |               |

| I2C1TRN  | 0202        | _       | —      | —       | _      | _      | _      | _      | _                  |       |       |            | Transmit     | Register   |       |       |       | OOFF          |

| I2C1BRG  | 0204        | _       | _      | _       | _      | _      | _      | _      |                    |       |       | Baud Rat   | e Generato   | r Register |       |       |       | 0000          |

| I2C1CON  | 0206        | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN               | GCEN  | STREN | ACKDT      | ACKEN        | RCEN       | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT | 0208        | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10              | IWCOL | I2COV | D_A        | Р            | S          | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD  | 020A        | _       | _      | _       | _      | _      | _      |        |                    |       |       | Address    | Register     |            |       |       |       | 0000          |

| I2C1MSK  | 020C        | —       | _      | _       | _      | _      | _      |        |                    |       |       | Address Ma | isk Register |            |       |       |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

#### TABLE 4-10: I2C2 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8              | Bit 7 | Bit 6 | Bit 5      | Bit 4        | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|--------|--------------------|-------|-------|------------|--------------|------------|-------|-------|-------|---------------|

| I2C2RCV  | 0210        |         |        |         | —      |        |        | _      | - Receive Register |       |       |            |              |            |       |       |       | 0000          |

| I2C2TRN  | 0212        | _       | _      |         | —      | _      |        | —      | -                  |       |       |            | Transmit     | Register   |       |       |       | OOFF          |

| I2C2BRG  | 0214        | _       | _      |         | —      | _      |        | —      |                    |       |       | Baud Rat   | te Generato  | r Register |       |       |       | 0000          |

| I2C2CON  | 0216        | I2CEN   | —      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN               | GCEN  | STREN | ACKDT      | ACKEN        | RCEN       | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT | 0218        | ACKSTAT | TRSTAT | -       | —      |        | BCL    | GCSTAT | ADD10              | IWCOL | I2COV | D_A        | Р            | S          | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD  | 021A        | _       | _      |         | —      | _      |        |        |                    |       |       | Address    | Register     |            |       |       |       | 0000          |

| I2C2MSK  | 021C        | _       | _      | -       | —      | _      | -      |        |                    |       |       | Address Ma | ask Register |            |       |       |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

### TABLE 4-11: UART1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15   | Bit 14                        | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5 | Bit 4       | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|-------------|----------|-------------------------------|----------|--------|--------|--------|-------|-------|--------|--------|-------|-------------|--------|-------|--------|-------|---------------|

| U1MODE   | 0220        | UARTEN   | _                             | USIDL    | IREN   | RTSMD  | —      | UEN1  | UEN0  | WAKE   | LPBACK | ABAUD | URXINV      | BRGH   | PDSEI | _<1:0> | STSEL | 0000          |

| U1STA    | 0222        | UTXISEL1 | UTXINV                        | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT  | URXISE | L<1:0> | ADDEN | RIDLE       | PERR   | FERR  | OERR   | URXDA | 0110          |

| U1TXREG  | 0224        | _        | _                             | _        | _      | _      | -      | _     |       |        |        | UART  | Fransmit Re | gister |       |        |       | xxxx          |

| U1RXREG  | 0226        | _        | _                             | _        | _      | _      | -      | _     |       |        |        | UART  | Receive Re  | gister |       |        |       | 0000          |

| U1BRG    | 0228        |          | Baud Rate Generator Prescaler |          |        |        |        |       |       |        |        | 0000  |             |        |       |        |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

| IABLE 4-23 | ABLE 4-23: ECAN2 REGISTER MAP WHEN C2CTRL1.WIN = 1 FOR PIC24HJ256GP610A DEVICES ONLY (CONTINUED) |        |           |        |        |        |        |       |                               |                               |          |       |       |        |       |        |        |               |

|------------|--------------------------------------------------------------------------------------------------|--------|-----------|--------|--------|--------|--------|-------|-------------------------------|-------------------------------|----------|-------|-------|--------|-------|--------|--------|---------------|

| File Name  | Addr                                                                                             | Bit 15 | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                         | Bit 7                         | Bit 6    | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

| C2RXF11EID | 056E                                                                                             |        |           |        | EID<   | 15:8>  |        |       |                               |                               |          |       | EID<7 | /:0>   |       |        |        | xxxx          |

| C2RXF12SID | 0570                                                                                             |        | SID<10:3> |        |        |        |        |       | SID<2:0> — EXIDE — EID<17:16> |                               |          |       |       |        |       | 17:16> | xxxx   |               |

| C2RXF12EID | 0572                                                                                             |        | EID<15:8> |        |        |        |        |       | EID<7:0>                      |                               |          |       |       |        |       |        | xxxx   |               |

| C2RXF13SID | 0574                                                                                             |        | SID<10:3> |        |        |        |        |       | SID<2:0> — EXIDE — EID<17:10  |                               |          |       |       |        |       | 17:16> | xxxx   |               |

| C2RXF13EID | 0576                                                                                             |        |           |        | EID<   | 15:8>  |        |       |                               | EID<7:0>                      |          |       |       |        |       |        | xxxx   |               |

| C2RXF14SID | 0578                                                                                             |        |           |        | SID<   | 10:3>  |        |       |                               | SID<2:0> — EXIDE — EID<17:16> |          |       |       |        |       |        | 17:16> | xxxx          |

| C2RXF14EID | 057A                                                                                             |        | EID<15:8> |        |        |        |        |       |                               |                               |          | EID<7 | ':0>  |        |       |        | xxxx   |               |

| C2RXF15SID | 057C                                                                                             |        | SID<10:3> |        |        |        |        |       | SID<2:0> — EXIDE — EID<17:16> |                               |          |       |       | 17:16> | xxxx  |        |        |               |

| C2RXF15EID | 15EID 057E EID<15:8>                                                                             |        |           |        |        |        |        |       |                               | EID<7                         | EID<7:0> |       |       |        |       |        |        |               |

### TABLE 4-23: ECAN2 REGISTER MAP WHEN C2CTRL1.WIN = 1 FOR PIC24HJ256GP610A DEVICES ONLY (CONTINUED)

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

DS70592D-page 49

| R/W-0            | R-0                                             | U-0                                                                                            | U-0                             | U-0              | U-0              | U-0             | U-0           |

|------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------|------------------|------------------|-----------------|---------------|

| ALTIVT           | DISI                                            | _                                                                                              | _                               | _                | _                | _               | _             |

| bit 15           |                                                 |                                                                                                |                                 |                  |                  |                 | bit 8         |

|                  |                                                 |                                                                                                |                                 |                  |                  |                 |               |

| U-0              | U-0                                             | U-0                                                                                            | R/W-0                           | R/W-0            | R/W-0            | R/W-0           | R/W-0         |

| <br>bit 7        | _                                               | —                                                                                              | INT4EP                          | INT3EP           | INT2EP           | INT1EP          | INT0EP<br>bit |

|                  |                                                 |                                                                                                |                                 |                  |                  |                 | DI            |

| Legend:          |                                                 |                                                                                                |                                 |                  |                  |                 |               |

| R = Readable     | e bit                                           | W = Writable                                                                                   | bit                             | U = Unimpler     | mented bit, read | l as '0'        |               |

| -n = Value at    | POR                                             | '1' = Bit is set                                                                               |                                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown          |

| bit 15<br>bit 14 | 0 = Use stand<br>DISI: DISI In<br>1 = DISI inst | nate vector tab<br>lard (default) v<br>struction Statu<br>ruction is activ<br>ruction is not a | le<br>ector table<br>s bit<br>e |                  |                  |                 |               |

| bit 13-5         | Unimplement                                     | ted: Read as '                                                                                 | 0'                              |                  |                  |                 |               |

| bit 4            | 1 = Interrupt o                                 | rnal Interrupt 4<br>on negative ed<br>on positive edg                                          | ge                              | Polarity Select  | t bit            |                 |               |

| bit 3            | 1 = Interrupt o                                 | rnal Interrupt 3<br>on negative ed<br>on positive edg                                          | ge                              | Polarity Select  | t bit            |                 |               |

| bit 2            | 1 = Interrupt o                                 | rnal Interrupt 2<br>on negative ed<br>on positive edg                                          | ge                              | Polarity Select  | t bit            |                 |               |

| bit 1            | 1 = Interrupt o                                 | rnal Interrupt ´<br>on negative ed<br>on positive edg                                          | ge                              | Polarity Select  | t bit            |                 |               |

| bit 0            | 1 = Interrupt c                                 | rnal Interrupt (<br>on negative ed<br>on positive edg                                          | ge                              | Polarity Select  | t bit            |                 |               |

### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| R/W-0           | R/W-0           | R/W-0                            | R/W-0          | R/W-0            | R/W-0            | R/W-0          | R/W-0   |

|-----------------|-----------------|----------------------------------|----------------|------------------|------------------|----------------|---------|

| U2TXIF          | U2RXIF          | INT2IF                           | T5IF           | T4IF             | OC4IF            | OC3IF          | DMA21IF |

| bit 15          |                 | 1                                |                |                  |                  |                | bit 8   |

| R/W-0           | R/W-0           | R/W-0                            | R/W-0          | R/W-0            | U-0              | R/W-0          | R/W-0   |

| IC8IF           | IC7IF           | AD2IF                            | INT1IF         | CNIF             | _                | MI2C1IF        | SI2C1IF |

| bit 7           |                 |                                  |                |                  |                  |                | bit 0   |

| Legend:         |                 |                                  |                |                  |                  |                |         |

| R = Readable    | bit             | W = Writable                     | bit            | U = Unimpler     | mented bit, rea  | d as '0'       |         |

| -n = Value at F | POR             | '1' = Bit is set                 |                | '0' = Bit is cle | ared             | x = Bit is unk | nown    |

|                 |                 |                                  |                |                  |                  |                |         |

| bit 15          |                 | RT2 Transmitte                   | •              | g Status bit     |                  |                |         |

|                 |                 | request has oc<br>request has no |                |                  |                  |                |         |

| bit 14          |                 | RT2 Receiver li                  |                | Statue hit       |                  |                |         |

|                 |                 | request has oc                   |                |                  |                  |                |         |

|                 |                 | request has no                   |                |                  |                  |                |         |

| bit 13          | INT2IF: Exter   | nal Interrupt 2                  | Flag Status b  | it               |                  |                |         |

|                 |                 | request has oc<br>request has no |                |                  |                  |                |         |

| bit 12          | T5IF: Timer5    | Interrupt Flag                   | Status bit     |                  |                  |                |         |

|                 |                 | request has oc<br>request has no |                |                  |                  |                |         |

| bit 11          | T4IF: Timer4    | Interrupt Flag                   | Status bit     |                  |                  |                |         |

|                 |                 | request has oc<br>request has no |                |                  |                  |                |         |

| bit 10          | OC4IF: Outpu    | ut Compare Ch                    | annel 4 Interr | upt Flag Status  | s bit            |                |         |

|                 |                 | request has oc<br>request has no |                |                  |                  |                |         |

| bit 9           | OC3IF: Outpu    | ut Compare Ch                    | annel 3 Interr | upt Flag Status  | s bit            |                |         |

|                 |                 | request has oc<br>request has no |                |                  |                  |                |         |

| bit 8           | •               | •                                |                | Complete Inte    | rrupt Flag Statu | ıs bit         |         |

|                 | 1 = Interrupt r | request has oc                   | curred         | ·                |                  |                |         |

| bit 7           | •               | request has no<br>Capture Chann  |                | Flag Status hit  |                  |                |         |

|                 |                 | request has oc                   | -              | nag otatus bit   |                  |                |         |

|                 |                 | equest has no                    |                |                  |                  |                |         |

| bit 6           |                 | Capture Chann                    |                | Flag Status bit  |                  |                |         |

|                 |                 | request has oc<br>request has no |                |                  |                  |                |         |

| bit 5           | •               | •                                |                | rupt Flag Statu  | s bit            |                |         |

|                 |                 | request has oc                   | -              | apt i lag oldtu  |                  |                |         |

|                 |                 | request has no                   |                |                  |                  |                |         |

| bit 4           | INT1IF: Exter   | nal Interrupt 1                  | Flag Status b  | it               |                  |                |         |

|                 |                 | equest has oc                    |                |                  |                  |                |         |

|                 | 0 = Interrupt r | request has no                   | toccurred      |                  |                  |                |         |

### REGISTER 7-15: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

| U-0           | R/W-1        | R/W-0                                  | R/W-0           | U-0               | R/W-1           | R/W-0           | R/W-0 |

|---------------|--------------|----------------------------------------|-----------------|-------------------|-----------------|-----------------|-------|

| —             |              | T1IP<2:0>                              |                 | —                 |                 | OC1IP<2:0>      |       |

| bit 15        |              |                                        |                 |                   |                 |                 | bit 8 |

|               |              |                                        |                 |                   |                 |                 |       |

| U-0           | R/W-1        | R/W-0                                  | R/W-0           | U-0               | R/W-1           | R/W-0           | R/W-0 |

| _             |              | IC1IP<2:0>                             |                 | —                 |                 | INT0IP<2:0>     |       |

| bit 7         |              |                                        |                 |                   |                 |                 | bit ( |

| Legend:       |              |                                        |                 |                   |                 |                 |       |

| R = Readabl   | e bit        | W = Writable                           | hit             | U = Unimpler      | mented bit, rea | ad as '0'       |       |

| -n = Value at |              | '1' = Bit is set                       |                 | '0' = Bit is cle  |                 | x = Bit is unkn | own   |

|               |              |                                        |                 |                   |                 |                 |       |

| bit 15        | Unimpleme    | ented: Read as '                       | )'              |                   |                 |                 |       |

| bit 14-12     | T1IP<2:0>:   | Timer1 Interrupt                       | Priority bits   |                   |                 |                 |       |

|               | 111 = Interr | upt is priority 7 (I                   | nighest priorit | y interrupt)      |                 |                 |       |

|               | •            |                                        |                 |                   |                 |                 |       |

|               | •            |                                        |                 |                   |                 |                 |       |

|               |              | upt is priority 1                      |                 |                   |                 |                 |       |

|               | 000 = Interr | upt source is dis                      | abled           |                   |                 |                 |       |

| bit 11        | -            | ented: Read as '                       |                 |                   |                 |                 |       |

| bit 10-8      |              | >: Output Compa                        |                 | -                 | ity bits        |                 |       |

|               | 111 = Interr | upt is priority 7 (I                   | nighest priorit | y interrupt)      |                 |                 |       |

|               | •            |                                        |                 |                   |                 |                 |       |

|               | •            |                                        |                 |                   |                 |                 |       |

|               |              | upt is priority 1<br>upt source is dis | abled           |                   |                 |                 |       |

| bit 7         | Unimpleme    | ented: Read as '                       | )'              |                   |                 |                 |       |

| bit 6-4       | IC1IP<2:0>:  | : Input Capture C                      | hannel 1 Inte   | errupt Priority b | its             |                 |       |

|               | 111 = Interr | upt is priority 7 (I                   | nighest priorit | y interrupt)      |                 |                 |       |

|               | •            |                                        |                 |                   |                 |                 |       |

|               | •            |                                        |                 |                   |                 |                 |       |

|               |              | upt is priority 1<br>upt source is dis | abled           |                   |                 |                 |       |

| bit 3         |              | nted: Read as '                        |                 |                   |                 |                 |       |

| bit 2-0       | INT0IP<2:0:  | >: External Interr                     | upt 0 Priority  | bits              |                 |                 |       |

|               | 111 = Interr | upt is priority 7 (ł                   | nighest priorit | y interrupt)      |                 |                 |       |

|               | •            |                                        |                 |                   |                 |                 |       |

|               | •            |                                        |                 |                   |                 |                 |       |

|               |              | upt is priority 1                      |                 |                   |                 |                 |       |

|               | 000 - Intorr | upt source is dis                      | ما ما م         |                   |                 |                 |       |

| U-0              | R/W-1             | R/W-0                                     | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |

|------------------|-------------------|-------------------------------------------|----------------|-------------------|-----------------|-----------------|-------|

| _                |                   | IC8IP<2:0>                                |                | —                 |                 | IC7IP<2:0>      |       |

| bit 15           |                   |                                           |                |                   | •               |                 | bit   |

| U-0              | R/W-1             | R/W-0                                     | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |

| _                |                   | INT1IP<2:0>                               | -              |                   |                 |                 |       |

| bit 7            |                   |                                           |                |                   |                 |                 | bit   |

| Legend:          |                   |                                           |                |                   |                 |                 |       |

| R = Readab       | le bit            | W = Writable I                            | oit            | U = Unimpler      | mented bit, rea | ad as '0'       |       |

| -n = Value a     | t POR             | '1' = Bit is set                          |                | '0' = Bit is cle  | ared            | x = Bit is unkn | own   |

| bit 15           | Unimpleme         | nted: Read as '0                          | )'             |                   |                 |                 |       |

| bit 14-12        | IC8IP<2:0>:       | Input Capture C                           | hannel 8 Inte  | errupt Priority b | its             |                 |       |

|                  | 111 = Interr      | upt is priority 7 (h                      | nighest priori | ty interrupt)     |                 |                 |       |

|                  | •                 |                                           |                |                   |                 |                 |       |

|                  | •                 |                                           |                |                   |                 |                 |       |

|                  |                   | upt is priority 1                         |                |                   |                 |                 |       |

|                  |                   | upt source is disa                        |                |                   |                 |                 |       |

| bit 11           |                   | ented: Read as '(                         |                | arruat Driarity b | ite             |                 |       |

| bit 10-8         |                   | : Input Capture C<br>upt is priority 7 (ł |                |                   | 115             |                 |       |

|                  | •                 |                                           | lightest phon  | ty interrupt)     |                 |                 |       |

|                  | •                 |                                           |                |                   |                 |                 |       |

|                  | •<br>001 = Interr | upt is priority 1                         |                |                   |                 |                 |       |

|                  |                   | upt source is disa                        | abled          |                   |                 |                 |       |

| bit 7            | Unimpleme         | nted: Read as 'o                          | )'             |                   |                 |                 |       |

| bit 6-4          | AD2IP<2:0>        | -: ADC2 Convers                           | ion Complet    | e Interrupt Prio  | rity bits       |                 |       |

|                  | 111 = Interr      | upt is priority 7 (h                      | nighest priori | ty interrupt)     |                 |                 |       |

|                  | •                 |                                           |                |                   |                 |                 |       |

|                  | •                 |                                           |                |                   |                 |                 |       |

|                  |                   | upt is priority 1                         | ablad          |                   |                 |                 |       |

| hit 2            |                   | upt source is disa                        |                |                   |                 |                 |       |

| bit 3<br>bit 2-0 | -                 | nted: Read as '0                          |                | hite              |                 |                 |       |

|                  |                   | upt is priority 7 (h                      |                |                   |                 |                 |       |

|                  | •                 |                                           |                | ·, ·····          |                 |                 |       |

|                  | •                 |                                           |                |                   |                 |                 |       |

|                  | •<br>001 - Intorr |                                           |                |                   |                 |                 |       |

|                  |                   | upt is priority 1                         |                |                   |                 |                 |       |

### REGISTER 7-20: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5

## 11.6 I/O Helpful Tips

- 1. In some cases, certain pins as defined in TABLE 24-9: "DC Characteristics: I/O Pin Input Specifications" under "Injection Current", have internal protection diodes to VDD and Vss. The term "Injection Current" is also referred to as "Clamp Current". On designated pins, with sufficient external current limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings with nominal VDD with respect to the VSS and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device that is clamped internally by the VDD and VSS power rails, may affect the ADC accuracy by four to six counts.

- I/O pins that are shared with any analog input pin, 2. (i.e., ANx), are always analog pins by default after any reset. Consequently, any pin(s) configured as an analog input pin, automatically disables the digital input pin buffer. As such, any attempt to read a digital input pin will always return a '0' regardless of the digital logic level on the pin if the analog pin is configured. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the analog pin configuration registers in the ADC module, (i.e., ADxPCFGL, AD1PCFGH), by setting the appropriate bit that corresponds to that I/O port pin to a '1'. On devices with more than one ADC, both analog pin configurations for both ADC modules must be configured as a digital I/O pin for that pin to function as a digital I/O pin.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in the data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each CN pin has a configurable internal weak pull-up resistor. The pull-ups act as a current source connected to the pin, and eliminates the need for external resistors in certain applications. The internal pull-up is to ~(VDD-0.8) not VDD. This is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH and at or below the VOL levels. However, for LEDs unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of the data sheet. For example:

VOH = 2.4v @ IOH = -8 mA and VDD = 3.3V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 24.0 "Electrical Characteristics" for additional information.

## 11.7 I/O Resources

Many useful resources related to I/O are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en546061

## 11.7.1 KEY RESOURCES

- Section 10. "I/O Ports" (DS70193)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

# 16.3 SPI Control Registers

## REGISTER 16-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER

| R/W-0  | U-0    | R/W-0   | U-0 | U-0 | U-0 | U-0    | U-0    |

|--------|--------|---------|-----|-----|-----|--------|--------|

| SPIEN  | _      | SPISIDL |     |     | —   |        | —      |

| bit 15 |        |         |     |     |     |        | bit 8  |

|        |        |         |     |     |     |        |        |

| U-0    | R/C-0  | U-0     | U-0 | U-0 | U-0 | R-0    | R-0    |

| _      | SPIROV | _       | _   | _   | _   | SPITBF | SPIRBF |

| bit 7  |        |         |     |     |     |        | bit 0  |

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15   | SPIEN: SPIx Enable bit                                                                                                                                                                                                                                                                                         |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1 = Enables module and configures SCKx, SDOx, SDIx and $\overline{SSx}$ as serial port pins 0 = Disables module                                                                                                                                                                                                |

| bit 14   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                     |

| bit 13   | SPISIDL: Stop in Idle Mode bit                                                                                                                                                                                                                                                                                 |

|          | <ul> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> </ul>                                                                                                                                                                          |

| bit 12-7 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                     |

| bit 6    | <ul> <li>SPIROV: Receive Overflow Flag bit</li> <li>1 = A new byte/word is completely received and discarded. The user software has not read the previous data in the SPIxBUF register</li> <li>0 = No overflow has occurred</li> </ul>                                                                        |

| bit 5-2  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                     |

| bit 1    | SPITBF: SPIx Transmit Buffer Full Status bit                                                                                                                                                                                                                                                                   |

|          | <ul> <li>1 = Transmit not yet started, SPIxTXB is full</li> <li>0 = Transmit started, SPIxTXB is empty</li> <li>Automatically set in hardware when CPU writes SPIxBUF location, loading SPIxTXB.</li> <li>Automatically cleared in hardware when SPIx module transfers data from SPIxTXB to SPIxSR.</li> </ul> |

| bit 0    | SPIRBF: SPIx Receive Buffer Full Status bit                                                                                                                                                                                                                                                                    |

|          | <ul> <li>1 = Receive complete, SPIxRXB is full</li> <li>0 = Receive is not complete, SPIxRXB is empty</li> <li>Automatically set in hardware when SPIx transfers data from SPIxSR to SPIxRXB.</li> <li>Automatically cleared in hardware when core reads SPIxBUF location, reading SPIxRXB.</li> </ul>         |

| U-0                     | U-0                                                                                                               | U-0                                                                                                                               | U-0                                      | U-0              | U-0              | U-0             | U-0   |

|-------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------|------------------|-----------------|-------|

| —                       | —                                                                                                                 | —                                                                                                                                 | -                                        | —                | _                |                 |       |

| bit 15                  |                                                                                                                   |                                                                                                                                   |                                          |                  |                  |                 | bit   |

| R/W-0                   | R/W-0                                                                                                             | R/W-0                                                                                                                             | U-0                                      | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| IVRIE                   | WAKIE                                                                                                             | ERRIE                                                                                                                             | _                                        | FIFOIE           | RBOVIE           | RBIE            | TBIE  |

| bit 7                   |                                                                                                                   |                                                                                                                                   |                                          |                  |                  |                 | bit   |

| Legend:                 |                                                                                                                   |                                                                                                                                   |                                          |                  |                  |                 |       |

| R = Readab              | le bit                                                                                                            | W = Writable I                                                                                                                    | bit                                      | U = Unimpler     | nented bit, read | as '0'          |       |

| -n = Value a            | t POR                                                                                                             | '1' = Bit is set                                                                                                                  |                                          | '0' = Bit is cle | ared             | x = Bit is unkr | iown  |

| bit 7<br>bit 6<br>bit 5 | 1 = Interrupt n<br>0 = Interrupt n<br><b>WAKIE:</b> Bus<br>1 = Interrupt n<br>0 = Interrupt n                     | I Message Inter<br>request enabled<br>request not ena<br>Wake-up Activit<br>request enabled<br>request not ena<br>Interrupt Enabl | d<br>bled<br>ty Interrupt E<br>d<br>bled |                  |                  |                 |       |

|                         | 0 = Interrupt i                                                                                                   | request enabled<br>request not ena                                                                                                | bled                                     |                  |                  |                 |       |

| bit 4<br>bit 3          | FIFOIE: FIFC                                                                                                      | ted: Read as 'd<br>Almost Full Inf<br>request enabled                                                                             | errupt Enabl                             | e bit            |                  |                 |       |

|                         | 0 = Interrupt i                                                                                                   | request not ena                                                                                                                   | bled                                     |                  |                  |                 |       |

| bit 2                   | 1 = Interrupt i                                                                                                   | Buffer Overflov<br>request enabled<br>request not ena                                                                             | , t                                      | nable bit        |                  |                 |       |

| bit 1                   | <b>RBIE:</b> RX Buffer Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled |                                                                                                                                   |                                          |                  |                  |                 |       |

| bit 0                   | 1 = Interrupt i                                                                                                   | fer Interrupt En<br>request enableo<br>request not ena                                                                            | ł                                        |                  |                  |                 |       |

### **REGISTER 19-7:** CIINTE: ECAN™ MODULE INTERRUPT ENABLE REGISTER

### REGISTER 19-24: CIRXOVF1: ECAN™ MODULE RECEIVE BUFFER OVERFLOW REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXOVF7 | RXOVF6 | RXOVF5 | RXOVF4 | RXOVF3 | RXOVF2 | RXOVF1 | RXOVF0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           | C = Clear only bit |                       |                    |

|-------------------|--------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit   | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **RXOVF15:RXOVF0:** Receive Buffer n Overflow bits

1 = Module pointed a write to a full buffer (set by module)

0 = Overflow is cleared (clear by application software)

### REGISTER 19-25: CIRXOVF2: ECAN™ MODULE RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Clear only bit |                       |                    |

|-------------------|--------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit   | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 RXOVF31:RXOVF16: Receive Buffer n Overflow bits

1 = Module pointed a write to a full buffer (set by module)

0 = Overflow is cleared (clear by application software)

| TABLE 21-2: CONFIGURATION BITS DESCRIPTION |          |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|--------------------------------------------|----------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit Field                                  | Register | RTSP<br>Effect | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| BWRP                                       | FBS      | Immediate      | Boot Segment Program Flash Write Protection<br>1 = Boot segment may be written<br>0 = Boot segment is write-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| BSS<2:0>                                   | FBS      | Immediate      | <ul> <li>Boot Segment Program Flash Code Protection Size</li> <li>x11 = No Boot program Flash segment</li> <li>Boot space is 1K IW less VS</li> <li>110 = Standard security; boot program Flash segment starts at End of VS, ends at 0x0007FE</li> <li>010 = High security; boot program Flash segment starts at End of VS, ends at 0x0007FE</li> <li>Boot space is 4K IW less VS</li> <li>101 = Standard security; boot program Flash segment starts at End of VS, ends at 0x001FFE</li> <li>001 = High security; boot program Flash segment starts at End of VS, ends at 0x001FFE</li> <li>001 = High security; boot program Flash segment starts at End of VS, ends at 0x001FFE</li> <li>Boot space is 8K IW less VS</li> </ul> |  |  |  |  |

|                                            |          |                | <ul> <li>100 = Standard security; boot program Flash segment starts at End of VS, ends at 0x003FFE</li> <li>000 = High security; boot program Flash segment starts at End of VS, ends at 0x003FFE</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| RBS<1:0>                                   | FBS      | Immediate      | Boot Segment RAM Code Protection<br>11 = No Boot RAM defined<br>10 = Boot RAM is 128 Bytes<br>01 = Boot RAM is 256 Bytes<br>00 = Boot RAM is 1024 Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| SWRP                                       | FSS      | Immediate      | Secure Segment Program Flash Write Protection<br>1 = Secure segment may be written<br>0 = Secure segment is write-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

### TABLE 21-2: CONFIGURATION BITS DESCRIPTION

NOTES:

## 23.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows<sup>®</sup> programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC<sup>®</sup> microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

### 23.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

## 23.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

| DC CHA       | RACTER | ISTICS                                                                                                                                    | Standard<br>(unless of<br>Operating | therwis | e stated<br>ature | l)<br>-40°C ≤ | <b>3.0V to 3.6V</b><br>TA $\leq$ +85°C for Industrial<br>TA $\leq$ +125°C for Extended                        |

|--------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------|-------------------|---------------|---------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Symbol | Characteristic                                                                                                                            | Min                                 | Тур     | Max               | Units         | Conditions                                                                                                    |

|              |        | Output Low Voltage<br>I/O Pins:<br>2x Sink Driver Pins - All pins not<br>defined by 4x or 8x driver pins                                  | _                                   | _       | 0.4               | V             | IOL $\leq$ 3 mA, VDD = 3.3V                                                                                   |

| DO10         | Vol    | <b>Output Low Voltage</b><br>I/O Pins:<br>4x Sink Driver Pins - RA2, RA3,<br>RA9, RA10, RA14, RA15, RB0,<br>RB1, RB11, RF4, RF5, RG2, RG3 | _                                   | _       | 0.4               | V             | IOL $\leq$ 6 mA, VDD = 3.3V                                                                                   |

|              |        | Output Low Voltage<br>I/O Pins:<br>8x Sink Driver Pins - OSC2, CLKO,<br>RC15                                                              | _                                   | _       | 0.4               | V             | IOL $\leq$ 10 mA, VDD = 3.3V                                                                                  |

|              |        | Output High Voltage<br>I/O Pins:<br>2x Source Driver Pins - All pins not<br>defined by 4x or 8x driver pins                               | 2.4                                 | _       | _                 | V             | $IOL \ge -3$ mA, VDD = 3.3V                                                                                   |

| DO20 Voн     | Vон    | Output High Voltage<br>I/O Pins:<br>4x Source Driver Pins - RA2, RA3,<br>RA9, RA10, RA14, RA15, RB0,<br>RB1, RB11, RF4, RF5, RG2, RG3     | 2.4                                 | _       | _                 | V             | $IOL \ge -6$ mA, VDD = 3.3V                                                                                   |

|              |        | Output High Voltage<br>I/O Pins:<br>8x Source Driver Pins - OSC2,<br>CLKO, RC15                                                           | 2.4                                 | _       | _                 | V             | IOL ≥ -10 mA, VDD = 3.3V                                                                                      |

|              |        | Output High Voltage<br>I/O Pins:                                                                                                          | 1.5                                 | _       | _                 |               | IOH ≥ -6 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                  |

|              |        | 2x Source Driver Pins - All pins not defined by 4x or 8x driver pins                                                                      | 2.0                                 | _       | _                 | V             | IOH ≥ -5 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                  |

|              |        |                                                                                                                                           | 3.0                                 | _       | _                 |               | $\label{eq:IOH} \begin{array}{l} \mbox{IOH} \geq -2 \mbox{ mA, VDD} = 3.3 V \\ \mbox{See Note 1} \end{array}$ |

|              |        | <b>Output High Voltage</b><br>4x Source Driver Pins - RA2, RA3,                                                                           | 1.5                                 | _       | _                 |               | IOH ≥ -12 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                 |

| DO20A        | Voн1   | RA9, RA10, RA14, RA15, RB0,<br>RB1, RB11, RF4, RF5, RG2, RG3                                                                              | 2.0                                 | -       | _                 | V             | IOH ≥ -11 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                 |

|              |        |                                                                                                                                           | 3.0                                 | _       | _                 |               | $\label{eq:IOH} \begin{array}{l} \mbox{IOH} \geq -3 \mbox{ mA, VDD} = 3.3 V \\ \mbox{See Note 1} \end{array}$ |

|              |        | Output High Voltage<br>8x Source Driver Pins - OSC2,                                                                                      | 1.5                                 | _       | _                 |               | IOH ≥ -16 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                 |

|              |        | CLKO, RC15                                                                                                                                | 2.0                                 |         |                   | V             | IOH ≥ -12 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                 |

|              |        |                                                                                                                                           | 3.0                                 |         |                   |               | IOH ≥ -4 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                  |

### TABLE 24-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

**Note 1:** Parameters are characterized, but not tested.

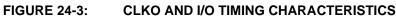

| AC CHARACTERISTICS |        |                                   | Standard Ope<br>(unless other)<br>Operating tem | vise state         | e <b>d)</b><br>-40°C ≤ | Ta≤ +8 | 5°C for l  | ndustrial<br>Extended |

|--------------------|--------|-----------------------------------|-------------------------------------------------|--------------------|------------------------|--------|------------|-----------------------|

| Param<br>No.       | Symbol | Character                         | Min                                             | Typ <sup>(1)</sup> | Max                    | Units  | Conditions |                       |

| DO31               | TioR   | Port Output Rise Time             | e                                               | _                  | 10                     | 25     | ns         |                       |

| DO32               | TIOF   | Port Output Fall Time             |                                                 |                    | 10                     | 25     | ns         | —                     |

| DI35               | TINP   | INTx Pin High or Low Time (input) |                                                 | 20                 | _                      | _      | ns         | _                     |

| DI40               | Trbp   | CNx High or Low Tim               | 2                                               |                    | _                      | TCY    | _          |                       |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

| AC CHA       | AC CHARACTERISTICS |                                                                           |           | d Operati<br>otherwise<br>g tempera | e stated)<br>ature -4 | l0°C ≤ Ta | <b>bV to 3.6V</b><br>≤ +85°C for Industrial<br>≤ +125°C for Extended |

|--------------|--------------------|---------------------------------------------------------------------------|-----------|-------------------------------------|-----------------------|-----------|----------------------------------------------------------------------|

| Param<br>No. | Symbol             | Characteristic                                                            | Min.      | Тур <sup>(2)</sup>                  | Conditions            |           |                                                                      |

|              |                    | Clock                                                                     | Paramete  | ers <sup>(1)</sup>                  |                       |           |                                                                      |

| AD50         | Tad                | ADC Clock Period                                                          | 117.6     |                                     |                       | ns        | _                                                                    |

| AD51         | tRC                | ADC Internal RC Oscillator<br>Period                                      | —         | 250                                 | _                     | ns        | —                                                                    |

|              |                    | Con                                                                       | version R | ate                                 |                       |           |                                                                      |

| AD55         | tCONV              | Conversion Time                                                           |           | 14 Tad                              |                       | ns        | _                                                                    |

| AD56         | FCNV               | Throughput Rate                                                           | _         |                                     | 500                   | ksps      | _                                                                    |

| AD57         | TSAMP              | Sample Time                                                               | 3 Tad     |                                     |                       | _         | _                                                                    |

|              | •                  | Timir                                                                     | g Parame  | ters                                |                       |           |                                                                      |

| AD60         | tPCS               | Conversion Start from Sample<br>Trigger <sup>(2)</sup>                    | 2.0 Tad   | _                                   | 3.0 Tad               | _         | Auto convert trigger not selected                                    |

| AD61         | tPSS               | Sample Start from Setting<br>Sample (SAMP) bit <sup>(2)</sup>             | 2.0 TAD   | —                                   | 3.0 Tad               | _         | _                                                                    |

| AD62         | tcss               | Conversion Completion to<br>Sample Start (ASAM = 1) <sup>(2)</sup>        | —         | 0.5 Tad                             | _                     | —         | _                                                                    |

| AD63         | tDPU               | Time to Stabilize Analog Stage<br>from ADC Off to ADC On <sup>(2,3)</sup> | _         |                                     | 20                    | μS        | _                                                                    |

## TABLE 24-42: ADC CONVERSION (12-BIT MODE) TIMING REQUIREMENTS

**Note 1:** Because the sample caps eventually loses charge, clock rates below 10 kHz may affect linearity performance, especially at elevated temperatures.

**2:** These parameters are characterized but not tested in manufacturing.

**3:** tDPU is the time required for the ADC module to stabilize when it is turned on (AD1CON1<ADON> = 1). During this time, the ADC result is indeterminate.

| TABLE 25-6:       DC CHARACTERISTICS: I/O PIN C         DC CHARACTERISTICS       DC CHARACTERISTICS |        |                                                                                                                                                                                                | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for High<br>Temperature |      |      |       |                                                    |