Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 18x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp506a-e-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

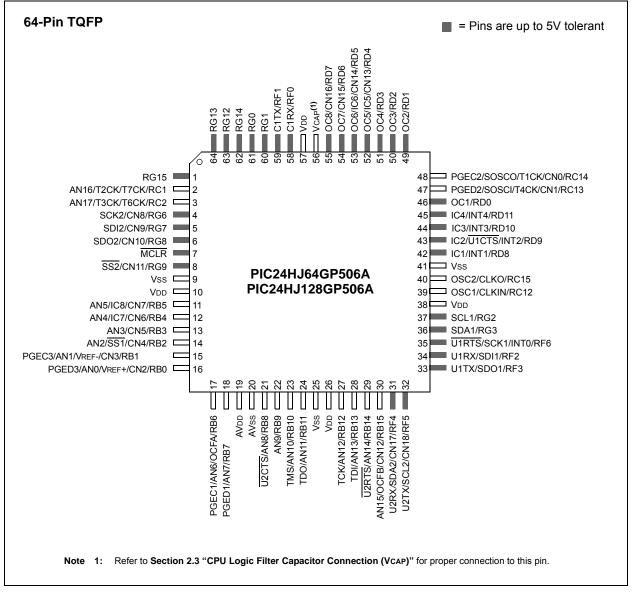

## Pin Diagrams (Continued)

### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to  $\leq$  8 MHz for start-up with PLL enabled to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLDBF to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration word.

## 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 3 or REAL ICE is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins, by setting all bits in the AD1PCFGL register.

The bits in this register that correspond to the A/D pins that are initialized by MPLAB ICD 3 or REAL ICE, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFGL register during initialization of the ADC module.

When MPLAB ICD 3 or REAL ICE is used as a programmer, the user application firmware must correctly configure the AD1PCFGL register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

# 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic-low state.

Alternatively, connect a 1k to 10k resistor between Vss and the unused pins.

### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

| U-0             | R/W-0           | R/W-0                            | R/W-0            | R/W-0                                    | R/W-0            | R/W-0           | R/W-0  |

|-----------------|-----------------|----------------------------------|------------------|------------------------------------------|------------------|-----------------|--------|

|                 | DMA1IF          | AD1IF                            | U1TXIF           | U1RXIF                                   | SPI1IF           | SPI1EIF         | T3IF   |

| bit 15          |                 |                                  |                  |                                          |                  |                 | bit 8  |

|                 |                 |                                  |                  |                                          |                  |                 |        |

| R/W-0           | R/W-0           | R/W-0                            | R/W-0            | R/W-0                                    | R/W-0            | R/W-0           | R/W-0  |

| T2IF            | OC2IF           | IC2IF                            | DMA01IF          | T1IF                                     | OC1IF            | IC1IF           | INTOIF |

| bit 7           |                 |                                  |                  |                                          |                  |                 | bit C  |

| Legend:         |                 |                                  |                  |                                          |                  |                 |        |

| R = Readable    | bit             | W = Writable                     | bit              | U = Unimpler                             | mented bit, rea  | d as '0'        |        |

| -n = Value at F | OR              | '1' = Bit is se                  |                  | '0' = Bit is cle                         |                  | x = Bit is unkn | iown   |

|                 |                 |                                  |                  |                                          |                  |                 |        |

| bit 15          | Unimplemen      | ted: Read as                     | 0'               |                                          |                  |                 |        |

| bit 14          | DMA1IF: DM      | A Channel 1 D                    | ata Transfer C   | Complete Interr                          | rupt Flag Status | bit             |        |

|                 |                 | request has oc                   |                  |                                          |                  |                 |        |

| bit 13          |                 | request has no<br>I Conversion C |                  | unt Elog Statu                           | o hit            |                 |        |

| DIL 13          |                 | request has oc                   | •                | upi riay Sialu                           |                  |                 |        |

|                 |                 | request has no                   |                  |                                          |                  |                 |        |

| bit 12          | U1TXIF: UAF     | RT1 Transmitte                   | r Interrupt Flag | g Status bit                             |                  |                 |        |

|                 |                 | request has oc                   |                  |                                          |                  |                 |        |

|                 |                 | request has no                   |                  |                                          |                  |                 |        |

| bit 11          |                 | RT1 Receiver I<br>request has oc |                  | Status Dit                               |                  |                 |        |

|                 |                 | request has oc                   |                  |                                          |                  |                 |        |

| bit 10          | -               | Event Interrup                   |                  | bit                                      |                  |                 |        |

|                 |                 | request has oc                   |                  |                                          |                  |                 |        |

|                 |                 | request has no                   |                  |                                          |                  |                 |        |

| bit 9           |                 | 1 Fault Interru                  | •                | bit                                      |                  |                 |        |

|                 |                 | request has oc<br>request has no |                  |                                          |                  |                 |        |

| bit 8           |                 | Interrupt Flag                   |                  |                                          |                  |                 |        |

|                 |                 | request has oc                   |                  |                                          |                  |                 |        |

|                 | -               | request has no                   |                  |                                          |                  |                 |        |

| bit 7           |                 | Interrupt Flag                   |                  |                                          |                  |                 |        |

|                 |                 | request has oc<br>request has no |                  |                                          |                  |                 |        |

| bit 6           |                 | ut Compare Ch                    |                  | upt Flag Status                          | s bit            |                 |        |

|                 |                 | request has oc                   |                  | -p · · · · · · · · · · · · · · · · · · · |                  |                 |        |

|                 | 0 = Interrupt i | request has no                   | t occurred       |                                          |                  |                 |        |

| bit 5           | -               | Capture Chann                    | •                | -lag Status bit                          |                  |                 |        |

|                 |                 | request has oc<br>request has no |                  |                                          |                  |                 |        |

| bit 4           | -               | -                                |                  | Complete Inte                            | rrupt Flag Statu | ıs bit          |        |

|                 |                 | request has oc                   |                  |                                          |                  |                 |        |

|                 |                 | request has no                   |                  |                                          |                  |                 |        |

| bit 3           |                 | Interrupt Flag                   |                  |                                          |                  |                 |        |

|                 |                 | request has oc                   |                  |                                          |                  |                 |        |

|                 | 0 = interrupt i | request has no                   | coccurred        |                                          |                  |                 |        |

| REGISTER 7-10: IE | EC0: INTERRUPT ENABLE CONTROL REGISTER 0 |

|-------------------|------------------------------------------|

|-------------------|------------------------------------------|

| U-0           | R/W-0           | R/W-0                            | R/W-0                   | R/W-0            | R/W-0            | R/W-0           | R/W-0           |

|---------------|-----------------|----------------------------------|-------------------------|------------------|------------------|-----------------|-----------------|

| —             | DMA1IE          | AD1IE                            | U1TXIE                  | U1RXIE           | SPI1IE           | SPI1EIE         | T3IE            |

| bit 15        |                 |                                  |                         |                  |                  |                 | bit 8           |

|               | <b>.</b>        | <b>D</b> 444 0                   | <b>DAA</b> ( <b>a</b> ) | <b>D</b> 444 0   | <b>D</b> 444 0   | DAVA            | <b>D</b> 444 0  |

| R/W-0         | R/W-0           | R/W-0                            | R/W-0                   | R/W-0            | R/W-0            | R/W-0           | R/W-0           |

| T2IE<br>bit 7 | OC2IE           | IC2IE                            | DMA0IE                  | T1IE             | OC1IE            | IC1IE           | INTOIE<br>bit C |

|               |                 |                                  |                         |                  |                  |                 |                 |

| Legend:       |                 |                                  |                         |                  |                  |                 |                 |

| R = Readable  | e bit           | W = Writable                     | bit                     | U = Unimpler     | mented bit, read | d as '0'        |                 |

| -n = Value at | POR             | '1' = Bit is se                  | t                       | '0' = Bit is cle | ared             | x = Bit is unkn | own             |

|               |                 |                                  |                         |                  |                  |                 |                 |

| bit 15        | -               | ted: Read as                     |                         |                  |                  |                 |                 |

| bit 14        |                 |                                  |                         | Complete Interr  | rupt Enable bit  |                 |                 |

|               |                 | request enable<br>request not en |                         |                  |                  |                 |                 |

| bit 13        | •               | •                                |                         | rupt Enable bit  |                  |                 |                 |

|               |                 | request enable                   |                         |                  |                  |                 |                 |

|               | -               | request not en                   |                         |                  |                  |                 |                 |

| bit 12        |                 | RT1 Transmitte                   |                         | able bit         |                  |                 |                 |

|               | •               | request enable<br>request not en |                         |                  |                  |                 |                 |

| bit 11        | -               | RT1 Receiver I                   |                         | le bit           |                  |                 |                 |

|               |                 | request enable                   | •                       |                  |                  |                 |                 |

|               | 0 = Interrupt r | request not en                   | abled                   |                  |                  |                 |                 |

| bit 10        |                 | Event Interrup                   |                         |                  |                  |                 |                 |

|               |                 | request enable<br>request not en |                         |                  |                  |                 |                 |

| bit 9         | -               | 1 Error Interru                  |                         |                  |                  |                 |                 |

| bit o         |                 | request enable                   | •                       |                  |                  |                 |                 |

|               | 0 = Interrupt r | request not en                   | abled                   |                  |                  |                 |                 |

| bit 8         |                 | Interrupt Enab                   |                         |                  |                  |                 |                 |

|               |                 | request enable<br>request not en |                         |                  |                  |                 |                 |

| bit 7         | •               | Interrupt Enab                   |                         |                  |                  |                 |                 |

| bit i         |                 | request enable                   |                         |                  |                  |                 |                 |

|               |                 | request not en                   |                         |                  |                  |                 |                 |

| bit 6         | OC2IE: Outpu    | ut Compare Cl                    | nannel 2 Interr         | upt Enable bit   |                  |                 |                 |

|               |                 | request enable                   |                         |                  |                  |                 |                 |

| hit E         | •               | request not en                   |                         | Enabla bit       |                  |                 |                 |

| bit 5         | -               | Capture Chanr<br>request enable  |                         |                  |                  |                 |                 |

|               |                 | request not en                   |                         |                  |                  |                 |                 |

| bit 4         | DMA0IE: DM      | A Channel 0 E                    | ata Transfer (          | Complete Interr  | upt Enable bit   |                 |                 |

|               |                 | request enable                   |                         |                  |                  |                 |                 |

|               | 0 = Interrupt r | request not en                   | abled                   |                  |                  |                 |                 |

| 1.11.0        | •               | •                                |                         |                  |                  |                 |                 |

| bit 3         | T1IE: Timer1    | Interrupt Enab                   | ole bit                 |                  |                  |                 |                 |

### REGISTER 7-27: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

| U-0           | R/W-1                | R/W-0                                    | R/W-0           | U-0              | R/W-1            | R/W-0           | R/W-0  |

|---------------|----------------------|------------------------------------------|-----------------|------------------|------------------|-----------------|--------|

| _             |                      | T8IP<2:0>                                |                 | _                |                  | MI2C2IP<2:0>    |        |

| bit 15        |                      |                                          |                 |                  |                  |                 | bit    |

| U-0           | R/W-1                | R/W-0                                    | R/W-0           | U-0              | R/W-1            | R/W-0           | R/W-0  |

|               | 10,00-1              | SI2C2IP<2:0>                             | 10,00-0         |                  |                  | T7IP<2:0>       | 1000-0 |

| bit 7         |                      | 0120211 12:04                            |                 |                  |                  | 1111 -2.0-      | bit    |

|               |                      |                                          |                 |                  |                  |                 |        |

| Legend:       |                      |                                          |                 |                  |                  |                 |        |

| R = Readabl   | e bit                | W = Writable                             | bit             | U = Unimple      | mented bit, read | d as '0'        |        |

| -n = Value at | POR                  | '1' = Bit is set                         |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 15        | Unimpleme            | ented: Read as '                         | 0'              |                  |                  |                 |        |

| bit 14-12     | -                    | Timer8 Interrupt                         |                 |                  |                  |                 |        |

|               |                      | rupt is priority 7 (                     | -               | y interrupt)     |                  |                 |        |

|               | •                    |                                          |                 |                  |                  |                 |        |

|               | •                    |                                          |                 |                  |                  |                 |        |

|               | 001 = Interi         | rupt is priority 1                       |                 |                  |                  |                 |        |

|               | 000 = Interi         | rupt source is dis                       | abled           |                  |                  |                 |        |

| bit 11        | Unimpleme            | ented: Read as '                         | 0'              |                  |                  |                 |        |

| bit 10-8      |                      | :0>: I2C2 Master                         |                 | •                | 6                |                 |        |

|               | 111 = Interi         | rupt is priority 7 (                     | highest priorit | y interrupt)     |                  |                 |        |

|               | •                    |                                          |                 |                  |                  |                 |        |

|               | •                    |                                          |                 |                  |                  |                 |        |

|               |                      | rupt is priority 1<br>rupt source is dis | abled           |                  |                  |                 |        |

| bit 7         |                      | ented: Read as '                         |                 |                  |                  |                 |        |

| bit 6-4       | -                    | :0>: I2C2 Slave E                        |                 | pt Priority bits |                  |                 |        |

|               |                      | rupt is priority 7 (I                    |                 | • •              |                  |                 |        |

|               | •                    |                                          |                 |                  |                  |                 |        |

|               | •                    |                                          |                 |                  |                  |                 |        |

|               | 001 = Interi         | rupt is priority 1                       |                 |                  |                  |                 |        |

|               | 000 <b>= Inter</b> i | rupt source is dis                       | abled           |                  |                  |                 |        |

| bit 3         | Unimpleme            | ented: Read as '                         | 0'              |                  |                  |                 |        |

| bit 2-0       |                      | Timer7 Interrupt                         | -               |                  |                  |                 |        |

|               | 111 = Interi         | rupt is priority 7 (I                    | highest priorit | y interrupt)     |                  |                 |        |

|               | •                    |                                          |                 |                  |                  |                 |        |

|               | •                    |                                          |                 |                  |                  |                 |        |

|               |                      | rupt is priority 1                       | a la la al      |                  |                  |                 |        |

|               | 000 = Interi         | rupt source is dis                       | abled           |                  |                  |                 |        |

#### REGISTER 8-3: DMAXSTA: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER A

| R/W-0           | R/W-0                                                                | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 |

|-----------------|----------------------------------------------------------------------|-------|-------|--------|----------|-------|-------|

|                 |                                                                      |       | STA   | <15:8> |          |       |       |

| bit 15          |                                                                      |       |       |        |          |       | bit 8 |

|                 |                                                                      |       |       |        |          |       |       |

| R/W-0           | R/W-0                                                                | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 |

|                 |                                                                      |       | STA   | <7:0>  |          |       |       |

| bit 7           |                                                                      |       |       |        |          |       | bit 0 |

|                 |                                                                      |       |       |        |          |       |       |

| Legend:         |                                                                      |       |       |        |          |       |       |

| R = Readable    | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |       |        | d as '0' |       |       |

| -n = Value at P | at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown      |       |       | nown   |          |       |       |

bit 15-0 STA<15:0>: Primary DMA RAM Start Address bits (source or destination)

#### REGISTER 8-4: DMAxSTB: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER B

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0            | R/W-0                               | R/W-0 | R/W-0 |

|-----------------------------------|-------|------------------|------------------------------------|------------------|-------------------------------------|-------|-------|

|                                   |       |                  | STB                                | <15:8>           |                                     |       |       |

| bit 15                            |       |                  |                                    |                  |                                     |       | bit 8 |

|                                   |       |                  |                                    |                  |                                     |       |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0            | R/W-0                               | R/W-0 | R/W-0 |

|                                   |       |                  | STE                                | 3<7:0>           |                                     |       |       |

| bit 7                             |       |                  |                                    |                  |                                     |       | bit 0 |

| Legend:                           |       |                  |                                    |                  |                                     |       |       |

| R = Readable bit W = Writable bit |       | it               | U = Unimplemented bit, read as '0' |                  |                                     |       |       |

| -n = Value at P                   | POR   | '1' = Bit is set |                                    | '0' = Bit is cle | = Bit is cleared x = Bit is unknown |       | nown  |

bit 15-0 STB<15:0>: Secondary DMA RAM Start Address bits (source or destination)

### **REGISTER 8-5:** DMAXPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0                                               | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|-----------------|-------|-----------------------------------------------------|-------|-----------------------------------------|-------|-------|-------|

|                 |       |                                                     | PAD   | <15:8>                                  |       |       |       |

| bit 15          |       |                                                     |       |                                         |       |       | bit 8 |

|                 |       |                                                     |       |                                         |       |       |       |

| R/W-0           | R/W-0 | R/W-0                                               | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                 |       |                                                     | PAD   | )<7:0>                                  |       |       |       |

| bit 7           |       |                                                     |       |                                         |       |       | bit 0 |

|                 |       |                                                     |       |                                         |       |       |       |

| Legend:         |       |                                                     |       |                                         |       |       |       |

| R = Readable    | bit   | W = Writable bit U = Unimplemented bit, read as '0' |       |                                         |       |       |       |

| -n = Value at P | OR    | '1' = Bit is set                                    |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |

bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

# REGISTER 8-6: DMAxCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0    | U-0   | U-0   | U-0   | U-0                 | U-0   | R/W-0 | R/W-0           |

|--------|-------|-------|-------|---------------------|-------|-------|-----------------|

| —      | _     | —     | —     |                     | —     | CNT<  | 9:8> <b>(2)</b> |

| bit 15 |       |       |       |                     |       |       | bit 8           |

|        |       |       |       |                     |       |       |                 |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0               | R/W-0 | R/W-0 | R/W-0           |

|        |       |       | CNT<  | 7:0> <sup>(2)</sup> |       |       |                 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 CNT<9:0>: DMA Transfer Count Register bits<sup>(2)</sup>

- **Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

- 2: Number of DMA transfers = CNT<9:0> + 1.

bit 7

bit 0

| R/W-0                 | R/W-0          | R/W-0                               | R/W-0                 | U-0               | U-0           | U-0            | U-0                  |

|-----------------------|----------------|-------------------------------------|-----------------------|-------------------|---------------|----------------|----------------------|

| T9MD                  | T8MD           | T7MD                                | T6MD                  |                   | _             | _              | _                    |

| bit 15                | - I            |                                     | 1                     |                   |               |                | bit 8                |

|                       |                |                                     |                       |                   |               |                |                      |

| U-0                   | U-0            | U-0                                 | U-0                   | U-0               | U-0           | R/W-0          | R/W-0                |

| _                     |                | —                                   | —                     | —                 | —             | I2C2MD         | AD2MD <sup>(1)</sup> |

| bit 7                 |                |                                     |                       |                   |               |                | bit (                |

| Logondi               |                |                                     |                       |                   |               |                |                      |

| Legend:<br>R = Readal | ble bit        | W = Writable                        | hit                   | U = Unimplem      | ented bit rea | ad as '0'      |                      |

| -n = Value a          |                | '1' = Bit is set                    |                       | '0' = Bit is clea |               | x = Bit is unk | nown                 |

|                       |                |                                     |                       |                   |               |                | -                    |

| bit 15                | T9MD: Timer    | 9 Module Disab                      | ole bit               |                   |               |                |                      |

|                       | 1 = Timer9 m   | odule is disable                    | ed                    |                   |               |                |                      |

|                       | 0 = Timer9 m   | odule is enable                     | d                     |                   |               |                |                      |

| bit 14                | T8MD: Timer    | 8 Module Disab                      | ole bit               |                   |               |                |                      |

|                       |                | odule is disable                    |                       |                   |               |                |                      |

|                       |                | odule is enable                     |                       |                   |               |                |                      |

| bit 13                | T7MD: Timer    | 7 Module Disab                      | ole bit               |                   |               |                |                      |

|                       | -              | odule is disable                    |                       |                   |               |                |                      |

|                       |                | odule is enable                     | -                     |                   |               |                |                      |

| bit 12                |                | 6 Module Disat                      |                       |                   |               |                |                      |

|                       |                | odule is disable<br>odule is enable |                       |                   |               |                |                      |

| bit 11-2              |                | ted: Read as '                      |                       |                   |               |                |                      |

| bit 1                 | •              | 2 Module Disat                      |                       |                   |               |                |                      |

|                       |                | lule is disabled                    |                       |                   |               |                |                      |

|                       |                | lule is enabled                     |                       |                   |               |                |                      |

| bit 0                 |                | 2 Module Disab                      | le bit <sup>(1)</sup> |                   |               |                |                      |

|                       |                | ule is disabled                     |                       |                   |               |                |                      |

|                       | $0 = AD2 \mod$ |                                     |                       |                   |               |                |                      |

**Note 1:** The PCFGx bits will have no effect if the ADC module is disabled by setting this bit. In this case, all port pins multiplexed with ANx will be in Digital mode.

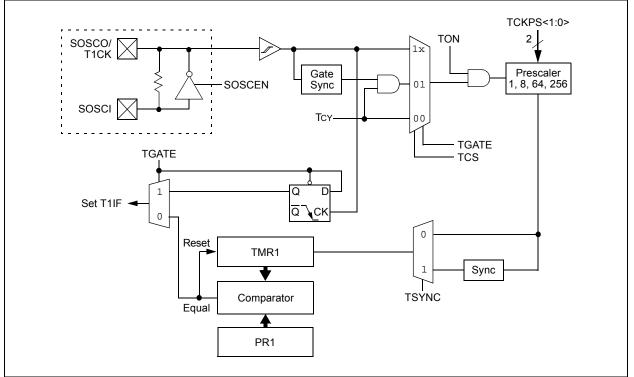

# 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 11. "Timers" (DS70205) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer, which can serve as the time counter for the real-time clock, or operate as a free-running interval timer/counter. Timer1 can operate in three modes:

- 16-bit Timer

- 16-bit Synchronous Counter

- 16-bit Asynchronous Counter

Timer1 also supports these features:

- Timer gate operation

- · Selectable prescaler settings

- Timer operation during CPU Idle and Sleep modes

- Interrupt on 16-bit Period register match or falling edge of external gate signal

Figure 12-1 presents a block diagram of the 16-bit timer module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1) in the T1CON register.

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits in the T1CON register.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits in the T1CON register.

- 4. Set or clear the TSYNC bit in T1CON to select synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the interrupt enable bit, T1IE. Use the priority bits, T1IP<2:0>, to set the interrupt priority.

| U-0             | U-0                                     | R/W-0                                    | R/W-0         | r-0                          | R/W-1            | R/W-0           | R/W-0 |  |  |  |

|-----------------|-----------------------------------------|------------------------------------------|---------------|------------------------------|------------------|-----------------|-------|--|--|--|

| _               | _                                       | CSIDL                                    | ABAT          |                              |                  | REQOP<2:0>      |       |  |  |  |

| bit 15          |                                         |                                          |               |                              |                  |                 | bit   |  |  |  |

| R-1             | R-0                                     | R-0                                      | U-0           | R/W-0                        | U-0              | U-0             | R/W-0 |  |  |  |

|                 | PMODE<2:0                               |                                          | 0-0           | CANCAP                       | 0-0              | 0-0             | WIN   |  |  |  |

| bit 7           |                                         | 12                                       |               | CANCAI                       |                  | _               | bit   |  |  |  |

|                 |                                         |                                          |               |                              |                  |                 |       |  |  |  |

| Legend:         |                                         | r = Bit is Res                           | erved         |                              |                  |                 |       |  |  |  |

| R = Readable b  | bit                                     | W = Writable                             | bit           | U = Unimplen                 | nented bit, read | l as '0'        |       |  |  |  |

| -n = Value at P | OR                                      | '1' = Bit is se                          | t             | '0' = Bit is clea            | ared             | x = Bit is unkr | nown  |  |  |  |

| bit 15-14       | Unimpleme                               | nted: Read as                            | 0'            |                              |                  |                 |       |  |  |  |

| bit 13          | CSIDL: Sto                              | p in Idle Mode b                         | bit           |                              |                  |                 |       |  |  |  |

|                 |                                         | •                                        |               | levice enters Idl            | e mode           |                 |       |  |  |  |

|                 |                                         | e module opera                           |               |                              |                  |                 |       |  |  |  |

| bit 12          |                                         | t All Pending Tr                         |               |                              |                  |                 |       |  |  |  |

|                 | •                                       | Il transmit buffe<br>will clear this bit |               | nsmission<br>smissions are a | borted           |                 |       |  |  |  |

| bit 11          | Reserved: [                             |                                          |               |                              |                  |                 |       |  |  |  |

| bit 10-8        | REQOP<2:0>: Request Operation Mode bits |                                          |               |                              |                  |                 |       |  |  |  |

|                 | 111 = Set Listen All Messages mode      |                                          |               |                              |                  |                 |       |  |  |  |

|                 | 110 = Rese                              | rved – do not us                         | se            |                              |                  |                 |       |  |  |  |

|                 |                                         | rved – do not us                         | -             |                              |                  |                 |       |  |  |  |

|                 |                                         | onfiguration mo                          |               |                              |                  |                 |       |  |  |  |

|                 |                                         | oopback mode                             | 5             |                              |                  |                 |       |  |  |  |

|                 |                                         | isable mode                              |               |                              |                  |                 |       |  |  |  |

|                 | 000 <b>= Set N</b>                      | ormal Operation                          | n mode        |                              |                  |                 |       |  |  |  |

| bit 7-5         | OPMODE<2                                | 2:0>: Operation                          | Mode bits     |                              |                  |                 |       |  |  |  |

|                 |                                         | le is in Listen A                        | ll Messages n | node                         |                  |                 |       |  |  |  |

|                 | 110 = Rese<br>101 = Rese                |                                          |               |                              |                  |                 |       |  |  |  |

|                 |                                         | le is in Configu                         | ation mode    |                              |                  |                 |       |  |  |  |

|                 |                                         | le is in Listen O                        |               |                              |                  |                 |       |  |  |  |

|                 | 010 = Modu                              | le is in Loopbac                         | k mode        |                              |                  |                 |       |  |  |  |

|                 |                                         | le is in Disable<br>le is in Normal      |               | do.                          |                  |                 |       |  |  |  |

| bit 4           |                                         | nted: Read as                            | -             |                              |                  |                 |       |  |  |  |

| bit 3           | -                                       |                                          |               | Capture Event                | Enable bit       |                 |       |  |  |  |

|                 | 1 = Enable i                            | -                                        |               | nessage receive              |                  |                 |       |  |  |  |

| bit 2-1         |                                         | nted: Read as                            | 0'            |                              |                  |                 |       |  |  |  |

| bit 0           | •                                       | Map Window Se                            |               |                              |                  |                 |       |  |  |  |

|                 | 1 = Use filte                           | -                                        |               |                              |                  |                 |       |  |  |  |

|                 |                                         |                                          |               |                              |                  |                 |       |  |  |  |

### REGISTER 19-1: CiCTRL1: ECAN™ MODULE CONTROL REGISTER 1

# REGISTER 19-31: CITRBnSTAT: ECAN™ MODULE RECEIVE BUFFER n STATUS

|                | (n = 0, | 1,, 31)      |       |              |                  |        |       |

|----------------|---------|--------------|-------|--------------|------------------|--------|-------|

| U-0            | U-0     | U-0          | R/W-x | R/W-x        | R/W-x            | R/W-x  | R/W-x |

| —              | —       | —            |       |              | FILHIT<4:0>      |        |       |

| bit 15         |         |              |       |              |                  |        | bit 8 |

|                |         |              |       |              |                  |        |       |

| U-0            | U-0     | U-0          | U-0   | U-0          | U-0              | U-0    | U-0   |

|                |         |              | _     | —            | —                | —      |       |

| bit 7          |         |              |       |              |                  |        | bit 0 |

|                |         |              |       |              |                  |        |       |

| Legend:        |         |              |       |              |                  |        |       |

| R = Readable I | bit     | W = Writable | bit   | U = Unimpler | mented bit, read | as '0' |       |

bit 15-13 **Unimplemented:** Read as '0'

-n = Value at POR

'1' = Bit is set

bit 12-8 **FILHIT<4:0>:** Filter Hit Code bits (only written by module for receive buffers, unused for transmit buffers) Encodes number of filter that resulted in writing this buffer.

'0' = Bit is cleared

bit 7-0 Unimplemented: Read as '0'

x = Bit is unknown

# 20.6 ADC Control Registers

# **REGISTER 20-1:** ADxCON1: ADCx CONTROL REGISTER 1(where x = 1 or 2)

| R/W-0  | U-0       | R/W-0  | R/W-0   | U-0    | R/W-0 | R/W-0 | R/W-0  |

|--------|-----------|--------|---------|--------|-------|-------|--------|

| ADON   | _         | ADSIDL | ADDMABM |        | AD12B | FORM  | 1<1:0> |

| bit 15 |           |        |         |        |       |       | bit 8  |

|        |           |        |         |        |       |       |        |

| R/W-0  | R/W-0     | R/W-0  | U-0     | R/W-0  | R/W-0 | R/W-0 | R/C-0  |

|        |           |        |         |        |       | HC,HS | HC, HS |

|        | SSRC<2:0> |        | —       | SIMSAM | ASAM  | SAMP  | DONE   |

| bit 7  |           |        |         |        |       |       | bit 0  |

| Legend:           | HC = Cleared by hardware | HS = Set by hardware      |                    |  |

|-------------------|--------------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, re | ad as '0'          |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared      | x = Bit is unknown |  |

| bit 15  | ADON: ADC Operating Mode bit                                                                                                                                                                                       |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = ADC module is operating                                                                                                                                                                                        |

|         | 0 = ADC module is off                                                                                                                                                                                              |

| bit 14  | Unimplemented: Read as '0'                                                                                                                                                                                         |

| bit 13  | ADSIDL: Stop in Idle Mode bit                                                                                                                                                                                      |

|         | 1 = Discontinue module operation when device enters Idle mode                                                                                                                                                      |

|         | 0 = Continue module operation in Idle mode                                                                                                                                                                         |

| bit 12  | ADDMABM: DMA Buffer Build Mode bit                                                                                                                                                                                 |

|         | 1 = DMA buffers are written in the order of conversion. The module will provide an address to the DMA channel that is the same as the address used for the non-DMA stand-alone buffer                              |

|         | <ul> <li>DMA buffers are written in Scatter/Gather mode. The module will provide a scatter/gather address<br/>to the DMA channel, based on the index of the analog input and the size of the DMA buffer</li> </ul> |

| bit 11  | Unimplemented: Read as '0'                                                                                                                                                                                         |

| bit 10  | AD12B: 10-Bit or 12-Bit Operation Mode bit                                                                                                                                                                         |

|         | 1 = 12-bit, 1-channel ADC operation                                                                                                                                                                                |

|         | 0 = 10-bit, 4-channel ADC operation                                                                                                                                                                                |

| bit 9-8 | FORM<1:0>: Data Output Format bits                                                                                                                                                                                 |

|         | For 10-bit operation:                                                                                                                                                                                              |

|         | 11 = Reserved                                                                                                                                                                                                      |

|         | 10 = Reserved                                                                                                                                                                                                      |

|         | 01 = Signed integer (Dout = ssss sssd dddd dddd, where s = .NOT.d<9>)<br>00 = Integer (Dout = 0000 00dd dddd dddd)                                                                                                 |

|         | For 12-bit operation:                                                                                                                                                                                              |

|         | 11 = Reserved                                                                                                                                                                                                      |

|         | 10 = Reserved                                                                                                                                                                                                      |

|         | 01 = Signed Integer (DOUT = ssss sddd dddd dddd, where s = .NOT.d<11>)                                                                                                                                             |

|         | 00 = Integer (DOUT = 0000  dddd  dddd  dddd)                                                                                                                                                                       |

| bit 7-5 | SSRC<2:0>: Sample Clock Source Select bits                                                                                                                                                                         |

|         | <ul><li>111 = Internal counter ends sampling and starts conversion (auto-convert)</li><li>110 = Reserved</li></ul>                                                                                                 |

|         | 100 - Reserved                                                                                                                                                                                                     |

|         | 100 = GP timer (Timer5 for ADC1, Timer3 for ADC2) compare ends sampling and starts conversion                                                                                                                      |

|         | 011 = Reserved<br>010 = GP timer (Timer3 for ADC1, Timer5 for ADC2) compare ends sampling and starts conversion                                                                                                    |

|         | 001 = Active transition on INT0 pin ends sampling and starts conversion                                                                                                                                            |

|         | 000 = Clearing sample bit ends sampling and starts conversion                                                                                                                                                      |

| Bit Field  | Register | RTSP<br>Effect | Description                                                                                                                                                                                                             |  |  |  |  |  |

|------------|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| FPWRT<2:0> | FPOR     | Immediate      | Power-on Reset Timer Value Select bits<br>111 = PWRT = 128 ms<br>110 = PWRT = 64 ms<br>101 = PWRT = 32 ms<br>100 = PWRT = 16 ms<br>011 = PWRT = 8 ms<br>010 = PWRT = 4 ms<br>001 = PWRT = 2 ms<br>000 = PWRT = Disabled |  |  |  |  |  |

| JTAGEN     | FICD     | Immediate      | JTAG Enable bits<br>1 = JTAG enabled<br>0 = JTAG disabled                                                                                                                                                               |  |  |  |  |  |

| ICS<1:0>   | FICD     | Immediate      | ICD Communication Channel Select bits<br>11 = Communicate on PGEC1 and PGED1<br>10 = Communicate on PGEC2 and PGED2<br>01 = Communicate on PGEC3 and PGED3<br>00 = Reserved                                             |  |  |  |  |  |

#### TABLE 21-2: CONFIGURATION BITS DESCRIPTION (CONTINUED)

#### TABLE 24-28: SPIx MAXIMUM DATA/CLOCK RATE SUMMARY

| AC CHARACTERISTICS   |                                          |                                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |     |     |  |

|----------------------|------------------------------------------|---------------------------------------------|-------------------------------------------------------|-----|-----|-----|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)            | CKE | СКР | SMP |  |

| 15 MHz               | Table 24-29                              |                                             | —                                                     | 0,1 | 0,1 | 0,1 |  |

| 10 MHz               | —                                        | Table 24-30                                 | —                                                     | 1   | 0,1 | 1   |  |

| 10 MHz               | —                                        | Table 24-31                                 | —                                                     | 0   | 0,1 | 1   |  |

| 15 MHz               | —                                        | —                                           | Table 24-32                                           | 1   | 0   | 0   |  |

| 11 MHz               | —                                        | —                                           | Table 24-33                                           | 1   | 1   | 0   |  |

| 15 MHz               | _                                        | _                                           | Table 24-34                                           | 0   | 1   | 0   |  |

| 11 MHz               |                                          |                                             | Table 24-35                                           | 0   | 0   | 0   |  |

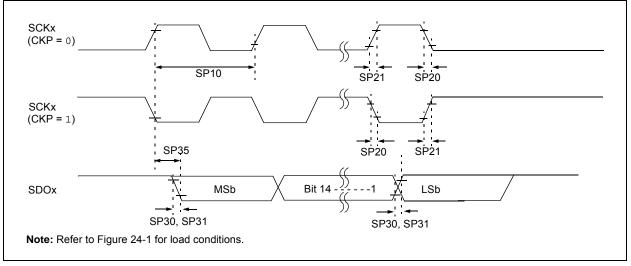

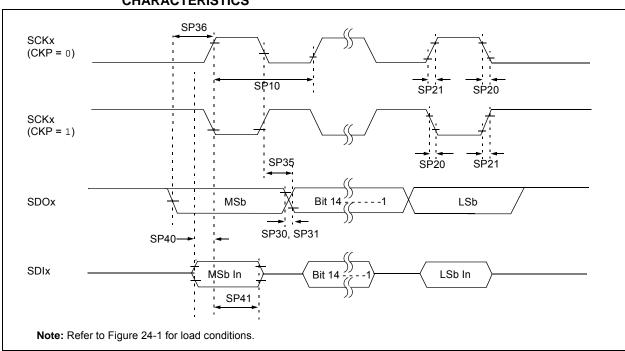

#### FIGURE 24-9: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY CKE = 0) TIMING CHARACTERISTICS

# FIGURE 24-11: SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = X, SMP = 1) TIMING CHARACTERISTICS

# TABLE 24-30:SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING<br/>REQUIREMENTS

| АС СНА       | RACTERIST             | īcs                                           | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                    |     |       |                                      |  |

|--------------|-----------------------|-----------------------------------------------|-------------------------------------------------------|--------------------|-----|-------|--------------------------------------|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                 | Min                                                   | Тур <sup>(2)</sup> | Max | Units | Conditions                           |  |

| SP10         | TscP                  | Maximum SCK Frequency                         | _                                                     | _                  | 10  | MHz   | See Note 3                           |  |

| SP20         | TscF                  | SCKx Output Fall Time                         | _                                                     | —                  |     | ns    | See parameter DO32 and <b>Note 4</b> |  |

| SP21         | TscR                  | SCKx Output Rise Time                         | —                                                     | —                  | _   | ns    | See parameter DO31 and <b>Note 4</b> |  |

| SP30         | TdoF                  | SDOx Data Output Fall Time                    | —                                                     | —                  | _   | ns    | See parameter DO32 and <b>Note 4</b> |  |

| SP31         | TdoR                  | SDOx Data Output Rise Time                    | —                                                     | _                  | —   | ns    | See parameter DO31 and <b>Note 4</b> |  |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge     | —                                                     | 6                  | 20  | ns    | _                                    |  |

| SP36         | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to<br>First SCKx Edge  | 30                                                    | —                  |     | ns    | _                                    |  |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 30                                                    | _                  |     | ns    | _                                    |  |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge  | 30                                                    | —                  | —   | ns    | —                                    |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

- **3:** The minimum clock period for SCKx is 100 ns. The clock generated in Master mode must not violate this specification.

- **4:** Assumes 50 pF load on all SPIx pins.

### 25.1 High Temperature DC Characteristics

#### TABLE 25-1: OPERATING MIPS VS. VOLTAGE

| Characteristic | VDD Range                   | Temperature Range | Max MIPS                   |

|----------------|-----------------------------|-------------------|----------------------------|

| Characteristic | (in Volts)                  | (in °C)           | PIC24HJXXXGPX06A/X08A/X10A |

| HDC5           | VBOR to 3.6V <sup>(1)</sup> | -40°C to +150°C   | 20                         |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules such as the ADC will have degraded performance. Device functionality is tested but not characterized. Refer to parameter BO10 in Table 24-11 for the minimum and maximum BOR values.

#### TABLE 25-2: THERMAL OPERATING CONDITIONS

| TABLE 23-2. THERIMAL OPERATING CONDITIONS                                                                                                                                              |        |               |             |      |      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|-------------|------|------|

| Rating                                                                                                                                                                                 | Symbol | Min           | Тур         | Max  | Unit |

| High Temperature Devices                                                                                                                                                               |        |               |             |      |      |

| Operating Junction Temperature Range                                                                                                                                                   | TJ     | -40           | —           | +155 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                    | TA     | -40           | —           | +150 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD     | I             | Pint + Pi/c | )    | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                      | PDMAX  | (TJ - TA)/θJA |             |      | W    |

#### TABLE 25-3: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARA         | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                |                              |     |     |   |                 |  |  |

|------------------|-------------------------------------------------------|----------------|------------------------------|-----|-----|---|-----------------|--|--|

| Parameter<br>No. | Symbol                                                | Characteristic | Min Typ Max Units Conditions |     |     |   |                 |  |  |

| Operating V      | Voltage                                               |                |                              |     |     |   |                 |  |  |

| HDC10            | Supply Vo                                             | Supply Voltage |                              |     |     |   |                 |  |  |

|                  | Vdd                                                   |                | 3.0                          | 3.3 | 3.6 | V | -40°C to +150°C |  |  |

#### TABLE 25-4: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACTERISTICS (unless oth                                                                                       |               |      |       | perating Co<br>erwise state<br>emperature            | ed) | <b>)V to 3.6V</b><br>≤ +150°C for High Temperature |  |

|----------------------------------------------------------------------------------------------------------------------|---------------|------|-------|------------------------------------------------------|-----|----------------------------------------------------|--|

| Parameter<br>No.                                                                                                     | Typical       | Мах  | Units | Conditions                                           |     |                                                    |  |

| Power-Down                                                                                                           | Current (IPD) |      |       |                                                      |     |                                                    |  |

| HDC60e                                                                                                               | 250           | 2000 | μA    | +150°C 3.3V Base Power-Down Current <sup>(1,3)</sup> |     |                                                    |  |

| <b>Note 1:</b> Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as inputs and |               |      |       |                                                      |     |                                                    |  |

**Note 1:** Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as inputs and pulled to Vss. WDT, etc., are all switched off, and VREGS (RCON<8>) = 1.

2: The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

3: These currents are measured on the device containing the most memory in this family.

4: These parameters are characterized, but are not tested in manufacturing.

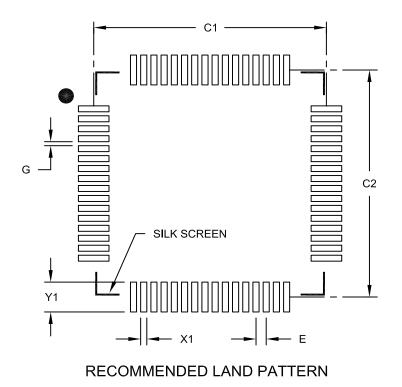

64-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units     |          |       |      |  |

|--------------------------|-----------|----------|-------|------|--|

| Dimensio                 | on Limits | MIN      | NOM   | MAX  |  |

| Contact Pitch            | E         | 0.50 BSC |       |      |  |

| Contact Pad Spacing      | C1        |          | 11.40 |      |  |

| Contact Pad Spacing      | C2        |          | 11.40 |      |  |

| Contact Pad Width (X64)  | X1        |          |       | 0.30 |  |

| Contact Pad Length (X64) | Y1        |          |       | 1.50 |  |

| Distance Between Pads    | G         | 0.20     |       |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2085B

# APPENDIX B: REVISION HISTORY

# Revision A (April 2009)

This is the initial released version of the document.

### **Revision B (October 2009)**

The revision includes the following global update:

Added Note 2 to the shaded table that appears at the beginning of each chapter. This new note provides information regarding the availability of registers and their associated bits

This revision also includes minor typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in the following table.

#### TABLE B-1:MAJOR SECTION UPDATES

| Section Name                                                         | Update Description                                                                                                                                          |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-bit<br>Microcontrollers"                       | Added information on high temperature operation (see <b>"Operating Range:</b> ").                                                                           |

| Section 10.0 "Power-Saving Features"                                 | Updated the last paragraph to clarify the number of cycles that occur prior to the start of instruction execution (see <b>Section 10.2.2 "Idle Mode"</b> ). |

| Section 11.0 "I/O Ports"                                             | Changed the reference to digital-only pins to 5V tolerant pins in the second paragraph of <b>Section 11.2</b> " <b>Open-Drain Configuration</b> ".          |

| Section 18.0 "Universal Asynchronous<br>Receiver Transmitter (UART)" | Updated the two baud rate range features to: 10 Mbps to 38 bps at 40 MIPS.                                                                                  |

| Section 20.0 "10-bit/12-bit Analog-to-Digital Converter (ADC)"       | Updated the ADCx block diagram (see Figure 20-1).                                                                                                           |

| Section 21.0 "Special Features"                                      | Updated the second paragraph and removed the fourth paragraph in <b>Section 21.1 "Configuration Bits"</b> .                                                 |

|                                                                      | Updated the Device Configuration Register Map (see Table 21-1).                                                                                             |

| Section 24.0 "Electrical Characteristics"                            | Updated the Absolute Maximum Ratings for high temperature and added Note 4.                                                                                 |