Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 18x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp506a-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                           | Pin<br>Type                      | Buffer<br>Type                   | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------|----------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN31                                           | I                                | Analog                           | Analog input channels.                                                                                                                                                                                                                                                                                                                                                                                                  |

| AVDD                                               | Р                                | Р                                | Positive supply for analog modules. This pin must be connected at all times.                                                                                                                                                                                                                                                                                                                                            |

| AVss                                               | Р                                | Р                                | Ground reference for analog modules.                                                                                                                                                                                                                                                                                                                                                                                    |

| CLKI<br>CLKO                                       | I<br>O                           | ST/CMOS                          | External clock source input. Always associated with OSC1 pin function.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in RC and EC modes. Always associated<br>with OSC2 pin function.                                                                                                                                                      |

| CN0-CN23                                           | I                                | ST                               | Input change notification inputs.<br>Can be software programmed for internal weak pull-ups on all inputs.                                                                                                                                                                                                                                                                                                               |

| C1RX<br>C1TX<br>C2RX<br>C2TX                       | <br>0<br> <br>0                  | ST<br>—<br>ST<br>—               | ECAN1 bus receive pin.<br>ECAN1 bus transmit pin.<br>ECAN2 bus receive pin.<br>ECAN2 bus transmit pin.                                                                                                                                                                                                                                                                                                                  |

| PGED1<br>PGEC1<br>PGED2<br>PGEC2<br>PGED3<br>PGEC3 | I/O<br>I<br>I/O<br>I<br>I/O<br>I | ST<br>ST<br>ST<br>ST<br>ST<br>ST | Data I/O pin for programming/debugging communication channel 1.<br>Clock input pin for programming/debugging communication channel 1.<br>Data I/O pin for programming/debugging communication channel 2.<br>Clock input pin for programming/debugging communication channel 2.<br>Data I/O pin for programming/debugging communication channel 3.<br>Clock input pin for programming/debugging communication channel 3. |

| IC1-IC8                                            | I                                | ST                               | Capture inputs 1 through 8.                                                                                                                                                                                                                                                                                                                                                                                             |

| INT0<br>INT1<br>INT2<br>INT3<br>INT4               |                                  | ST<br>ST<br>ST<br>ST<br>ST       | External interrupt 0.<br>External interrupt 1.<br>External interrupt 2.<br>External interrupt 3.<br>External interrupt 4.                                                                                                                                                                                                                                                                                               |

| MCLR                                               | I/P                              | ST                               | Master Clear (Reset) input. This pin is an active-low Reset to the device.                                                                                                                                                                                                                                                                                                                                              |

| OCFA<br>OCFB<br>OC1-OC8                            | <br> <br>0                       | ST<br>ST<br>—                    | Compare Fault A input (for Compare Channels 1, 2, 3 and 4).<br>Compare Fault B input (for Compare Channels 5, 6, 7 and 8).<br>Compare outputs 1 through 8.                                                                                                                                                                                                                                                              |

| OSC1<br>OSC2                                       | I<br>I/O                         | ST/CMOS                          | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator                                                                                                                                                                                                                                                    |

| 0002                                               | 1/0                              |                                  | mode. Optionally functions as CLKO in RC and EC modes.                                                                                                                                                                                                                                                                                                                                                                  |

| RA0-RA7<br>RA9-RA10<br>RA12-RA15                   | I/O<br>I/O<br>I/O                | ST<br>ST<br>ST                   | PORTA is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                      |

| RB0-RB15                                           | I/O                              | ST                               | PORTB is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                      |

| RC1-RC4<br>RC12-RC15                               | I/O<br>I/O                       | ST<br>ST                         | PORTC is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                      |

| RD0-RD15                                           | I/O                              | ST                               | PORTD is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                      |

| RE0-RE7                                            | I/O                              | ST                               | PORTE is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                      |

| RF0-RF8<br>RF12-RF13                               | I/O                              | ST                               | PORTF is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                      |

| RG0-RG3<br>RG6-RG9<br>RG12-RG15                    | I/O<br>I/O<br>I/O                | ST<br>ST<br>ST                   | PORTG is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                      |

### TABLE 1-1: PINOUT I/O DESCRIPTIONS

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels Analog = Analog input P = Powe O = Output I = Input

| TABLE 1-1:  | FINUU       |                | CRIPTIONS (CONTINUED)                                          |

|-------------|-------------|----------------|----------------------------------------------------------------|

| Pin Name    | Pin<br>Type | Buffer<br>Type | Description                                                    |

| SCK1        | I/O         | ST             | Synchronous serial clock input/output for SPI1.                |

| SDI1        | I           | ST             | SPI1 data in.                                                  |

| SDO1        | 0           | _              | SPI1 data out.                                                 |

| SS1         | I/O         | ST             | SPI1 slave synchronization or frame pulse I/O.                 |

| SCK2        | I/O         | ST             | Synchronous serial clock input/output for SPI2.                |

| SDI2        | I           | ST             | SPI2 data in.                                                  |

| SDO2        | 0           | _              | SPI2 data out.                                                 |

| SS2         | I/O         | ST             | SPI2 slave synchronization or frame pulse I/O.                 |

| SCL1        | I/O         | ST             | Synchronous serial clock input/output for I2C1.                |

| SDA1        | I/O         | ST             | Synchronous serial data input/output for I2C1.                 |

| SCL2        | I/O         | ST             | Synchronous serial clock input/output for I2C2.                |

| SDA2        | I/O         | ST             | Synchronous serial data input/output for I2C2.                 |

| SOSCI       | I           | ST/CMOS        | 32.768 kHz low-power oscillator crystal input; CMOS otherwise. |

| SOSCO       | 0           | _              | 32.768 kHz low-power oscillator crystal output.                |

| TMS         | I           | ST             | JTAG Test mode select pin.                                     |

| TCK         | I           | ST             | JTAG test clock input pin.                                     |

| TDI         | I           | ST             | JTAG test data input pin.                                      |

| TDO         | 0           | —              | JTAG test data output pin.                                     |

| T1CK        | I           | ST             | Timer1 external clock input.                                   |

| T2CK        | I           | ST             | Timer2 external clock input.                                   |

| T3CK        | I           | ST             | Timer3 external clock input.                                   |

| T4CK        | I           | ST             | Timer4 external clock input.                                   |

| T5CK        | I           | ST             | Timer5 external clock input.                                   |

| T6CK        | I           | ST             | Timer6 external clock input.                                   |

| T7CK        | I           | ST             | Timer7 external clock input.                                   |

| T8CK        | I           | ST             | Timer8 external clock input.                                   |

| T9CK        | Ι           | ST             | Timer9 external clock input.                                   |

| U1CTS       | I           | ST             | UART1 clear to send.                                           |

| U1RTS       | 0           | —              | UART1 ready to send.                                           |

| U1RX        | I           | ST             | UART1 receive.                                                 |

| U1TX        | 0           | —              | UART1 transmit.                                                |

| U2CTS       | I           | ST             | UART2 clear to send.                                           |

| U2RTS       | 0           | —              | UART2 ready to send.                                           |

| U2RX        | I           | ST             | UART2 receive.                                                 |

| U2TX        | 0           | —              | UART2 transmit.                                                |

| Vdd         | Р           | _              | Positive supply for peripheral logic and I/O pins.             |

| VCAP        | Р           |                | CPU logic filter capacitor connection.                         |

| Vss         | Р           |                | Ground reference for logic and I/O pins.                       |

| VREF+       | I           | Analog         | Analog voltage reference (high) input.                         |

| VREF-       | Ι           | Analog         | Analog voltage reference (low) input.                          |

| Legend: CMC | OMO = 200   | S compatible   | e input or output Analog = Analog input P = Power              |

### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels

Analog = Analog input O = Output P = Power I = Input

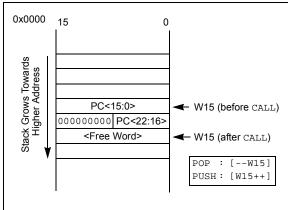

## 4.2.6 SOFTWARE STACK

In addition to its use as a working register, the W15 register in the PIC24HJXXXGPX06A/X08A/X10A devices is also used as a software Stack Pointer. The Stack Pointer always points to the first available free word and grows from lower to higher addresses. It predecrements for stack pops and post-increments for stack pushes, as shown in Figure 4-5. For a PC push during any CALL instruction, the MSB of the PC is zeroextended before the push, ensuring that the MSB is always clear.

| Note: | A PC push during exception processing    |

|-------|------------------------------------------|

|       | concatenates the SRL register to the MSB |

|       | of the PC prior to the push.             |

The Stack Pointer Limit register (SPLIM) associated with the Stack Pointer sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' because all stack operations must be word-aligned. Whenever an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation. Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800. This prevents the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

FIGURE 4-5: CALL STACK FRAME

## 4.2.7 DATA RAM PROTECTION FEATURE

The PIC24H product family supports Data RAM protection features that enable segments of RAM to be protected when used in conjunction with Boot and Secure Code Segment Security. BSRAM (Secure RAM segment for BS) is accessible only from the Boot Segment Flash code, when enabled. SSRAM (Secure RAM segment for RAM) is accessible only from the Secure Segment Flash code, when enabled. See Table 4-1 for an overview of the BSRAM and SSRAM SFRs.

## 4.3 Instruction Addressing Modes

The addressing modes in Table 4-34 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions are somewhat different from those in the other instruction types.

### 4.3.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire data space.

## 4.3.2 MCU INSTRUCTIONS

The 3-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2 where:

Operand 1 is always a working register (i.e., the addressing mode can only be Register Direct) which is referred to as Wb.

Operand 2 can be a W register, fetched from data memory, or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-bit or 10-bit Literal

#### 5.4.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of program Flash memory at a time. To do this, it is necessary to erase the 8-row erase page that contains the desired row. The general process is:

- 1. Read eight rows of program memory (512 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase the page (see Example 5-1):

- a) Set the NVMOP bits (NVMCON<3:0>) to '0010' to configure for block erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the page to be erased into the TBLPAG and W registers.

- Perform a dummy table write operation (TBLWTL) to any address within the page that needs to be erased.

- d) Write 0x55 to NVMKEY.

- e) Write 0xAA to NVMKEY.

- f) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 64 instructions from data RAM into the program memory buffers (see Example 5-2).

- 5. Write the program block to Flash memory:

- a) Set the NVMOP bits to '0001' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 0x55 to NVMKEY.

- c) Write 0xAA to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

- Repeat steps 4 and 5, using the next available 64 instructions from the block in data RAM by incrementing the value in TBLPAG, until all 512 instructions are written back to Flash memory.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-3.

### EXAMPLE 5-1: ERASING A PROGRAM MEMORY PAGE

| ; Set up NVMCON for block erase operation |                                         |

|-------------------------------------------|-----------------------------------------|

| MOV #0x4042, W0                           | i                                       |

| MOV W0, NVMCON                            | ; Initialize NVMCON                     |

| ; Init pointer to row to be ERASED        |                                         |

| MOV #tblpage(PROG_ADDR), W0               | ;                                       |

| MOV W0, TBLPAG                            | ; Initialize PM Page Boundary SFR       |

| MOV #tbloffset(PROG_ADDR), W0             | ; Initialize in-page EA<15:0> pointer   |

| TBLWTL W0, [W0]                           | ; Set base address of erase block       |

| DISI #5                                   | ; Block all interrupts with priority <7 |

|                                           | ; for next 5 instructions               |

| MOV #0x55, W0                             |                                         |

| MOV W0, NVMKEY                            | ; Write the 55 key                      |

| MOV #0xAA, W1                             | ;                                       |

| MOV W1, NVMKEY                            | ; Write the AA key                      |

| BSET NVMCON, #WR                          | ; Start the erase sequence              |

| NOP                                       | ; Insert two NOPs after the erase       |

| NOP                                       | ; command is asserted                   |

|                                           |                                         |

Note: A program memory page erase operation is set up by performing a dummy table write (TBLWTL) operation to any address within the page. This methodology is different from the page erase operation on dsPIC30F/33F devices in which the erase page was selected using a dedicated pair of registers (NVMADRU and NVMADR).

## REGISTER 7-17: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

| U-0              | R/W-1            | R/W-0                                      | R/W-0          | U-0              | R/W-1           | R/W-0           | R/W-0 |

|------------------|------------------|--------------------------------------------|----------------|------------------|-----------------|-----------------|-------|

| —                |                  | U1RXIP<2:0>                                |                | —                |                 | SPI1IP<2:0>     |       |

| bit 15           |                  |                                            |                |                  |                 |                 | bit   |

| 11.0             |                  | R/W-0                                      |                | 11.0             |                 | R/W-0           |       |

| U-0              | R/W-1            | SPI1EIP<2:0>                               | R/W-0          | U-0              | R/W-1           | T3IP<2:0>       | R/W-0 |

| bit 7            |                  | 0111211 \2.02                              |                |                  |                 | 1011 \2.02      | bit   |

| 510 1            |                  |                                            |                |                  |                 |                 | bit   |

| Legend:          |                  |                                            |                |                  |                 |                 |       |

| R = Readabl      | e bit            | W = Writable                               | bit            | U = Unimple      | mented bit, rea | d as '0'        |       |

| -n = Value at    | POR              | '1' = Bit is set                           |                | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |

| bit 15           | Unimpleme        | ented: Read as '                           | 0'             |                  |                 |                 |       |

| bit 14-12        | -                | :0>: UART1 Rece                            |                | Prioritv bits    |                 |                 |       |

|                  |                  | rupt is priority 7 (                       | -              | -                |                 |                 |       |

|                  | •                |                                            |                |                  |                 |                 |       |

|                  | •                |                                            |                |                  |                 |                 |       |

|                  | 001 = Inter      | rupt is priority 1                         |                |                  |                 |                 |       |

|                  |                  | rupt source is dis                         | abled          |                  |                 |                 |       |

| bit 11           | Unimpleme        | ented: Read as '                           | 0'             |                  |                 |                 |       |

| bit 10-8         |                  | >: SPI1 Event In                           | =              | -                |                 |                 |       |

|                  | 111 = Inter      | rupt is priority 7 (                       | highest priori | ty interrupt)    |                 |                 |       |

|                  | •                |                                            |                |                  |                 |                 |       |

|                  | •                |                                            |                |                  |                 |                 |       |

|                  |                  | rupt is priority 1<br>rupt source is dis   | abled          |                  |                 |                 |       |

| bit 7            |                  | ented: Read as '                           |                |                  |                 |                 |       |

| bit 6-4          | -                | :0>: SPI1 Error II                         |                | ty bits          |                 |                 |       |

|                  |                  | rupt is priority 7 (                       | -              | -                |                 |                 |       |

|                  | •                |                                            |                |                  |                 |                 |       |

|                  | •                |                                            |                |                  |                 |                 |       |

|                  |                  | rupt is priority 1                         |                |                  |                 |                 |       |

| <b>h</b> :+ 0    |                  | rupt source is dis                         |                |                  |                 |                 |       |

| bit 3<br>bit 2-0 | -                | ented: Read as '                           |                |                  |                 |                 |       |

| DIL 2-0          |                  | : Timer3 Interrupt<br>rupt is priority 7 ( | -              | v interrunt)     |                 |                 |       |

|                  | •                |                                            | nightest phon  | ly interrupt)    |                 |                 |       |

|                  | •                |                                            |                |                  |                 |                 |       |

|                  | •<br>001 = Inter | muchic criteriter d                        |                |                  |                 |                 |       |

|                  |                  |                                            |                |                  |                 |                 |       |

| U-0            | R/W-1                                                                                                                                   | R/W-0                                  | R/W-0           | U-0              | R/W-1            | R/W-0           | R/W-0 |  |  |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------|------------------|------------------|-----------------|-------|--|--|--|

| —              |                                                                                                                                         | T6IP<2:0>                              |                 | —                | — DMA4IP<2:0>    |                 |       |  |  |  |

| bit 15         |                                                                                                                                         |                                        |                 |                  |                  |                 | bit   |  |  |  |

|                |                                                                                                                                         |                                        |                 |                  |                  |                 |       |  |  |  |

| U-0            | U-0                                                                                                                                     | U-0                                    | U-0             | U-0              | R/W-1            | R/W-0           | R/W-0 |  |  |  |

| _              | —                                                                                                                                       | —                                      |                 |                  |                  | OC8IP<2:0>      |       |  |  |  |

| bit 7          |                                                                                                                                         |                                        |                 |                  |                  |                 | bit   |  |  |  |

| Legend:        |                                                                                                                                         |                                        |                 |                  |                  |                 |       |  |  |  |

| R = Readab     | ole bit                                                                                                                                 | W = Writable                           | bit             | U = Unimple      | mented bit, rea  | d as '0'        |       |  |  |  |

| -n = Value a   | at POR                                                                                                                                  | '1' = Bit is set                       |                 | '0' = Bit is cle | eared            | x = Bit is unkn | iown  |  |  |  |

| bit 1 <i>5</i> | l inima la vere                                                                                                                         | nted. Deed at f                        | <u>`</u>        |                  |                  |                 |       |  |  |  |

| bit 15         | -                                                                                                                                       | nted: Read as '                        |                 |                  |                  |                 |       |  |  |  |

| bit 14-12      |                                                                                                                                         | Timer6 Interrupt                       | •               |                  |                  |                 |       |  |  |  |

|                | <ul> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> </ul>                                                          |                                        |                 |                  |                  |                 |       |  |  |  |

|                | •                                                                                                                                       |                                        |                 |                  |                  |                 |       |  |  |  |

|                | •                                                                                                                                       |                                        |                 |                  |                  |                 |       |  |  |  |

|                |                                                                                                                                         | upt is priority 1                      | ablad           |                  |                  |                 |       |  |  |  |

| L:1 11         |                                                                                                                                         | upt source is dis                      |                 |                  |                  |                 |       |  |  |  |

| bit 11         | -                                                                                                                                       | nted: Read as '                        |                 |                  |                  |                 |       |  |  |  |

| bit 10-8       |                                                                                                                                         | D>: DMA Channe                         |                 | •                | e interrupt Prio | ity bits        |       |  |  |  |

|                | •                                                                                                                                       | upt is priority 7 (I                   | lignest phone   | y interrupt)     |                  |                 |       |  |  |  |

|                | •                                                                                                                                       |                                        |                 |                  |                  |                 |       |  |  |  |

|                | •                                                                                                                                       |                                        |                 |                  |                  |                 |       |  |  |  |

|                |                                                                                                                                         | upt is priority 1                      | ablad           |                  |                  |                 |       |  |  |  |

|                |                                                                                                                                         | upt source is dis                      |                 |                  |                  |                 |       |  |  |  |

| bit 7-3        | Unimplemented: Read as '0'                                                                                                              |                                        |                 |                  |                  |                 |       |  |  |  |

| bit 2-0        | <b>OC8IP&lt;2:0&gt;:</b> Output Compare Channel 8 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                                        |                 |                  |                  |                 |       |  |  |  |

|                | 111 = Interru<br>•                                                                                                                      | upt is priority 7 (i                   | nignest priorit | y interrupt)     |                  |                 |       |  |  |  |

|                | •                                                                                                                                       |                                        |                 |                  |                  |                 |       |  |  |  |

|                |                                                                                                                                         |                                        |                 |                  |                  |                 |       |  |  |  |

|                | •                                                                                                                                       |                                        |                 |                  |                  |                 |       |  |  |  |

|                |                                                                                                                                         | upt is priority 1<br>upt source is dis |                 |                  |                  |                 |       |  |  |  |

### REGISTER 7-26: IPC11: INTERRUPT PRIORITY CONTROL REGISTER 11

### REGISTER 8-2: DMAxREQ: DMA CHANNEL x IRQ SELECT REGISTER

| R/W-0                | U-0   |

|----------------------|-----|-----|-----|-----|-----|-----|-------|

| FORCE <sup>(1)</sup> | —   | —   | —   | —   | —   | —   | —     |

| bit 15               |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0      | R/W-0                  | R/W-0      | R/W-0      |

|-------|------------------------|------------------------|------------------------|------------|------------------------|------------|------------|

| —     | IRQSEL6 <sup>(2)</sup> | IRQSEL5 <sup>(2)</sup> | IRQSEL4 <sup>(2)</sup> | IRQSEL3(2) | IRQSEL2 <sup>(2)</sup> | IRQSEL1(2) | IRQSEL0(2) |

| bit 7 |                        |                        |                        |            |                        |            | bit 0      |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | l as '0'         |                      |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 15 **FORCE:** Force DMA Transfer bit<sup>(1)</sup>

1 = Force a single DMA transfer (Manual mode)

0 = Automatic DMA transfer initiation by DMA request

bit 14-7 Unimplemented: Read as '0'

- bit 6-0 IRQSEL<6:0>: DMA Peripheral IRQ Number Select bits<sup>(2)</sup> 0000000-1111111 = DMAIRQ0-DMAIRQ127 selected to be Channel DMAREQ

- **Note 1:** The FORCE bit cannot be cleared by the user. The FORCE bit is cleared by hardware when the forced DMA transfer is complete.

2: Please see Table 8-1 for a complete listing of IRQ numbers for all interrupt sources.

## **REGISTER 15-1:** OCxCON: OUTPUT COMPARE x CONTROL REGISTER (x = 1, 2)

| U-0    | U-0 | R/W-0  | U-0     | U-0    | U-0   | U-0      | U-0   |

|--------|-----|--------|---------|--------|-------|----------|-------|

| _      | —   | OCSIDL |         | —      | —     | —        | —     |

| bit 15 |     |        | •       |        |       |          | bit 8 |

|        |     |        |         |        |       |          |       |

| U-0    | U-0 | U-0    | R-0, HC | R/W-0  | R/W-0 | R/W-0    | R/W-0 |

|        | —   | —      | OCFLT   | OCTSEL |       | OCM<2:0> |       |

| bit 7  |     |        | •       |        |       |          | bit 0 |

|        |     |        |         |        |       |          |       |

| Legend:           | HC = Hardware Clearable bit |                                    |                    |  |  |

|-------------------|-----------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                          |

|-----------|-------------------------------------------------------------------------------------|

| bit 13    | OCSIDL: Stop Output Compare in Idle Mode Control bit                                |

|           | 1 = Output Compare x halts in CPU Idle mode                                         |

|           | 0 = Output Compare x continues to operate in CPU Idle mode                          |

| bit 12-5  | Unimplemented: Read as '0'                                                          |

| bit 4     | OCFLT: PWM Fault Condition Status bit                                               |

|           | 1 = PWM Fault condition has occurred (cleared in hardware only)                     |

|           | 0 = No PWM Fault condition has occurred (this bit is only used when OCM<2:0> = 111) |

| bit 3     | OCTSEL: Output Compare Timer Select bit                                             |

|           | 1 = Timer3 is the clock source for Compare x                                        |

|           | 0 = Timer2 is the clock source for Compare x                                        |

| bit 2-0   | OCM<2:0>: Output Compare Mode Select bits                                           |

|           | 111 = PWM mode on OCx, Fault pin enabled                                            |

|           | 110 = PWM mode on OCx, Fault pin disabled                                           |

|           | 101 = Initialize OCx pin low, generate continuous output pulses on OCx pin          |

|           | 100 = Initialize OCx pin low, generate single output pulse on OCx pin               |

|           | 011 = Compare event toggles OCx pin                                                 |

|           | 010 = Initialize OCx pin high, compare event forces OCx pin low                     |

|           | 001 = Initialize OCx pin low, compare event forces OCx pin high                     |

|           | 000 = Output compare channel is disabled                                            |

## 16.3 SPI Control Registers

## REGISTER 16-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER

| R/W-0  | U-0    | R/W-0   | U-0 | U-0 | U-0 | U-0    | U-0    |

|--------|--------|---------|-----|-----|-----|--------|--------|

| SPIEN  | _      | SPISIDL |     |     | —   |        | —      |

| bit 15 |        |         |     |     |     |        | bit 8  |

|        |        |         |     |     |     |        |        |

| U-0    | R/C-0  | U-0     | U-0 | U-0 | U-0 | R-0    | R-0    |

| _      | SPIROV | _       | _   | _   | _   | SPITBF | SPIRBF |

| bit 7  |        |         |     |     |     |        | bit 0  |

| Legend:                           | C = Clearable bit |                                    |                    |  |  |

|-----------------------------------|-------------------|------------------------------------|--------------------|--|--|

| R = Readable bit W = Writable bit |                   | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                 | '1' = Bit is set  | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 15   | SPIEN: SPIx Enable bit                                                                                                                                                                                                                                                                                         |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1 = Enables module and configures SCKx, SDOx, SDIx and $\overline{SSx}$ as serial port pins 0 = Disables module                                                                                                                                                                                                |

| bit 14   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                     |

| bit 13   | SPISIDL: Stop in Idle Mode bit                                                                                                                                                                                                                                                                                 |

|          | <ul> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> </ul>                                                                                                                                                                          |

| bit 12-7 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                     |

| bit 6    | <ul> <li>SPIROV: Receive Overflow Flag bit</li> <li>1 = A new byte/word is completely received and discarded. The user software has not read the previous data in the SPIxBUF register</li> <li>0 = No overflow has occurred</li> </ul>                                                                        |

| bit 5-2  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                     |

| bit 1    | SPITBF: SPIx Transmit Buffer Full Status bit                                                                                                                                                                                                                                                                   |

|          | <ul> <li>1 = Transmit not yet started, SPIxTXB is full</li> <li>0 = Transmit started, SPIxTXB is empty</li> <li>Automatically set in hardware when CPU writes SPIxBUF location, loading SPIxTXB.</li> <li>Automatically cleared in hardware when SPIx module transfers data from SPIxTXB to SPIxSR.</li> </ul> |

| bit 0    | SPIRBF: SPIx Receive Buffer Full Status bit                                                                                                                                                                                                                                                                    |

|          | <ul> <li>1 = Receive complete, SPIxRXB is full</li> <li>0 = Receive is not complete, SPIxRXB is empty</li> <li>Automatically set in hardware when SPIx transfers data from SPIxSR to SPIxRXB.</li> <li>Automatically cleared in hardware when core reads SPIxBUF location, reading SPIxRXB.</li> </ul>         |

### REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | ADDEN: Address Character Detect bit (bit 8 of received data = 1)                                                                                                            |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode enabled. If 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode disabled</li> </ul>                     |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                        |

|       | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                       |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                   |

|       | <ul> <li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul> |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                  |

|       | 1 = Framing error has been detected for the current character (character at the top of the receive FIFO)                                                                    |

|       | 0 = Framing error has not been detected                                                                                                                                     |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (read/clear only)                                                                                                             |

|       | 1 = Receive buffer has overflowed                                                                                                                                           |

|       | 0 = Receive buffer has not overflowed. Clearing a previously set OERR bit (1 $\rightarrow$ 0 transition) will reset<br>the receiver buffer and the UxRSR to the empty state |

| bit 0 | URXDA: Receive Buffer Data Available bit (read-only)                                                                                                                        |

|       | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                               |

|       |                                                                                                                                                                             |

**Note 1:** Refer to **Section 17. "UART**" (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for transmit operation.

## **REGISTER 19-11:** CIFEN1: ECAN<sup>™</sup> MODULE ACCEPTANCE FILTER ENABLE REGISTER

| R/W-1                             | R/W-1   | R/W-1   | R/W-1   | R/W-1                              | R/W-1   | R/W-1  | R/W-1  |  |

|-----------------------------------|---------|---------|---------|------------------------------------|---------|--------|--------|--|

| FLTEN15                           | FLTEN14 | FLTEN13 | FLTEN12 | FLTEN11                            | FLTEN10 | FLTEN9 | FLTEN8 |  |

| bit 15                            |         |         |         |                                    |         |        | bit 8  |  |

|                                   |         |         |         |                                    |         |        |        |  |

| R/W-1                             | R/W-1   | R/W-1   | R/W-1   | R/W-1                              | R/W-1   | R/W-1  | R/W-1  |  |

| FLTEN7                            | FLTEN6  | FLTEN5  | FLTEN4  | FLTEN3                             | FLTEN2  | FLTEN1 | FLTEN0 |  |

| bit 7                             |         |         |         |                                    |         |        | bit 0  |  |

|                                   |         |         |         |                                    |         |        |        |  |

| Legend:                           |         |         |         |                                    |         |        |        |  |

| R = Readable bit W = Writable bit |         |         | bit     | U = Unimplemented bit, read as '0' |         |        |        |  |

-n = Value at POR  $(1)^2$  = Bit is set  $(0)^2$  = Bit is cleared x = Bit is unknown

bit 15-0 FLTENn: Enable Filter n (0-15) to Accept Messages bits

1 = Enable Filter n

0 = Disable Filter n

| REGISTER <sup>·</sup>                                                                                                                                       |                                                                            | nSID: ECAN⊺<br>1,, 15)                                                                                                                                                                   | MODULE /                          | ACCEPTANCI               | E FILTER n S                | FANDARD IDI | ENTIFIER |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------|-----------------------------|-------------|----------|--|

| R/W-x                                                                                                                                                       | R/W-x                                                                      | R/W-x                                                                                                                                                                                    | R/W-x                             | R/W-x                    | R/W-x                       | R/W-x       | R/W-x    |  |

|                                                                                                                                                             |                                                                            |                                                                                                                                                                                          | SID<                              | :10:3>                   |                             |             |          |  |

| bit 15                                                                                                                                                      |                                                                            |                                                                                                                                                                                          |                                   |                          |                             |             | bit 8    |  |

| R/W-x                                                                                                                                                       | R/W-x                                                                      | R/W-x                                                                                                                                                                                    | U-0                               | R/W-x                    | U-0                         | R/W-x       | R/W-x    |  |

| SID<2:0>                                                                                                                                                    |                                                                            |                                                                                                                                                                                          |                                   | EXIDE                    |                             | EID<1       | 17:16>   |  |

| bit 7                                                                                                                                                       |                                                                            |                                                                                                                                                                                          |                                   |                          |                             |             | bit C    |  |

| Legend:         R = Readable bit       W = Writable b         -n = Value at POR       '1' = Bit is set         bit 15-5       SID<10:0>: Standard Identifie |                                                                            |                                                                                                                                                                                          | U = Unimplen<br>'0' = Bit is clea | nented bit, read<br>ared | l as '0'<br>x = Bit is unkr | nown        |          |  |

| bit 15-5                                                                                                                                                    | 1 = Message                                                                | address bit SII<br>address bit SII                                                                                                                                                       | Dx must be '1                     |                          |                             |             |          |  |

| bit 4                                                                                                                                                       | Unimplemer                                                                 | ted: Read as '                                                                                                                                                                           | 0'                                |                          |                             |             |          |  |

| bit 3                                                                                                                                                       | <u>If MIDE = 1:</u><br>1 = Match on<br>0 = Match on<br><u>If MIDE = 0:</u> | EXIDE: Extended Identifier Enable bit<br><u>If MIDE = 1:</u><br>1 = Match only messages with extended identifier addresses<br>0 = Match only messages with standard identifier addresses |                                   |                          |                             |             |          |  |

| bit 2                                                                                                                                                       | Unimplemer                                                                 | ted: Read as '                                                                                                                                                                           | 0'                                |                          |                             |             |          |  |

| bit 1-0                                                                                                                                                     | 1 = Message                                                                | Extended Ider<br>address bit Ell<br>address bit Ell                                                                                                                                      | Dx must be '1                     |                          |                             |             |          |  |

## REGISTER 19-17: CiRXFnEID: ECAN<sup>TM</sup> MODULE ACCEPTANCE FILTER n EXTENDED IDENTIFIER (n = 0, 1, ..., 15)

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x           | R/W-x           | R/W-x |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | EID   | <15:8>            |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

| DA4             | D 44/ | D///             |       | D/4/              | D 0 0 /         |                 |       |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x           | R/W-x           | R/W-x |

|                 |       |                  | EID   | <7:0>             |                 |                 |       |

| bit 7           |       |                  |       |                   |                 | bit 0           |       |

| Lanand          |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplen      | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 EID<15:0>: Extended Identifier bits

1 = Message address bit EIDx must be '1' to match filter

0 = Message address bit EIDx must be '0' to match filter

### REGISTER 19-18: CiFMSKSEL1: ECAN™ MODULE FILTER 7-0 MASK SELECTION REGISTER

| R/W-0         | R/W-0                                                       | R/W-0                              | R/W-0            | R/W-0        | R/W-0           | R/W-0    | R/W-   | 0     |

|---------------|-------------------------------------------------------------|------------------------------------|------------------|--------------|-----------------|----------|--------|-------|

| F7MSK<1:0>    |                                                             | F6MSł                              | <<1:0>           | F5MS         | K<1:0>          | F4MSI    | K<1:0> |       |

| bit 15        |                                                             |                                    |                  |              |                 |          |        | bit 8 |

| R/W-0         | R/W-0                                                       | R/W-0                              | R/W-0            | R/W-0        | R/W-0           | R/W-0    | R/W-   | .0    |

| -             | SK<1:0>                                                     | F2MSł                              |                  | -            | K<1:0>          |          | K<1:0> | 0     |

| bit 7         |                                                             | 1 2100                             | ( 1.0            | 1 1110       | 11.0            | 1 0100   | -      | bit 0 |

|               |                                                             |                                    |                  |              |                 |          |        |       |

| Legend:       |                                                             |                                    |                  |              |                 |          |        |       |

| R = Readabl   | e bit                                                       | W = Writable                       | bit              | U = Unimplen | nented bit, rea | d as '0' |        |       |

| -n = Value at | a = Value at POR (1' = Bit is set 0' = Bit is cleared x = E |                                    | x = Bit is unkr  | nown         |                 |          |        |       |

|               |                                                             |                                    |                  |              |                 |          |        |       |

| bit 15-14     |                                                             | : Mask Source                      | e for Filter 7 b | it           |                 |          |        |       |

|               |                                                             | ed; do not use<br>ance Mask 2 reg  | nisters contair  | n mask       |                 |          |        |       |

|               | •                                                           | ance Mask 1 reg                    |                  |              |                 |          |        |       |

|               |                                                             | ance Mask 0 reg                    |                  |              |                 |          |        |       |

| bit 13-12     |                                                             | : Mask Source                      | e for Filter 6 b | it           |                 |          |        |       |

|               |                                                             | ed; do not use<br>ance Mask 2 reg  | nistore contair  | mask         |                 |          |        |       |

|               |                                                             | ance Mask 2 reg                    |                  |              |                 |          |        |       |

|               | •                                                           | ance Mask 0 reg                    | •                |              |                 |          |        |       |

| bit 11-10     |                                                             | : Mask Source                      | e for Filter 5 b | it           |                 |          |        |       |

|               |                                                             | ed; do not use                     | niatoro contair  | mool         |                 |          |        |       |

|               |                                                             | ance Mask 2 reg<br>ance Mask 1 reg |                  |              |                 |          |        |       |

|               |                                                             | ance Mask 0 reg                    |                  |              |                 |          |        |       |

| bit 9-8       | F4MSK<1:0>                                                  | . Mask Source                      | e for Filter 4 b | it           |                 |          |        |       |

|               |                                                             | ed; do not use                     |                  |              |                 |          |        |       |

|               | -                                                           | ance Mask 2 reg<br>ance Mask 1 reg |                  |              |                 |          |        |       |

|               |                                                             | ance Mask 0 reg                    |                  |              |                 |          |        |       |

| bit 7-6       | F3MSK<1:0>                                                  | . Mask Source                      | e for Filter 3 b | it           |                 |          |        |       |

|               |                                                             | ed; do not use                     |                  |              |                 |          |        |       |

|               |                                                             | ance Mask 2 reg<br>ance Mask 1 reg |                  |              |                 |          |        |       |

|               |                                                             | ance Mask 0 reg                    |                  |              |                 |          |        |       |

| bit 5-4       | -                                                           | : Mask Source                      | -                |              |                 |          |        |       |

|               |                                                             | ed; do not use                     |                  |              |                 |          |        |       |

|               |                                                             | ance Mask 2 reg<br>ance Mask 1 reg |                  |              |                 |          |        |       |

|               |                                                             | ance Mask 1 reg                    |                  |              |                 |          |        |       |

| bit 3-2       |                                                             | . Mask Source                      |                  |              |                 |          |        |       |

|               |                                                             | ed; do not use                     |                  |              |                 |          |        |       |

|               |                                                             | ance Mask 2 reg                    |                  |              |                 |          |        |       |

|               |                                                             | ance Mask 1 reg<br>ance Mask 0 reg |                  |              |                 |          |        |       |

| bit 1-0       | -                                                           | : Mask Source                      | -                |              |                 |          |        |       |

|               |                                                             | ed; do not use                     |                  |              |                 |          |        |       |

|               | 10 <b>= Accepta</b>                                         | ance Mask 2 reg                    |                  |              |                 |          |        |       |

|               |                                                             | ance Mask 1 reg                    |                  |              |                 |          |        |       |

|               | 00 = Accepta                                                | ance Mask 0 reg                    | jisters contair  | IIIIask      |                 |          |        |       |