Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 20 MIPS                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 18x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp506a-h-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE       | 4-6:        | TIME   | R REG      | ISTER N | IAP    |        |        |              |              |                |                      |       |        |       |       |       |       |               |

|-------------|-------------|--------|------------|---------|--------|--------|--------|--------------|--------------|----------------|----------------------|-------|--------|-------|-------|-------|-------|---------------|

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14     | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8        | Bit 7          | Bit 6                | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1        | 0100        |        |            |         |        |        |        |              | Timer1       | Register       |                      |       |        |       |       |       |       | 0000          |

| PR1         | 0102        |        |            |         |        |        |        |              | Period F     | Register 1     |                      |       |        |       |       |       |       | FFFF          |

| T1CON       | 0104        | TON    |            | TSIDL   |        | _      | _      | _            | _            | _              | TGATE                | TCKP  | S<1:0> | _     | TSYNC | TCS   | _     | 0000          |

| TMR2        | 0106        |        |            |         |        |        |        |              | Timer2       | Register       |                      |       |        |       |       |       |       | 0000          |

| TMR3HLD     | 0108        |        |            |         |        |        | Tim    | ner3 Holding | Register (fo | r 32-bit time  | operations c         | only) |        |       |       |       |       | xxxx          |

| TMR3        | 010A        |        |            |         |        |        |        |              | Timer3       | Register       |                      |       |        |       |       |       |       | 0000          |

| PR2         | 010C        |        |            |         |        |        |        |              | Period F     | Register 2     |                      |       |        |       |       |       |       | FFFF          |

| PR3         | 010E        |        |            |         |        |        |        |              | Period F     | Register 3     |                      |       |        |       |       |       |       | FFFF          |

| T2CON       | 0110        | TON    |            | TSIDL   | _      | _      | _      | _            | _            | _              | TGATE                | TCKP  | S<1:0> | T32   | —     | TCS   | _     | 0000          |

| T3CON       | 0112        | TON    |            | TSIDL   | _      | _      | _      | _            | _            | _              | TGATE                | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

| TMR4        | 0114        |        |            |         |        |        |        |              | Timer4       | Register       |                      |       |        |       |       |       |       | 0000          |

| TMR5HLD     | 0116        |        |            |         |        |        |        | Timer5 Hold  | ing Register | (for 32-bit op | perations only       | /)    |        |       |       |       |       | xxxx          |

| TMR5        | 0118        |        |            |         |        |        |        |              | Timer5       | Register       |                      |       |        |       |       |       |       | 0000          |

| PR4         | 011A        |        |            |         |        |        |        |              | Period F     | Register 4     |                      |       |        |       |       |       |       | FFFF          |

| PR5         | 011C        |        |            |         |        |        |        |              | Period F     | Register 5     |                      |       |        |       |       |       |       | FFFF          |

| T4CON       | 011E        | TON    | _          | TSIDL   | _      | _      | _      | _            | _            | _              | TGATE                | TCKP  | S<1:0> | T32   | _     | TCS   | _     | 0000          |

| T5CON       | 0120        | TON    | _          | TSIDL   | _      | _      | _      | _            | _            | _              | TGATE                | TCKP  | S<1:0> | _     | _     | TCS   | —     | 0000          |

| TMR6        | 0122        |        |            |         |        |        |        |              | Timer6       | Register       |                      |       |        |       |       |       |       | 0000          |

| TMR7HLD     | 0124        |        |            |         |        |        | -      | Timer7 Hold  | ing Register | (for 32-bit op | perations only       | /)    |        |       |       |       |       | xxxx          |

| TMR7        | 0126        |        |            |         |        |        |        |              | Timer7       | Register       |                      |       |        |       |       |       |       | 0000          |

| PR6         | 0128        |        |            |         |        |        |        |              | Period F     | Register 6     |                      |       |        |       |       |       |       | FFFF          |

| PR7         | 012A        |        |            |         |        |        |        |              | Period F     | Register 7     |                      |       |        |       |       |       |       | FFFF          |

| T6CON       | 012C        | TON    |            | TSIDL   | _      | _      | _      | _            | _            | _              | TGATE                | TCKP  | S<1:0> | T32   | _     | TCS   | _     | 0000          |

| T7CON       | 012E        | TON    |            | TSIDL   | _      | _      | _      | _            | _            | _              | TGATE                | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

| TMR8        | 0130        |        |            |         |        |        |        |              | Timer8       | Register       |                      |       |        |       |       |       |       | 0000          |

| TMR9HLD     | 0132        |        |            |         |        |        | -      | Timer9 Hold  | ing Register | (for 32-bit op | perations only       | /)    |        |       |       |       |       | xxxx          |

| TMR9        | 0134        |        |            |         |        |        |        |              | Timer9       | Register       |                      |       |        |       |       |       |       | 0000          |

| PR8         | 0136        |        |            |         |        |        |        |              | Period F     | Register 8     |                      |       |        |       |       |       |       | FFFF          |

| PR9         | 0138        |        |            |         |        |        |        |              | Period F     | Register 9     |                      |       |        |       |       |       |       | FFFF          |

| T8CON       | 013A        | TON    | _          | TSIDL   | —      | —      | —      | —            | —            | —              | TGATE                | TCKP  | S<1:0> | T32   | _     | TCS   | —     | 0000          |

| T9CON       | 013C        | TON    | _          | TSIDL   | _      | _      | _      | _            | _            | _              | TGATE                | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

| L           |             |        | har an Daa |         |        |        |        |              |              |                | Dire Liberte al avai |       |        |       |       |       |       |               |

#### . . TIMED DEGIGTED MAD

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

| IABLE 4-23 | S: EC | AN2 RI | GISTE  | R MAF  | WHEN   |        | RL1.W  | IN = 1 | FOR PIC | PIC24HJ256GP61UA DEVICES ONLY (CONTINUED) |          |       |       |       |                 |        |            |               |  |

|------------|-------|--------|--------|--------|--------|--------|--------|--------|---------|-------------------------------------------|----------|-------|-------|-------|-----------------|--------|------------|---------------|--|

| File Name  | Addr  | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8   | Bit 7                                     | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2           | Bit 1  | Bit 0      | All<br>Resets |  |

| C2RXF11EID | 056E  |        |        |        | EID<   | 15:8>  |        |        |         |                                           |          |       | EID<7 | /:0>  |                 |        |            | xxxx          |  |

| C2RXF12SID | 0570  |        |        |        | SID<   | 10:3>  |        |        |         | SID<2:0> — EXIDE — EID<17:16>             |          |       |       |       | - EID<17:16> xx |        |            |               |  |

| C2RXF12EID | 0572  |        |        |        | EID<   | 15:8>  |        |        |         |                                           |          |       | EID<7 | ':0>  |                 |        |            | xxxx          |  |

| C2RXF13SID | 0574  |        |        |        | SID<   | 10:3>  |        |        |         |                                           | SID<2:0> |       | _     | EXIDE | —               | EID<1  | EID<17:16> |               |  |

| C2RXF13EID | 0576  |        |        |        | EID<   | 15:8>  |        |        |         |                                           |          |       | EID<7 | ':0>  |                 |        |            | xxxx          |  |

| C2RXF14SID | 0578  |        |        |        | SID<   | 10:3>  |        |        |         |                                           | SID<2:0> |       | _     | EXIDE | —               | EID<1  | 17:16>     | xxxx          |  |

| C2RXF14EID | 057A  |        |        |        | EID<   | 15:8>  |        |        |         |                                           |          |       | EID<7 | ':0>  |                 |        |            | xxxx          |  |

| C2RXF15SID | 057C  |        |        |        | SID<   | 10:3>  |        |        |         | SID<2:0> — EXIDE — EID<17:16>             |          |       |       |       |                 | 17:16> | xxxx       |               |  |

| C2RXF15EID | 057E  |        |        |        | EID<   | 15:8>  |        |        |         |                                           |          |       | EID<7 | /:0>  |                 |        |            | xxxx          |  |

#### TABLE 4-23: ECAN2 REGISTER MAP WHEN C2CTRL1.WIN = 1 FOR PIC24HJ256GP610A DEVICES ONLY (CONTINUED)

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

DS70592D-page 49

#### TABLE 4-31: SYSTEM CONTROL REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8 | Bit 7   | Bit 6  | Bit 5  | Bit 4      | Bit 3 | Bit 2     | Bit 1   | Bit 0 | All<br>Resets       |

|-----------|------|--------|--------|-----------|--------|--------|--------|-----------|-------|---------|--------|--------|------------|-------|-----------|---------|-------|---------------------|

| RCON      | 0740 | TRAPR  | IOPUWR | —         | —      | —      | _      | _         | VREGS | EXTR    | SWR    | SWDTEN | WDTO       | SLEEP | IDLE      | BOR     | POR   | xxxxx(1)            |

| OSCCON    | 0742 | _      | (      | COSC<2:0> | >      | _      | ١      | NOSC<2:0  | >     | CLKLOCK | _      | LOCK   |            | CF    | _         | LPOSCEN | OSWEN | <sub>0300</sub> (2) |

| CLKDIV    | 0744 | ROI    | [      | DOZE<2:0> | >      | DOZEN  | FI     | RCDIV<2:0 | )>    | PLLPOS  | T<1:0> | —      |            | F     | PLLPRE<4: | :0>     |       | 3040                |

| PLLFBD    | 0746 |        | —      |           | —      | —      | _      |           |       |         |        | F      | PLLDIV<8:0 | >     |           |         |       | 0030                |

| OSCTUN    | 0748 |        | —      |           | _      | —      | _      | _         | _     | _       | —      |        |            | TUN   | l<5:0>    |         |       | 0000                |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: RCON register Reset values dependent on type of Reset.

2: OSCCON register Reset values dependent on the FOSC Configuration bits and by type of Reset.

#### TABLE 4-32: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets       |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|--------|-------|--------|-------|---------------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | _      | _      | _      | —     | _     | _     | ERASE |       |       |        | NVMO  | P<3:0> |       | <sub>0000</sub> (1) |

| NVMKEY    | 0766 | —      |        | —      |        |        |        | —     |       |       |       |       | NVMKE | Y<7:0> |       |        |       | 0000                |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: Reset value shown is for POR only. Value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

#### TABLE 4-33: PMD REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|-------|--------|-------|---------------|

| PMD1      | 0770 | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | —      | _     | —     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | C2MD  | C1MD   | AD1MD | 0000          |

| PMD2      | 0772 | IC8MD  | IC7MD  | IC6MD  | IC5MD  | IC4MD  | IC3MD  | IC2MD | IC1MD | OC8MD  | OC7MD | OC6MD | OC5MD  | OC4MD  | OC3MD | OC2MD  | OC1MD | 0000          |

| PMD3      | 0774 | T9MD   | T8MD   | T7MD   | T6MD   | -      | _      | _     | —     | —      | -     | —     |        | _      | _     | I2C2MD | AD2MD | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

| Flag Bit          | Setting Event                                        | Clearing Event               |

|-------------------|------------------------------------------------------|------------------------------|

| TRAPR (RCON<15>)  | Trap conflict event                                  | POR, BOR                     |

| IOPUWR (RCON<14>) | Illegal opcode or uninitialized<br>W register access | POR, BOR                     |

| EXTR (RCON<7>)    | MCLR Reset                                           | POR                          |

| SWR (RCON<6>)     | RESET instruction                                    | POR, BOR                     |

| WDTO (RCON<4>)    | WDT time-out                                         | PWRSAV instruction, POR, BOR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP instruction                            | POR, BOR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE instruction                             | POR, BOR                     |

| BOR (RCON<1>)     | BOR, POR                                             | _                            |

| POR (RCON<0>)     | POR                                                  | _                            |

#### TABLE 6-1:RESET FLAG BIT OPERATION

Note: All Reset flag bits may be set or cleared by the user software.

### 6.1 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen, as shown in Table 6-2. If clock switching is disabled, the system clock source is always selected according to the oscillator Configuration bits. Refer to **Section 9.0** "Oscillator Configuration" for further details.

# TABLE 6-2:OSCILLATOR SELECTION vs.TYPE OF RESET (CLOCK<br/>SWITCHING ENABLED)

| Reset Type | Clock Source Determinant      |

|------------|-------------------------------|

| POR        | Oscillator Configuration bits |

| BOR        | (FNOSC<2:0>)                  |

| MCLR       | COSC Control bits             |

| WDTR       | (OSCCON<14:12>)               |

| SWR        | ]                             |

### 6.2 Device Reset Times

The Reset times for various types of device Reset are summarized in Table 6-3. The system Reset signal is released after the POR and PWRT delay times expire.

The time at which the device actually begins to execute code also depends on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable reset delay times.

The FSCM delay determines the time at which the FSCM begins to monitor the system clock source after the reset signal is released.

| R/W-0            | R-0                                             | U-0                                                                                            | U-0                             | U-0              | U-0              | U-0             | U-0           |

|------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------|------------------|------------------|-----------------|---------------|

| ALTIVT           | DISI                                            | _                                                                                              | _                               | _                | _                | _               | _             |

| bit 15           |                                                 |                                                                                                |                                 |                  |                  |                 | bit 8         |

|                  |                                                 |                                                                                                |                                 |                  |                  |                 |               |

| U-0              | U-0                                             | U-0                                                                                            | R/W-0                           | R/W-0            | R/W-0            | R/W-0           | R/W-0         |

| <br>bit 7        | _                                               | —                                                                                              | INT4EP                          | INT3EP           | INT2EP           | INT1EP          | INT0EP<br>bit |

|                  |                                                 |                                                                                                |                                 |                  |                  |                 | DI            |

| Legend:          |                                                 |                                                                                                |                                 |                  |                  |                 |               |

| R = Readable     | e bit                                           | W = Writable                                                                                   | bit                             | U = Unimpler     | mented bit, read | l as '0'        |               |

| -n = Value at    | POR                                             | '1' = Bit is set                                                                               |                                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown          |

| bit 15<br>bit 14 | 0 = Use stand<br>DISI: DISI In<br>1 = DISI inst | nate vector tab<br>lard (default) v<br>struction Statu<br>ruction is activ<br>ruction is not a | le<br>ector table<br>s bit<br>e |                  |                  |                 |               |

| bit 13-5         | Unimplement                                     | ted: Read as '                                                                                 | 0'                              |                  |                  |                 |               |

| bit 4            | 1 = Interrupt o                                 | rnal Interrupt 4<br>on negative ed<br>on positive edg                                          | ge                              | Polarity Select  | t bit            |                 |               |

| bit 3            | 1 = Interrupt o                                 | rnal Interrupt 3<br>on negative ed<br>on positive edg                                          | ge                              | Polarity Select  | t bit            |                 |               |

| bit 2            | 1 = Interrupt o                                 | rnal Interrupt 2<br>on negative ed<br>on positive edg                                          | ge                              | Polarity Select  | t bit            |                 |               |

| bit 1            | 1 = Interrupt o                                 | rnal Interrupt ´<br>on negative ed<br>on positive edg                                          | ge                              | Polarity Select  | t bit            |                 |               |

| bit 0            | 1 = Interrupt c                                 | rnal Interrupt (<br>on negative ed<br>on positive edg                                          | ge                              | Polarity Select  | t bit            |                 |               |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

#### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

| U-0             | R/W-0           | R/W-0                            | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|-----------------|-----------------|----------------------------------|------------------|------------------|------------------|-----------------|--------|

|                 | DMA1IF          | AD1IF                            | U1TXIF           | U1RXIF           | SPI1IF           | SPI1EIF         | T3IF   |

| bit 15          |                 |                                  |                  |                  |                  |                 | bit 8  |

|                 |                 |                                  |                  |                  |                  |                 |        |

| R/W-0           | R/W-0           | R/W-0                            | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| T2IF            | OC2IF           | IC2IF                            | DMA01IF          | T1IF             | OC1IF            | IC1IF           | INTOIF |

| bit 7           |                 |                                  |                  |                  |                  |                 | bit C  |

| Legend:         |                 |                                  |                  |                  |                  |                 |        |

| R = Readable    | bit             | W = Writable                     | bit              | U = Unimpler     | mented bit, rea  | d as '0'        |        |

| -n = Value at F | OR              | '1' = Bit is se                  |                  | '0' = Bit is cle |                  | x = Bit is unkn | iown   |

|                 |                 |                                  |                  |                  |                  |                 |        |

| bit 15          | Unimplemen      | ted: Read as                     | 0'               |                  |                  |                 |        |

| bit 14          | DMA1IF: DM      | A Channel 1 D                    | ata Transfer C   | Complete Interr  | rupt Flag Status | bit             |        |

|                 |                 | request has oc                   |                  |                  |                  |                 |        |

| bit 13          |                 | request has no<br>I Conversion C |                  | unt Elog Statu   | o hit            |                 |        |

| DIL 13          |                 | request has oc                   | •                | upi riay Sialu   |                  |                 |        |

|                 |                 | request has no                   |                  |                  |                  |                 |        |

| bit 12          | U1TXIF: UAF     | RT1 Transmitte                   | r Interrupt Flag | g Status bit     |                  |                 |        |

|                 |                 | request has oc                   |                  |                  |                  |                 |        |

|                 |                 | request has no                   |                  |                  |                  |                 |        |

| bit 11          |                 | RT1 Receiver I<br>request has oc |                  | Status Dit       |                  |                 |        |

|                 |                 | request has oc                   |                  |                  |                  |                 |        |

| bit 10          | -               | Event Interrup                   |                  | bit              |                  |                 |        |

|                 |                 | request has oc                   |                  |                  |                  |                 |        |

|                 |                 | request has no                   |                  |                  |                  |                 |        |

| bit 9           |                 | 1 Fault Interru                  | •                | bit              |                  |                 |        |

|                 |                 | request has oc<br>request has no |                  |                  |                  |                 |        |

| bit 8           |                 | Interrupt Flag                   |                  |                  |                  |                 |        |

|                 |                 | request has oc                   |                  |                  |                  |                 |        |

|                 | -               | request has no                   |                  |                  |                  |                 |        |

| bit 7           |                 | Interrupt Flag                   |                  |                  |                  |                 |        |

|                 |                 | request has oc<br>request has no |                  |                  |                  |                 |        |

| bit 6           |                 | ut Compare Ch                    |                  | upt Flag Status  | s bit            |                 |        |

|                 |                 | request has oc                   |                  | -p               |                  |                 |        |

|                 | 0 = Interrupt i | request has no                   | t occurred       |                  |                  |                 |        |

| bit 5           | -               | Capture Chann                    | •                | -lag Status bit  |                  |                 |        |

|                 |                 | request has oc<br>request has no |                  |                  |                  |                 |        |

| bit 4           | -               | -                                |                  | Complete Inte    | rrupt Flag Statu | ıs bit          |        |

|                 |                 | request has oc                   |                  |                  |                  |                 |        |

|                 |                 | request has no                   |                  |                  |                  |                 |        |

| bit 3           |                 | Interrupt Flag                   |                  |                  |                  |                 |        |

|                 |                 | request has oc                   |                  |                  |                  |                 |        |

|                 | 0 = interrupt i | request has no                   | coccurred        |                  |                  |                 |        |

#### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 2 | OC1IF: Output Compare Channel 1 Interrupt Flag Status bit |

|-------|-----------------------------------------------------------|

|       | <ol> <li>Interrupt request has occurred</li> </ol>        |

|       | 0 = Interrupt request has not occurred                    |

| bit 1 | IC1IF: Input Capture Channel 1 Interrupt Flag Status bit  |

|       | 1 = Interrupt request has occurred                        |

|       | 0 = Interrupt request has not occurred                    |

| bit 0 | INTOIF: External Interrupt 0 Flag Status bit              |

|       | 1 = Interrupt request has occurred                        |

|       | 0 = Interrupt request has not occurred                    |

| U-0             | U-0        | U-0                               | U-0             | U-0              | U-0              | U-0             | U-0 |

|-----------------|------------|-----------------------------------|-----------------|------------------|------------------|-----------------|-----|

| _               | _          | _                                 | _               | _                |                  |                 | _   |

| bit 15          |            |                                   |                 |                  |                  |                 | bit |

|                 | DAM 0      | DAMA                              | DAMA            |                  | DANO             | DAMO            |     |

| R/W-0<br>C2TXIE | R/W-0      | R/W-0                             | R/W-0<br>DMA6IE | U-0              | R/W-0            | R/W-0           | U-0 |

| bit 7           | C1TXIE     | DIVIA/IE                          | DIVIAGE         |                  | U2EIE            | U1EIE           | bit |

|                 |            |                                   |                 |                  |                  |                 |     |

| Legend:         |            |                                   |                 |                  |                  |                 |     |

| R = Readable    | e bit      | W = Writable                      | bit             | U = Unimpler     | nented bit, read | d as '0'        |     |

| -n = Value at   | POR        | '1' = Bit is set                  |                 | '0' = Bit is cle | ared             | x = Bit is unkn | own |

|                 |            |                                   | - 1             |                  |                  |                 |     |

| bit 15-8        | •          | ited: Read as '                   |                 |                  |                  |                 |     |

| bit 7           |            |                                   | •               | Interrupt Enable | e bit            |                 |     |

|                 |            | request enable<br>request not ena |                 |                  |                  |                 |     |

| bit 6           |            | -                                 |                 | Interrupt Enable | ⊇ hit            |                 |     |

|                 |            | request enable                    | •               |                  |                  |                 |     |

|                 |            | request not ena                   |                 |                  |                  |                 |     |

| bit 5           | DMA7IE: DM | IA Channel 7 D                    | ata Transfer (  | Complete Enab    | le Status bit    |                 |     |

|                 |            | request enable                    |                 |                  |                  |                 |     |

|                 |            | request not ena                   |                 |                  |                  |                 |     |

| bit 4           |            |                                   |                 | Complete Enab    | le Status bit    |                 |     |

|                 |            | request enable                    |                 |                  |                  |                 |     |

| L:4 0           | -          | request not ena                   |                 |                  |                  |                 |     |

| bit 3           | -          | ited: Read as '                   |                 |                  |                  |                 |     |

| bit 2           |            | T2 Error Interru                  |                 |                  |                  |                 |     |

|                 | •          | request enable<br>request not ena |                 |                  |                  |                 |     |

| bit 1           |            | T1 Error Interru                  |                 |                  |                  |                 |     |

|                 |            | request enable                    |                 |                  |                  |                 |     |

|                 |            | request not ena                   |                 |                  |                  |                 |     |

|                 |            |                                   |                 |                  |                  |                 |     |

#### REGISTER 7-14: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

#### REGISTER 7-27: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

| U-0           | R/W-1                | R/W-0                                    | R/W-0           | U-0              | R/W-1            | R/W-0           | R/W-0  |

|---------------|----------------------|------------------------------------------|-----------------|------------------|------------------|-----------------|--------|

| _             |                      | T8IP<2:0>                                |                 | _                |                  | MI2C2IP<2:0>    |        |

| bit 15        |                      |                                          |                 |                  |                  |                 | bit    |

| U-0           | R/W-1                | R/W-0                                    | R/W-0           | U-0              | R/W-1            | R/W-0           | R/W-0  |

|               | 10,00-1              | SI2C2IP<2:0>                             | 10,00-0         |                  |                  | T7IP<2:0>       | 1000-0 |

| bit 7         |                      | 0120211 12:04                            |                 |                  |                  | 1111 -2.0-      | bit    |

|               |                      |                                          |                 |                  |                  |                 |        |

| Legend:       |                      |                                          |                 |                  |                  |                 |        |

| R = Readabl   | e bit                | W = Writable                             | bit             | U = Unimple      | mented bit, read | d as '0'        |        |

| -n = Value at | POR                  | '1' = Bit is set                         |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 15        | Unimpleme            | ented: Read as '                         | 0'              |                  |                  |                 |        |

| bit 14-12     | -                    | Timer8 Interrupt                         |                 |                  |                  |                 |        |

|               |                      | rupt is priority 7 (                     | -               | y interrupt)     |                  |                 |        |

|               | •                    |                                          |                 |                  |                  |                 |        |

|               | •                    |                                          |                 |                  |                  |                 |        |

|               | 001 = Interi         | rupt is priority 1                       |                 |                  |                  |                 |        |

|               | 000 = Interi         | rupt source is dis                       | abled           |                  |                  |                 |        |

| bit 11        | Unimpleme            | ented: Read as '                         | 0'              |                  |                  |                 |        |

| bit 10-8      |                      | :0>: I2C2 Master                         |                 | •                | 6                |                 |        |

|               | 111 = Interi         | rupt is priority 7 (                     | highest priorit | y interrupt)     |                  |                 |        |

|               | •                    |                                          |                 |                  |                  |                 |        |

|               | •                    |                                          |                 |                  |                  |                 |        |

|               |                      | rupt is priority 1<br>rupt source is dis | abled           |                  |                  |                 |        |

| bit 7         |                      | ented: Read as '                         |                 |                  |                  |                 |        |

| bit 6-4       | -                    | :0>: I2C2 Slave E                        |                 | pt Priority bits |                  |                 |        |

|               |                      | rupt is priority 7 (I                    |                 | • •              |                  |                 |        |

|               | •                    |                                          |                 |                  |                  |                 |        |

|               | •                    |                                          |                 |                  |                  |                 |        |

|               | 001 = Interi         | rupt is priority 1                       |                 |                  |                  |                 |        |

|               | 000 <b>= Inter</b> i | rupt source is dis                       | abled           |                  |                  |                 |        |

| bit 3         | Unimpleme            | ented: Read as '                         | 0'              |                  |                  |                 |        |

| bit 2-0       |                      | Timer7 Interrupt                         | -               |                  |                  |                 |        |

|               | 111 = Interi         | rupt is priority 7 (I                    | highest priorit | y interrupt)     |                  |                 |        |

|               | •                    |                                          |                 |                  |                  |                 |        |

|               | •                    |                                          |                 |                  |                  |                 |        |

|               |                      | rupt is priority 1                       | a la la al      |                  |                  |                 |        |

|               | 000 = Interi         | rupt source is dis                       | abled           |                  |                  |                 |        |

#### REGISTER 7-29: IPC14: INTERRUPT PRIORITY CONTROL REGISTER 14

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0   | U-0       | U-0   |

|---------|-----|-----|-----|-----|-------|-----------|-------|

| —       | —   | —   | —   | —   | —     | —         | —     |

| bit 15  |     | •   |     |     |       |           | bit 8 |

|         |     |     |     |     |       |           |       |

| U-0     | U-0 | U-0 | U-0 | U-0 | R/W-1 | R/W-0     | R/W-0 |

| _       | —   | —   | —   | —   |       | C2IP<2:0> |       |

| bit 7   |     |     |     |     |       |           | bit 0 |

|         |     |     |     |     |       |           |       |

| Logond: |     |     |     |     |       |           |       |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-3 | Unimplemented: Read as '0' |

|----------|----------------------------|

|----------|----------------------------|

- C2IP<2:0>: ECAN2 Event Interrupt Priority bits

- 111 = Interrupt is priority 7 (highest priority interrupt)

- •

bit 2-0

- •

- 001 = Interrupt is priority 1

- 000 = Interrupt source is disabled

#### REGISTER 7-30: IPC15: INTERRUPT PRIORITY CONTROL REGISTER 15

| U-0           | U-0           | U-0                | U-0             | U-0                                     | U-0               | U-0    | U-0   |  |

|---------------|---------------|--------------------|-----------------|-----------------------------------------|-------------------|--------|-------|--|

| _             | —             | —                  | _               |                                         | —                 | —      | _     |  |

| bit 15        |               |                    |                 |                                         |                   |        | bit 8 |  |

|               |               |                    |                 |                                         |                   |        |       |  |

| U-0           | R/W-1         | R/W-0              | R/W-0           | U-0                                     | U-0               | U-0    | U-0   |  |

| —             |               | DMA5IP<2:0>        |                 |                                         | —                 | —      | —     |  |

| bit 7         |               |                    |                 |                                         |                   |        | bit 0 |  |

|               |               |                    |                 |                                         |                   |        |       |  |

| Legend:       |               |                    |                 |                                         |                   |        |       |  |

| R = Readable  | e bit         | W = Writable       | bit             | U = Unimpler                            | nented bit, read  | as '0' |       |  |

| -n = Value at | POR           | '1' = Bit is set   |                 | '0' = Bit is cleared x = Bit is unknown |                   |        |       |  |

|               |               |                    |                 |                                         |                   |        |       |  |

| bit 15-7      | Unimplemer    | ted: Read as '     | 0'              |                                         |                   |        |       |  |

| bit 6-4       | DMA5IP<2:0    | >: DMA Chann       | el 5 Data Tra   | nsfer Complete                          | Interrupt Priorit | y bits |       |  |

|               | 111 = Interru | pt is priority 7 ( | highest priorit | y interrupt)                            |                   |        |       |  |

|               | •             |                    |                 |                                         |                   |        |       |  |

|               |               |                    |                 |                                         |                   |        |       |  |

001 = Interrupt is priority 1 000 = Interrupt source is disabled

bit 3-0 Unimplemented: Read as '0'

### 9.1 CPU Clocking System

There are seven system clock options provided by the PIC24HJXXXGPX06A/X08A/X10A:

- FRC Oscillator

- FRC Oscillator with PLL

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- Secondary (LP) Oscillator

- LPRC Oscillator

- FRC Oscillator with postscaler

#### 9.1.1 SYSTEM CLOCK SOURCES

The FRC (Fast RC) internal oscillator runs at a nominal frequency of 7.37 MHz. The user software can tune the FRC frequency. User software can optionally specify a factor (ranging from 1:2 to 1:256) by which the FRC clock frequency is divided. This factor is selected using the FRCDIV<2:0> (CLKDIV<10:8>) bits.

The primary oscillator can use one of the following as its clock source:

- XT (Crystal): Crystals and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- HS (High-Speed Crystal): Crystals in the range of 10 MHz to 40 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- EC (External Clock): External clock signal is directly applied to the OSC1 pin.

The secondary (LP) oscillator is designed for low power and uses a 32.768 kHz crystal or ceramic resonator. The LP oscillator uses the SOSCI and SOSCO pins.

The LPRC (Low-Power RC) internal oscillator runs at a nominal frequency of 32.768 kHz. It is also used as a reference clock by the Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The clock signals generated by the FRC and primary oscillators can be optionally applied to an on-chip Phase-Locked Loop (PLL) to provide a wide range of output frequencies for device operation. PLL configuration is described in **Section 9.1.3 "PLL Configuration**".

The FRC frequency depends on the FRC accuracy (see Table 24-19) and the value of the FRC Oscillator Tuning register (see Register 9-4).

### 9.1.2 SYSTEM CLOCK SELECTION

The oscillator source that is used at a device Power-on Reset event is selected using Configuration bit settings. The oscillator Configuration bit settings are located in the Configuration registers in the program memory. (Refer to **Section 21.1 "Configuration Bits"** for further details.) The Initial Oscillator Selection Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), and the Primary Oscillator Mode Select Configuration bits, POSCMD<1:0> (FOSC<1:0>), select the oscillator source that is used at a Power-on Reset. The FRC primary oscillator is the default (unprogrammed) selection.

The Configuration bits allow users to choose between twelve different clock modes, shown in Table 9-1.

The output of the oscillator (or the output of the PLL if a PLL mode has been selected) FOSC is divided by 2 to generate the device instruction clock (FCY) and the peripheral clock time base (FP). FCY defines the operating speed of the device, and speeds up to 40 MHz are supported by the PIC24HJXXXGPX06A/ X08A/X10A architecture.

Instruction execution speed or device operating frequency, FCY, is calculated, as shown in Equation 9-1:

#### EQUATION 9-1: DEVICE OPERATING FREQUENCY

$$FCY = \frac{FOSC}{2}$$

#### 9.1.3 PLL CONFIGURATION

The primary oscillator and internal FRC oscillator can optionally use an on-chip PLL to obtain higher speeds of operation. The PLL provides a significant amount of flexibility in selecting the device operating speed. A block diagram of the PLL is shown in Figure 9-2.

The output of the primary oscillator or FRC, denoted as 'FIN', is divided down by a prescale factor (N1) of 2, 3, ... or 33 before being provided to the PLL's Voltage Controlled Oscillator (VCO). The input to the VCO must be selected to be in the range of 0.8 MHz to 8 MHz. Since the minimum prescale factor is 2, this implies that FIN must be chosen to be in the range of 1.6 MHz to 16 MHz. The prescale factor 'N1' is selected using the PLLPRE<4:0> bits (CLKDIV<4:0>).

The PLL Feedback Divisor, selected using the PLLDIV<8:0> bits (PLLFBD<8:0>), provides a factor 'M', by which the input to the VCO is multiplied. This factor must be selected such that the resulting VCO output frequency is in the range of 100 MHz to 200 MHz.

The VCO output is further divided by a postscale factor 'N2'. This factor is selected using the PLLPOST<1:0> bits (CLKDIV<7:6>). 'N2' can be either 2, 4 or 8, and must be selected such that the PLL output frequency (Fosc) is in the range of 12.5 MHz to 80 MHz, which generates device operating speeds of 6.25-40 MIPS.

For a primary oscillator or FRC oscillator, output 'FIN', the PLL output 'FOSC' is given by:

### EQUATION 9-2: Fosc CALCULATION

$FOSC = FIN \cdot \left(\frac{M}{N1 \cdot N2}\right)$

| U-0                 | U-0                                                                                    | U-0                                                                                     | U-0                                                                          | U-0                                     | U-0              | U-0             | U-0   |

|---------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------|------------------|-----------------|-------|

| —                   | _                                                                                      |                                                                                         | _                                                                            | —                                       | _                |                 | _     |

| bit 15              |                                                                                        |                                                                                         |                                                                              |                                         |                  |                 | bit   |

|                     |                                                                                        |                                                                                         |                                                                              |                                         |                  |                 |       |

| U-0                 | U-0                                                                                    | R/W-0                                                                                   | R/W-0                                                                        | R/W-0                                   | R/W-0            | R/W-0           | R/W-0 |

|                     |                                                                                        |                                                                                         |                                                                              | TUN<                                    | :5:0> <b>(1)</b> |                 |       |

| bit 7               |                                                                                        |                                                                                         |                                                                              |                                         |                  |                 | bit ( |

|                     |                                                                                        |                                                                                         |                                                                              |                                         |                  |                 |       |

| Legend:             |                                                                                        |                                                                                         |                                                                              |                                         |                  |                 |       |

| R = Readable        | e bit                                                                                  | W = Writable                                                                            | bit                                                                          | U = Unimplem                            | nented bit, read | d as '0'        |       |

| -n = Value at       | POR                                                                                    | '1' = Bit is set                                                                        |                                                                              | '0' = Bit is clea                       | ared             | x = Bit is unki | nown  |

|                     |                                                                                        |                                                                                         |                                                                              |                                         |                  |                 |       |

|                     |                                                                                        |                                                                                         |                                                                              |                                         |                  |                 |       |

| bit 15-6            | Unimplemen                                                                             | ted: Read as '                                                                          | 0'                                                                           |                                         |                  |                 |       |

| bit 15-6<br>bit 5-0 | •                                                                                      | <b>ted:</b> Read as '<br>RC Oscillator T                                                |                                                                              |                                         |                  |                 |       |

|                     | <b>TUN&lt;5:0&gt;:</b> F                                                               |                                                                                         | uning bits <sup>(1)</sup>                                                    | 345 MHz)                                |                  |                 |       |

|                     | <b>TUN&lt;5:0&gt;:</b> F                                                               | RC Oscillator T                                                                         | uning bits <sup>(1)</sup>                                                    | 345 MHz)                                |                  |                 |       |

|                     | <b>TUN&lt;5:0&gt;:</b> F                                                               | RC Oscillator T                                                                         | uning bits <sup>(1)</sup>                                                    | 345 MHz)                                |                  |                 |       |

|                     | TUN<5:0>: F<br>111111 = Ce<br>•<br>•                                                   | RC Oscillator T<br>nter frequency                                                       | <sup>-</sup> uning bits <sup>(1)</sup><br>– 0.375% (7.                       | ·                                       |                  |                 |       |

|                     | TUN<5:0>: F<br>111111 = Ce<br>100001 = Ce                                              | RC Oscillator T                                                                         | - 0.375% (7.<br>– 11.625% (6                                                 | .52 MHz)                                |                  |                 |       |

|                     | TUN<5:0>: F<br>111111 = Ce<br>•<br>•<br>100001 = Ce<br>100000 = Ce<br>011111 = Ce      | RC Oscillator T<br>nter frequency<br>nter frequency<br>nter frequency<br>nter frequency | - 0.375% (7.<br>- 0.375% (7.<br>- 11.625% (6<br>- 12% (6.49<br>+ 11.625% (8  | .52 MHz)<br>MHz)<br>.23 MHz)            |                  |                 |       |

|                     | TUN<5:0>: F<br>111111 = Ce<br>•<br>•<br>100001 = Ce<br>100000 = Ce<br>011111 = Ce      | RC Oscillator T<br>nter frequency<br>nter frequency<br>nter frequency                   | - 0.375% (7.<br>- 0.375% (7.<br>- 11.625% (6<br>- 12% (6.49<br>+ 11.625% (8  | .52 MHz)<br>MHz)<br>.23 MHz)            |                  |                 |       |

|                     | TUN<5:0>: F<br>111111 = Ce<br>•<br>•<br>100001 = Ce<br>100000 = Ce<br>011111 = Ce      | RC Oscillator T<br>nter frequency<br>nter frequency<br>nter frequency<br>nter frequency | - 0.375% (7.<br>- 0.375% (7.<br>- 11.625% (6<br>- 12% (6.49<br>+ 11.625% (8  | .52 MHz)<br>MHz)<br>.23 MHz)            |                  |                 |       |

|                     | TUN<5:0>: F<br>111111 = Ce<br>•<br>•<br>100001 = Ce<br>100000 = Ce<br>011111 = Ce      | RC Oscillator T<br>nter frequency<br>nter frequency<br>nter frequency<br>nter frequency | - 0.375% (7.<br>- 0.375% (7.<br>- 11.625% (6<br>- 12% (6.49<br>+ 11.625% (8  | .52 MHz)<br>MHz)<br>.23 MHz)            |                  |                 |       |

|                     | TUN<5:0>: F<br>111111 = Ce<br>100001 = Ce<br>100000 = Ce<br>011111 = Ce<br>011110 = Ce | RC Oscillator T<br>nter frequency<br>nter frequency<br>nter frequency<br>nter frequency | - 0.375% (7.<br>- 11.625% (6<br>- 12% (6.49<br>+ 11.625% (8<br>+ 11.25% (8.1 | .52 MHz)<br>MHz)<br>.23 MHz)<br>20 MHz) |                  |                 |       |

### REGISTER 9-4: OSCTUN: FRC OSCILLATOR TUNING REGISTER<sup>(2)</sup>

- **Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation and is neither characterized nor tested.

- 2: This register is reset only on a Power-on Reset (POR).

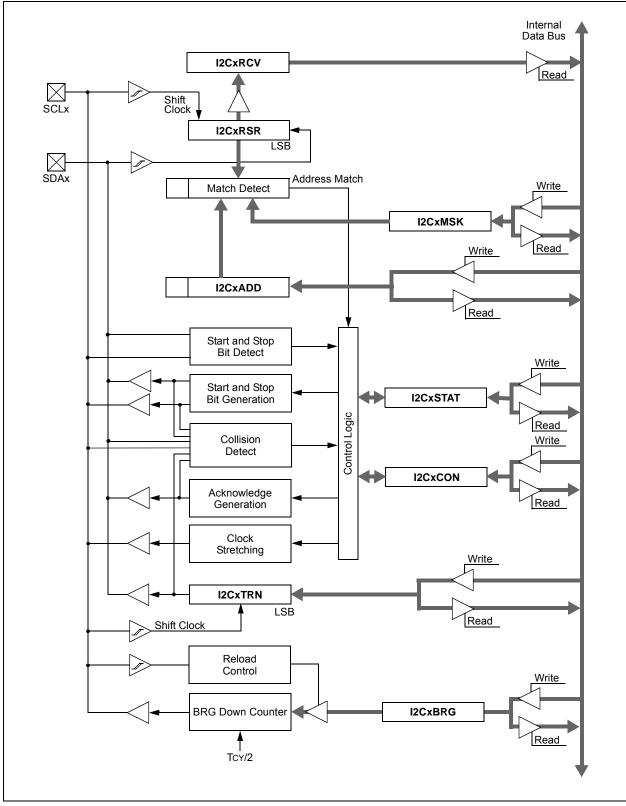

FIGURE 17-1:  $I^2 C^{TM}$  BLOCK DIAGRAM (x = 1 OR 2)

#### REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | ADDEN: Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                                |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode enabled. If 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode disabled</li> </ul>                                                                         |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                            |

|       | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                                                                           |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                                                                       |

|       | <ul><li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li><li>0 = Parity error has not been detected</li></ul>                                                        |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                                                                      |

|       | 1 = Framing error has been detected for the current character (character at the top of the receive FIFO)                                                                                                                        |

|       | 0 = Framing error has not been detected                                                                                                                                                                                         |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (read/clear only)                                                                                                                                                                 |

|       | <ul> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed. Clearing a previously set OERR bit (1 → 0 transition) will reset<br/>the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | URXDA: Receive Buffer Data Available bit (read-only)                                                                                                                                                                            |

|       | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                   |

|       |                                                                                                                                                                                                                                 |

**Note 1:** Refer to **Section 17. "UART**" (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for transmit operation.

| U-0             | U-0                                                                          | R/W-0                                    | R/W-0         | r-0                          | R/W-1            | R/W-0           | R/W-0 |  |  |

|-----------------|------------------------------------------------------------------------------|------------------------------------------|---------------|------------------------------|------------------|-----------------|-------|--|--|

| _               | _                                                                            | CSIDL                                    | ABAT          |                              |                  | REQOP<2:0>      |       |  |  |

| bit 15          |                                                                              |                                          |               |                              |                  |                 | bit   |  |  |

| R-1             | R-0                                                                          | R-0                                      | U-0           | R/W-0                        | U-0              | U-0             | R/W-0 |  |  |

|                 | PMODE<2:0                                                                    |                                          | 0-0           | CANCAP                       | 0-0              | 0-0             | WIN   |  |  |

| bit 7           |                                                                              | 12                                       |               | CANCAI                       |                  | _               | bit   |  |  |

|                 |                                                                              |                                          |               |                              |                  |                 |       |  |  |

| Legend:         |                                                                              | r = Bit is Res                           | erved         |                              |                  |                 |       |  |  |

| R = Readable b  | bit                                                                          | W = Writable                             | bit           | U = Unimplen                 | nented bit, read | l as '0'        |       |  |  |

| -n = Value at P | OR                                                                           | '1' = Bit is se                          | t             | '0' = Bit is clea            | ared             | x = Bit is unkr | nown  |  |  |

| bit 15-14       | Unimpleme                                                                    | nted: Read as                            | 0'            |                              |                  |                 |       |  |  |

| bit 13          | CSIDL: Sto                                                                   | p in Idle Mode b                         | bit           |                              |                  |                 |       |  |  |

|                 |                                                                              | •                                        |               | levice enters Idl            | e mode           |                 |       |  |  |

|                 |                                                                              | e module opera                           |               |                              |                  |                 |       |  |  |

| bit 12          |                                                                              | t All Pending Tr                         |               |                              |                  |                 |       |  |  |

|                 | •                                                                            | Il transmit buffe<br>will clear this bit |               | nsmission<br>smissions are a | borted           |                 |       |  |  |

| bit 11          | Reserved: [                                                                  |                                          |               |                              |                  |                 |       |  |  |

| bit 10-8        | REQOP<2:0>: Request Operation Mode bits                                      |                                          |               |                              |                  |                 |       |  |  |

|                 | 111 = Set Listen All Messages mode                                           |                                          |               |                              |                  |                 |       |  |  |

|                 | 110 = Rese                                                                   | rved – do not us                         | se            |                              |                  |                 |       |  |  |

|                 |                                                                              | rved – do not us                         | -             |                              |                  |                 |       |  |  |

|                 |                                                                              | onfiguration mo                          |               |                              |                  |                 |       |  |  |

|                 |                                                                              | oopback mode                             | 5             |                              |                  |                 |       |  |  |

|                 |                                                                              | isable mode                              |               |                              |                  |                 |       |  |  |

|                 | 000 <b>= Set N</b>                                                           | ormal Operation                          | n mode        |                              |                  |                 |       |  |  |

| bit 7-5         | OPMODE<2                                                                     | 2:0>: Operation                          | Mode bits     |                              |                  |                 |       |  |  |

|                 |                                                                              | le is in Listen A                        | ll Messages n | node                         |                  |                 |       |  |  |

|                 | 110 = Rese<br>101 = Rese                                                     |                                          |               |                              |                  |                 |       |  |  |

|                 |                                                                              |                                          | ation mode    |                              |                  |                 |       |  |  |

|                 | 100 = Module is in Configuration mode<br>011 = Module is in Listen Only mode |                                          |               |                              |                  |                 |       |  |  |

|                 | 010 = Modu                                                                   | le is in Loopbac                         | k mode        |                              |                  |                 |       |  |  |

|                 |                                                                              | le is in Disable<br>le is in Normal      |               | do.                          |                  |                 |       |  |  |

| bit 4           |                                                                              | nted: Read as                            | -             |                              |                  |                 |       |  |  |

| bit 3           | -                                                                            |                                          |               | Capture Event                | Enable bit       |                 |       |  |  |

|                 | 1 = Enable i                                                                 | -                                        |               | nessage receive              |                  |                 |       |  |  |

| bit 2-1         |                                                                              | nted: Read as                            | 0'            |                              |                  |                 |       |  |  |

| bit 0           | •                                                                            | Map Window Se                            |               |                              |                  |                 |       |  |  |

|                 | 1 = Use filte                                                                | -                                        |               |                              |                  |                 |       |  |  |

|                 |                                                                              |                                          |               |                              |                  |                 |       |  |  |

#### REGISTER 19-1: CiCTRL1: ECAN™ MODULE CONTROL REGISTER 1

#### REGISTER 19-24: CiRXOVF1: ECAN™ MODULE RECEIVE BUFFER OVERFLOW REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |