Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 20 MIPS                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 18x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp506a-h-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| PIC24H Product Families                                                     |                                                      | 2   |

|-----------------------------------------------------------------------------|------------------------------------------------------|-----|

|                                                                             |                                                      |     |

| 2.0 Guidelines for Getting Started with 16-Bit Mid                          | crocontrollers                                       | 19  |

|                                                                             |                                                      |     |

| 4.0 Memory Organization                                                     |                                                      | 29  |

| 5.0 Flash Program Memory                                                    |                                                      | 59  |

| 6.0 Reset                                                                   |                                                      | 65  |

| 7.0 Interrupt Controller                                                    |                                                      | 69  |

| 8.0 Direct Memory Access (DMA)                                              |                                                      | 113 |

| 9.0 Oscillator Configuration                                                |                                                      | 123 |

| 10.0 Power-Saving Features                                                  |                                                      | 133 |

| 11.0 I/O Ports                                                              |                                                      | 141 |

| 12.0 Timer1                                                                 |                                                      | 145 |

|                                                                             |                                                      |     |

|                                                                             |                                                      |     |

|                                                                             |                                                      |     |

| 16.0 Serial Peripheral Interface (SPI)                                      |                                                      | 159 |

| 17.0 Inter-Integrated Circuit <sup>™</sup> (I <sup>2</sup> C <sup>™</sup> ) |                                                      | 165 |

|                                                                             | er (UART)                                            |     |

| 19.0 Enhanced CAN (ECAN™) Module                                            |                                                      | 179 |

|                                                                             | С)                                                   |     |

| 21.0 Special Features                                                       |                                                      | 221 |

| 22.0 Instruction Set Summary                                                |                                                      | 229 |

| 23.0 Development Support                                                    |                                                      | 237 |

| 24.0 Electrical Characteristics                                             |                                                      | 241 |

| 25.0 High Temperature Electrical Characteristics .                          |                                                      | 287 |

| 26.0 DC and AC Device Characteristics Graphs                                |                                                      | 297 |

|                                                                             |                                                      |     |

| Appendix A: Migrating from PIC24HJXXXGPX06/X                                | 08/X10 Devices to PIC24HJXXXGPX06A/X08A/X10A Devices | 311 |

| Appendix B: Revision History                                                |                                                      | 312 |

| Index                                                                       |                                                      | 317 |

| The Microchip Web Site                                                      |                                                      | 321 |

| Customer Change Notification Service                                        |                                                      | 321 |

| Customer Support                                                            |                                                      | 321 |

| Reader Response                                                             |                                                      | 322 |

| Product Identification System                                               |                                                      | 323 |

#### 3.0 CPU

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 2. "CPU" (DS70204) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The PIC24HJXXXGPX06A/X08A/X10A CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set and addressing modes. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space. The actual amount of program memory implemented varies by device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double word move (MOV.D) instruction and the table instructions. Overhead-free, single-cycle program loop constructs are supported using the REPEAT instruction, which is interruptible at any point.

The PIC24HJXXXGPX06A/X08A/X10A devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can serve as a data, address or address offset register. The 16th working register (W15) operates as a software Stack Pointer (SP) for interrupts and calls.

The PIC24HJXXXGPX06A/X08A/X10A instruction set includes many addressing modes and is designed for optimum C compiler efficiency. For most instructions, the PIC24HJXXXGPX06A/X08A/X10A is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing A + B = C operations to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1, and the programmer's model for the PIC24HJXXXGPX06A/X08A/X10A is shown in Figure 3-2.

#### 3.1 Data Addressing Overview

The data space can be linearly addressed as 32K words or 64 Kbytes using an Address Generation Unit (AGU). The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program to data space mapping feature lets any instruction access program space as if it were data space.

The data space also includes 2 Kbytes of DMA RAM, which is primarily used for DMA data transfers, but may be used as general purpose RAM.

#### 3.2 Special MCU Features

The PIC24HJXXXGPX06A/X08A/X10A features a 17-bit by 17-bit, single-cycle multiplier. The multiplier can perform signed, unsigned and mixed-sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication makes mixed-sign multiplication possible.

The PIC24HJXXXGPX06A/X08A/X10A supports 16/16 and 32/16 integer divide operations. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A multi-bit data shifter is used to perform up to a 16-bit, left or right shift in a single cycle.

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

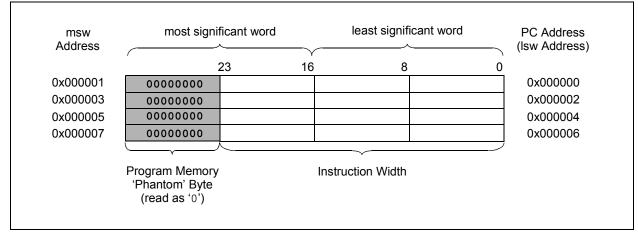

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement also provides compatibility with data memory space addressing and makes it possible to access data in the program memory space.

#### 4.1.2 INTERRUPT AND TRAP VECTORS

All PIC24HJXXXGPX06A/X08A/X10A devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user at 0x000000, with the actual address for the start of code at 0x000002.

PIC24HJXXXGPX06A/X08A/X10A devices also have two interrupt vector tables, located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the many device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the interrupt vector tables is provided in **Section 7.1 "Interrupt Vector Table"**.

#### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

| File Name  | Addr | Bit 15 | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10             | Bit 9    | Bit 8    | Bit 7                         | Bit 6    | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|------------|------|--------|-----------|--------|--------|--------|--------------------|----------|----------|-------------------------------|----------|--------|--------|--------|--------|--------|--------|---------------|

| C1RXF1EID  | 0446 |        | 1         | 1      | EID<   | :15:8> |                    |          |          |                               |          |        | EID<   | 7:0>   |        |        |        | xxxx          |

| C1RXF2SID  | 0448 |        |           |        | SID<   | :10:3> |                    |          |          | SID<2:0> — EXIDE — EID<17:16> |          |        |        |        | 17:16> | xxxx   |        |               |

| C1RXF2EID  | 044A |        | EID<15:8> |        |        |        |                    |          |          |                               | EID<     | 7:0>   |        |        |        | xxxx   |        |               |

| C1RXF3SID  | 044C |        |           |        | SID<   | :10:3> |                    |          |          |                               | SID<2:0> |        | _      | EXIDE  | _      | EID<   | 17:16> | xxxx          |

| C1RXF3EID  | 044E |        | EID<15:8> |        |        |        |                    |          |          |                               | EID<     | 7:0>   |        |        |        | xxxx   |        |               |

| C1RXF4SID  | 0450 |        | SID<10:3> |        |        |        |                    |          | SID<2:0> |                               | _        | EXIDE  | _      | EID<   | 17:16> | xxxx   |        |               |

| C1RXF4EID  | 0452 |        | EID<15:8> |        |        |        |                    |          |          | EID<                          | 7:0>     |        |        |        | xxxx   |        |        |               |

| C1RXF5SID  | 0454 |        | SID<10:3> |        |        |        |                    |          | SID<2:0> |                               | _        | EXIDE  | -      | EID<'  | 17:16> | xxxx   |        |               |

| C1RXF5EID  | 0456 |        | EID<15:8> |        |        |        |                    |          |          | EID<                          | 7:0>     |        |        |        | xxxx   |        |        |               |

| C1RXF6SID  | 0458 |        | SID<10:3> |        |        |        |                    | SID<2:0> |          | _                             | EXIDE    | _      | EID<'  | 17:16> | xxxx   |        |        |               |

| C1RXF6EID  | 045A |        | EID<15:8> |        |        |        | EID<7:0>           |          |          |                               |          |        | xxxx   |        |        |        |        |               |

| C1RXF7SID  | 045C |        | SID<10:3> |        |        |        |                    | SID<2:0> |          | —                             | EXIDE    | —      | EID<'  | 17:16> | xxxx   |        |        |               |

| C1RXF7EID  | 045E |        | EID<15:8> |        |        |        |                    |          |          | EID<                          | 7:0>     |        |        |        | xxxx   |        |        |               |

| C1RXF8SID  | 0460 |        | SID<10:3> |        |        |        |                    | SID<2:0> |          | —                             | EXIDE    | _      | EID<'  | 17:16> | xxxx   |        |        |               |

| C1RXF8EID  | 0462 |        |           |        | EID<   | :15:8> |                    |          |          | EID<7:0>                      |          |        |        |        | xxxx   |        |        |               |

| C1RXF9SID  | 0464 |        |           |        | SID<   | :10:3> |                    |          |          | SID<2:0> — EXIDE —            |          |        |        |        | EID<   | 17:16> | xxxx   |               |

| C1RXF9EID  | 0466 |        |           |        | EID<   | :15:8> |                    |          |          | EID<7:0>                      |          |        |        |        |        | xxxx   |        |               |

| C1RXF10SID | 0468 |        |           |        | SID<   | :10:3> |                    |          |          | SID<2:0> — EXIDE — EIE        |          |        |        |        | EID<   | 17:16> | xxxx   |               |

| C1RXF10EID | 046A |        |           |        | EID<   | :15:8> |                    |          |          | EID<7:0>                      |          |        |        |        |        |        | xxxx   |               |

| C1RXF11SID | 046C |        |           |        | SID<   | :10:3> |                    |          |          |                               | SID<2:0> |        | —      | EXIDE  | —      | EID<'  | 17:16> | xxxx          |

| C1RXF11EID | 046E |        |           |        | EID<   | :15:8> |                    |          |          |                               |          |        | EID<   | 7:0>   |        |        |        | xxxx          |

| C1RXF12SID | 0470 |        |           |        | SID<   | :10:3> |                    |          |          |                               | SID<2:0> |        | —      | EXIDE  | —      | EID<   | 17:16> | xxxx          |

| C1RXF12EID | 0472 |        |           |        | EID<   | :15:8> |                    |          |          |                               |          |        | EID<   | 7:0>   |        |        |        | xxxx          |

| C1RXF13SID | 0474 |        | SID<10:3> |        |        |        | SID<2:0> — EXIDE — |          |          |                               | EID<     | 17:16> | xxxx   |        |        |        |        |               |

| C1RXF13EID | 0476 |        | EID<15:8> |        |        |        | EID<7:0>           |          |          |                               |          |        | xxxx   |        |        |        |        |               |

| C1RXF14SID | 0478 |        |           |        | SID<   | :10:3> |                    |          |          | SID<2:0> — EXIDE — EID<17:1   |          |        | 17:16> | xxxx   |        |        |        |               |

| C1RXF14EID | 047A |        |           |        | EID<   | :15:8> |                    |          |          |                               |          |        | EID<   | 7:0>   |        |        |        | xxxx          |

| C1RXF15SID | 047C |        |           |        | SID<   | :10:3> |                    |          |          |                               | SID<2:0> |        | —      | EXIDE  | —      | EID<'  | 17:16> | xxxx          |

| C1RXF15EID | 047E |        |           |        | EID<   | :15:8> |                    |          |          |                               |          |        | EID<   | 7:0>   |        |        |        | xxxx          |

#### ONILY (CONTINUED) DICOALLINNY ODEACA/E40A/C40A DEVICES

Legend:

© 2009-2012 Microchip Technology Inc.

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

#### 4.2.6 SOFTWARE STACK

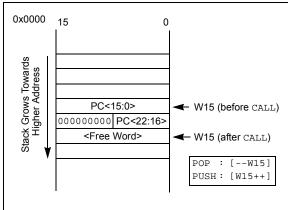

In addition to its use as a working register, the W15 register in the PIC24HJXXXGPX06A/X08A/X10A devices is also used as a software Stack Pointer. The Stack Pointer always points to the first available free word and grows from lower to higher addresses. It predecrements for stack pops and post-increments for stack pushes, as shown in Figure 4-5. For a PC push during any CALL instruction, the MSB of the PC is zeroextended before the push, ensuring that the MSB is always clear.

| Note: | A PC push during exception processing    |

|-------|------------------------------------------|

|       | concatenates the SRL register to the MSB |

|       | of the PC prior to the push.             |

The Stack Pointer Limit register (SPLIM) associated with the Stack Pointer sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' because all stack operations must be word-aligned. Whenever an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation. Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800. This prevents the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

FIGURE 4-5: CALL STACK FRAME

#### 4.2.7 DATA RAM PROTECTION FEATURE

The PIC24H product family supports Data RAM protection features that enable segments of RAM to be protected when used in conjunction with Boot and Secure Code Segment Security. BSRAM (Secure RAM segment for BS) is accessible only from the Boot Segment Flash code, when enabled. SSRAM (Secure RAM segment for RAM) is accessible only from the Secure Segment Flash code, when enabled. See Table 4-1 for an overview of the BSRAM and SSRAM SFRs.

#### 4.3 Instruction Addressing Modes

The addressing modes in Table 4-34 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions are somewhat different from those in the other instruction types.

#### 4.3.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire data space.

#### 4.3.2 MCU INSTRUCTIONS

The 3-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2 where:

Operand 1 is always a working register (i.e., the addressing mode can only be Register Direct) which is referred to as Wb.

Operand 2 can be a W register, fetched from data memory, or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-bit or 10-bit Literal

| Reset Type      | Clock Source  | SYSRST Delay           | System Clock<br>Delay | FSCM<br>Delay | See Notes        |

|-----------------|---------------|------------------------|-----------------------|---------------|------------------|

| POR             | EC, FRC, LPRC | TPOR + TSTARTUP + TRST | —                     | _             | 1, 2, 3          |

|                 | ECPLL, FRCPLL | TPOR + TSTARTUP + TRST | TLOCK                 | TFSCM         | 1, 2, 3, 5, 6    |

|                 | XT, HS, SOSC  | TPOR + TSTARTUP + TRST | Тоѕт                  | TFSCM         | 1, 2, 3, 4, 6    |

|                 | XTPLL, HSPLL  | TPOR + TSTARTUP + TRST | TOST + TLOCK          | TFSCM         | 1, 2, 3, 4, 5, 6 |

| MCLR            | Any Clock     | Trst                   | —                     | _             | 3                |

| WDT             | Any Clock     | Trst                   | —                     | _             | 3                |

| Software        | Any clock     | Trst                   | —                     | _             | 3                |

| Illegal Opcode  | Any Clock     | Trst                   | —                     | _             | 3                |

| Uninitialized W | Any Clock     | Trst                   | —                     | _             | 3                |

| Trap Conflict   | Any Clock     | Trst                   | —                     | —             | 3                |

#### TABLE 6-3: RESET DELAY TIMES FOR VARIOUS DEVICE RESETS

**Note 1:** TPOR = Power-on Reset delay (10 μs nominal).

**2:** TSTARTUP = Conditional POR delay of 20 μs nominal (if on-chip regulator is enabled) or 64 ms nominal Power-up Timer delay (if regulator is disabled). TSTARTUP is also applied to all returns from powered-down states, including waking from Sleep mode, only if the regulator is enabled.

- 3: TRST = Internal state Reset time (20 μs nominal).

- **4:** TOST = Oscillator Start-up Timer. A 10-bit counter counts 1024 oscillator periods before releasing the oscillator clock to the system.

- **5:** TLOCK = PLL lock time (20  $\mu$ s nominal).

- **6:** TFSCM = Fail-Safe Clock Monitor delay (100 μs nominal).

#### 6.2.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) have a relatively long start-up time. Therefore, one or more of the following conditions is possible after the Reset signal is released:

- The oscillator circuit has not begun to oscillate

- The Oscillator Start-up Timer has not expired (if a crystal oscillator is used)

- The PLL has not achieved a lock (if PLL is used)

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

#### 6.2.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it begins to monitor the system clock source when the Reset signal is released. If a valid clock source is not available at this time, the device automatically switches to the FRC oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine.

#### 6.2.2.1 FSCM Delay for Crystal and PLL Clock Sources

When the system clock source is provided by a crystal oscillator and/or the PLL, a small delay, TFSCM, is automatically inserted after the POR and PWRT delay times. The FSCM does not begin to monitor the system clock source until this delay expires. The FSCM delay time is nominally 500  $\mu$ s and provides additional time for the oscillator and/or PLL to stabilize. In most cases, the FSCM delay prevents an oscillator failure trap at a device Reset when the PWRT is disabled.

#### 6.3 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset, with the exception of two registers. The Reset value for the Reset Control register, RCON, depends on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, depends on the type of Reset and the programmed values of the oscillator Configuration bits in the FOSC Configuration register.

#### REGISTER 7-12: IEC2: INTERRUPT ENABLE CONTROL REGISTER 2

| R/W-0         | R/W-0           | U-0                               | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |

|---------------|-----------------|-----------------------------------|----------------|------------------|------------------|-----------------|---------|--|--|--|--|

| T6IE          | DMA4IE          | —                                 | OC8IE          | OC7IE            | OC6IE            | OC5IE           | IC6IE   |  |  |  |  |

| bit 15        |                 |                                   |                |                  | •                |                 | bit 8   |  |  |  |  |

| R/W-0         | R/W-0           | R/W-0                             | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |

| IC5IE         | IC4IE           | IC3IE                             | DMA3IE         | C1IE             | C1RXIE           | SPI2IE          | SPI2EIE |  |  |  |  |

| bit 7         |                 |                                   |                | 0                |                  |                 | bit (   |  |  |  |  |

| Legend:       |                 |                                   |                |                  |                  |                 |         |  |  |  |  |

| R = Readable  | e bit           | W = Writable                      | bit            | U = Unimpler     | mented bit, read | l as '0'        |         |  |  |  |  |

| -n = Value at | POR             | '1' = Bit is set                  |                | '0' = Bit is cle | eared            | x = Bit is unki | nown    |  |  |  |  |

| bit 15        | T6IE: Timer6    | Interrupt Enabl                   | e bit          |                  |                  |                 |         |  |  |  |  |

|               |                 | request enable                    |                |                  |                  |                 |         |  |  |  |  |

|               | 0 = Interrupt r | equest not ena                    | bled           |                  |                  |                 |         |  |  |  |  |

| bit 14        |                 | A Channel 4 D                     |                | Complete Interi  | rupt Enable bit  |                 |         |  |  |  |  |

|               |                 | equest enable<br>equest not ena   |                |                  |                  |                 |         |  |  |  |  |

| bit 13        | •               | ted: Read as '                    |                |                  |                  |                 |         |  |  |  |  |

| bit 12        | •               | ut Compare Ch                     |                | unt Enable bit   |                  |                 |         |  |  |  |  |

| 511 12        | •               | request enable                    |                |                  |                  |                 |         |  |  |  |  |

|               |                 | 0 = Interrupt request not enabled |                |                  |                  |                 |         |  |  |  |  |

| bit 11        | OC7IE: Outpu    | ut Compare Ch                     | annel 7 Interr | upt Enable bit   |                  |                 |         |  |  |  |  |

|               |                 | equest enable<br>equest not ena   |                |                  |                  |                 |         |  |  |  |  |

| bit 10        | OC6IE: Outpu    | ut Compare Ch                     | annel 6 Interr | upt Enable bit   |                  |                 |         |  |  |  |  |

|               |                 | equest enable<br>equest not ena   |                |                  |                  |                 |         |  |  |  |  |

| bit 9         | OC5IE: Outpu    | ut Compare Ch                     | annel 5 Interr | upt Enable bit   |                  |                 |         |  |  |  |  |

|               |                 | equest enable<br>equest not ena   |                |                  |                  |                 |         |  |  |  |  |

| bit 8         |                 | Capture Channe                    |                | Enable bit       |                  |                 |         |  |  |  |  |

|               |                 | equest enable<br>equest not ena   |                |                  |                  |                 |         |  |  |  |  |

| bit 7         |                 | Capture Channe                    |                | Enable bit       |                  |                 |         |  |  |  |  |

|               | -               | equest enable                     |                |                  |                  |                 |         |  |  |  |  |

|               | •               | request not ena                   |                |                  |                  |                 |         |  |  |  |  |

| bit 6         | -               | Capture Channe                    |                | Enable bit       |                  |                 |         |  |  |  |  |

|               |                 | equest enable<br>equest not ena   |                |                  |                  |                 |         |  |  |  |  |

| bit 5         | •               | Capture Channe                    |                | -nable bit       |                  |                 |         |  |  |  |  |

|               | -               | equest enable                     | -              |                  |                  |                 |         |  |  |  |  |

|               | 0 = Interrupt r | equest not ena                    | bled           |                  |                  |                 |         |  |  |  |  |

| bit 4         | DMA3IE: DM      | A Channel 3 D                     | ata Transfer C | Complete Interi  | rupt Enable bit  |                 |         |  |  |  |  |

|               |                 | equest enable<br>equest not ena   |                |                  |                  |                 |         |  |  |  |  |

| bit 3         | -               | Event Interrup                    |                |                  |                  |                 |         |  |  |  |  |

| bit J         |                 | equest enable                     |                |                  |                  |                 |         |  |  |  |  |

|               |                 | equest not ena                    |                |                  |                  |                 |         |  |  |  |  |

| U-0                                                                      | U-0                                                                        | U-0                                                                                                                    | U-0                           | U-0           | R/W-1           | R/W-0       | R/W-0 |  |  |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------|-----------------|-------------|-------|--|--|

| _                                                                        | _                                                                          | _                                                                                                                      | _                             | —             |                 | DMA1IP<2:0> |       |  |  |

| bit 15                                                                   | ·                                                                          | ·                                                                                                                      |                               |               |                 |             | bit   |  |  |

| U-0                                                                      | R/W-1                                                                      | R/W-0                                                                                                                  | R/W-0                         | U-0           | R/W-1           | R/W-0       | R/W-0 |  |  |

| —                                                                        |                                                                            | AD1IP<2:0>                                                                                                             |                               |               |                 | U1TXIP<2:0> |       |  |  |

| bit 7                                                                    |                                                                            |                                                                                                                        |                               |               | •               |             | bit   |  |  |

| Legend:                                                                  |                                                                            |                                                                                                                        |                               |               |                 |             |       |  |  |

| R = Readab                                                               | ole bit                                                                    | W = Writable                                                                                                           | bit                           | U = Unimplei  | mented bit, rea | ad as '0'   |       |  |  |

| -n = Value at POR (1' = Bit is set 0' = Bit is cleared x = Bit is unknow |                                                                            |                                                                                                                        |                               |               |                 |             |       |  |  |

| bit 10-8<br>bit 7<br>bit 6-4                                             | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen | >: DMA Channe<br>pt is priority 7 (I<br>pt is priority 1<br>pt source is dis<br><b>ted:</b> Read as '(<br>ADC1 Convers | nighest priori<br>abled<br>)' | ty interrupt) |                 |             |       |  |  |

|                                                                          | •<br>•<br>001 = Interru                                                    | pt is priority 7 (I<br>pt is priority 1<br>pt source is dis                                                            |                               | ty interrupt) |                 |             |       |  |  |

| bit 3                                                                    | Unimplemen                                                                 | ted: Read as 'd                                                                                                        | )'                            |               |                 |             |       |  |  |

| bit 2-0                                                                  |                                                                            | •: UART1 Trans<br>pt is priority 7 (I                                                                                  |                               |               |                 |             |       |  |  |

|                                                                          | 001 = Interru<br>000 = Interru                                             | ot is priority 1<br>pt source is dis                                                                                   | abled                         |               |                 |             |       |  |  |

#### REGISTER 7-18: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

#### REGISTER 8-2: DMAxREQ: DMA CHANNEL x IRQ SELECT REGISTER

| R/W-0                | U-0   |

|----------------------|-----|-----|-----|-----|-----|-----|-------|

| FORCE <sup>(1)</sup> | —   | —   | —   | —   | —   | —   | —     |

| bit 15               |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0                  | R/W-0                  | R/W-0      | R/W-0      | R/W-0                  | R/W-0      | R/W-0      |

|-------|------------------------|------------------------|------------|------------|------------------------|------------|------------|

| —     | IRQSEL6 <sup>(2)</sup> | IRQSEL5 <sup>(2)</sup> | IRQSEL4(2) | IRQSEL3(2) | IRQSEL2 <sup>(2)</sup> | IRQSEL1(2) | IRQSEL0(2) |

| bit 7 |                        |                        |            |            |                        |            | bit 0      |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15 **FORCE:** Force DMA Transfer bit<sup>(1)</sup>

1 = Force a single DMA transfer (Manual mode)

0 = Automatic DMA transfer initiation by DMA request

bit 14-7 Unimplemented: Read as '0'

- bit 6-0 IRQSEL<6:0>: DMA Peripheral IRQ Number Select bits<sup>(2)</sup> 0000000-1111111 = DMAIRQ0-DMAIRQ127 selected to be Channel DMAREQ

- **Note 1:** The FORCE bit cannot be cleared by the user. The FORCE bit is cleared by hardware when the forced DMA transfer is complete.

2: Please see Table 8-1 for a complete listing of IRQ numbers for all interrupt sources.

| R/W-0                 | R/W-0          | R/W-0                                                                 | R/W-0                 | U-0               | U-0           | U-0            | U-0                  |  |  |

|-----------------------|----------------|-----------------------------------------------------------------------|-----------------------|-------------------|---------------|----------------|----------------------|--|--|

| T9MD                  | T8MD           | T7MD                                                                  | T6MD                  |                   | _             | _              | _                    |  |  |

| bit 15                | - I            |                                                                       | 1                     |                   |               |                | bit 8                |  |  |

|                       |                |                                                                       |                       |                   |               |                |                      |  |  |

| U-0                   | U-0            | U-0                                                                   | U-0                   | U-0               | U-0           | R/W-0          | R/W-0                |  |  |

| _                     |                | —                                                                     | —                     | —                 | —             | I2C2MD         | AD2MD <sup>(1)</sup> |  |  |

| bit 7                 |                |                                                                       |                       |                   |               |                | bit (                |  |  |

| Logondi               |                |                                                                       |                       |                   |               |                |                      |  |  |

| Legend:<br>R = Readal | ble bit        | W = Writable                                                          | hit                   | U = Unimplem      | ented bit rea | ad as '0'      |                      |  |  |

| -n = Value a          |                | '1' = Bit is set                                                      |                       | '0' = Bit is clea |               | x = Bit is unk | nown                 |  |  |

|                       |                |                                                                       |                       |                   |               |                | -                    |  |  |

| bit 15                | T9MD: Timer    | 9 Module Disab                                                        | ole bit               |                   |               |                |                      |  |  |

|                       | 1 = Timer9 m   | odule is disable                                                      | ed                    |                   |               |                |                      |  |  |

|                       | 0 = Timer9 m   | odule is enable                                                       | d                     |                   |               |                |                      |  |  |

| bit 14                | T8MD: Timer    | 8 Module Disab                                                        | ole bit               |                   |               |                |                      |  |  |

|                       |                | odule is disable                                                      |                       |                   |               |                |                      |  |  |

|                       |                | odule is enable                                                       |                       |                   |               |                |                      |  |  |

| bit 13                | T7MD: Timer    | 7 Module Disab                                                        | ole bit               |                   |               |                |                      |  |  |

|                       | -              | odule is disable                                                      |                       |                   |               |                |                      |  |  |

|                       |                | odule is enable                                                       | -                     |                   |               |                |                      |  |  |

| bit 12                |                | 6 Module Disat                                                        |                       |                   |               |                |                      |  |  |

|                       |                | odule is disable<br>odule is enable                                   |                       |                   |               |                |                      |  |  |

| bit 11-2              |                | ted: Read as '                                                        |                       |                   |               |                |                      |  |  |

| bit 1                 | •              |                                                                       |                       |                   |               |                |                      |  |  |

|                       |                | <b>I2C2MD:</b> I2C2 Module Disable bit<br>1 = I2C2 module is disabled |                       |                   |               |                |                      |  |  |

|                       |                | lule is enabled                                                       |                       |                   |               |                |                      |  |  |

| bit 0                 |                | 2 Module Disab                                                        | le bit <sup>(1)</sup> |                   |               |                |                      |  |  |

|                       |                | ule is disabled                                                       |                       |                   |               |                |                      |  |  |

|                       | $0 = AD2 \mod$ |                                                                       |                       |                   |               |                |                      |  |  |

**Note 1:** The PCFGx bits will have no effect if the ADC module is disabled by setting this bit. In this case, all port pins multiplexed with ANx will be in Digital mode.

#### REGISTER 13-2: TyCON (T3CON, T5CON, T7CON OR T9CON) CONTROL REGISTER

| R/W-0              | U-0 | R/W-0                | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------------------|-----|----------------------|-----|-----|-----|-----|-------|

| TON <sup>(1)</sup> | —   | TSIDL <sup>(2)</sup> | _   | —   | —   | —   | —     |

| bit 15             |     |                      |     |     |     |     | bit 8 |

|                    |     |                      |     |     |     |     |       |

| U-0   | R/W-0                | R/W-0 | R/W-0    | U-0 | U-0 | R/W-0                | U-0   |

|-------|----------------------|-------|----------|-----|-----|----------------------|-------|

| _     | TGATE <sup>(1)</sup> | TCKPS | <1:0>(1) | —   | —   | TCS <sup>(1,3)</sup> | —     |

| bit 7 |                      |       |          |     |     |                      | bit 0 |

| Legend:    |                                                          |                                                             |                                   |                                     |

|------------|----------------------------------------------------------|-------------------------------------------------------------|-----------------------------------|-------------------------------------|

| R = Read   | able bit                                                 | W = Writable bit                                            | U = Unimplemented bit,            | read as '0'                         |

| -n = Value | at POR                                                   | '1' = Bit is set                                            | '0' = Bit is cleared              | x = Bit is unknown                  |

| bit 15     | 1 = Starts                                               | nery On bit <sup>(1)</sup><br>s 16-bit Timery               |                                   |                                     |

|            | •                                                        | s 16-bit Timery                                             |                                   |                                     |

| bit 14     | •                                                        | mented: Read as '0'                                         |                                   |                                     |

| bit 13     |                                                          | top in Idle Mode bit <sup>(2)</sup>                         |                                   |                                     |

|            |                                                          | ontinue module operation wh<br>nue module operation in Idle |                                   |                                     |

| bit 12-7   | Unimple                                                  | mented: Read as '0'                                         |                                   |                                     |

| bit 6      | TGATE:                                                   | Timery Gated Time Accumul                                   | ation Enable bit <sup>(1)</sup>   |                                     |

|            |                                                          | s ignored.                                                  |                                   |                                     |

| bit 5-4    | TCKPS<<br>11 = 1:25<br>10 = 1:64<br>01 = 1:8<br>00 = 1:1 |                                                             | escale Select bits <sup>(1)</sup> |                                     |

| bit 3-2    | Unimple                                                  | mented: Read as '0'                                         |                                   |                                     |

| bit 1      | TCS: Tim                                                 | nery Clock Source Select bit <sup>(</sup>                   | 1,3)                              |                                     |

|            |                                                          | nal clock from pin TyCK (on nal clock (Fcy)                 | the rising edge)                  |                                     |

| bit 0      | Unimple                                                  | mented: Read as '0'                                         |                                   |                                     |

| Note 1:    |                                                          | peration is enabled (T2CON-<br>set through T2CON.           | <3> = 1), these bits have no ef   | ffect on Timery operation; all time |

- 2: When 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

- 3: The TyCK pin is not available on all timers. Refer to the "Pin Diagrams" section for the available pins.

### 15.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual", Section 13. "Output Compare" (DS70209), which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The output compare module can select either Timer2 or Timer3 for its time base. The module compares the value of the timer with the value of one or two Compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the Compare register value. The output compare module generates either a single output pulse, or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events.

The output compare module has multiple operating modes:

- Active-Low One-Shot mode

- Active-High One-Shot mode

- Toggle mode

- · Delayed One-Shot mode

- Continuous Pulse mode

- PWM mode without Fault Protection

- PWM mode with Fault Protection

#### FIGURE 15-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

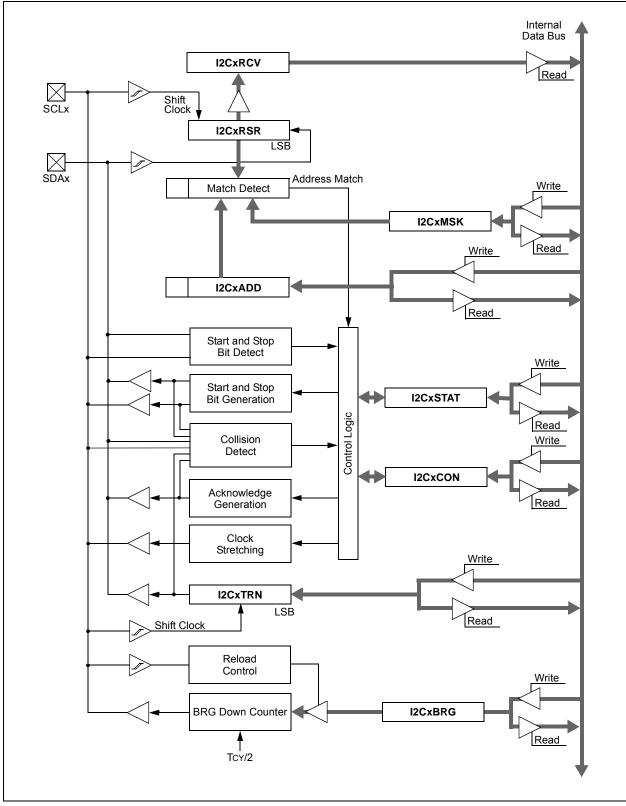

FIGURE 17-1:  $I^2 C^{TM}$  BLOCK DIAGRAM (x = 1 OR 2)

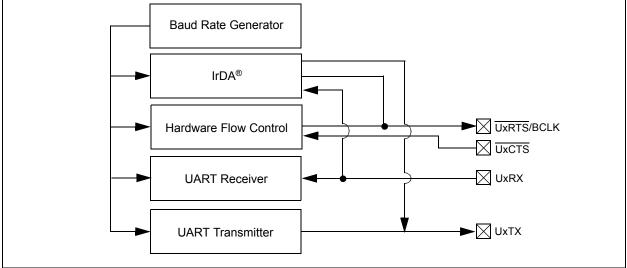

#### 18.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "UART" (DS70188) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the PIC24HJXXXGPX06A/X08A/X10A device family. The UART is a full-duplex asynchronous system that can communicate with peripheral devices, such as personal computers, LIN, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8 or 9-bit Data Transmission through the UxTX and UxRX pins

- Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS pins

- Fully Integrated Baud Rate Generator with 16-bit Prescaler

- Baud rates ranging from 10 Mbps to 38 bps at 40 MIPS

- 4-deep First-In-First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- Transmit and Receive Interrupts

- A Separate Interrupt for all UART Error Conditions

- · Loopback mode for Diagnostic Support

- Support for Sync and Break Characters

- Supports Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA<sup>®</sup> Support

A simplified block diagram of the UART is shown in Figure 18-1. The UART module consists of the key important hardware elements:

- Baud Rate Generator

- Asynchronous Transmitter

- · Asynchronous Receiver

- **Note 1:** Both UART1 and UART2 can trigger a DMA data transfer. If U1TX, U1RX, U2TX or U2RX is selected as a DMA IRQ source, a DMA transfer occurs when the U1TXIF, U1RXIF, U2TXIF or U2RXIF bit gets set as a result of a UART1 or UART2 transmission or reception.

- 2: If DMA transfers are required, the UART TX/RX FIFO buffer must be set to a size of 1 byte/word (i.e., UTXISEL<1:0> = 00 and URXISEL<1:0> = 00).

#### **REGISTER 18-1: UXMODE: UARTX MODE REGISTER (CONTINUED)**

| bit 4   | <b>URXINV:</b> Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                          |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                    |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul> |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                         |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                      |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                      |

|         | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                              |

- **Note 1:** Refer to **Section 17. "UART**" (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for receive or transmit operation.

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

| U-0            | U-0                                                                                                                                                    | U-0                                                                                                           | U-0                               | U-0              | U-0              | U-0                | U-0   |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------|------------------|--------------------|-------|--|

| _              | —                                                                                                                                                      | —                                                                                                             |                                   | —                |                  | —                  | —     |  |

| bit 15         |                                                                                                                                                        |                                                                                                               |                                   |                  |                  |                    | bit   |  |

| R/W-0          | R/W-0                                                                                                                                                  | R/W-0                                                                                                         | U-0                               | R/W-0            | R/W-0            | R/W-0              | R/W-0 |  |

| IVRIE          | WAKIE                                                                                                                                                  | ERRIE                                                                                                         |                                   | FIFOIE           | RBOVIE           | RBIE               | TBIE  |  |

| bit 7          |                                                                                                                                                        | I                                                                                                             |                                   |                  |                  |                    | bit   |  |

| Legend:        |                                                                                                                                                        |                                                                                                               |                                   |                  |                  |                    |       |  |

| R = Readab     | le bit                                                                                                                                                 | W = Writable                                                                                                  | bit                               | U = Unimplen     | nented bit, read | as '0'             |       |  |

| -n = Value a   | t POR                                                                                                                                                  | '1' = Bit is set                                                                                              |                                   | '0' = Bit is cle | ared             | x = Bit is unknown |       |  |

| bit 7<br>bit 6 | 1 = Interrupt r<br>0 = Interrupt r<br><b>WAKIE:</b> Bus<br>1 = Interrupt r                                                                             | I Message Inter<br>request enabled<br>request not ena<br>Wake-up Activi<br>request enabled<br>request not ena | d<br>Ibled<br>ty Interrupt E<br>d |                  |                  |                    |       |  |

| bit 5          | ERRIE: Error Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled                                                |                                                                                                               |                                   |                  |                  |                    |       |  |

| bit 4          | Unimplemen                                                                                                                                             | ted: Read as 'o                                                                                               | )'                                |                  |                  |                    |       |  |

| bit 3          | 1 = Interrupt i                                                                                                                                        | Almost Full Inf<br>request enabled<br>request not ena                                                         | d                                 | e bit            |                  |                    |       |  |

| bit 2          | <b>RBOVIE:</b> RX Buffer Overflow Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled                           |                                                                                                               |                                   |                  |                  |                    |       |  |

| bit 1          | <ul> <li><b>RBIE:</b> RX Buffer Interrupt Enable bit</li> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul>      |                                                                                                               |                                   |                  |                  |                    |       |  |

| bit 0          | 0 = Interrupt request not enabled<br><b>TBIE:</b> TX Buffer Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled |                                                                                                               |                                   |                  |                  |                    |       |  |

#### **REGISTER 19-7:** CIINTE: ECAN™ MODULE INTERRUPT ENABLE REGISTER

| DC CHARACTERISTICS                       |                    |    | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |       |        |            |         |  |

|------------------------------------------|--------------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|------------|---------|--|

| Parameter No. Typical <sup>(2)</sup> Max |                    |    | Doze<br>Ratio                                                                                                                                                                                                                                                                     | Units |        | Conditions |         |  |

| Doze Current (IDO                        | ze) <sup>(1)</sup> | •  |                                                                                                                                                                                                                                                                                   |       | •      |            |         |  |

| DC73a                                    | 11                 | 35 | 1:2                                                                                                                                                                                                                                                                               | mA    |        |            | 40 MIPS |  |

| DC73f                                    | 11                 | 30 | 1:64                                                                                                                                                                                                                                                                              | mA    | -40°C  | 3.3V       |         |  |

| DC73g                                    | 11                 | 30 | 1:128                                                                                                                                                                                                                                                                             | mA    |        |            |         |  |

| DC70a                                    | 42                 | 50 | 1:2                                                                                                                                                                                                                                                                               | mA    |        | 3.3V       | 40 MIPS |  |

| DC70f                                    | 26                 | 30 | 1:64                                                                                                                                                                                                                                                                              | mA    | +25°C  |            |         |  |

| DC70g                                    | 25                 | 30 | 1:128                                                                                                                                                                                                                                                                             | mA    |        |            |         |  |

| DC71a                                    | 41                 | 50 | 1:2                                                                                                                                                                                                                                                                               | mA    |        |            | 40 MIPS |  |

| DC71f                                    | 25                 | 30 | 1:64                                                                                                                                                                                                                                                                              | mA    | +85°C  | 3.3V       |         |  |

| DC71g                                    | 24                 | 30 | 1:128                                                                                                                                                                                                                                                                             | mA    |        |            |         |  |

| DC72a                                    | 42                 | 50 | 1:2                                                                                                                                                                                                                                                                               | mA    |        |            |         |  |

| DC72f                                    | 26                 | 30 | 1:64                                                                                                                                                                                                                                                                              | mA    | +125°C | 3.3V       | 40 MIPS |  |

| DC72g                                    | 25                 | 30 | 1:128                                                                                                                                                                                                                                                                             | mA    |        |            |         |  |

#### TABLE 24-8: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

**Note 1:** IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

- Oscillator is configured in EC mode and external clock active, OSC1 is driven with external square wave from rail-to-rail with overshoot/undershoot < 250 mV</li>

- CLKO is configured as an I/O input pin in the Configuration word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (defined PMDx bits are set to zero and unimplemented PMDx bits are set to one)

- CPU executing while(1) statement

- · JTAG is disabled

- 2: Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated.

### TABLE 24-32:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING<br/>REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.4V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                    |     |       |                                      |  |

|--------------------|-----------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------------------------|--|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                | Min                                                                                                                                                                                                                                                                                     | Тур <sup>(2)</sup> | Мах | Units | Conditions                           |  |

| SP70               | TscP                  | Maximum SCK Input Frequency                                  |                                                                                                                                                                                                                                                                                         | _                  | 15  | MHz   | See Note 3                           |  |

| SP72               | TscF                  | SCKx Input Fall Time                                         | —                                                                                                                                                                                                                                                                                       | _                  | —   | ns    | See parameter DO32 and Note 4        |  |