Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | PIC                                                                              |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | ·                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 18x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp506at-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

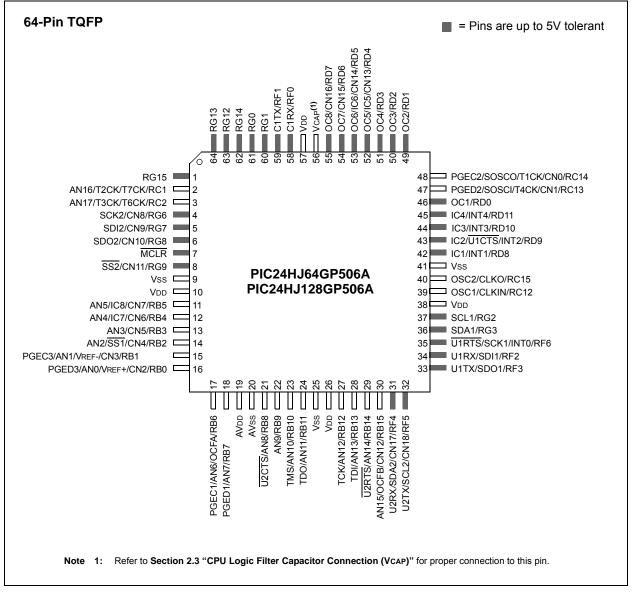

### Pin Diagrams (Continued)

#### Pin Diagrams (Continued) 100-Pin TQFP Pins are up to 5V tolerant AN22/CN22/RA6 AN23/CN23/RA7 OC7/CN15/RD6 OC6/CN14/RD5 OC5/CN13/RD4 IC6/CN19/RD13 OC8/CN16/RD7 C1TX/RF1 C1RX/RF0 AN26/RE2 **AN27/RE3** OC4/RD3 AN28/RE4 AN24/REC IC5/RD12 AN25/RE OC3/RD2 OC2/RD1 VCAP<sup>(1)</sup> RG13 RG12 RG14 RG1 RGO VDD 75 Vss RG15 74 PGEC2/SOSCO/T1CK/CN0/RC14 VDD 2 73 PGED2/SOSCI/CN1/RC13 AN29/RE5 3 72 OC1/RD0 AN30/RE6 IC4/RD11 71 AN31/RE7 5 70 IC3/RD10 AN16/T2CK/T7CK/RC1 6 69 IC2/RD9 AN17/T3CK/T6CK/RC2 68 IC1/RD8 AN18/T4CK/T9CK/RC3 8 AN19/T5CK/T8CK/RC4 67 INT4/RA15 - 9 SCK2/CN8/RG6 10 66 INT3/RA14 SDI2/CN9/RG7 11 65 Vss SDO2/CN10/RG8 OSC2/CLKO/RC15 12 64 MCLR OSC1/CLKIN/RC12 13 63 PIC24HJ64GP510A SS2/CN11/RG9 14 62 Vdd PIC24HJ128GP510A Vss 15 61 TDO/RA5 VDD 16 60 TDI/RA4 TMS/RA0 17 59 SDA2/RA3 AN20/INT1/RA12 118 58 SCL2/RA2 AN21/INT2/RA13 19 57 SCL1/RG2 AN5/CN7/RB5 20 56 SDA1/RG3 AN4/CN6/RB4 21 55 SCK1/INT0/RF6 AN3/CN5/RB3 \_\_\_\_22 54 SDI1/RF7 AN2/SS1/CN4/RB2 23 53 SDO1/RF8 PGEC3/AN1/CN3/RB1 24 52 U1RX/RF2 PGED3/AN0/CN2/RB0 25 U1TX/RF3 51 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50 50< TCK/RA1 U2RTS/RF13 U2CTS/RF12 AN12/RB12 [ AN13/RB13 [ AN14/RB14 [ U2RX/CN17/RF4 U2TX/CN18/RF5 AVSS AN8/RB8 [ AN9/RB9 [ AN10/RB10 [ AN11/RB11 [ AVDD VREF-/RA9 VREF+/RA10 ۵ Vss VDD IC7/U1CTS/CN20/RD14 IC8/U1RTS/CN21/RD15 PGEC1/AN6/OCFA/RB6 PGED1/AN7/RB7 Vss AN15/OCFB/CN12/RB15 Note 1: Refer to Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)" for proper connection to this pin.

| Pin Name                                           | Pin<br>Type                      | Buffer<br>Type                   | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------|----------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN31                                           | I                                | Analog                           | Analog input channels.                                                                                                                                                                                                                                                                                                                                                                                                  |

| AVDD                                               | Р                                | Р                                | Positive supply for analog modules. This pin must be connected at all times.                                                                                                                                                                                                                                                                                                                                            |

| AVss                                               | Р                                | Р                                | Ground reference for analog modules.                                                                                                                                                                                                                                                                                                                                                                                    |

| CLKI<br>CLKO                                       | I<br>O                           | ST/CMOS                          | External clock source input. Always associated with OSC1 pin function.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in RC and EC modes. Always associated<br>with OSC2 pin function.                                                                                                                                                      |

| CN0-CN23                                           | I                                | ST                               | Input change notification inputs.<br>Can be software programmed for internal weak pull-ups on all inputs.                                                                                                                                                                                                                                                                                                               |

| C1RX<br>C1TX<br>C2RX<br>C2TX                       | <br>0<br> <br>0                  | ST<br>—<br>ST<br>—               | ECAN1 bus receive pin.<br>ECAN1 bus transmit pin.<br>ECAN2 bus receive pin.<br>ECAN2 bus transmit pin.                                                                                                                                                                                                                                                                                                                  |

| PGED1<br>PGEC1<br>PGED2<br>PGEC2<br>PGED3<br>PGEC3 | I/O<br>I<br>I/O<br>I<br>I/O<br>I | ST<br>ST<br>ST<br>ST<br>ST<br>ST | Data I/O pin for programming/debugging communication channel 1.<br>Clock input pin for programming/debugging communication channel 1.<br>Data I/O pin for programming/debugging communication channel 2.<br>Clock input pin for programming/debugging communication channel 2.<br>Data I/O pin for programming/debugging communication channel 3.<br>Clock input pin for programming/debugging communication channel 3. |

| IC1-IC8                                            | I                                | ST                               | Capture inputs 1 through 8.                                                                                                                                                                                                                                                                                                                                                                                             |

| INT0<br>INT1<br>INT2<br>INT3<br>INT4               |                                  | ST<br>ST<br>ST<br>ST<br>ST       | External interrupt 0.<br>External interrupt 1.<br>External interrupt 2.<br>External interrupt 3.<br>External interrupt 4.                                                                                                                                                                                                                                                                                               |

| MCLR                                               | I/P                              | ST                               | Master Clear (Reset) input. This pin is an active-low Reset to the device.                                                                                                                                                                                                                                                                                                                                              |

| OCFA<br>OCFB<br>OC1-OC8                            | <br> <br>0                       | ST<br>ST<br>—                    | Compare Fault A input (for Compare Channels 1, 2, 3 and 4).<br>Compare Fault B input (for Compare Channels 5, 6, 7 and 8).<br>Compare outputs 1 through 8.                                                                                                                                                                                                                                                              |

| OSC1<br>OSC2                                       | I<br>I/O                         | ST/CMOS                          | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator                                                                                                                                                                                                                                                    |

| 0002                                               | 1/0                              |                                  | mode. Optionally functions as CLKO in RC and EC modes.                                                                                                                                                                                                                                                                                                                                                                  |

| RA0-RA7<br>RA9-RA10<br>RA12-RA15                   | I/O<br>I/O<br>I/O                | ST<br>ST<br>ST                   | PORTA is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                      |

| RB0-RB15                                           | I/O                              | ST                               | PORTB is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                      |

| RC1-RC4<br>RC12-RC15                               | I/O<br>I/O                       | ST<br>ST                         | PORTC is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                      |

| RD0-RD15                                           | I/O                              | ST                               | PORTD is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                      |

| RE0-RE7                                            | I/O                              | ST                               | PORTE is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                      |

| RF0-RF8<br>RF12-RF13                               | I/O                              | ST                               | PORTF is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                      |

| RG0-RG3<br>RG6-RG9<br>RG12-RG15                    | I/O<br>I/O<br>I/O                | ST<br>ST<br>ST                   | PORTG is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                      |

### TABLE 1-1: PINOUT I/O DESCRIPTIONS

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels Analog = Analog input P = Powe O = Output I = Input

# 3.3 CPU Control Registers

### REGISTER 3-1: SR: CPU STATUS REGISTER

| U-0                  | U-0                                          | U-0                                                                                                                                    | U-0              | U-0                      | U-0                 | U-0               | R/W-0          |  |  |  |

|----------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------|---------------------|-------------------|----------------|--|--|--|

|                      | _                                            | _                                                                                                                                      | _                |                          |                     |                   | DC             |  |  |  |

| bit 15               |                                              |                                                                                                                                        |                  |                          |                     |                   | bit 8          |  |  |  |

| R/W-0 <sup>(1)</sup> | R/W-0 <sup>(2)</sup>                         | R/W-0 <sup>(2)</sup>                                                                                                                   | R-0              | R/W-0                    | R/W-0               | R/W-0             | R/W-0          |  |  |  |

|                      | IPL<2:0> <sup>(2)</sup>                      |                                                                                                                                        | RA               | Ν                        | OV                  | Z                 | С              |  |  |  |

| bit 7                |                                              |                                                                                                                                        |                  |                          |                     |                   | bit (          |  |  |  |

| Legend:              |                                              |                                                                                                                                        |                  |                          |                     |                   |                |  |  |  |

| C = Clear only       | y bit                                        | R = Readabl                                                                                                                            | e bit            | U = Unimplei             | mented bit, read    | l as '0'          |                |  |  |  |

| S = Set only b       | bit                                          | W = Writable                                                                                                                           | bit              | -n = Value at            | POR                 |                   |                |  |  |  |

| '1' = Bit is set     |                                              | '0' = Bit is cle                                                                                                                       | ared             | x = Bit is unk           | nown                |                   |                |  |  |  |

| bit 15-9             | Unimpleme                                    | nted: Read as                                                                                                                          | ʻ0'              |                          |                     |                   |                |  |  |  |

| bit 8                | DC: MCU AL                                   | U Half Carry/B                                                                                                                         | orrow bit        |                          |                     |                   |                |  |  |  |

|                      | -                                            |                                                                                                                                        | low-order bit (  | for byte sized           | data) or 8th low-   | order bit (for wo | ord sized data |  |  |  |

|                      |                                              | sult occurred                                                                                                                          | 14b law and an k | it (far buta aim         | ad data) as Oth     | leve and an bit ( | for word since |  |  |  |

|                      |                                              | the result occu                                                                                                                        |                  | Dit (for byte siz        | ed data) or 8th     | iow-order bit (   | for word sized |  |  |  |

| bit 7-5              |                                              |                                                                                                                                        |                  | atus bits <sup>(2)</sup> |                     |                   |                |  |  |  |

|                      |                                              | PL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2)</sup> 11 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled |                  |                          |                     |                   |                |  |  |  |

|                      | 110 = CPU Interrupt Priority Level is 6 (14) |                                                                                                                                        |                  |                          |                     |                   |                |  |  |  |

|                      | 101 = CPU Interrupt Priority Level is 5 (13) |                                                                                                                                        |                  |                          |                     |                   |                |  |  |  |

|                      | 100 = CPU Interrupt Priority Level is 4 (12) |                                                                                                                                        |                  |                          |                     |                   |                |  |  |  |

|                      |                                              | <ul> <li>D11 = CPU Interrupt Priority Level is 3 (11)</li> <li>D10 = CPU Interrupt Priority Level is 2 (10)</li> </ul>                 |                  |                          |                     |                   |                |  |  |  |

|                      |                                              | nterrupt Priority                                                                                                                      |                  |                          |                     |                   |                |  |  |  |

|                      |                                              | nterrupt Priority                                                                                                                      |                  |                          |                     |                   |                |  |  |  |

| bit 4                | RA: REPEAT                                   | Loop Active bi                                                                                                                         | t                |                          |                     |                   |                |  |  |  |

|                      |                                              | loop in progres                                                                                                                        |                  |                          |                     |                   |                |  |  |  |

| bit 3                |                                              | J Negative bit                                                                                                                         | -                |                          |                     |                   |                |  |  |  |

|                      | 1 = Result w                                 | as negative                                                                                                                            |                  |                          |                     |                   |                |  |  |  |

| 1.11.0               |                                              | as non-negativ                                                                                                                         |                  | tive)                    |                     |                   |                |  |  |  |

| bit 2                |                                              | U Overflow bit                                                                                                                         |                  |                          |                     |                   |                |  |  |  |

|                      |                                              | ed for signed ar<br>ign bit to chang                                                                                                   | · ·              | omplement). It           | indicates an ove    | erflow of the ma  | agnitude whici |  |  |  |

|                      |                                              | <b>U U</b>                                                                                                                             | ·                | ic (in this arith        | metic operation)    |                   |                |  |  |  |

|                      | 0 = No overf                                 |                                                                                                                                        | .g               |                          |                     |                   |                |  |  |  |

| bit 1                | Z: MCU ALU                                   |                                                                                                                                        |                  |                          |                     |                   |                |  |  |  |

|                      |                                              |                                                                                                                                        |                  |                          | e time in the pa    |                   | oult)          |  |  |  |

| bit 0                |                                              | J Carry/Borrow                                                                                                                         |                  | Jo line ∠ Dil Na         | s cleared it (i.e., | a 11011-2010 10   | suit)          |  |  |  |

| 2.00                 |                                              |                                                                                                                                        |                  | oit (MSb) of the         | e result occurred   | 1                 |                |  |  |  |

|                      |                                              | -out from the M                                                                                                                        |                  |                          |                     | -                 |                |  |  |  |

|                      |                                              |                                                                                                                                        |                  |                          | RCON<3>) to for     |                   |                |  |  |  |

|                      | <pre>vei. The value i _&lt;3&gt; = 1.</pre>  | in parentneses                                                                                                                         | indicates the I  | rl     rl<3> =           | 1. User interrup    |                   |                |  |  |  |

|                      |                                              |                                                                                                                                        |                  |                          |                     |                   |                |  |  |  |

2: The IPL<2:0> Status bits are read only when NSTDIS = 1 (INTCON1<15>).

### 7.3 Interrupt Control and Status Registers

PIC24HJXXXGPX06A/X08A/X10A devices implement a total of 30 registers for the interrupt controller:

- INTCON1

- INTCON2

- IFS0 through IFS4

- IEC0 through IEC4

- IPC0 through IPC17

- INTTREG

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table.

The IFS registers maintain all of the interrupt request flags. Each source of interrupt has a Status bit, which is set by the respective peripherals or external signal and is cleared via software.

The IEC registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals. The IPC registers are used to set the interrupt priority level for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

The INTTREG register contains the associated interrupt vector number and the new CPU interrupt priority level, which are latched into vector number (VEC-NUM<6:0>) and Interrupt level (ILR<3:0>) bit fields in the INTTREG register. The new interrupt priority level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence that they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having vector number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0>, and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

Although they are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. The CPU STATUS register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU interrupt priority level. The user can change the current CPU priority level by writing to the IPL bits.

The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-1 through Register 7-32.

### REGISTER 7-12: IEC2: INTERRUPT ENABLE CONTROL REGISTER 2

| R/W-0         | R/W-0           | U-0                             | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|---------------|-----------------|---------------------------------|----------------|------------------|------------------|-----------------|---------|

| T6IE          | DMA4IE          | —                               | OC8IE          | OC7IE            | OC6IE            | OC5IE           | IC6IE   |

| bit 15        |                 |                                 |                |                  | •                |                 | bit 8   |

| R/W-0         | R/W-0           | R/W-0                           | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| IC5IE         | IC4IE           | IC3IE                           | DMA3IE         | C1IE             | C1RXIE           | SPI2IE          | SPI2EIE |

| bit 7         |                 |                                 |                | 0                |                  |                 | bit (   |

| Legend:       |                 |                                 |                |                  |                  |                 |         |

| R = Readable  | e bit           | W = Writable                    | bit            | U = Unimpler     | mented bit, read | l as '0'        |         |

| -n = Value at | POR             | '1' = Bit is set                |                | '0' = Bit is cle | eared            | x = Bit is unki | nown    |

| bit 15        | T6IE: Timer6    | Interrupt Enabl                 | e bit          |                  |                  |                 |         |

|               |                 | request enable                  |                |                  |                  |                 |         |

|               | 0 = Interrupt r | equest not ena                  | bled           |                  |                  |                 |         |

| bit 14        |                 | A Channel 4 D                   |                | Complete Interi  | rupt Enable bit  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 13        | •               | ted: Read as '                  |                |                  |                  |                 |         |

| bit 12        | •               | ut Compare Ch                   |                | unt Enable bit   |                  |                 |         |

| 511 12        | •               | request enable                  |                |                  |                  |                 |         |

|               |                 | equest not ena                  |                |                  |                  |                 |         |

| bit 11        | OC7IE: Outpu    | ut Compare Ch                   | annel 7 Interr | upt Enable bit   |                  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 10        | OC6IE: Outpu    | ut Compare Ch                   | annel 6 Interr | upt Enable bit   |                  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 9         | OC5IE: Outpu    | ut Compare Ch                   | annel 5 Interr | upt Enable bit   |                  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 8         |                 | Capture Channe                  |                | Enable bit       |                  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 7         |                 | Capture Channe                  |                | Enable bit       |                  |                 |         |

|               | -               | equest enable                   |                |                  |                  |                 |         |

|               | •               | request not ena                 |                |                  |                  |                 |         |

| bit 6         | -               | Capture Channe                  |                | Enable bit       |                  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 5         | •               | Capture Channe                  |                | -nable bit       |                  |                 |         |

|               | -               | equest enable                   | -              |                  |                  |                 |         |

|               | 0 = Interrupt r | equest not ena                  | bled           |                  |                  |                 |         |

| bit 4         | DMA3IE: DM      | A Channel 3 D                   | ata Transfer C | Complete Interi  | rupt Enable bit  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 3         | -               | Event Interrup                  |                |                  |                  |                 |         |

| bit J         |                 | equest enable                   |                |                  |                  |                 |         |

|               |                 | equest not ena                  |                |                  |                  |                 |         |

### REGISTER 7-13: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3

| R/W-0       R/W-0 <th< th=""><th>U-0</th><th>U-0</th><th>R/W-0</th><th>U-0</th><th>U-0</th><th>U-0</th><th>U-0</th><th>R/W-0</th></th<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | U-0       | U-0                           | R/W-0                         | U-0            | U-0            | U-0             | U-0      | R/W-0 |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------------|-------------------------------|----------------|----------------|-----------------|----------|-------|--|--|--|--|

| R/W-0       R/W-0 <th< td=""><td>—</td><td>—</td><td>DMA5IE</td><td>—</td><td>—</td><td>—</td><td>—</td><td>C2IE</td></th<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | —         | —                             | DMA5IE                        | —              | —              | —               | —        | C2IE  |  |  |  |  |

| C2RXIE       INT4IE       INT3IE       T9IE       T8IE       MI2C2IE       SI2C2IE       T7IE         bit 7       bit       bit       bit       bit       bit         segend:       R Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       bit         n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 13       DMASIE: DMA Channel 5 Data Transfer Complete Interrupt Enable bit       1       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0       = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0       = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0       = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0 = Interrupt request not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 15    |                               |                               |                |                |                 |          | bit 8 |  |  |  |  |

| C2RXIE       INT4IE       INT3IE       T9IE       T8IE       MI2C2IE       SI2C2IE       T7IE         bit 7       bit       bit       bit       bit       bit         segend:       R Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       bit         n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 13       DMASIE: DMA Channel 5 Data Transfer Complete Interrupt Enable bit       1       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0       = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0       = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0       = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0 = Interrupt request not enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |                               |                               |                |                |                 |          |       |  |  |  |  |

| it 7       bit         cegend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 13       DMASIE: DMA Channel 5 Data Transfer Complete Interrupt Enable bit       1       Is interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request enabled       0       Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request enabled       0       Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request not enabled       0       Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-0     | R/W-0                         | R/W-0                         | R/W-0          | R/W-0          | R/W-0           | R/W-0    | R/W-0 |  |  |  |  |

| segend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-14       Unimplemented: Read as '0'       i'' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 13       DMASIE: DMA Channel 5 Data Transfer Complete Interrupt Enable bit       1 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 3       C2RXIE: ECAN2 Event Interrupt Enable bit       1 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 4       Interrupt request not enabled       0 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 5       INT3IE: External Interrupt 3 Enable bit       1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 4       T9IE: Timer9 Interrupt Enable bit       1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 4       T9IE: Timer9 Interrupt Enable bit       1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 4       T9IE: Timer8 Interrupt Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | C2RXIE    | INT4IE                        | INT3IE                        | T9IE           | T8IE           | MI2C2IE         | SI2C2IE  | T7IE  |  |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 13       DMASIE: DMA Channel 5 Data Transfer Complete Interrupt Enable bit       1       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request not enabled       0       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0       = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0       = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request enabled       0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 7     |                               |                               |                |                |                 |          | bit   |  |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 13       DMASIE: DMA Channel 5 Data Transfer Complete Interrupt Enable bit       1       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request not enabled       0       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled       0       = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0       = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0       = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request enabled       0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Logondi   |                               |                               |                |                |                 |          |       |  |  |  |  |

| n = Value at POR 1' = Bit is set 0' = Bit is cleared x = Bit is unknown<br>bit 15-14 Unimplemented: Read as '0'<br>bit 13 DMASIE: DMA Channel 5 Data Transfer Complete Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled<br>bit 12-9 Unimplemented: Read as '0'<br>bit 8 C2IE: ECAN2 Event Interrupt Enable bit<br>1 = Interrupt request not enabled<br>0 = Interrupt request not enabled<br>bit 5 INT3IE: External Interrupt 3 Enable bit<br>1 = Interrupt request not enabled<br>0 = Interrupt request not enabled<br>bit 4 T9IE: Timer9 Interrupt Enable bit<br>1 = Interrupt request not enabled<br>0 = Interrupt request not enabled<br>0 = Interrupt request not enabled<br>bit 3 T8IE: Timer8 Interrupt Enable bit<br>1 = Interrupt request not enabled<br>0 = Interrupt request not enabled<br>0 = Interrupt request not enabled<br>0 = Interrupt request not enabled<br>1 = Interrupt request not enabled<br>0 = Interrupt request enabled<br>0 = Interrupt request enabled<br>0 = Interrupt req                                                                                       | •         | hit                           | W = Writable                  | hit            | II = Unimple   | mented hit rear | 1 as 'N' |       |  |  |  |  |

| Dit 15-14       Unimplemented: Read as '0'         Dit 13       DMASIE: DMA Channel 5 Data Transfer Complete Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request not enabled         Dit 12-9       Unimplemented: Read as '0'         Dit 8       C2IE: ECAN2 Event Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request enabled         Dit 7       C2RXIE: ECAN2 Receive Data Ready Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request enabled         Dit 6       INT4IE: External Interrupt 4 Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         Dit 5       INT3IE: External Interrupt 3 Enable bit         1 = Interrupt request not enabled       0 = Interrupt request enabled         Dit 4       T9IE: Timer9 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request enabled         Dit 4       T9IE: Timer9 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         Dit 4       T9IE: Timer9 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         Dit 4       T9IE: Timer8 Interrupt Terupt Enable bit         1 = Interrupt request not enabled       0 = Inter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                               |                               |                | •              |                 |          | own   |  |  |  |  |

| bit 13       DMASIE: DMA Channel 5 Data Transfer Complete Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request not enabled         0 bit 12-9       Unimplemented: Read as '0'         bit 8       C2IE: ECAN2 Event Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request not enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request en                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           | Ölt                           |                               |                |                |                 |          |       |  |  |  |  |

| 1 = Interrupt request enabled<br>0 = Interrupt request not enabled<br>0 = Interrupt request not enabled<br>0 = Interrupt request enabled<br>0 = Interrupt request enabled<br>0 = Interrupt request not enabled<br>0 = Interrupt request not enabled<br>0 = Interrupt request enabled<br>0 = Interrupt req | bit 15-14 | Unimplemen                    | nted: Read as '               | 0'             |                |                 |          |       |  |  |  |  |

| 0 = Interrupt request not enabled         oit 12-9       Unimplemented: Read as '0'         oit 8       C2IE: ECAN2 Event Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request enabled         oit 7       C2RXIE: ECAN2 Receive Data Ready Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         oit 7       C2RXIE: ECAN2 Receive Data Ready Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         oit 6       INT4IE: External Interrupt 4 Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         oit 5       INT3IE: External Interrupt 3 Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         oit 4       T9IE: Timer9 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         oit 3       T8IE: Timer8 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         oit 2       MI2C2IE: I2C2 Master Events Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request not enabled         oit 1       SI2C2IE: I2C2 Slave Events Interrupt Enable bit         1 = Interrupt request not enabled       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 13    | DMA5IE: DM                    | IA Channel 5 D                | ata Transfer ( | Complete Inter | rupt Enable bit |          |       |  |  |  |  |

| bit 12-9       Unimplemented: Read as '0'         bit 8       C2IE: ECAN2 Event Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 6       INT4IE: External Interrupt 4 Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 5       INT3IE: External Interrupt 3 Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 4       T9IE: Timer9 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 3       T8IE: Timer9 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 3       T8IE: Timer8 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 4       T9IE: Timer8 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 4       Interrupt request not enabled         bit 5       MI2C2IE: I2C2 Mast                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                               |                               |                |                |                 |          |       |  |  |  |  |

| bit 8       C2IE: ECAN2 Event Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request not enabled         bit 7       C2RXIE: ECAN2 Receive Data Ready Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request enabled         bit 6       INT4IE: External Interrupt 4 Enable bit         1 = Interrupt request enabled       0 = Interrupt request enabled         bit 5       INT3IE: External Interrupt 3 Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 5       INT3IE: External Interrupt 3 Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 4       T9IE: Timer9 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 3       T8IE: Timer9 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 4       T9IE: Timer9 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 3       T8IE: Timer9 Interrupt Enable bit         1 = Interrupt request not enabled       0 = Interrupt request not enabled         bit 4       SI2C2IE: I2C2 Master Events Interrupt Enable bit         1 = Interrupt request not enabled<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           | -                             | -                             |                |                |                 |          |       |  |  |  |  |

| 1 = Interrupt request enabled         0 = Interrupt request not enabled         0it 7       C2RXIE: ECAN2 Receive Data Ready Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request not enabled         0it 6       INT4IE: External Interrupt 4 Enable bit         1 = Interrupt request on enabled       0 = Interrupt request enabled         0 = Interrupt request enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           | •                             |                               |                |                |                 |          |       |  |  |  |  |

| <ul> <li>0 = Interrupt request not enabled</li> <li>0 = Interrupt request not enabled</li> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> <li>0 = Interrupt request enabled<!--</td--><td>bit 8</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></li></ul>                                                                                                                                                                                                                                                                                                   | bit 8     |                               |                               |                |                |                 |          |       |  |  |  |  |

| bit 7       C2RXIE: ECAN2 Receive Data Ready Interrupt Enable bit         1 = Interrupt request enabled       0 = Interrupt request not enabled         bit 6       INT4IE: External Interrupt 4 Enable bit         1 = Interrupt request enabled       0 = Interrupt request enabled         0 = Interrupt request ont enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt request not enabled         0 = Interrupt request not enabled       0 = Interrupt reque                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           | •                             | •                             |                |                |                 |          |       |  |  |  |  |